держит генератор тактовой частоты, первый и второй распределители импульсов, триггер, первый и второй счетчики, первый, второй, третий и четвертый элементы ИЛИ, причем выход генератора тактовой частоты соединен с тактовыми входами первого и второго распределителей импульсов и является первым-выходом блока распределения тактовых импуЛьсов, вторым и третьим выходами.которого являются соответственно первыйи второй выходы первого распределителя импульсов, выходы первого, второго, третьего и четвертого элементов ИЛИ являются соответственно четвертым, пятым, шестым и седьмым выходами блока распределения тактовых импульсов, восьмым и девятым выходами которого являются соответственно первый.и второй выходы второго распределителя импульсов первый и второй входы четвертого элемента ИЛИ подключены к трехьим выходам соответстве но первого и второго распределителей импульсов, четвертые выходы которых соединены соответственно с первым и вторым входами первого элемента ИЛИ, первый и второй входы второго элемента ИЛИ подключены к пятым выходам соответственно первого и второго распределителей импульсов, шестые выходы которых соединены соответственно с первым и вторым входами третьего элемента ИЛИ, седьмой выход первого распределителя импульсов через первый счетчик подключен к первому входу триггера, десятым выходом блока распределения тактовых импульсов является седьмой вЫход второго распределителя импульсов, восьмой выход KOTOpofb через второй счетчик подключен ко второму входу триггера, прямой и инверсный выходы которого соединены с управляющими входами соответственно второго и первого распределителей импульсов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Время-импульсное устройство дляуМНОжЕНия | 1979 |

|

SU847329A1 |

| Вычислительное устройство | 1985 |

|

SU1305722A1 |

| Телемеханическая система | 1983 |

|

SU1211783A1 |

| Многоканальная телеизмерительная система | 1985 |

|

SU1357993A1 |

| Многоканальная время-импульсная телеизмерительная система | 1984 |

|

SU1288738A1 |

| Сенсорный переключатель | 1982 |

|

SU1051720A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU930387A1 |

| Множительно-делительное устройство | 1982 |

|

SU1088016A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С КАНАЛАМИ СВЯЗИ | 1990 |

|

RU2020565C1 |

| Устройство для измерения и контроля технологических параметров | 1983 |

|

SU1136116A1 |

Изобретение относится к электрическим вычислительным устройствам и может быть использовано в аналоговых вычислительных машинах.

Известно времяимпульсное множи;тельное устройство, содержащее интеграторы, ключи, компаратор, одновибраторы l ..

Недостатком этого устройства является «изкое быстродействие,

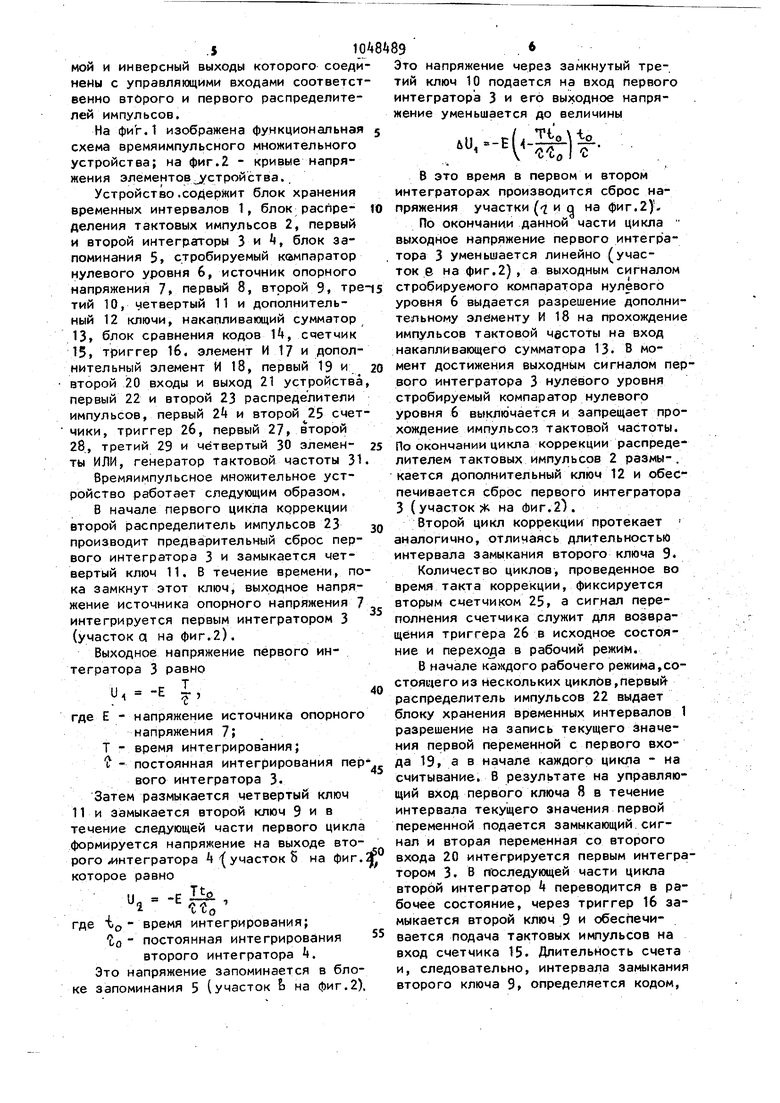

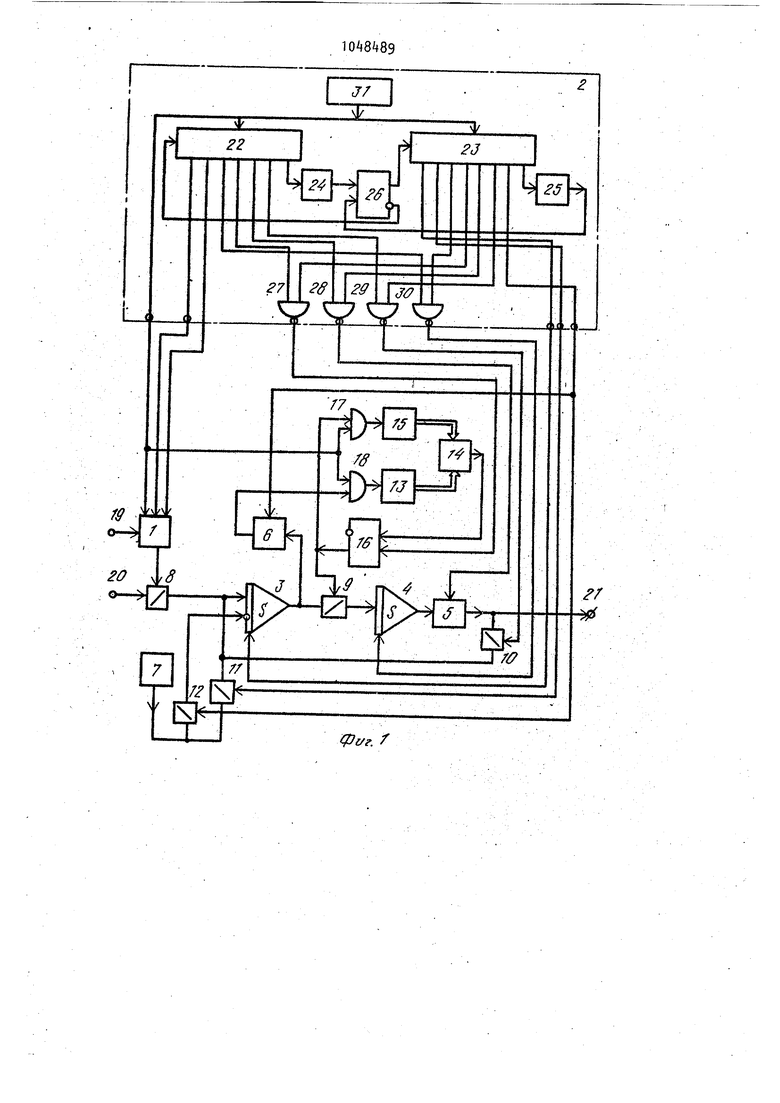

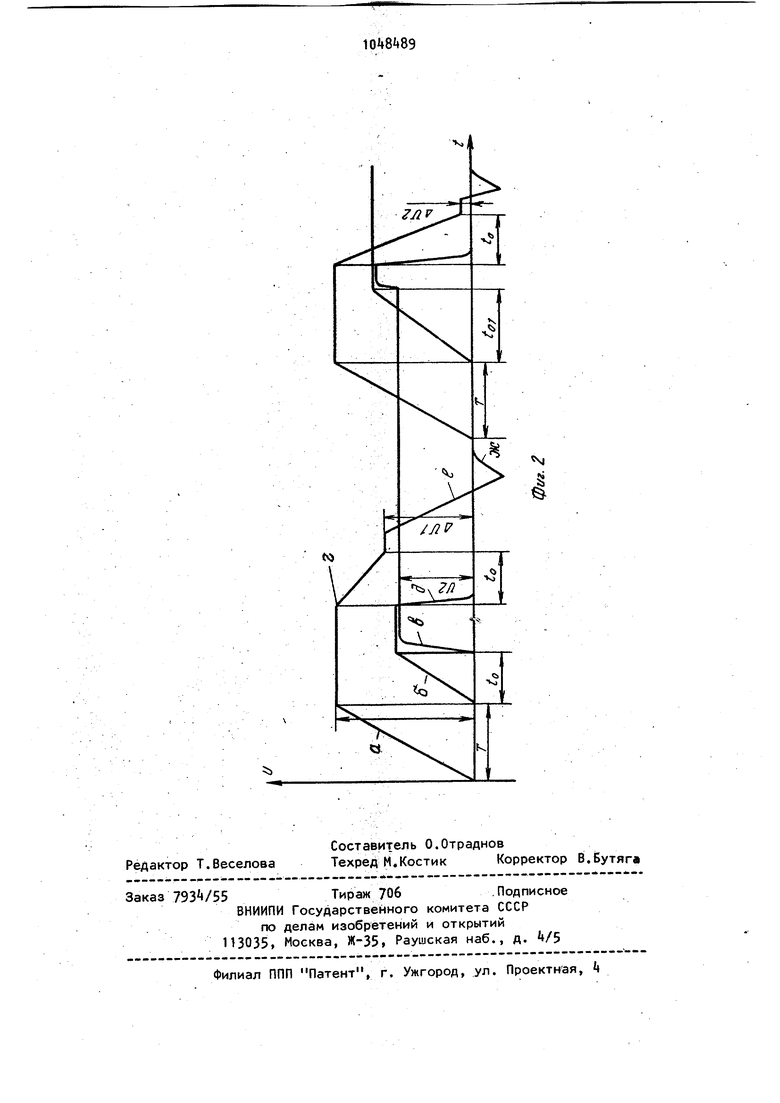

Наиболее-близким к предлагаемому является времяимпульсноемножительное устройство, содержащее блок хранения временных интервалов, выход которого подключен к управляющему входу первого ключа, соединеные последовательно первый интегратор, второй ключ, второй интегратор, блок запоминан я, выход которого является выходом устройства и через третий ключ соединен со входом первого интегратора, выход источника опорного напряжения через четвертый ключ соединен со входом первого интегратора, распределитель тактовь1х импульсов, элемент И, выход которого пйдключен ко входу источника, накапливающий сумматор, блок сравнения кодов, ко входам которого подключены выходы счетчика и накапливающего сумматора, триггер, ёыход которого соединен с управляющим входом второго ключа и с первым входом элементе И, второй вход которого соединен со входом тактовой частоты блока хранения временных интервалов и с первым выходом распределителя тактовых импульсов., второй и третий выходы которого подключены ко входам записи и считывания блока хранения временных интервалов, выход блока сравнения кодов соединен с первым вхо,дом триггера, четвертый, пятый, шестой, седьмой, восьмой и девятый выходы распределителя тактовых импульсов подключены соответственно ко второму .входу триггера, к управляющему входу блока записи, к у(1равляющему входу третьего-ключа, ко входу сброса второго интегратора, ко входу сброса первого интегратора, к управляющему входу четвертого ключа, первым и вторым входами устройства являются соответственно вход блока хранения временных интервалов и вход первого ключа. выход которого подключен к- первому входу первого интегратора 2J . Недостатком данного устройства является малое быстродействие и сложность струкЧуры. Цель изобретения - повьшение быстродейст;вйя и упрощение. Поставленная цель достигается тем что во времяимпульсное множительное устройство, содержащее блок хранения временных интервалов, вход которого является первым входом устройства, блок распределения тактовых импульсов первый, второй и третий выходы которого подключены соответственно ко входам тактовой частоты, записи и считыв.ания блока хранения временных интервалов, соединенные последовательно первый ключ, первый интегратор, второй ключ, второй интегратор, блок запоминания, выход которого является выходом устройства и через третий КЛИЧ соединен со входом перво го интегратора, источник опорного напряжения, выход которого через четвертый ключ подключен к входу пер вого интегратора., накапливающий сумматор, блок сравнения кодов, счетчик триггер и элемент И, выходы накапливающего сумматора vt счетчика подключены к соответствующим входам блока сравнения кодов, выход которого соединен с первым входом триггера, выход которого соединен с управляющим входом второго ключа и с первым входом элемента И, второй вход которого подключен к первому выходу блока рас ределения тактовых импульсов, выход элемента И соединен со входом счетчика, четвертый, пятый, шестой и сед мой выходы блока распределения тактовых импульсов соединены соответственно Со вторым входом триггера, с управляющим входом блока запоминания с управляющим входом третьего ключа и со входом сброса второго интеграто ра, выход блока хранения временных интервалов подключен к управляющему вхолу первого ключа, вход которого является вторым входом устройства, восьмой и девятый выходы блока-распр деления тактовых импульсов соединены соответственно со входом сброса первого интегратора и С управляющим . входом четвертого ключа, введены стробируемый компаратор нулевого уро ня, дополнительныёэлементы И, и ключ, причем выход первого интегратора соединен со входом стрбируемого компа3 ратора нулевого уровня, выход которого подключен к первому входу дополнительного элемента И, второй вход которого соединен со вторым входом основного элемента И, выход дополнительного элемента И подключен ко входу накапливающегосумматора, десятый выход блока распределения тактовых импульсов соединен с управляющими входами стробируемого компараторанулевого уровня и дополнительного ключа, выход источника опорного напряжения через дополнительный ключ подключен к другому входу первого инTejfiaTopa. , При этом блок распределения тактовых импульсов содержит генератор тактовый частоты, первый и второй распределители импульсов, триггер, первый и второй Счетчики, первый, второй, третий и четвертый элементы ИЛИ, причем выход генератора тактовой частоты соединен с тактовыми входами первого и второго распределителей импульсов и является первым выходом блока распределения тактовых импульсов, вторым и третьим ваходами которого являются соответственно первый и второй выходы первого распределителя импульсов, выходы первого, второго, третьего и четвертого элементов ИЛИ являются соответственно четвертым, пятым, шестым и седьмым выходами блока распределения тактовых импульсов, восьмым и девятым выходами которого являются соответственно первый и второй выходы второго распределителя имп ульсов, первы11 и второй входы четвертого элемента ИЛИподключен к третьим выходам соответственно первого и второго распределителей импульсов, четвертые выходы которых соединены соответственно с первым и вторым входами первого элемента ИЛИ, первый и второй входы второго элемента ИЛИ подключены к пятым выходм соответственно первого и второго распределителей импульсов, шес тые выходы которых соединены соответственно с первым и вторым входами третьего элемента ИЛИ, седьмой выход первого распределителя импульсов через первый Счетчик подключен к первому входу триггера, девятым выходом блока распределения тактовых импуль.сов является седьмой выход второго распределителя импульсов, восьмой выход которого через второй счетчий подключен ко второму входу триггера, прямои и инверсный выходы которого соеди нены с управляющими входами соответст венно второго и первого распределителей импульсов. На фиг,1 изображена функциональная схема времяимпульсного множительного устройства; на фиг.2 - кривые напряжения элементов устройства.. Устройство .содержит блок хранения временных интервалов 1, блок распределения тактовых импульсов 2, первый и второй интеграторы 3 и i, блок запоминания 5, стробируемый ксампаратор нулевого уровня 6, источник опорного напряжения 7, первый 8, второй 9, тре тий 10, четвертый 11 и дополнительный 12 ключи, накапливающий сумматор 13 блок сравнения кодов 1, счетчик 15, триггер 16, элемент И 17 и дополнительный элемент И 18, первый 19 и второй 20 входы и выход 21 устройства первый 22 и второй 23 распределители импульсов, первый 2k и второй 25 смет чики, триггер 2б, первый 27, второй 28, третий 29 и четвертый 30 элементы ИЛИ, генератор тактовой частоты 31 Времяимпульсное множительное устройство работает следующим образом, В начале первого цикла коррекции второй распределитель импульсов 23 производит предварительный сброс первого интегратора 3 и замыкается четвертый ключ 11, В течение времени, по ка замкнут этот ключ, выходное напряжение источника опорного напряжения 7 интегрируется первым интегратором 3 (участок а на фиг,2). Выходное напряжение первого интегратора 3 равно Т и, -Е где Е - напряжение источника опорного напряжения 7; время интегрирования; постоянная интегрирования пер вого интегратора 3. Затем размыкается четвертый ключ 11 и замыкается второй ключ 9 и в течение следующей части первого цикла формируется напряжение на выходе второго Л1нтегратора k ( участок S на фиг, которое равно время интегрирования; 1о - постоянная интегрирования второго интегратора i. Это напряжение запоминается в блоке запоминания 5 (участок Ь на фиг,2). Это напряжение через замкнутый третий ключ 10 подается на вход первого интегратора 3 и его выходное напряжение уменьшается до величины это время а первом и втором интеграторах производится сброс напряжения участки (7 и Q на фиг,2). По окончании данной части цикла выходное напряжение первого интегратора 3 уменьшается линейно (участок е на фиг,2), а выходным сигналом стробируемого компаратора нулевого уровня 6 выдается разрешение дополнительному элементу И 18 на прохождение импульсов тактовой частоты на вход накапливающего сумматора 13, В момент достижения выходным сигналом первого интегратора 3 нулевого уровня стробируемый компаратор нулевого уровня 6 выключается и запрещает прохождение импульсоз тактовой частоты. По окончании цикла коррекции распределителем тактовых импульсов 2 размы-. кается дополнительный ключ 12 и обес печивается сброс первого интегратора 3 (участок ж на фиг,2), Второй цикл коррекции протекает аналогично, отличаясь длительностью интервала замыкания второго ключа 9. Количество циклов, проведенное во время такта коррекции, фиксируется вторым счетчиком 25, а сигнал переполнения счетчика служит для возвращения триггера 26 в исходное состояние и перехода в рабочий режим, В начале каждого рабочего режима,состоящего из нескольких циклов,первый распределитель импульсов 22 выдает блоку хранения временных интервалов 1 разрешение на запись текущего значения первой переменной с первого входа 19 а в начале каждого цикла - на считывание. В результате на управляющий вход первого ключа 8 в течение интервала текущего значения первой переменной подается замыкающий сигнал и вторая переменная со второго входа 20 интегрируется первым интегратором 3, В последующей части цикла вторбй интегратор k переводится в рабочее состояние, через триггер 16 замыкается второй ключ 9 и обеспечивается подача тактовых импульсов на вход счетчика 15, Длительность счета и, следовательно, интервала замыкания второго ключа 9, определяется кодом. записанным в режиме коррекции в накапливающем сумматоре 13 и соответст вует -условию сходимости итерационного процесса: .T 1. L . Tfletjj - длительность счета. По окончании данного интервала выходное напряжение второго интегра Itopa А запоминается в блоке запоминания 5 а в оставшейся части цикла вЦходное напряжение этого блока через замкнутый третий ключ 10 подается йй вход первого интегратора 3, в кбто- ; ром интегрируется, и результат инте|-рирования алгебраически суммируется с ошибкой, накопленной в предыдущих циклах.,. ,.. . . ,,.-:.Г ...;: -.-.;- :- Ч 1 89 Проведение рабочего цикла некоторое числа раз обеспечивает на дыходе 21 напряжение ,.( где tx - переменная йа первом входе EV- переменная на втором входе 20. По сравнению с прототипом предлбженное времяийпульсное множительное устройство обладает более высоким быстродействием За счет уменьшения длительности процесса коррекции и ; более простой структурой за C4et устранения кодирующего преобразователя и дополнительного блока запоми- нания.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| МНОГОНАПРАВЛЕННОЕ ЭЛЕКТРОМАГНИТНОЕ ЯРМО ДЛЯ ОБСЛЕДОВАНИЯ КАНАЛОВ | 2012 |

|

RU2550760C1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Планшайба для точной расточки лекал и выработок | 1922 |

|

SU1976A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Время-импульсное устройство дляуМНОжЕНия | 1979 |

|

SU847329A1 |

Авторы

Даты

1983-10-15—Публикация

1982-05-28—Подача