(54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ СРЕДНЕКВАДРАТИЧЕСКОГО

ЗНАЧЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО для ИЗМЕРЕНИЯ МОЩНОСТИ:!оюзя-°-^'-^^•^?ПНП-.ТслНл^;::^:^:;:| | 1972 |

|

SU351170A1 |

| Устройство контроля каналов связи | 1988 |

|

SU1578820A1 |

| Цифровой измеритель RLC-параметров | 1986 |

|

SU1357874A1 |

| Устройство для определения средне-КВАдРАТичНОгО зНАчЕНия | 1979 |

|

SU842834A1 |

| Цифровой измеритель RLC-параметров | 1986 |

|

SU1337820A1 |

| Цифровой измеритель составляющих комплексных сопротивлений | 1987 |

|

SU1456907A1 |

| Устройство для управления фотоколориметрическим газоанализатором | 1982 |

|

SU1092468A1 |

| Аналого-цифровой преобразователь интегральных характеристик электрических величин | 1981 |

|

SU1035790A1 |

| Устройство для сортировки корнеклубнеплодов | 1983 |

|

SU1126232A1 |

| Цифровой вольтметр действующего значения | 1981 |

|

SU1073707A1 |

Изобретение относится к вычислительной технике и может быть использовано для оценки параметров случайных величин.

Известно устройство для определения среднеквадратического значения, содержащее п нуль-органов, выход каждого их которых через соответствующий дешифратор подключен к входу элемента ИЛИ, блок управления, первый выход которого соединен с управляющими входами дешифраторов, линейный и квадратичный интеграторы, входы которых подключены к выходу цифрового генератора, причем управляющие входы интеграторов соединены с вторым выходом блока управления, первый выход линейного интегратора соединен с входами п нуль-органов, а вторые выходы линейного и квадратичного интеграторов подключены к. соответствующим входам блока памяти, выход элемента ИЛИ подключен к одному из входов блока управления,другой вход блока управления соединен с выходом п-го дешифратора и первым управляющим входом блока памяти- 1.

Однако устройство характеризуется невысокой точностью и надежностью, обусловленными применением аналоговых блоков.

Наиболее близким к изобретению по технической сущности является устройство для вычисления среднеквадратического значения , содержащее цифровой генератор, выход которого подключен, к первому входу линейного интегратора, выход которого соеди10нен с первым входом блока памяти, второй вход которого объединен с первым входом нуль-органа и подключен к выходу интегрирующего квадратора, первый вход которого подклю15чен к первому выходу блока управления, второй выход блока управления соединен с вторым входом линейного интегратора, переключатель , п ин- формационных входов которого являют20ся входами устройства, второй вход нуль-органа соединен с первым выходом блока памяти,второй выход которого является выходом устройства,Недостатками известного устройст25ва .являются невысокое быстродействие и сложность.

Цель изобретения - упрощение устройства иповышение быстродействия.

Поставленная цель достигается

30 тем, что в устройство введен блок

переполнения, при этом вьоход линейно го интегратора подключен к (п+1)-му информационному входу переключателя и входу блока переполнения, выход которого соединен с первым входом блока управления, второй вход которого соединен с выходом нуль-органа, третий выход блока управления подключен к соответствующим управляющим входам переключателя, выход которого соединен с вторым входом интегрирующего квадратора, четвертый выход блок управления подключен к третьему входу блока памяти.

Кроме того, блок управления содержит два триггера, два элемента И, два делителя частоты, дешифратор, два счетчика, два элемента ИЛИ, два элемента 2И-ИЛИ, фазовращатель, четыре мультивибратора, при этом вход первого мультивибратора объединен с первыми входами первого элемента ИЛИ, первого и второго счетчиков, первого и второго элементов 2И-ИЛИ и фазовращателя и подключен к единичному выходу первого триггера, выходы первого И второго мультивибраторов, первого и второго элементов И объединены и являются первым выходом блока управления, единичный выход первого триггера является вторым выходом блока управления нулевой выход первого триггера соединен с вторыми входами первого и второго элементов 2И-ИЛИ, выход первого элемента 2И-ИЛИ, через второй мультивибратор подключен к второму входу второго счетчика и единичному дходу второго триггера, нулевой вход которого соединен с выходом второго элемента 2И-ИЛИ, третий вход которого подключен к выходу первого счетчика, второй вход которого соединен с выходом первого элемента И, четвертый вход второго элемента 2ИИЛИ подключен- к выходу второго элемента И, первый вход которого объединен с первым входом первого элемента И и соединен с выходом второго триггера, второй вход первого элемента И подключен к первому выходу фазовращателя, второй выход которого соединен с вторым входом второго элемента И, третий вход которого подключён к выходу первого элемента .ИЛИ, второй вход фазовращателя объединен с входами первого и второго делителей частоты и соединен с выходом третьего мультивибратора, выходы первого и второго делителей частоты подключены соответственно к третьему и четвертому входам первого элемента 2И-ИЛИ, йУхода второго счетчика соединены с cooTBexftTByкядими входами дешифратора, выход которого является третьим выходом блока управления, выход старшего разряда второго счетчика подключен к входу четвертого мультивибратора.

выход которого соединен с входом установки в единицу первого триггера, вход установки ц ноль которого подключен к выходу второго элемента ИЛ входы которого являются соответствено первым и вторым входами блока управления, выход четвертого мультивибратора является четвертым выхо.дом блока управления.

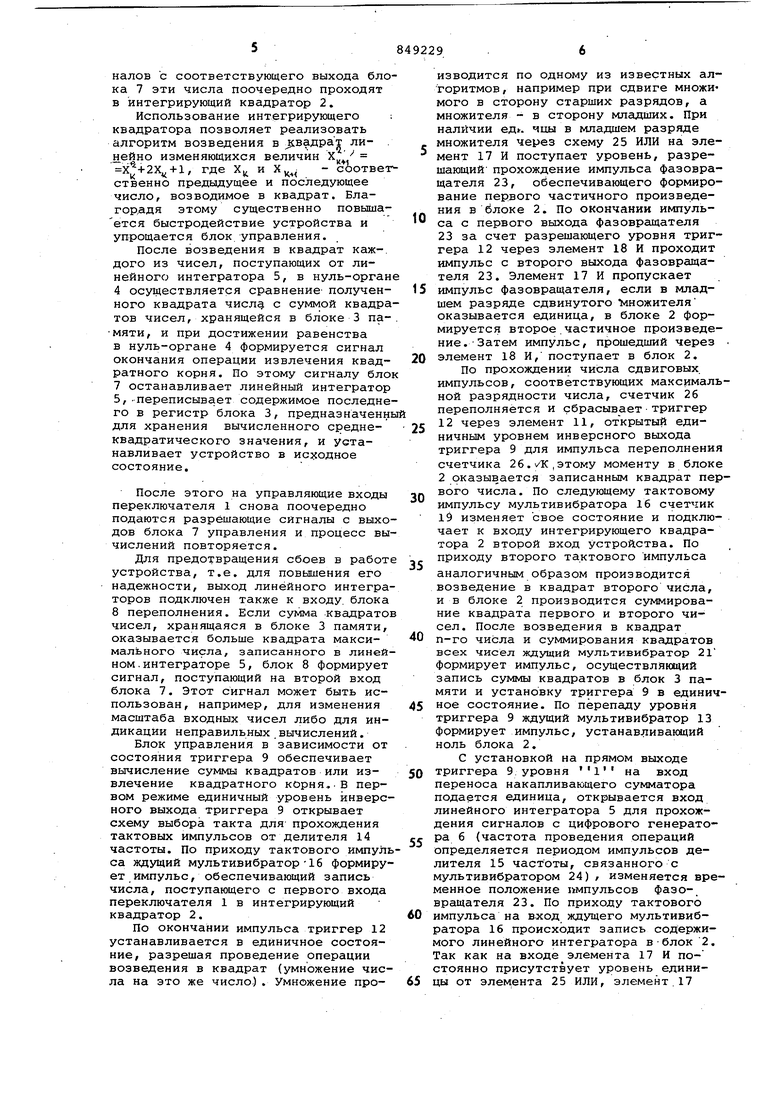

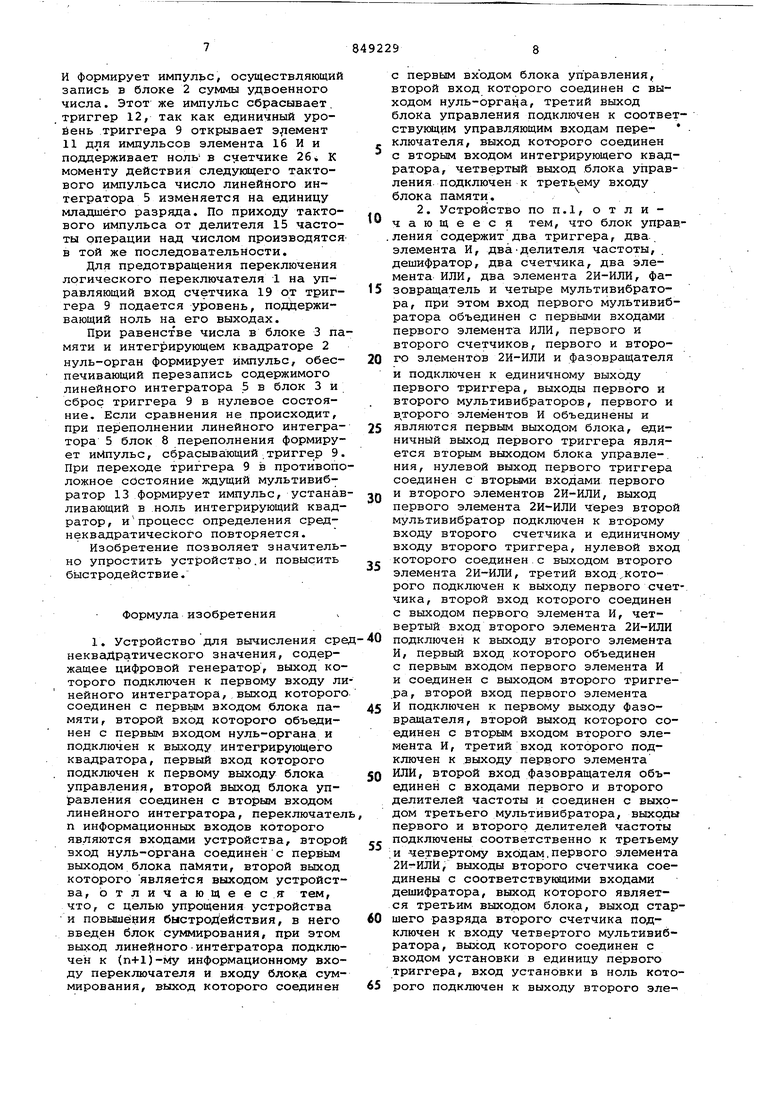

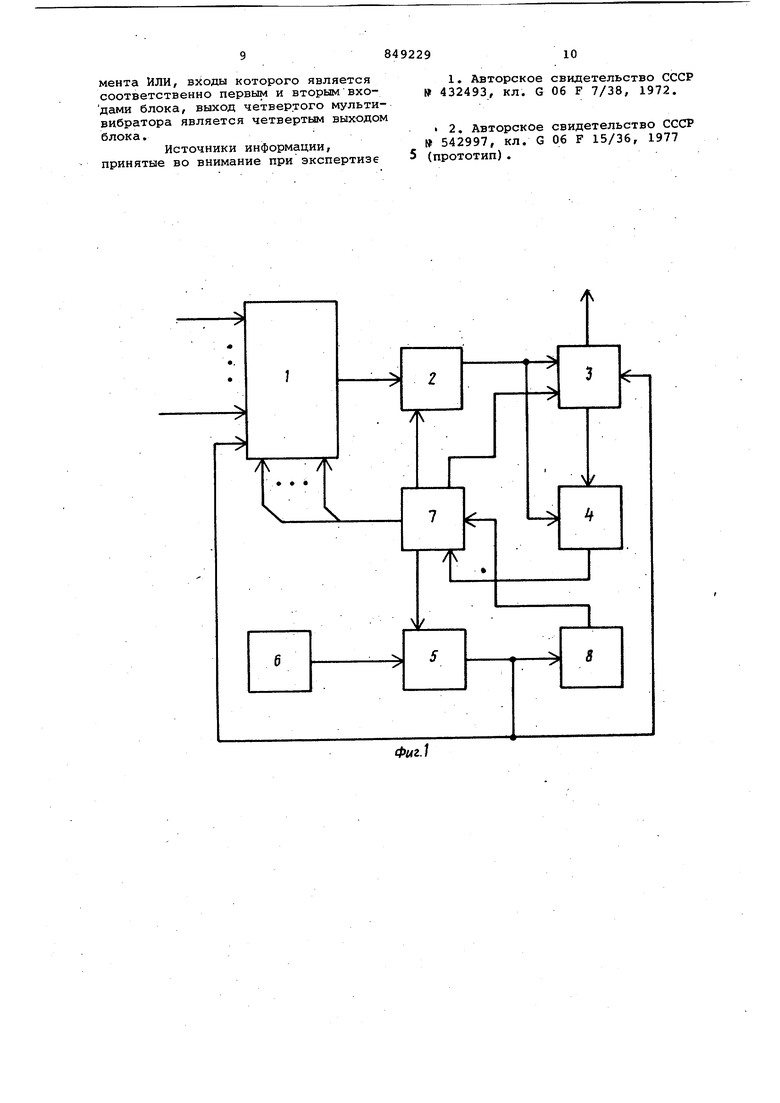

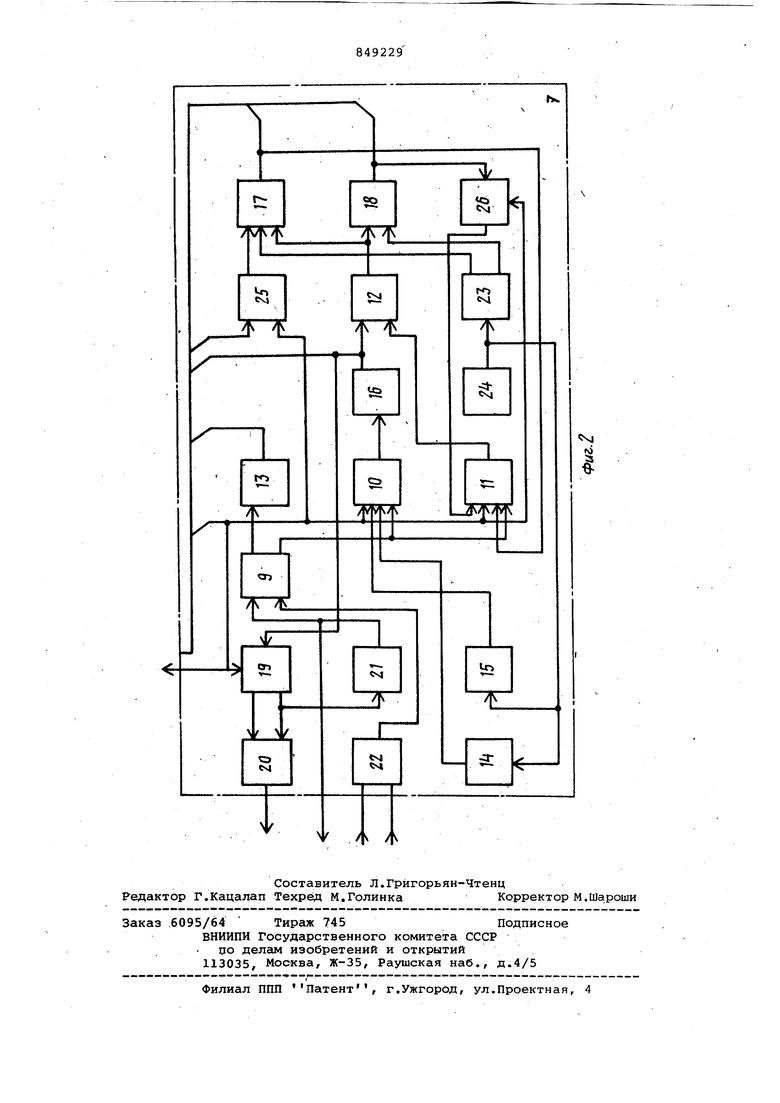

На фиг.1 представлена блок-схема устройства; на фиг.2 - схема блока, .управления.

Устройство содержит переключател 1, интегрирующий квадратор 2, блок 3 памяти нуль-орган 4, линейный интегратор 5, цифровой генератор б, блок 7 управления и блок 8 переполнения.

Блок управления состоит из первого триггера 9, первого 10 и второго 11 элементов 2И-ИЛИ, второго триггера 12, первого мультивибратор 13, первого 14 и второго 15 делителей частоты, второго мультивибратора 16, второго элемента 17 И,первого элемента .18 И, второго счетчика Г9, дешифратора 20, четвертого мультивибратора 21, второго элемента 22 ИЛИ, фазовращателя 23, третьего мультивибратора 24, первого элеме.нта 25 ИЛИ и первого счетчика 26.

Устройство работает следующим образом.

Коды входных чисел подаются на информационные входы переключателя а на управляющие входы с соответствующих выходов блока 7 управления в течение каждого такта работы поочередно поступают сигналы, разрешающие прохождение входных чисел в интегрирующий квадратор 2, в котором осуществляется возведение числа в квадрат, суммирование результата возведения в квадрат с числом, записанным в интегрирующем квадраторе 2 в предыдущем такте работы, и хранение полученной суммы до следующего такта. В результате поочередного возведения в квадрат входных чисел в интегрирующем квадраторе 2 оказывается записанной сумма квадратов всех чисел.

Далее производится извлечение квадратного корня. Сначала по сигнала.м с блока 7 управления код, соответствующий сумме квадратов входных чисел, переписывается в регистр блока 3 памяти, а интегрирующий квадратор 2 устанавливается в нуль. Затем разрешающий сигнал с блока 7 подается на линейный интегратор 5, например счетчик импульсов на вход которого поступают импульсы от цифрового генератора 6. Коды чисел, начиная от нуля, с выхода линейного интегратора 5 подаются на (п+1)-й информационный вход переключателя 1, и при подаче на (п+1)-й управляющий вход переключателя сигналов с соответствующего выхода бло ка 7 эти числа поочередно проходят в интегрирующий квадратор 2. Использование интегрирующего квадратора позволяет реализовать алгоритм возведения в свадрат лицейно изменяющихся величин хЧ2Х; + 1, где Х и Х - сбответ ственно предыдущее и последующее число, возводимое в квадрат. Благорддя этому существенно повышается быстродействие устройства и упрощается блок управления. После возведения в квадрат каж-. дого из чисел, поступающих от линейного интегратора 5, в нуль-орган 4 осуществляется сравнение- полученного квадрата числ с суммой квадра тов чисел, хранящейся в блоке 3 памяти, и при достижении равенства в нуль-органе 4 формируется сигнал окончания операции извлечения квадратного корня. По этому сигналу бло 7останавливает линейный интегратор 5,.переписывает содержимое последне го в регистр блока 3, предназначенн для хранения вычисленного среднеквадратического значения, и устанавливает устройство в исходное состояние. После этого на управляющие входы переключателя 1 снова поочередно подаются разрешающие сигналы с выхо дов блока 7 управления и процесс вы числений повторяется. Для предотвращения сбоев в работ устройства, т.е. для повышения его надежности, выход линейного интегра торов подключен также к входу, блока 8переполнения. Если сумма квадрато чисел, хранящаяся в блоке 3 памяти, оказывается больше квадрата максимального числа, записанного в линей ном . интеграторе 5, блок 8 формирует сигнал, поступающий на второй вход блока 7. Этот сигнал может быть использован, например, для изменения масштаба входных чисел либо для индикации неправильных.вычислений. Блок управления в зависимости от состояния триггера 9 обеспечивает вычисление суммы квадратов или извлечение квадратного корня,.В первом режиме единичный уровень инверсного выхода триггера 9 открывает схему выбора такта для прохождения тактовых импульсов от делителя 14 частоты. По приходу тактового импуль са ждущий мультивибратор16 формирует импульс, обеспечивающий запись числа, поступающего с первого входа переключателя 1 в интегрирующий квадратор 2. По окончании импульса триггер 12 устанавливается в единичное состояние, разрешая проведение операции возведения в квадрат (умножение числа на это же число.) . Умножение производится по одному из известных алгоритмов , например при сдвиге множи мого в сторону старших: разрядов, а множителя - в сторону младших. При наличии ед. чцы в младшем разряде множителя через схему 25 ИЛИ на элемент 17 И поступает уровень, разрешающий прохождение импульса фазовращателя 23, обеспечивающего формирование первого частичного произведения в блоке 2. По окончании импульса с первого выхода фазовращателя 23 за счет разрешающего уровня триггера 12 через элемент 18 И проходит импульс с второго выхода фазовращателя 23. Элемент 17 И пропускает импульс фазовращателя, если в младшем разряде сдвинутого множителя оказывается единица, в блоке 2 формируется второе.частичное произведение. Затем импульс, прошедший через . элемент 18 И, поступает в блок 2. по прохождении числа сдвиговых импульсов, соответствующих максимальной разрядности числа, счетчик 26 переполняется и сбрасывает.триггер 12 через элемент 11, открытый единичным уровнем инверсного выхода триггера 9 для импульса переполнения счетчика 26./К,этому моменту в блоке 2 оказывается записанным квадрат первого числа. По следующему тактовому импульсу мультивибратора 16 счетчик 19 изменяет свое состояние и подключает к входу интегрирующего квадратора 2 второй вход устройства. По приходу второго тактового импульса аналогичным образом производится возведение в квадрат второго числа, и в блоке 2 производится суммирование квадрата первого и второго чисел. После возведения в квадрат п-го числа и суммирования квадратов всех чисел ждущий мультивибратор 21 формирует импульс, осуществляющий запись суммы квадратов в блок 3 памяти и установку триггера 9 в единичное состояние. По перепаду уровня триггера 9 ждущий мультивибратор 13 Формирует импульс/ устанавливающий ноль блока 2, С установкой на прямом выходе триггера 9,уровня Ч на вход переноса накапливающего сумматора подается единица, открывается вход линейного интегратора 5 для прохождения сигналов с цифрового генератора 6 (частота проведения операций определяется периодом импульсов делителя 15 частоты, связанного с мультивибратором 24), изменяется временное положение 1 мпульсов фазовращателя 23. По приходу тактового импульса на в-ход ждущего мультивибратора 16 происходит запись содержимого линейного интегратора в-блок2. Так как на входе элемента 17 И постоянно присутствует уровень единицы от элемента 25 ИЛИ, элемент.17

И формирует импульс, осуществляющий запись в блоке 2 суммы удвоенного числа. Этот же импульс сбрасывает, триггер 12, так как единичный уровень триггера 9 открывает э;1емент 11 для импульсов элемента 16 И и поддерживает ноль в сч етчике 26 К моменту действия следующего тактового импульса число линейного интегратора 5 изменяется на единицу младшего разряда. По приходу тактового импульса от делителя 15 частоты операции над числом производятся в той же последовательности.

Для предотвращения переключения логического переключателя 1 на управляющий вход счетчика 19 от триггера 9 подается уровень, поддерживающий ноль на его выходах.

При равенстве числа в блоке 3 памяти и интегрирующем квадраторе 2 нуль-орган формирует импульс, обеспечивающий перезапись содержимого линейного интегратора 5 в блок 3 и сброс триггера 9 в нулевое состояние. Если сравнения не происходит, при переполнении линейного интегратора 5 блок 8 переполнения формирует иМпульс, сбрасывающий триггер 9. При переходе триггера 9 в противоположное состояние ждущий мультивибратор 13 формирует импульс, устанав ливающий в ноль интегрирующий квадратор, и процесс определения среднеквадратического повторяется.

Изобретение позволяет значительно упростить устройство.и повысить быстродействие.

Формула изобретения

с первым входом блока управления, второй вход которого соединен с выходом нуль-оргаца, третий выход блока управления подключен к соответствукядим управляющим входам переключателя, выход которого соединен с вторым входом интегрирующего квадратора, четвертый выход блока управления подключен к третьему входу блока памяти.

и подключен к единичному выходу первого триггера, выходы первого и второго мультивибраторов, первого и в торого элементов и объединены и являются первым выходом блока, единичный выход первого триггера является вторым выходом блока управле-. ния, нулевой выход первого триггера соединен с вторыми входами первого и второго элементов 2И-ИЛИ, выход первого элемента 2И-ИЛИ через второй мультивибратор подключен к второму входу второго счетчика и единичному входу второго триггера, нулевой вход которого соединен с выходом второго элемента 2И-ИЛИ, третий вход,которого подключен к выходу первого счетчика, второй вход которого соединен с выходом первого элемента И, четвертый вход второго элемента 2И-ИЛИ подключен к выходу второго элемента И, первый вход которого объединен с первым входом первого элемента И и соединен с выходом второго триггера, второй вход первого элемента И подключен к первому выходу фазовращателя, второй выход которого соединен с вторым входом второго элемента И, третий вход которого подключен к выходу первого элемента ИЛИ, второй вход фазовращателя объединен с входами первого и второго делителей частоты и соединен с выходом третьего мультивибратора, выходы первого и второго делителей частоты подключены соответственно к третьему ;и четвертому входам,первого элемента 2И-ИЛИ, выходы второго счетчика соединены с соответствукяцими входами дешифратора, выход которого является третьим выходом блока, выход старшего разряда второго счетчика подключен к входу четвертого мультивибратора, выход которого соединен с входом установки в единицу первого триггера, вход установки в ноль которого подключен к выходу второго элемента ИЛИ, которого является соответственно первым и вторым входами блока, выход четвертого мультивибратора является четвертым выходом блока.

Источники информации, принятые во внимание при экспертизе

свидетельство СССР 06 F 7/38, 1972.

свидетельство СССР 06 F 15/36, 1977

Ч

Авторы

Даты

1981-07-23—Публикация

1979-04-12—Подача