1

Изобретение относится к вычислительной технике и может быть испольэорано в виброметрии, в частности в цифровых шумомерах.

Известно устройство для определения среднеквадратического значения содержащее два счетчика, накапливающий сумматор, триггер, вентиль, линию задержки, элемент ИЛИ, элементы И 1 1 , ; .

Наиболее близким к предлагаемому по техническому решению является устройство для определения среднеквадратического значения, содержащее цифровой генератор ймпульсЬв, первый и второй выходы которого подключены соответственно к первому входу линейного и квадратичного интеграторав вторые входы которых объединены и соединены с первым выходом блока управления, выход линейного интегратора подключен к информационному входу первого регистра памяти и к первому входу первого нуль-органа, второй вход которого является первым входом устройства, выход квадратичного интегратора соединен с первым входом второго нуль-органа 2.

Известные устройства сложны и имеют низкое быстродействие. I

Цель изобретения - упрощение устройства.и повышение его быстродействия.

Поставленная цель достигается тем, что в .устройство для определений среднеквадратического значения введены сумматор, регистр, переключатель, при этом выход квадратичного интегратора подключен к первому

0 входу переключателя, второй вход которого объединен с первым входом регистра и соединен со вторым выходом Ълока управления,первый вход которого подключен к выходу первого нуль-орга5на, второй вход блока управления является вторым входом устройства,выход регистра соединен с третьим входом переключателя, выход которого подключен к вычитающему входу сумматора, суммирующий вход которого объе0динен со вторым входом второго нульоргана и соединен с выходом второго регистра блока памяти, информационный вход которого объединен со

5 вторым входом регистра и подключен к выходу сумматора, управляющий вход второго регистра памяти соединен с первым выходом блока управления, выход второго нуль-органа подключен к управляющему входу первого

0

егистра блока памяти, выход которого является выходом устройства.

Кроме того, блок управления соержит триггер, элемент И, счетчик элемент ИЛИ, выход которого подклюен к счетному входу триггера, выход которого сЬединен с первым входом Элемента И и является вторым выходом блока управления , выход элемента И подключен к счетному входу счетчика, выход которого является первым выходом блока управления и соединен с первым входом элемента ИЛИ, вторые входы элемента ИЛИ и элемента И являются соответственно первым и вторым входами блока управления.

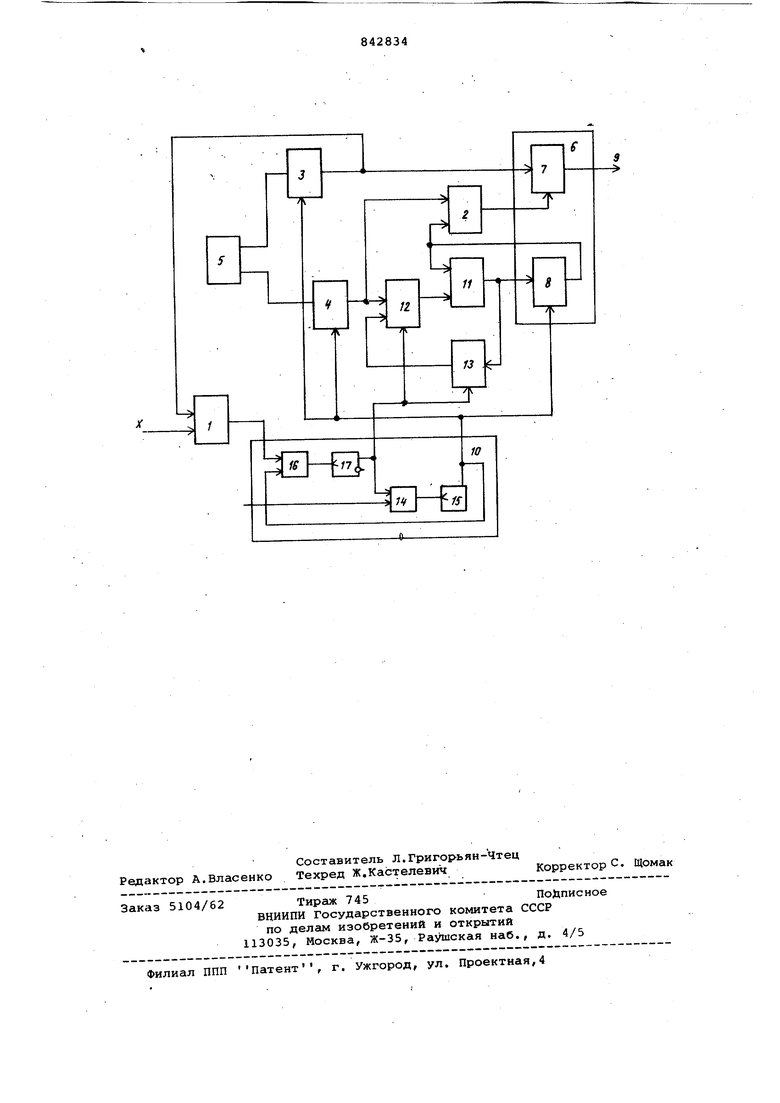

На чертеже представлено устройство, блок-схема.

Устройство содержит первый и второй нуль-органы 1,2, линейный интегратор 3j, квадратичный интегратор 4, цифровой генератор 5, блок 6 памяти, первый регистр 7 Памяти, второй регистр 8 памяти, выход блока памяти 9, блок 10 управления, сумматор 11, переключатель 12, регистр 13, элемент И 14, счетчик 15, элемент ИЛИ 16, триггер 17,

Предлагаемое устройство реализует выражение

Т

v4

...4.х

, где X,,,,,X п- массив отсчетов входного сигнала, являющийся хронологи..ч ее КИМ потоком, предшествующим текущему отсчегу х. Однако в предлагаемом устройстве это вырггжение представлено в рекуррентном виде, удобном для вычисления скользящего среднего. Предположим,что на вход устройства поступил очередной х„ отсчет, тогда- для усреднения взяты отсчеты Хд,,.Х| и выражение 1; принимает вид:

.....,,.lj4l

. п

-й....-.4Х

(ПН),

; где

среднее значение квадрата, полученное на предыдущем этапе вычислений (когда последним входным отсчетом был х), Продолжая равенство, имеем

17 I 51 -х л. |() n, г, n- n

Последняя часть равенства дает рекурентную формулу

Г I

vl

г Jii Jsa-lixriV4 1 n+(

Устройство работает следующим образом.

В исходном положении интеграторы сброшены в О, на выходах нульорганов - нулевые сигналы, переключатель замыкает цепьг выход квадратичного интегратора - вычитающий 5 вход сумматора. Триггер 17 находится в нулевом состоянии, при этом его выход,являющийся вторым выходом блока 10 управления, одновременно соединен с элементом 14 И, на другой

л вход которого подаются тактовые

импульсы ТИ, Так как триггер 17 находится в О, то элемент 14 и . закрыт и тактовые импульсы ТИ через него не проходят. Счетчик 15 также находится в состоянии, С

5 началом работы начинается одновременное формирование линейного (на линейном интеграторе 3) и квадратичного (на квадратичном интегра,торе 4) кодов. Интеграторы образуют

0 две самостоятельные цепи в (пределах цикла преобразования), Цепи зти начинаются интеграторами и заканчиваются регистрами 7 и 8 блока 6 памяти. Цепь квадратирования реализует подкоренное выражение. Последовательность квадратов чисел (временная дискретизированная парабола) подается через переключатель 12 на вычитающий вход сумматора 11, на

.. прямом входе которого держится код х , зафиксированный в регистре 8 блока б памяти на предьвдущем этапе преобразования. Соответствующий временной параболе код первой степени непрерывно сравнивается с входным

отсчетом х, нуль-органом 1, В

момент равенства сравниваемых чисел нуль-орган 1 вырабатывает импульс, который поступает на вход блока 10 управления. Импульс проходит через

0 элемент 16 ИЛИ на счетный вход

триггера 17, переключая триггер 17 в единичное состояние. На выходе триггера 17, а, значит, .и на втором выходе блока 10 управления, появляется единичный потенциал, который выдает разрешение элементу 14 И на прохождение тактовых импульсов ТИ на счетчик 15 и с появлением которого (в момент формирования фронл та нарастания этого потенциала)

происходит запись в регистр 13 текущей разности с выхода сумматора 11. Эта разность равна х - х , Этот же потенциал переводит переключатель 12 во второе состояние, при

5 котором замыкается цепь: выход регистра. 13 - вычитающий вход сумматора 11, При этом разность, записанная в регистре 13, подается на сумматор СОсдвигом на п разрядов

0 вправо, т.е, в виде(,)/ri.

На выходе сумматора, таким образом, устанавливается код х , , т,е, новое значение усредненного квадрата, которое и сохраняется до конца

5 цикла преобразования. Вторая параллельная цепь производит вычисление квадратного корня из числа х . Пр этом нуль-орган 2 этой цепи непрерывно сравнивает код х с выхода блока 6 памяти с временной парабол от квадратичного интегратора 4, В момент равенства чисел нуль-орган вырабатывает сигнал на первый управляющий вход блока б памяти, и в регистр 7 этого блока записывает код первой степени с выхода линейного интегратора, 3 . Записанный код равняется корню квадратному из х т.е. о После выполнения описанн действий в цепях преобразования в счетчике 15 наступает переполнение импульс переполнения подается на первый. выход блока 10 управления 1и через элемент 16 ИЛИ - на счетны вход триггера 17, возвращая его в О состояние, С появлением импу са переполнения в регистр 8 блока 6 памяти (по второму управляющему входу) записывается код х ., интег раторы обнуляются и переключатель 12 возвращается в исходное положение. Таким образом, в исходное положение возвращается вся схем устройства. Объем счетчика 15 выбра из расчета времени преобразования максимальнсэго числа, т.е.переполнение счетчика 15 не может наступить раньше, чем окончатся вычисления. После этого на вход устройства поступает следующий отсчет х. и все повторяется снова в описанной выае последовательности. В отличие от известного предлагаемое устройство выполняет квадратирование и извлечение квадратного корня однов ременно, в пределах одного цикла, почему и. является принципи.ально более быстродействующим. Количество усредняемых чисел (п) варьируется величиной сдвига числа с выхода регистра 13 по вычитающему входу сумматора 11, без затрат оборудования, что также резко отличает предлагаемое .ство рт известногр. Формула изобретения 1. Устройство для определения среднеквадратичного значения, содер жащее цифровой генератор импульсов, перрый и второй выходы которого подключены соответственно к первьам входам линейного и квадратичного интеграторов, вторые входы которых объединены и соединены с первым выходом блока управления, выход линейного интегратора подключен информационному входу первого регистра памяти и к первому входу первого нуль-органа, второй вход которого является первым входом устройства, выход квадратичного интегратора соединен -с первым входом второго нуль-органа, отличающееся тем, что, с целью упрощения устройства и повышения быстродействия, в него введены сумматор, регистр и- переключатель, при этом выход квадратичного интегратора подключен к первому входу переключателя, второй вход которого объединен с первым входом регистра и соединен со вторым выходом блока.управления, первый,вхоД которого подключен к выходу первого нуль-органа, второй вход блока управления является вторым входом устройства, выход регистра соединен с третьим входом переключателя, выход которого подключен к вычитающему входу ;сумматора, суммирующий вход которого объединен со вторым входом нуль-органа и соединен с выходом второго регистра памяти, информационный вход которого объединен со вторым входом регистра и подключен к выходу сумматора,; управляющий, вход второго регистра памяти соединен с первым входом блока управления, выход второго нуль-органа подключен к .управляющему входу первого регистра памяти, выход которого является выходом устройства. 2. Устройство по п, 1, отличающееся тем, что блок управления содержит триггер, элемент И, счетчик и .элемент ИЛИ, .выход которого подключен к счетному входу триггера, выход которого соединен с первым входом элемента И и является вторым выходом блока управления, выход элемента И подключен к счетному входу счетчика, выход которого является первым выходом блока управления и соединен первым входом элемента ИЛИ, вторые входы элемента ИЛИ и элемента И являются соответственно первым и вторым входами блока управления. Источники информации, принятые во внимание при экспертизе 1,Авторское свидетельство СССР 304584, кл. G Об F 15/34, 1969, 2.Авторское свидетельство СССР 524997, кл. G 06 F 15/36, 1974.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления средне-КВАдРАТичЕСКОгО зНАчЕНия | 1979 |

|

SU849229A1 |

| Аналого-цифровой преобразователь интегральных характеристик электрических величин | 1981 |

|

SU1035790A1 |

| Устройство для определения среднеквадратического значения | 1983 |

|

SU1130877A1 |

| Аналого-цифровой преобразователь интегральных характеристик электрических величин с мультипликативной автокоррекцией | 1984 |

|

SU1185604A1 |

| Цифровой измеритель RLC-параметров | 1986 |

|

SU1357874A1 |

| МНОГОМЕРНЫЙ СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР УСРЕДНЕННОЙ МОЩНОСТИ НЕСТАЦИОНАРНОЙ НАГРУЗКИ | 1992 |

|

RU2060542C1 |

| Устройство для раздельного управления группами вентилей преобразователя | 1983 |

|

SU1125726A1 |

| Анализатор случайных процессов | 1987 |

|

SU1474678A1 |

| Некогерентный приемник | 1988 |

|

SU1525933A1 |

| Преобразователь код-мощность | 1982 |

|

SU1070530A1 |

Авторы

Даты

1981-06-30—Публикация

1979-07-09—Подача