(54) УСТРОЙСТВО для ОБРАТНОГО ТРИГОНОМЕТРИЧЕСКОГО

ПРЕОБРАЗОВАНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Тригонометрический функциональный преобразователь | 1978 |

|

SU771683A1 |

| Стробоскопический преобразователь электри-чЕСКиХ СигНАлОВ | 1979 |

|

SU834529A1 |

| УСТРОЙСТВО ОПРЕДЕЛЕНИЯ АППАРАТНОЙ ЗАДЕРЖКИ ВЫХОДНОГО СИГНАЛА ПЕРЕДАТЧИКА | 2015 |

|

RU2581767C1 |

| Стробоскопический аналого-цифровой преобразователь | 1981 |

|

SU1023651A1 |

| Адаптивный аналого-цифровой преобразователь | 1979 |

|

SU822349A1 |

| Цифровой интегрирующий вольтметр | 1979 |

|

SU834898A1 |

| Синтезатор частот | 1980 |

|

SU978365A1 |

| СПОСОБ УПРАВЛЕНИЯ ЭЛЕКТРОПРИВОДОМ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2020724C1 |

| КАЛИБРОВОЧНОЕ УСТРОЙСТВО ДЛЯ УЛЬТРАЗВУКОВОГО РАСХОДОМЕРА | 1995 |

|

RU2082951C1 |

| УСТРОЙСТВО КОМПЕНСАЦИИ СТРУКТУРНЫХ ПОМЕХ | 2010 |

|

RU2450445C2 |

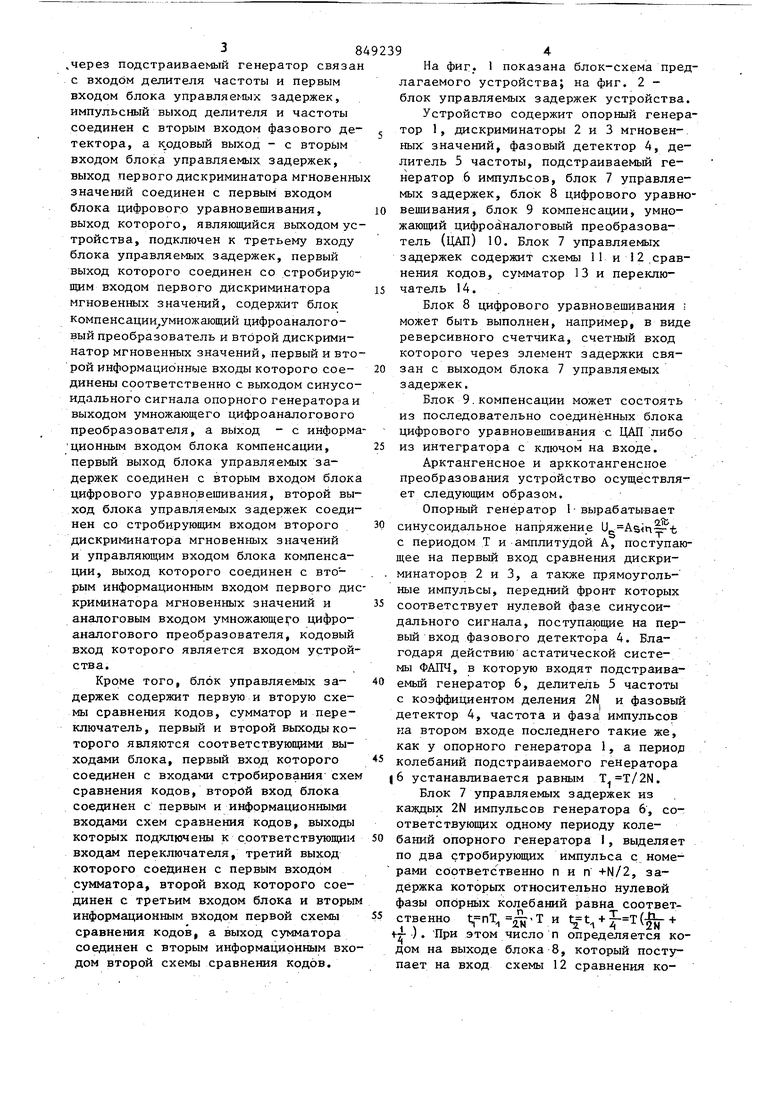

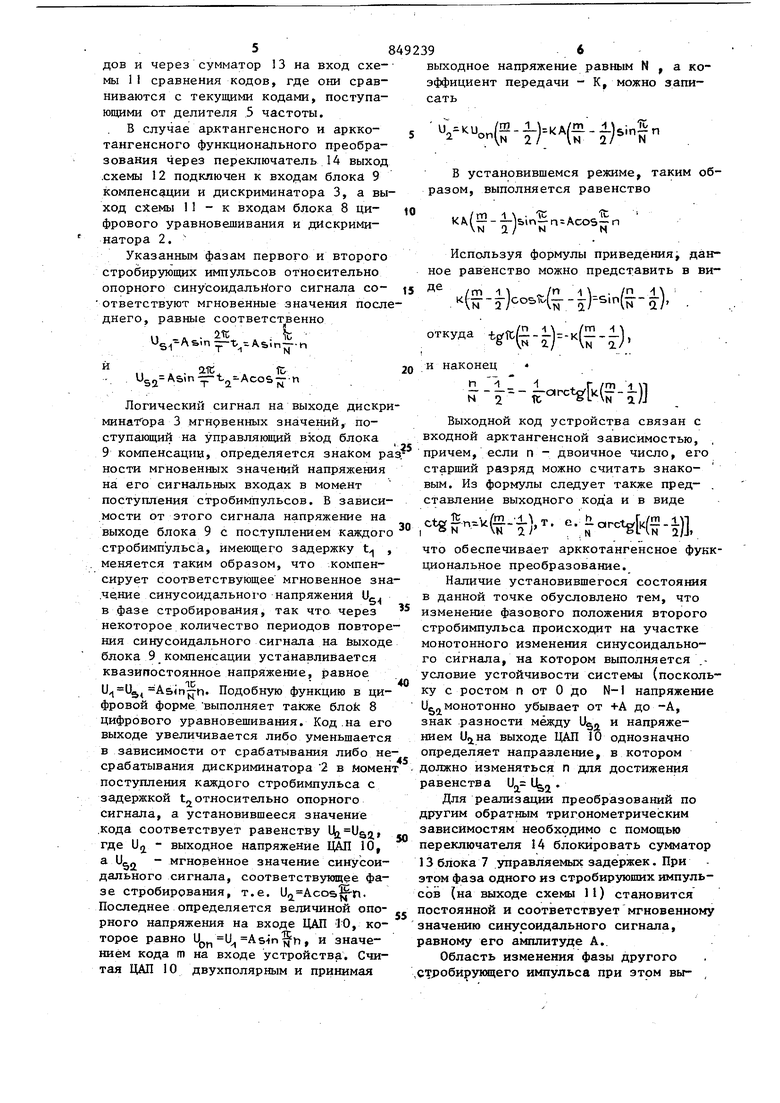

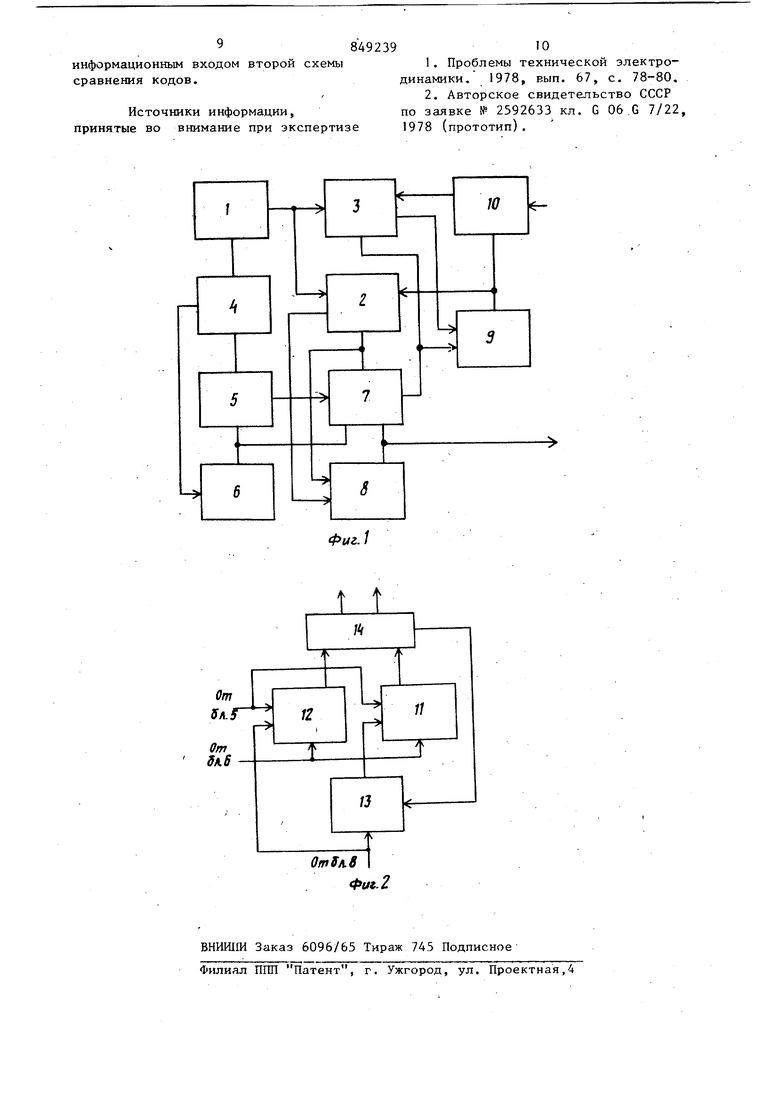

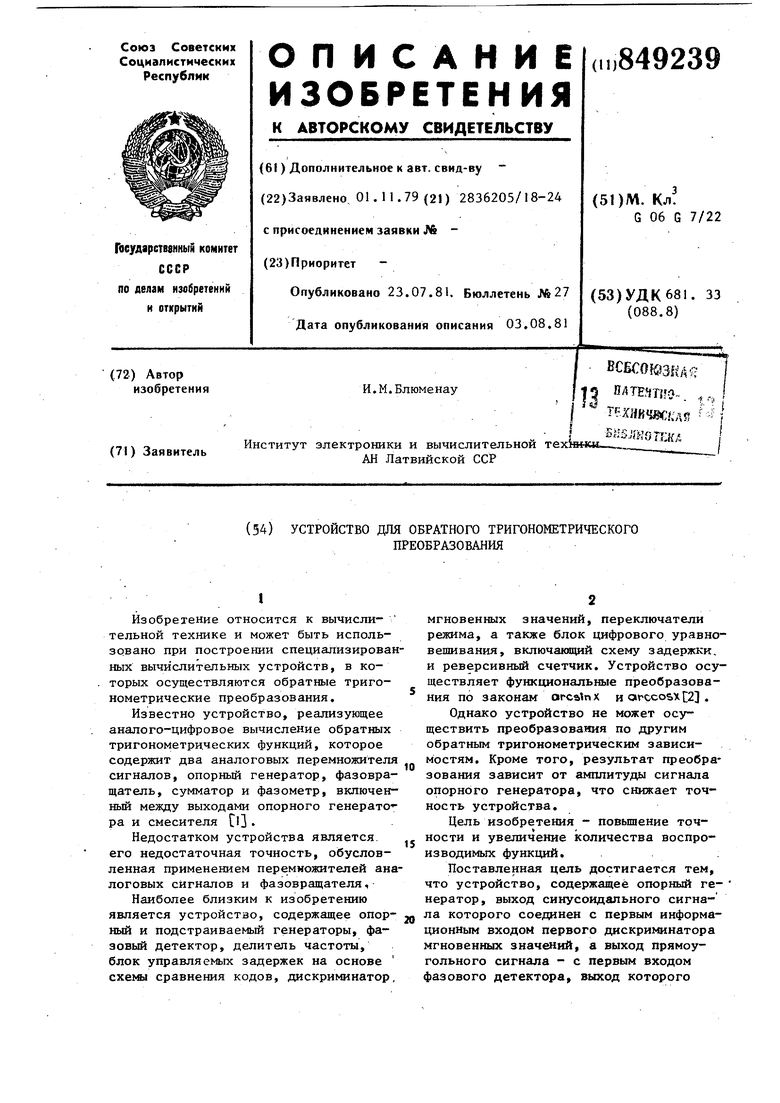

изобретение относится к вычислительной технике и может быть использовано при построении специализирован ных вычислительных устройств, в которых осуществляются обратные тригонометрические преобразования. Известно устройство, реализующее аналого-цифровое вычисление обратных тригонометрических функций, которое содержит два аналоговых перемножителя сигналов, опорный генератор, фазовращатель, сумматор и фазометр, включенный между выходами опорного генерато ра и смесителя СО. Недостатком устройства является, его недостаточная точность, обусловленная применением перемножителей ана логовых сигналов и фазовращателя, Наиболее близким к изобретению является устройство, содержащее опорный и подстраиваемый генераторы, фазовый детектор, делитель частоты, блок управляемых задержек на основе cxei« i сравнения кодов, дискриминатор мгновенных значений, переключатели режима, а также блок цифрового уравновещивания, включакидий схему задержки, и реверсивный счетчик. Устройство осуществляет функциональные преобразования по законам orcatnx и arccosx П2 . Однако устройство не может осуществить преобразования по другим обратным тригонометрическим зависимостям. Кроме того, результат преобразования зависит от амплитуды сигнала опорно го генератора, что снижает точность устройства. Цель изобретения - повьшение точности и увеличение количества воспроизводимых функций,: Поставленная цель достигается тем, что устройство, содержащее опорный генератор, выход синусоидапьного сигнала которого соединен с первым информационным входом первого дискриминатора мгновенных значений, а выход прямоугольного сигнала - с первым входом фазового детектора, выход которого 38 .через подстраиваемый генератор связа с входом делителя частоты и первым входом блока управляемых задержек, импульсный выход делителя и частоты соединен с вторым входом фазового де тектора, а к.одовый выход - с вторым входом блока управляемых задержек, выход первого дискриминатора мгновенны значений соединен с первым входом блока цифрового уравновешивания, выход которого, являющийся выходом ус тройства, подключен к третьему входу блока управляемых задержек, первый выход которого соединен со стробирующим входом первого дискриминатора мгновенных значений, содержит блок компенсации умножающий цифроаналоговый преобразователь и второй дискриминатор мгновенных значений, первый и вто рой информационные входы которого соединены соответственно с выходом синусоидального сигнала опорного генератора и выходом умножающего цифроаналогового преобразователя, а выход - с информ ционным входом блока компенсации, первый выход блока управляемых задержек соединен с вторым входом блок цифрового уравновешивания, второй вы ход блока управляемых задержек соеди нен со стробирующим входом второго дискриминатора мгновенных значений и управляющим входом блока компенсации, выход которого соединен с вторым информационным входом первого ди криминатора мгновенных значений и аналоговым входом умножающего цифроаналогового преобразователя, кодовый вход которого является входом устрой ства. Кроме того, блок управляемых задержек содержит первую и вторую схемы сравнения кодов, сумматор и переключатель, первый и второй выходы которого являются соответствующими выходами блока, первый вход которого соединен с входами стробирова1шя схе сравнения кодов, второй вход блока соединен с первым и информационными входами схем сравнения кодов, выходы которых подключены к соответствующим входам переключателя, третий выход которого соединен с первым входом сумматора, второй вход которого соединен с третьим входом блока и вторьш информационным входом первой схемы сравнения кодов, а выход сумматора соединен с вторым информационным вхо дом второй схемы сравнения кодов. На фиг. 1 показана блок-схема предлагаемого ycтpoйcтвaJ на фиг. 2 блок управляемых задержек устройства. Устройство содержит опорный генератор 1, дискриминаторы 2 и 3 мгновенных значений, фазовый детектор 4, делитель 5 частоты, подстраиваемый генератор 6 импульсов, блок 7 управляемых задержек, блок 8 цифрового уравновешивания, блок 9 компенсации, умножающий цифроаналоговый преобразователь (ЦАП) 10. Блок 7 управляемых задержек содержит схемы 11 и 12,сравнения кодов, сумматор 13 и переключатель 14.. Блок 8 цифрового уравновешивания ; может быть выполнен, например, в виде реверсивного счетчика, счетный вход которого через элемент задержки связан с выходом блока 7 управляемых задержек. Блок 9.компенсации может состоять из последовательно соединённых блока цифрового уравновешивания с ЦАП либо из интегратора с ключом на входе. Арктангенсное и арккотангенсное преобразования устройство осуществляет следующим образом. Опорный генератор 1-вырабатывает синусоидальное напряжени е U ASin t с периодом Т и амплитудой А, поступающее на первый вход сравнения дискриминаторов 2 и 3, а также прямоугольные импульсы, передний фронт которых соответствует нулевой фазе синусоидального сигнала, поступающие на первый вход фазового детектора 4. Благодаря действию астатической системы ФАПЧ, в которую входят подстраиваемый генератор 6, делитель 5 частоты с коэффициентом деления 2N и фазовый детектор 4, частота и фаза импульсов на втором входе последнего такие же, как у опорного генератора 1, а период колебаний подстраиваемого генератора 6 устанавливается равным Т.T/2N. Блок 7 управляемых задержек из каждых 2N импульсов генератора 6, соответствующих одному периоду колебаний опорного генератора 1, выделяет по два стробирующих импульса с номерами соответственно ПИП +N/2, задержка которых относительно нулевой фазы опорных колебаний равна соответственно tfnT Т и + ( + -т- ). При этом число п определяется кодом на выходе блока 8, который поступает на вход схемы 12 сравнения кодов и через сумматор 13 на вход схемы 11 сравнения кодов, где они сравниваются с текущими кодами, поступающими от делителя 5 частоты.

В случае арктангенсного и арккотангенсного функционального преобразования через переключатель 14 выход .схемы 12 подключен к входам блока 9 компенсадии и дискриминатора 3, а выход схемы 11 - к входам блока 8 цифрового уравновешивания и дискриминатора 2.

Указанным фазам первого и второго стробирующих импульсов относительно опорного синусоидальйого сигнала соответствуют мгновенные значения последнего, равные соответственно 21С. . . fc II - . и52 А51П-t,,.j,-AcoS --п Логический сигнал на выходе дискриминатора 3 мгнрвенных значений, поступающий на управляющий вход блока 9 компенсации, определяется знаком раз ности мгновенных значений напряжения на его сигнальных входах в момент поступления стробимпульсов, В зависимости от этого сигнала напряжение на выходе блока 9 с поступлением каждого стробимпульса, имеющего задержку Ц , меняется таким образом, что .компенсирует соответствующее мгновенное зна.че1ние синусоидального напряжения Ug в фазе стробирования, так что через некоторое количество периодов повторе НИН синусоидального сигнала на быходе блока 9 компенсации устанавливается квазипостоянное напряжение, равное 1C , . Подобную функцию в цифровой форме выполняет также 6nok 8 цифрового уравновешивания. Код .на его выходе увеличивается либо уменьшается в зависимости от срабатывания либо несрабатывания дискриминатора 2 в момент поступления каждого стробимпульса с задержкой t относительно опорного сигнала, а установившееся значение .кода соответствует равенству где и, - выходное напряжение ЦАП 10, а U-n - мгновенное значение синусоидального сигнала, соответствующее фазе стробирования, т.е. . Последнее определяется величиной опорного напряжения на входе ЦАП 10, которое равно U As-in n, и значениём кода m на входе устройства. Считая ДАП 10 двухполярным и принимая

выходное напряжение равным N а коэффициент передачи - К, можно записать

)(f-f)nfn

в установившемся режиме, таким образом, выполняется равенство

К(.),;.|,.д,оэ|п

Используя формулы приведенияj данное равенство можно представить в виC-т)(S-). откуда ;tg,(-l).K(-l), И наконец f л Л г /т 1 1 o,,tg.kc(---) Выходной код устройства связан с входной арктангенсной зависимостью, , причем, если п - двоичное число, его старший разряд можно считать знаковым. Из формулы следует также пред- . ставление выходного кода и в виде г.-, -F ( + IM ,tg-n l4 -;jj--,T. t.. arctgrj --|j что обеспечивает арккотангенсное функциональное преобразование. Наличие установившегося состояния в данной точке обусловлено тем, что изменение фазового положения второго стробимпульса происходит на участке монотонного изменения синусоидального сигнала, на котором выполняется .условие устойчивости системы (поскольку с ростом п от О до N-1 напряжение и,.монотонно убывает от +А до -А, знак разности между Ц и напряжением выходе ЦАП 10 однозначно определяет направление, в котором должно изменяться п для достижения равенства U,.j 14, . Для реализации преобразований по ДРУГим обратным тригонометрическим зависимостям необходимо с помощью переключателя 14 блокировать сумматор 13 блока 7 управляемых задержек. При этом фаза одного из стробируюших импульсов (на выходе схемы И) становится постоянной и соответствует мгновенному значению синусоидального сигнала, равному его амплитуде А., Область изменения фазы другого стробирующего импульса при этом вы- , бирается такой, что в ней обеспе чивается МОНОТОННОСТЬ используемого участка синусоидального напряжения. Например, в случае, когда на блок 9 компенсации поступают импульсы с задержкой (2 4Ijj з блок 8 цифро вого уравновешивания - с задержкой г/Г напряжение на выходе блока 9 рав но U Asin1t(, а напряжение на выходе 10 равно А. (при ). При это п -1 Г г 1 т I .. N u° l VTr-T/J Для реализации преобразования по арксекансной (арккосекансной) зависимости достаточно с помощью переключателя 14 скоммутировать выходы блока 7 управляемых задержек так, что задержка стробимпульсов, поступа ющих на блок 9 компенсации, постоянна и равна Т/4, а стробимпульсов, по ступающих на блок 8, равна IT/ При зтом, аналогично предьщущему, в установившемся реткиме 1с . . V . , /m it откуда - -jcos-п .) Аналогично реализуются также acxsm и arccoseo - функциональны преобразования. Изобретение позволяет повысить то ность реализуемых функциональных пре образований: п, обеспечить расширение функциональных возможностей путем реализации всех обратных тригоно метрических функций. При этом преобр зователь содержит минимальное количество прецизионных аналоговых узлов что повышает надежность его работы и допускает выполнение на стандартны интеграторных микросхемах. Формула изобретения Устройство для обратного триго нометрического преобразования, содер жащее опорный генератор, выход инусоидального Сигнала которого соедине с первым информационным входом первого дискриминатора мгновенных значений, а выход прямоугольного сигнала - с первым входом фазового детект ра, выход которого через подстраивае мый генератор импульсов связан с вхо дом делителя частоты и первым входом блока управляемых задержек, импульсный выход делителя частоты соединен с вторым входом фазового детектора, а кодовый выход - с вторым входом блока управляемых задержек, выход первого дискриминатора мгновенных значений соединен с первым входом блока цифрового уравновешивания, выход которого, являющийся выходом устройства, подключен к третьему входу блока управляемых задержек, первый выход которого соединен со стробирующим входом первого дискриминатора мгновенных значений, отличающееся тем, что, с целью повышения точности и расширения класса воспроизводимых функций, устройство содержит блок компенсации, умножающий цифроаналоговый преобразователь и второй дискриминатор мгновенных значений, первьш и второй информационные входы которого соединены соответственно с выходом синусоидального сигнала опорного генератора и выходом умножающего цифроаналогово- го преобразователя, а выход - с информационным входом блока компенсации, первый выход блока управляемых задержек соединен с вторым входом блока цифрового уравновешивания, второй выход блока управляемых задержек соединен со стробирукщим входом второго дискриминатора мгновенных значений и управляющим входом блока компенсации, выход которого соединен со вторым информационным входом первого дискриминатора мгновенных значений и аналоговым входом умножающего цифроаналогового преобразователя, кодовый вход которого является входом .устройства. 2. Устройство по п. 1, о т л и ч аю щ е е с я тем, что блок управляемых задержек содержит первую и вторую сравнения кодов, сумматор и переключатель, первый и второй выходы которого являются соответствующими выходами блока, первый вход которого соединен с входами стробирования схем сравнения кодов, второй вход блока соединен с первыми информационными ; входами схем сравнения кодов, выходы которых подключены к соответствующим входам переключателя, третий выход которого соединен с первым входом сумматора,, вто-. рой вход которого соединен с третьим входом блока и вторьм информационным входом первой схемы сравнения кодов, а выход сумматора соединен с вторым

849239

информационным входом второй схемы сравнения кодов.

Источники информации, принятые во внимание при экспертизе

10

1,Проблемы технической электродинамики, 1978, Еып. 67, с, 78-80.

Авторы

Даты

1981-07-23—Публикация

1979-11-01—Подача