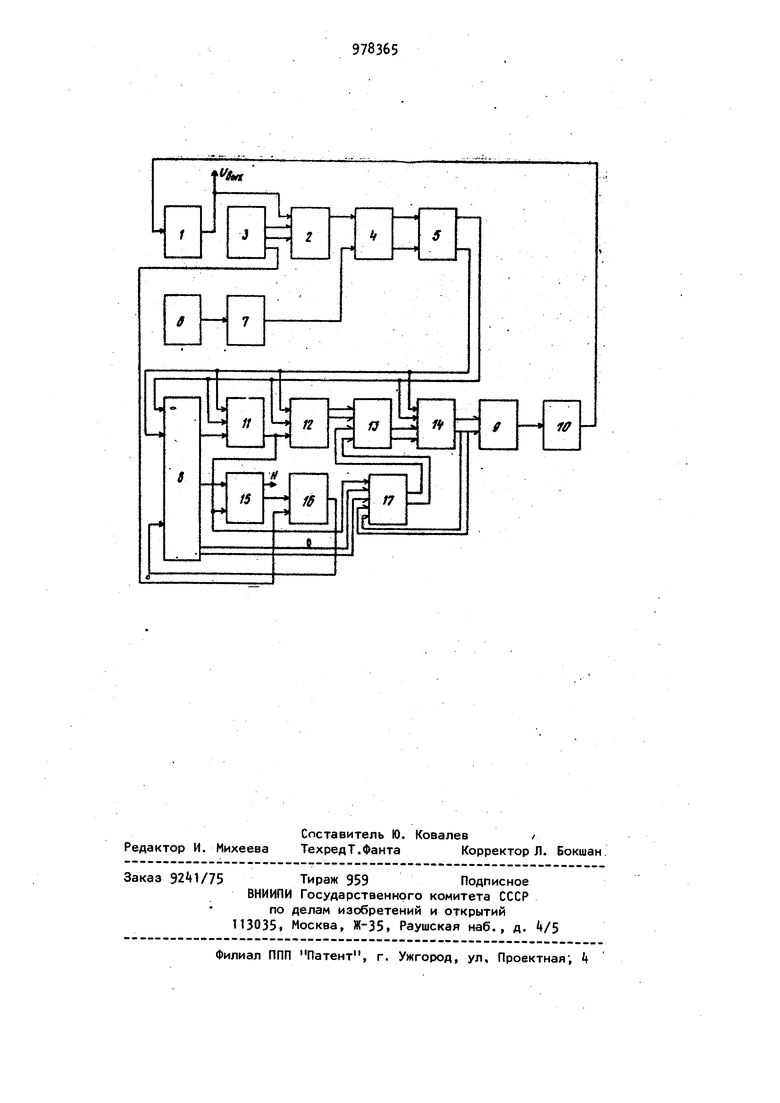

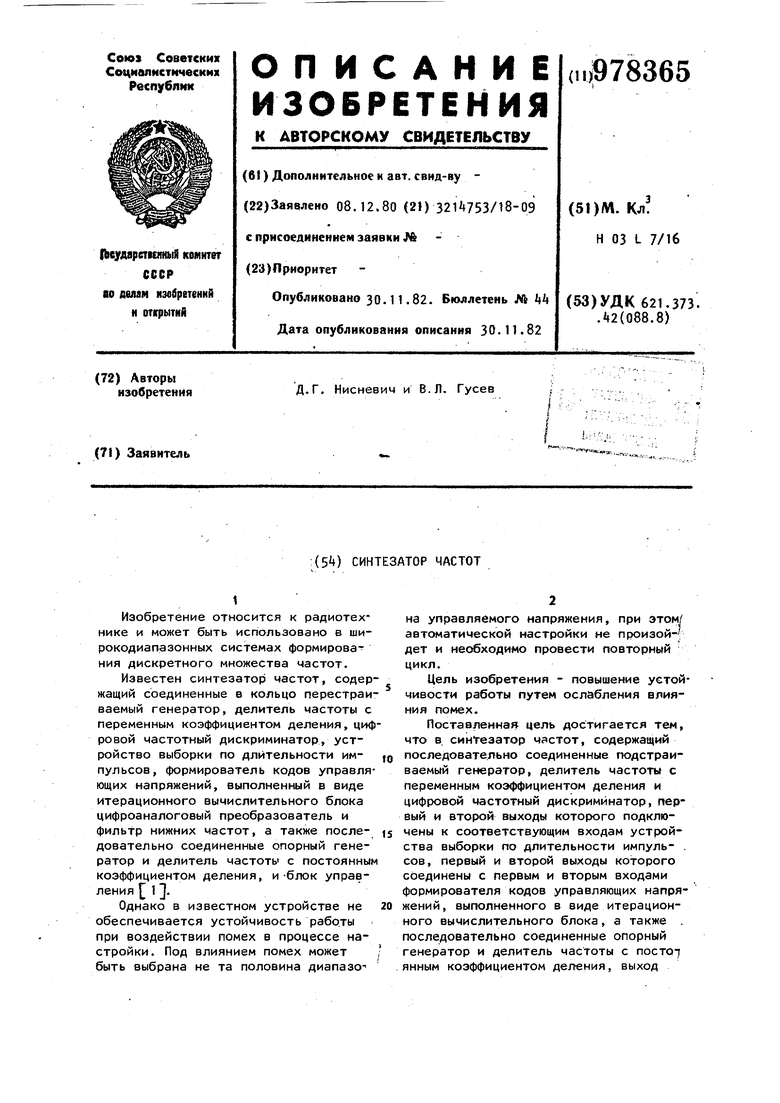

(Sk) СИНТЕЗАТОР ЧАСТОТ Изобретение относится к радиотехнике и может быть использовано в широкодиапазонных системах формирования дискретного множества частот. Известен синтезатор частот, содер жащий соединенные в кольцо перестраи ваемый генератор, делитель частоты с переменным коэффициентом деления, циф ровой частотный дискриминатор, устройство выборки по длительности импульсов, формирователь кодов управля ющих напряжений, выполненный в виде итерационного вычислительного блока цифроаналоговый преобразователь и фильтр нижних частот, а также последовательно соединенные опорный генератор и делитель частоты с постоянны коэффициентом деления, и-блок управления 1 . Однако в известном устройстве не обеспечивается устойчивость работы при воздействии помех в процессе настройки. Под влиянием помех может быть выбрана не та половина диапазона управляемого напряжения, при этом/ автоматической настройки не произойдет и необходимо провести повторный цикл. Цель изобретения - повышение устойчивости работы путем ослабления влияния помех. Поставленная цель достигается тем, что в. синтезатор частот, содержащий последовательно соединенные подстраиваемый генератор, делитель частоты с переменным коэффициентом деления и цифровой частотный дискриминатор, первый и второй выходы которого подключены к соответствующим входам устройства выборки по длительности импуль- . сов, первый и второй выходы которого соединены с первым и вторым входами формирователя кодов управляющих напряжений, выполненного в виде итерационного вычислительного блока, а также . последовательно соединенные опорный генератор и делитель частоты с посто янным коэффициентом деления, выход которого подключен к другому входу цифрового частотного дискриминатора, последовательно соединенные цифроаналоговый преобразователь и фильтр нижних частот, выход которого подключен к управляющему входу подстраиваемого генератора, и блок управления, первый выход которого соединен с управляющим входом делителя частоты с переменным коэф°фициентом деления, введены последовательно соединенные индикатор настройки и блок памяти, последовательно соединенные сумматор, регистр-и коммутатор и последовательно соединен ные блок защиты от ложных сигналов и элемент ИЛИ, второй вход которого соединен с другим входом блока управления , а выход элемента ИЛИ подключен к стартовому входу формирователя кода управляющих напряжений, первый и второй выходы которого соединены соответ ственно с цикловым входом блока защиты от ложных сигналов и режимным входом индикатора настройки, первые и вторые входы которого объединены с вторым и третьим входами блока памяти и вторым и третьим входами регист°ра и подключены к первому и второму выходам устройства выборки по длитель ности импульсов, входы первого и BTOрого операндов сумматора подключены соответственно к выходу блока памяти и коммутатора, второй вход блока защиты от лсшных сигналов объединен с управляющим входом коммутатора и подключен к выходу индикатора настройки, поразрядные выходы регистра соединены с поразрядными входами цифроаналогово го преобразователя, а информационные выходы формирователя кодов управляющих напряжений соединены с второй группой входов коммутатора. На чертеже изображена структурная электрическая схема предлагаемого синтезатора частот. Синтезатор частот содержит подстра иваемый генератор 1, делитель 2 часто ты с переменным коэффициентом деления блок J управления, цифровой частотный дискриминатор k, устройство 5 выборки по длительности импульсов, опорный генератор 6, делитель 7 частоты с постоянным коэффициентом деления, формирователь 8 кодов управляющих напряжений, цифроаналоговый преобразоватёль 9, фильтр 10 нижних частот, инди катор 11 настройки, блок 12 памяти, сумматор 13, регистр И, блок 15 защиты от ложных сигналов, элемент ИЛИ 16 и коммутатор 17 Устройство работает следующим образом. На управляющий вход подстраиваемого генератора 1 с выхода цифроаналогового преобразователя 9 подается управляющее напряжение, величина которого пропорциональна коду с выхода регистра Н. Процесс настройки осуществляется с помощью ряда последовательных итерационных циклов. Индикатор 11 настройки по сигналам с устройства 5 выборки и формирователя 8 кодов вырабатывает сигналы, индицирующие нахождение системы а режиме дихотомического поиска или окончания его. Эти сигналы запоминаются на все время этапа настройки. Алгоритм работы индикатора описывается следующими булевыми выражениями: d (а V Ь)-с; 3 с V а-Ь, где а, t) - сигналы с выхода устройстства 5 выборки, соответствующее положительной и отрицательной расстройке, по частоте; с - сигнала начала поиска с формирователя 8 кодов; d - сигнал В режиме поиска система настроилась ; d - сигнал Идет поиск - система не настроилась. Индикатор 11 настройки может быть реализован с помощью комбинационной логической схемы и элементов памяти. В блок 12 памяти записаны три числа О, -f 1, -1. В Течение процесса поиска с выхода блока 12 памяти на входы первого операнда сумматора 13 подается О и коммутатор 17 соединяет информационные выходы формирователя 8 кодов с входами второго операнда сумматора 13. После оконч:ания поиска по сигналу индикатора 11 настройки синтезатор частот переходит в режим автоматической подстройки частоты, коммутатор 17 переключается и соеди яет выходы регистра И с входами второго операнда сумматора 13. При этом если на выходе устройства 5 выборки появляется сигнал о частотной расстройке, то в соответствии со знаком расстройки блок памяти выдает на сумматор 13 код 4-1 или -1. Вследствие этого напряжение на выходе цифроаналогового преобразователя 9 увеличится или уменьшится на один дискрет. компенсируя расстройку. Полоса удержания описанной системы автоматической подстройки равна всему рабочему г диапазону подстраиваемого генератора 1 . Блок 15 защиты служит для автоматического повторного запуска системы в случае сбоя. На вход блока 15 защиты поступают сигналы с выхода индикатора 11 настройки и циклового выхода формирователя 8 кодов. Если в течение К циклов с выхода индикатора 11 настройки придет сигнал, что требуемая частота не выставлена, то по сигналу с выхода блока 15 защиты через элeмeнJ i ИЛИ 16 осуществляют повторной запуск формирователя 8 кодов. Блок 15 защиты может быть реализован с помощью комбинационной логической схемы, элементов памяти и пересчетного устройства. Формирователь 8 кодов может запускаться также по сигналу с блока 3 управления через элемент ИЛИ 16.Если после заданного количества повторных запусков синтезатор частот не настраивается, на дополнительном выходе блока 15 защиты вырабатывается сигнал Неисправность. Таким образом, предлагаемое устрой ство обладает повышенной устойчивостью к воздействию помех в процессе настройки. Формула изобретения Синтезатор частот, содержащий последовательно соединенные подстраиваемый генератор, делитель частоты с переменным коэффициентом деления и цифровой частотный дискриминатор, пер вый и второй выходы которого подключены к соответствующим входам устройства выборки по длительности имульсов первый и второй выходы которого соеди нены с первым и вторым входами формирователя кодов управляющих напряжений выполненного в виде итерационного вычислительного блока, а также последовательно соединенные опорный генератор и делитель частоты с постоянным коэффициентом деления, выход которого подключен .к другому входу цифрового частотного дискриминатора, последовательно соединенные цифроаналоговый преобразователь и фильтр нижних частот, выход которого подключен к управляющему входу подстраиваемого генератора, блок управления, первый выход которого соединен с управляющим вхо- дом делителя частоты с переменным коэффициентом деления,отличающий с я тем, что, с целью повышения устойчивости работы путем ослабления влияния помех, в него введены последовательно соединенные индикатор настройки и блок памяти, последовательно соединенные сумматор, регистр и коммутатор и последовательно соединенные блок защиты от ложных сигналов и элемент ИЛИ, второй вход которого соединен с другим входом блока управления, а выход элемента ИЛИ подключен к стартовому входу формирователя кода управляющих напряжений, первый и второй выходы которого соединены соответственно с цикловым входом блока защиты от ложных сигналов и режимным входом индикатора настройки, первые и вторые входы которого объединены с вторыми и третьими входами блока памяти и с вторыми и третьими входами регистра и подключены к первому и второму выходам устройства выборки по длительности импульЪов, входы первого и второго операндов сумматора подключены соответственно к выходу блока памяти и коммутатора, второй вход блока защиты от ложных сигналов объединен с управляющим входом коммутатора и подключен к выход: индикатора настройки „ поразрядные выходы регистра соединены с поразрядными входами цифроаналогового преобразователя, а информационные выходы формирователя кодов управляющих напряжений соединены с второй группой входов коммутатора. Исто««1ики информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 657575, кл. Н 03 L 7/0о, 1976 (прототип) .,

15

16 Т ns /7

| название | год | авторы | номер документа |

|---|---|---|---|

| Синтезатор частот | 1980 |

|

SU985947A1 |

| Синтезатор частоты с частотной модуляцией | 1986 |

|

SU1345343A1 |

| СПОСОБ ОПРЕДЕЛЕНИЯ МЕСТА ПОВРЕЖДЕНИЯ ЭЛЕКТРИЧЕСКОГО КАБЕЛЯ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2001 |

|

RU2190234C1 |

| УСТРОЙСТВО ДЛЯ ВЫДЕЛЕНИЯ ТАКТОВОГО КОЛЕБАНИЯ | 1991 |

|

RU2007881C1 |

| УСТРОЙСТВО КОМПЕНСАЦИИ СТРУКТУРНЫХ ПОМЕХ | 2013 |

|

RU2534221C1 |

| Синтезатор частот | 1986 |

|

SU1376242A1 |

| Синтезатор частот | 1987 |

|

SU1543545A1 |

| Цифровой синтезатор частоты с частотной модуляцией | 1989 |

|

SU1771068A1 |

| Устройство для контроля видеосигнала | 1982 |

|

SU1069190A1 |

| КОРРЕЛЯЦИОННЫЙ ПРИЕМНИК ШУМОПОДОБНЫХ СИГНАЛОВ С МИНИМАЛЬНОЙ ЧАСТОТНОЙ МОДУЛЯЦИЕЙ | 2014 |

|

RU2548010C1 |

Авторы

Даты

1982-11-30—Публикация

1980-12-08—Подача