(54) АНАЛИЗАТОР СПЕКТРА

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой анализатор спектра | 1979 |

|

SU798615A1 |

| Способ анализа спектра сигналов и устройство для его осуществления | 1988 |

|

SU1573432A1 |

| Цифровой анализатор спектра | 1985 |

|

SU1256044A1 |

| Анализатор спектра случайныхпРОцЕССОВ | 1979 |

|

SU838600A1 |

| Частотный анализатор | 1990 |

|

SU1798630A1 |

| Многоканальное измерительное устройство для цифровой фильтрации | 1985 |

|

SU1252919A1 |

| Цифровой Фурье-преобразователь | 1982 |

|

SU1043663A1 |

| Устройство для вычисления спектра сигналов | 1989 |

|

SU1667102A1 |

| Цифровой анализатор спектра в ортогональном базисе | 1983 |

|

SU1124326A1 |

| Устройство для контроля и управления технологическим процессом тренировки и испытаний фотоэлектронных умножителей | 1986 |

|

SU1325516A1 |

1

Изобретение относится к радиоизмерительной технике и может быть использовано для измерения спектра, взаимного спектра и коэффициента когерентности.

Известны анализаторы спектра с циф ровой фильтрацией сигнала, содержащие входной аналого-цифровой преобразователь, блоки памяти, арифметический блок, вычислители и блок ввода весовой функции 1..

Однако точность измерений таких анализаторов недостаточна.

Наиболее близким по технической сущности к предлагаемому является анализатор, содержащий входной преобразователь, умножитель, сумматоры, делители, блок сравнения и блоки памяти 2.

Недостатком известного анализатора являются большие погрешности измерений, вызванные низким быстродействием.

Цель изобретения - повышение точности измерений.

Указанная цель достигается тем, что в анализатор спектра, содержащий последовательно соединенные входной блок, фильтр верхних частот, аналоговый коммутатор, аналоговый блок

памяти, аналого-цифровой преобразователь, преобразователь кода и первый блок памяти, подключенный ко входу второго блока памяти и ко входу умножителя, второй вход которого подключен к выходу устройства ввода весовых коэффициентов, а также два сумматора, два делителя, два вычислителя, блок логарифмирования, блок

10 управления и индикатор, причем выход преобразователя кода подключен одновременно ко второму входу второго блока памяти и ко входу блока Сравнения, второй вход которого соединен

15 с выходом переключателя кодов, дополнительно введены три блока памяти и цифровой коммутатор, вход которого подключен к выходу умножителя, а выход соединен с последовательно сое20диненными первым сумматором, первым делителем, первым вычислителем, вторым сумматором, вторым делителем, третьим блоком памяти и индикатором, при этом третий блок памяти связан

25 с блоком логарифмирования и вторым вычислителем, второй сумматор связан с четвертым блоком памяти, ( выход первого сумматора подключен ко входу пятого блока памяти, выход которого соединен со вторым входом цифрового

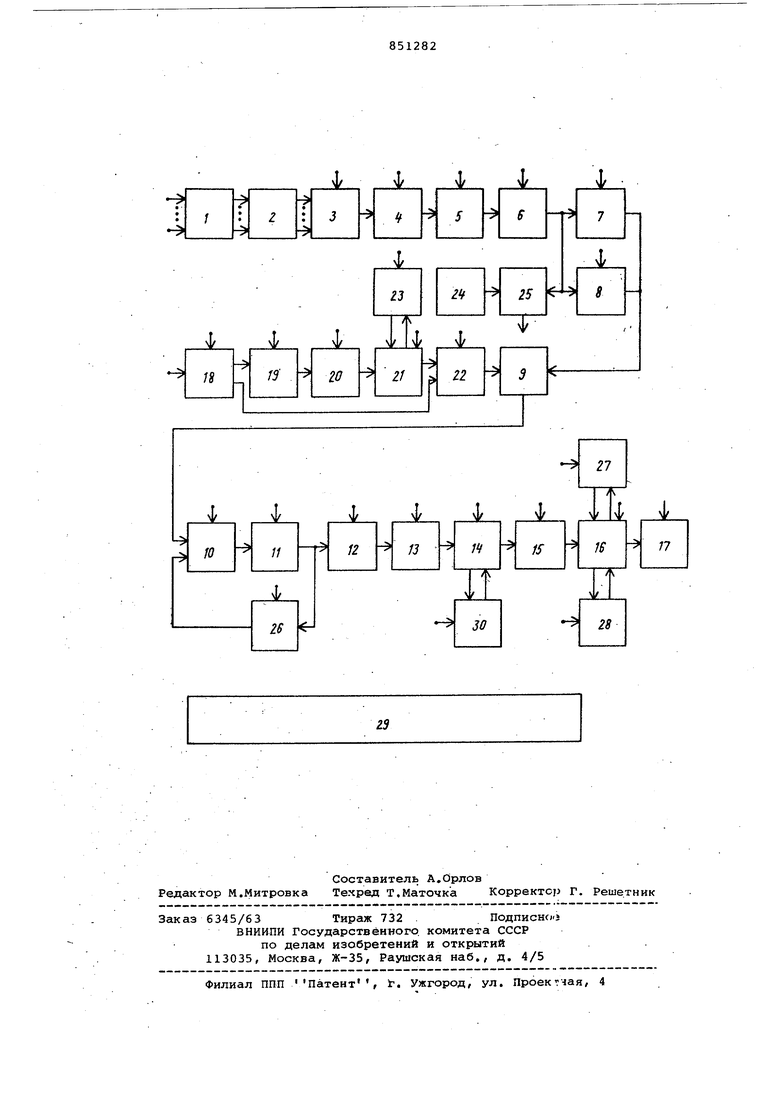

3Q KOHMyf fOj. При этом устройство ввода вессхэыз коэффициентов выполнено в виде последовательно соединенных блока ввода весовой функции, блока памп Ч/ еобразователя код-частота, адресног блока и второго блока памя1ти, второй вход которого подключен ко второму выходу блока ввода, причем адресный блок связан с третьим блоком памяти. На чертеже представлена структурная схема предлагаемого анализатора. Анализатор состоит из входного блока 1, фильтра 2 верхних частот, ана логового коммутатора 3, аналогового блока 4 памяти, аналого-цифрового преобразователя 5, преобразователя б кода, блоков 7 и 8 памяти, умножител 9, цифрового коммутатора Ю, первого сумматора 11, первого делителя 12, первого вычислители 13, второго сумматора 14, второго делителя 15, блока 16 памяти, индикатора 17, устройства 18 ввода весовых коэффициентов, блока 19 памяти, преобразовател 20 код-частота, адресного блока 21, блоков 22 и 23 памяти, переключателя 24 кодов, блока 25 сравнения, блока 26 памяти, блока 27 логарифмирования второго вычислителя 28, блока 29 управления и блока 30 памяти. Анализатор работает следующим образом. Входные сигналы поступают на вход ной блок 1, имеющий требуемые входно сопротивление и коэффициент усиления по каждому из каналов. Фильтр 2 верх них, частот отфильтровывает гармоники входного сигнала, частота которых больше максимальной. Далее сигналы поступают на вход коммутатора 3, который последовательно через, равные интервалы времени опрашивает все каналы/ и мгновенное значение в момент опроса запоминается аналоговым блоко 4 памяти и хранится в течение времен преобразования аналого-цифрового преоб азователя 5, Аналого-цифровой преобразователь 5 преобразует мгновенные значения аналогового сигнала в последовательный код, который затем преобразуется преобразователем б кода в параллельный код. Выходной код преобразователя 6 кода, соответствующий определенному мгновенному значению входного сигнал в п-ом канале, сравнивается в блоке 25 сравнения с предварительно набран ным на переключателе 24 кодом уровня запуска. Если мгновен«ое значение входного сигнала превышает заданный уровень,,на выходе блока 25 сравнения появляется управляющий сигнал, запускающий анализатор. При этом выходной код преобразователя 6 кода поступает на блоки 7 и 8 памяти,которые работгиот попеременно в режиме записи и в режиме считы;вания. ДПя разложения входных сигнгшов на.ортогональные базисные составляющие в анализаторе применена цифроваяфильтрация сигнала. Для этого предварительно в блок 22 памяти импульсной переходной характеристики фильтра вводят через устройство 18 ввода функцию, в базисе которой прош::ходит разложение сигнала. Частоты, по которым необходимо произвести разложение сигнала, заносят в блок 19 памяти кодов час-, тот с помощью устройства 18 ввода. Анализ сигнала происходит последовательно во времени по всем частотам, хранящимся в блоке 19 памяти. Изменение фазы базисной функции осуществляют путем изменения начального адреса считывания. Изменение частоты базисной функции, хранящейся в блоке 22 памяти, осуществляют изменением частоты опроса ячеек этого запоминающего блока, т.е. тактовой частоты адресного блока 21.- Для этого из блока 19 извлекают код очередной частоты, преобразуют в преобразователе 20 код-частота этот код в. частоту импульсов, поступающих на адресный блок 21. Мгновенные значения входного сигнала, записанные в блоках 7 и В, считывают последовательно через время Т с ячеек соответствующего канала и подают на умножитель 9. Синхронно, через время Т считывают с блока 22 значения базисной функции по адресу, определяемому адресным блоком 21,к подают на второй вход умножителя 9. Коды с выхода умножителя 9 передают через цифровой, коммутатор 10 и накапливают в первом накапливающем сумматоре 11, Так как интервал времени , через который изменяется адрес в блоках 7 и 8, равен TO, интервал времени, через который изменяется адрес в блоке 22 памяти, переменный и определяется частотой/ на которой идет анализ. Кроме того, если объем выборки сигнала не равен количеству ординат базисной функции, то необходимо по окончании анализа по данной выборке по каждой частоте и переходе к анализу по следующей выборке по каждой частоте запомнить накопленное значение по данной выборке по каждому каналу и каждой частоте и адрес ординаты. Время первого усреднения определяется произведением периода считывания дискретных значений из блока 22 на число дискрет, записанных в этом блоке, т.е. - коэффициент сжатия инфор« мацйи блоками 7 и 8; - частота считывания информации ; эоп частота записи информации. При этом с увеличением частоты исследуемых гармонических составляющих пропорционально растет и уменьшается интервал усреднения Т . Этим дости1;:ается повышение быстродействия за счет уменьшения до минимально необходимого значения Т для.каждой частоты. Вследствие этого уменьшается динамическая погрешность измерения, вызванная ограниченным временем существования периодических составляющих во входном сигнале. Так, например, если в блок 22. памяти импульсной переходной характеристики занести дискретные значения синусоидальной составляющей, умноженные на гауссово Сглаживающее окно, то для всех анализируемых частот можно достичь минимальное значение произведения полосы пропускания на время изме рения (Тус), которое определяется соотношением неопределенности. В час ности, для 1/3-октавной полосы анализатора и динамического диапазона 40 дБ достаточно шесть периодов пери одических составляющих во входном сигнале для измерения с достаточно малой погрешностью, для 1/6-октавной полосы - двенадцать периодов и т.д. После окончания времени первого усреднения на данной частоте накопленная сумма произведений из первого сумматора 11 поступает через делитель 12 в вычислитель 13. В делителе 12 производится деление накопленной суммы на значение Ту. Так как различные для каждой частоты и изменяются в зависимости от информации, записанной в блоке 19, то для большинства анализируемых частот , оказывается некратным длительности записи информации в бло ках 7 и 8, а No(fci °°TBeTCTBeHHO некратно длительности считывания. В это случае при считывании последней ячей ки блоков 7 или 8 при анализе на час тоте fj.- из блока 22 памяти считывается непоследняя ячейка. Поэтому для продолжения усреднения по тому же интервалу на той же частоте запоминается адрес ячейки блока 22 памяти импульсной переходной характеристики в блоке 23 памяти адреса остатков, а накопленная сумма произведеикй в сум маторе 11 запоминается в блоке 26 памяти остатков. После этого производится анализ на следующей частоте. После окончания ангшиза информации по всем частотам и каналам из блоков памяти (например 7 начинается ангшиз информации, записанной в другой блок памяти (например 8). При этом в начале анализа на частоте f из блока 23 памяти адреса остатков в адресный блок 21 переписывается записанный там адрес ячейки блока 22 памяти, на котором заканчивается анализ при считывании из первого блока памяти (например 7), а в сум-; матор 11 переписывается из блока 26 Памяти остатков накопленная ранее Ьумма произведений. В первом вычислителе 13 вычисляется модуль и фаза спектра входных сигкалов, усредненных на участках Для дополнительного уменьшения погрешиостеЛ из-за флюктуации измеряемых спектральных характеристик исследуемого сигнала в анализаторе производят второе усреднение измеряемых характеристик по времени или аисамблю. Это усреднение спектральных характеристик производят путем накопления о втором сумматоре 14 с последующим хранением частично накопленных сумм в блоке 30 памяти.Число циклов второго усреднения задается блоком 29 управления.После окончания второго усреднения информация передается в блок 16 памяти через второй делитель 15, в котором осуществляется деление на число циклов второго усреднения. Для вычисления коэффициента когерентности двух сигналов с блока 16 памяти считывают усредненные оцеНки и передают их в вычислитель 28, который вычисляет коэффициент когерентности сигналов. Вычисленные значения коэффициента когерентности педают в блок 16 памяти и запоминают. Для представления спектральных характеристик в логарифмическом масштабе их считывают из блока 16 памяти в блок 27 логарифмирования, где преобразуют в логарифмический код и передают обратно в блок 16 памяти. Для отображения каждой измеренной характеристики в линейном или логарифмическом масштабе производится считывание с соответствующих ячеек блока 16 памяти и индицируется результат, на индикаторе 17. Представление результатов на экране индикатора 17 производится в координатах измеряемая спектральная, характеристика - частота - время для каждого кангипа, т.е. для каждого входного сигнала, а также в координатах измеряемая спектральная характеристика - частота-каналы для всех кангшов. Таким образом, предлагаемый анализатор позволяет повысить быстродействие при измерении спектра за счет уменьшения и регулировки времени усреднения. Для каждой исследуемой частотной составляющей длительность первого усреднения составляет минимально необходимое время/ равное целому числу периодов этой исследуемой частотной составляющей. Число периодов, укладывающихся в интервал усреднения, определяется необходимой полосой анализа. Повыение быстродействия позволяет повыить точность за счет- уменьшения цииамических погрешностей при измеении сигналов, имеющих периодические составляющие ограниченной длительности. Предлагаемый анализатор позволяет также измерять взаимный спект и коэффициент когерентности. Кроме того извне импульсно-переходно характеристики избирательного фильтр делает возможным производить иэмерения спектра сигналов при различных а не только гармонических базисных функциях, на которые производится разложение, что обеспечивает возможность измерения сечений ipyxMepHqro преобразования Фурье. Формула изобретения 1. Анализатор спектра, содержащий последовательно соединенные входной блок, фильтр верхних частот, аналоговый коммутатор, аналоговый блок па мяти,аналого-цифровой преобразовател преобразователь кода и первый блок памяти, подключенный ко входу второго блока памяти и ко входу умножител вт.орой вход которого подключен к выходу устройства ввода весовых коэффи циентов, а также два сумматора, два делителя, два вычислителя, блок логорифмирования, блок управления и ин;1,икатор, причем выход преобразователя кода подключен одновременно ко второму входу второго блока памяти и ко входу блока сравнения, второй вход которого соединен с выходом переключателя кодов, о т л и ч а ющ и и с я тем, что, с целью повышения точности измерений, в него дополнительно введены три блока памяти и цифровой коммутатор, вход которого подключен к выходу умножителя, а выход соединен с последовательно соединенными первым сумматором, первым делителем, первым вычислителем, вторым сумматором, вторым делителем, третьим блоком памяти и индикатором, при этом третий блок памяти связан с блоком логарифмирования и вторым вычислителем, второй сумматор связан с четвертым блоком памяти/ а выход первого сумматора подключен ко входу пятого блока памяти, выход которого соединен со вторым входом цифрового коммутатора. 2. Анализатор по п. 1, отличающийся тем, что устройство ввода весовых коэффициентов выполнено в виде последовательно соединенных блока ввода весовой функции, блока памяти, преобразователя код-частота, адресного блока и второго блока памяти, второй вход которого подключен ко второму выходу блока ввода, при этом адресный блок связан с третьим блоком памяти. Источники информацииf принятые во внимание при экспертизе 1.Мизин И.А;, Матвеев А,А. Цифровые фильтры. М. , 1979, с, 101,1Я-5. 2.Патент Великобритании W 1494476, 1977.

г

iL

Авторы

Даты

1981-07-30—Публикация

1979-10-29—Подача