1

изобретение относится к вычислительной технике и может быть использовано в вычислительных системах коллективного использования.

Известно многоканальное устройство для управления очередностью обращения к общему потребителю, содержащее регистр, триггер, элементы ИЛИ, генератор импульсов 1J.

Недостаток такого устройства заключается в низкой производительности .

Наиболее близким по технической сущности и достигаемому результату к предлагаемому является устройство переменного приоритета, содержгицее регистр, группу элементов И, коммутатор, блок управления, блок памяти 2.

Однако это устройство обладает низкой пропускной способностью.

Цель изобретения - повышение производительности.

Поставленная цель достигается тем, что в устройство для управления очередностью обслуживания запросов, содержгицее регистр, группу элементов И, распределитель управляющих сигналов, коммутатор, блок памяти, причем группа информационных входов

. регистра является группой информационных входов устройства, разрядные выходы регистра соединены с первыми входами соответствующих

5 элементов И группы, группа выходов блока памяти соединена с первой группой входов коммутатора, первый выход распределителя управляющих сигналов соединен с входом коммутатора,

10 второй выход распределителя управляющих сигналов соединен с входом блока памяти, введены генератор импульсов, шифратор, :.ёшифратор,два элемента ИЛИ, счетчи, блок раздеV5 ления сигналов, причем второй вход каждого элемента И группы соединен с соответствующим выходом генератора импульсов, третий вход каждого элемента И группы соединен с третьим выходом распределителя управляющих сигналов, выходы элементов И группы соединены с группой входов шифратора, группа выходов шифратора соединена со второй группой

25 входов коммутатора, первая группа выходов коммутатора соединена с груп;7ой входов дешифратора, вторая группа выходов коммутатора соединена с группой входов блока памяти,

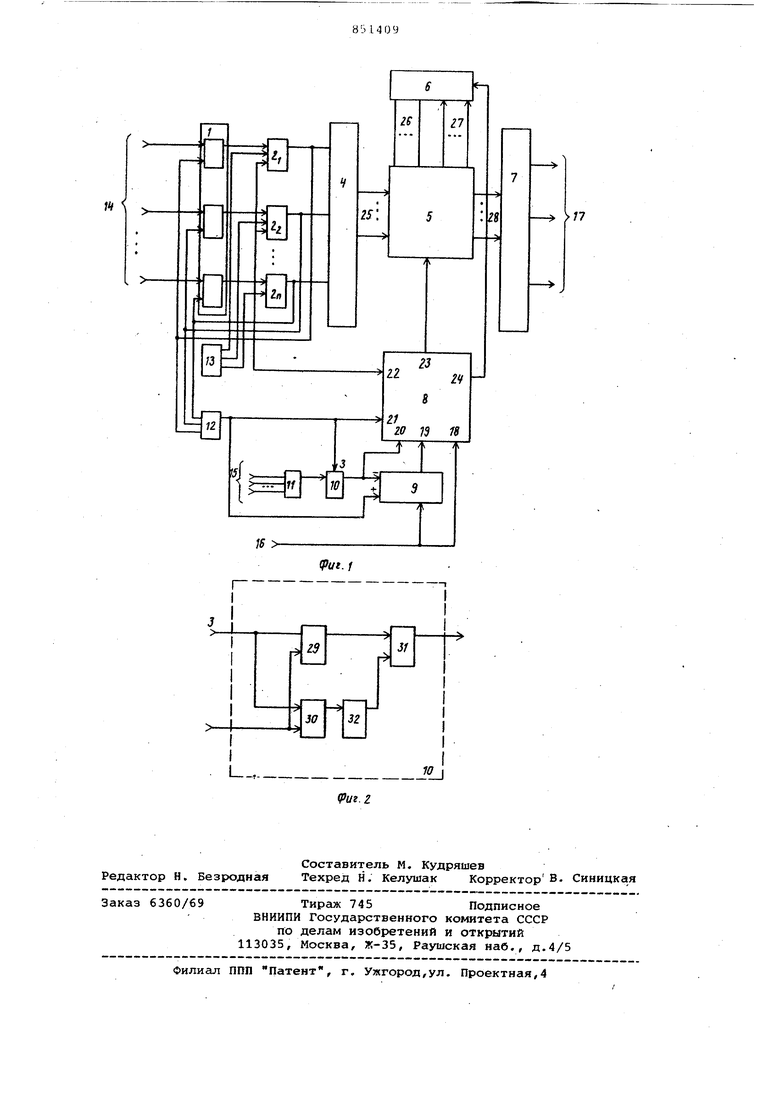

30 группа выходов элементов И группы соелинена с группой управляющих входов регистра и со входами первого элемента ИЛИ, выход которого соединен с первым входом коммутатора с суммирующим входом счетчика и с первых входом блока разделения сигналов, группа входов второго элемента ИЛИ является группой управлякидих входов устройства, выход второго элемента ИЛИ соединен со вторым входом блока разделения сигналов, выход блока разделения сигналов соединен со вторым входом распределител управляющих сигналов и с вычитающим входом счетчика, управляющий вход устройства соединен с управляющим входом счетчика и с третьим входом распределителя управляющих сигналов выход счетчика соединен с четвертым входом распределителя управлякхдих сигналов, группа выходов дешифратора является группой информационных входов устройства. Поставленная цель достигается также тем, что блок разделения сигна лов содержит два элемента И, элемент ИЛИ, элемент задержки, причем первый вход первого элемента И блока соеди нен с первым входом блока и с первым входом второго элемента И блока, вторые входы первого и второго элементов И блока соединены со вторым ВХОДСЯ4 блока, выход второго элемент И блока соединен через элемент задержки блока с первь м входом элемента ИЛИ блока, второй вход элемен та Т1ЛИ блока соединен с выходом пер вого элемента И блока, выход элемен та ИЛИ блока соединен с вьосодом бло ха. На фиг. 1 приведена структурная схема устройства, на фиг. 2 структурная схема блока разделениясигналов. Предлагаемое устройство содержит регистр 1, группу элементов И первый вход 3 блока 10 разделения сигналов, шифратор 4, коммутатор 5, блок 6 памяти, дешифратор 7, распре делитель 8 управлякицих сигналов, счетчик 9, блок 10 разделения сигна лов, элементы ИЛИ 11 и 12, генератор 13 импульсов, группу информационных входов 14 устройства, группу управляющих входов 15 устройства управляющий вход 16 устройства, группу информационных выходов 17 устройства, третий вход 18, четвертый вход 19, второй вход 20, первый , первый выход 22, второй выход 23, третий выход ,24, первая группа входов 25 коммутатора, втора группа входов 26 кстмутатора, втора группа выходов 27 коммутатора, перв группа выходов 28 коквлутатора, элементы И 29 и 30, элемент ИЛИ 31, элемент 32 задержки. Устройство работает следующим образом. с приходом запроса на один из входов группы входов 14 производится запоминание его в регистре 1. Соответствующий выход этого регистра подготавливает к работе соответствующий элемент группы И , на другой вход которого поступает сдвинутый по времени опрашивающий импульс с генератора 13. На третий вход выбранного элемента И 2 поступает разрешающий потенциал с выхода 22. Сигнал с выхода элемента И 2 поступает на вход шифратора 4, а также на сброс соответствуквдего азряда в регистре 1 и через элемент ИЛИ 12 на суммирующий вход счетчика 9 и вход 21. По этому сигналу распределитель 8 снимет разрешающий потенциал с третьих входов элементов И и выдает соответствующие управляющие сигналы. Если очередь пуста (на входе 19 имеется сигнал от реверсивного счетчика 9), то с выхода 23 на коммутатор 5 выдается соответствующий управляю1аий сигнал, по которому тот коммутирует свою группу входов 25 с группой выходов 28, и код номера абонента с выходов шифратора 4 поступает на входы дешифратора 7 без записи его в буферное запоминающее устройство, если очередь не пуста, то распределитель 8 выдает по своим 23 и 24 выходам соответствующие управляющие сигналы,по которым коммутатор 5 коммутирует свою группу входов 25 с группой выходов 27, и код номера абонента с выходов шифратора 4 записывается в блок б. Через время t«, которое равно времени записи кода номера абонента в блок 6, на выходе 22 появляется разрешакиций потенцигш, поступающий на третьи входы элементов И . С приходом сигнала об освобожде- . НИИ обслуживаюсзего устройства на группу входов 15 этот сигнал через элемент ИЛИ 11 и блок 10 разделения сигналов поступает на вычитающий вход реверсивного счетчика 9 и вход 20. По этому сигналу распределитель 8 выдает по своим 23 и 24 выходам соответствующие управляющие сигналы на коммутатор 5 и блок 6. В блоке 6 выбирается ячейка, и из нее считывается код номера абонента, дольше всех находившегося в очереди, а коммутатор 5 коммутирует свою группу входов с группой выходов 28, и код номера абонента поступает из блока б на дешифратор 7.В случае одновременного поступления на группу входов 14 запросов от двух и более абонентов проход их на шифратор 4 осуществляется последовательно из-за опроса элементов И 2 -2„ сдвинутыми импульсс1ми с генератора 13 импульсов опроса. При одновременном появлении сигнала о поступлении запроса на выходе эле мента ИЛИ 12 и сигнала об освобождении обслунивающего устройства на выходе элемента ИЛИ 11 блок 10 разделения сигналов обеспечивает преимущественное прохокодение сигнала о поступлении запроса за счет того, что сигнал об освобождении обслужи{вакхдего устройства в этом случае задерживается в блоке 10 разделения сигнёшов и появляется на его выходе через время t),которое равно времени записи кода номера абонента в буфер ное запоминакяцее устройства 6. Предлагаемое устройство позволяет упростить устройство за счет отсутствия в нем блоков разрешения кон фликтных ситуаций. ФоЕячула изобретения 1. Устройство для управления очередностью Обслуживания запросов, содержащее регистр, группу элементов И распределитель управляющих сигналов коммутатор, блок памяти, причем труп па информационных BXOJQOB регистра является группой информационных входов устройства, разрядные выходы регистра соединены с первыми входами соответствукицих элементов И группы, группа выходов блока памяти соединен с первой группой входов коммутатора первый выход распределителя управляющих сигналов соединен со входом коммутатора, второй выход распредели теля управляющих сигналов соединен со входом блока памяти, о т л и ч а ю щ е ее я тем, что, с целью повышения производительности,устройcTiso содержит генератор импульсов, шифратор, дешифратор, два элемента ИЛИ, счетчик, блок разделения сигнгшов, причём второй вход каждого элемента И группы соединен с соответствующим выходом генератора импульсов, третий вход каждого элемента И группы соединен с третьим вы ходом распределителя управляющих сигналов, выходы элементов И группы соединены с группой входов шифратора .группа выходов шифратора соединена со второй группой входов коммутатора, первая группа выходов коммутатора соединена с группой входов дешифратора, вторая группа выходов коммутатора соединена с группой входов блока памяти, группа выходов элементов И группы соединена с группой управлшпцих входов регистра и со входами первого элемента ИЛИ, выход первого элемента ИЛИ соединен с первым входом коммутатора, с суммирующим входом счетчика и с первым входом блока разделения сигналов, группа входов второго элемента ИЛИ является группой управляющих входов устройства, вьвсод второго элемента ИЛИ соединен со вторьт входом блока разделения сигналов, выход блока разделения сигнгшов соединенГ . со вторым входом распределителя управляющих сигналов и с вычитакяцим входом счетчика, управляющий вход устройства соединен с управляющим входом счетчика и с третьим входом распределителя управляющих сигналов, выход счетчика соединен с четвертым входом распределителя управляю11и Х сигналов f группа выходов дешифратора является группой информационных выходов устройства. 2 Устройство по п.1, отличающееся тем, что блок разделения сигналов содержит два элемента И, элемент ИЛИ, элемент за держки, причем первый вход первого элемента И соединен с первым входом блока и с первым входс { второго элемента И, вторые входы первого и второго элементов И соединены со вторым входом блока, выход второго элемента И соединен через элемент задержки с первым входом элемента ИЛИ, второй вход элемента ИЛИ соединен с выходом первого элемента И, выход элемента ШШ соединен с выходом блока. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР I 631921, кл. S 06 F 9/18, 1978. 2.Авторское свидетельство СССР 590742, кл. 6 06 F 9/18, 1978 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для организации очередности приема информации | 1983 |

|

SU1128255A1 |

| Система коммутации | 1985 |

|

SU1317448A1 |

| Имитатор абонентов | 1983 |

|

SU1291987A1 |

| Многоканальное буферное запоминающее устройство | 1990 |

|

SU1721631A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1990 |

|

SU1702380A1 |

| Устройство для обработки запросов | 1984 |

|

SU1213478A1 |

| Устройство для формирования лексических массивов | 1980 |

|

SU934487A1 |

| Система ввода-вывода для микропрограммируемой ЭВМ | 1988 |

|

SU1667084A1 |

| Устройство для обмена информацией | 1982 |

|

SU1048468A1 |

| Устройство управления | 1989 |

|

SU1654820A1 |

Авторы

Даты

1981-07-30—Публикация

1979-12-25—Подача