Изобретение относится к вычислительной технике и может быть использовано при проектировании средств управления многопроцессорных вычислительных систем.

Цель изобретения - расширение области применения за счет реализации на прерывание объекта управления.

Расширение области применения обеспечивается за счет возможности использования в составе устройства иерархической вычислительной системы. Эта система содержит на верхнем уровне центральное устройство управления (процессор высшего уровня управления),

вырабатывающее системные команды управления, предопределяющее режимы работы как устройств, идентичных данному и находящихся на втором уровне иерархии управления, так и объектов управления (процессоров) низшего третьего уровня, управляемых устройствами управления.

При этом устройство управления верхнего уровня может задавать маску абонентов, которая запрещает выдачу команд с второго уровня управления объектам управления третьего уровня. Это позволяет расширить область применения устройства за счет обеспечения

О

сл

4

00

to

возможности селективного управления объектами низшего уровня, что важно, например, при отказе некоторых из них либо при динамически изменяемом числе параллельных ветвей программ, реализуемых процессорами низшего уровня управления.

Устройство управления выдает на объекты управления коды реализуемых операций, которые могут восприниматься последними как имена реализуемых ими процедур, а также адреса областей (страниц) общей памяти, к которым разрешается обращаться соответствующим процессорам. Сообщение указанной информации необходимо для повышения достоверности функционирования устройства за счет предотвращения конфликтов при обращении к общему полю памяти,

На входы устройства поступают логические условия трех типов: статичес- кие, определяющие режим работы устройства и поступающие от процессора внешнего уровня управления, динамические, поступающие от объектов управления низшего уровня и определяющие состояние объекта управления, а также ход выполнения им заданных операций, и кроме того, логические условияма г

системы.

Использование технических средств, позволяющих обрабатывать указанное множество логических условий, в совокупности с другими элементами обеспечивает расширение области применения устройства.

., задаваемые с блока задания режи- I., которые могут использоваться, например , при отладке

Кроме того, на входы устройства от абонентов управления низшего уровня поступают сигналы прерывания (сигналы отказов двух типов). Сигналы отказов первого типа не требуют организации повтора команды, выдаваемой устройством, а лишь инициируют формирование соответствующего кода сообщения для процессора верхнего уровня управления. Сигналы отказов второго типа соответствуют случаю, когда необходимо осуществить замену области памяти в связи, например, с обнаружением средствами контроля объекта управления отказов памяти. В этом случае организуется повторение команд с указанием объекту управления модифицированного адреса области памяти.

4820й

Кроме того, устройством формируется код сообщения для процессора верхнего уровня, а также выдается извещающий сигнал о необходимости задержать выдачу следующей системной команды этим процессором. При этом обеспечивается повышение достоверности информации и расширение области примеJQ нения устройства.

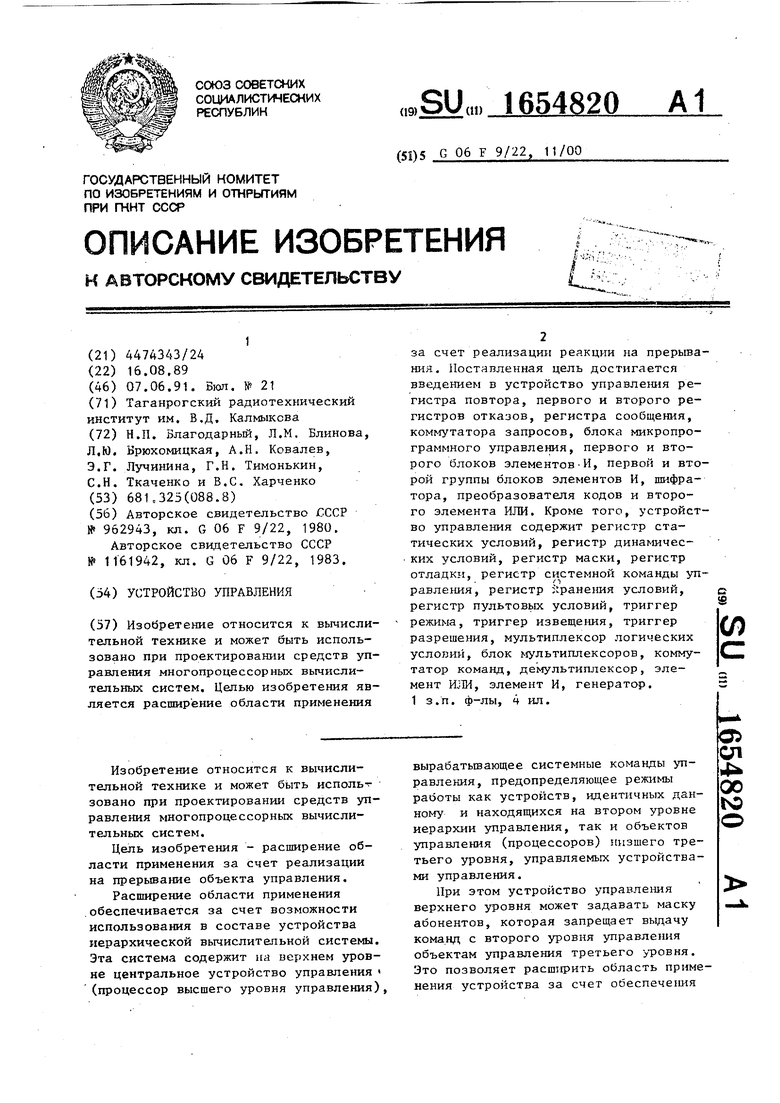

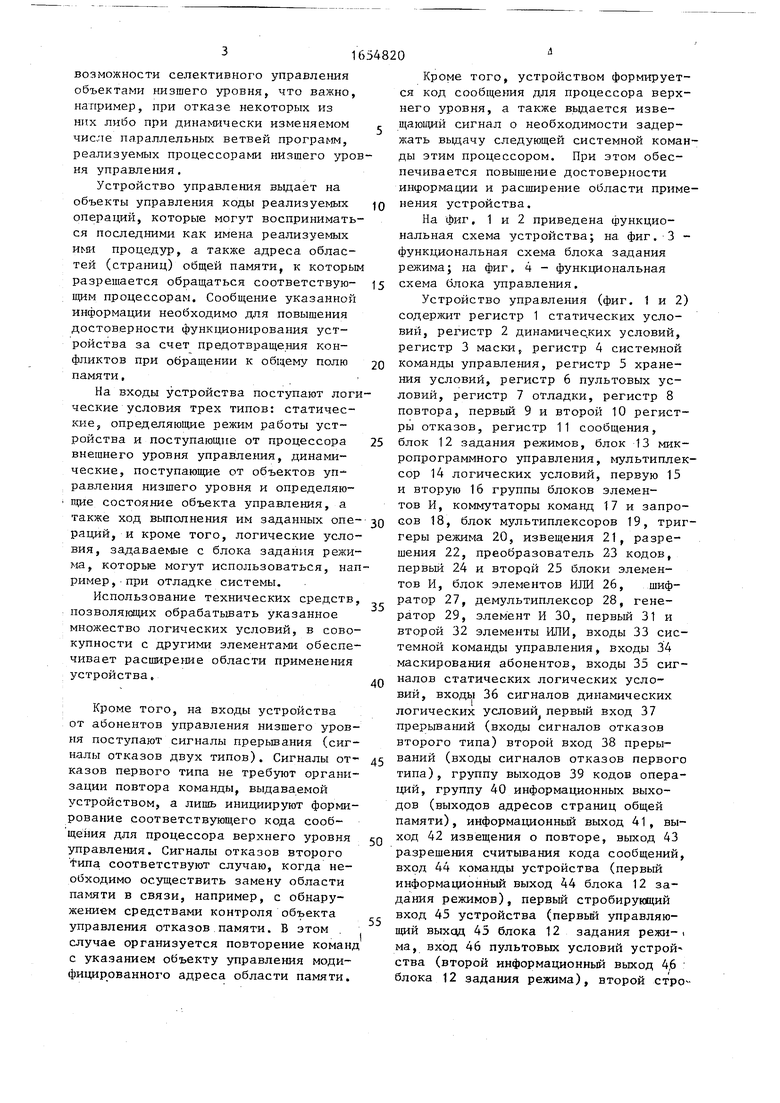

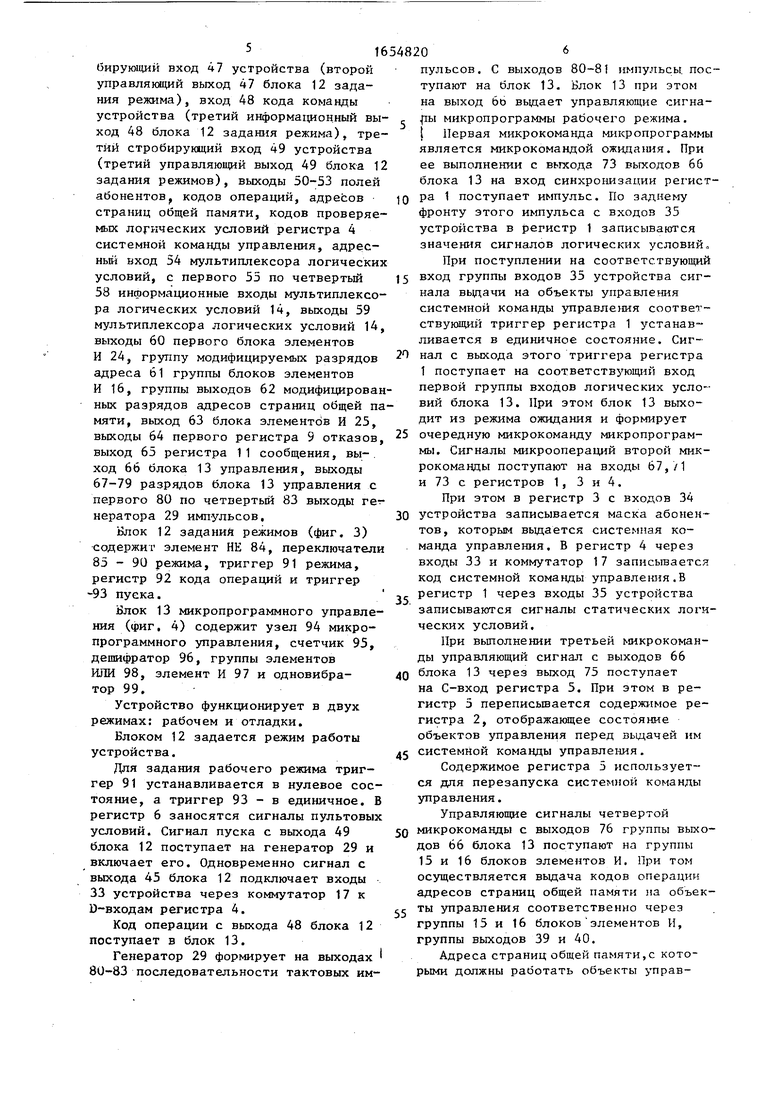

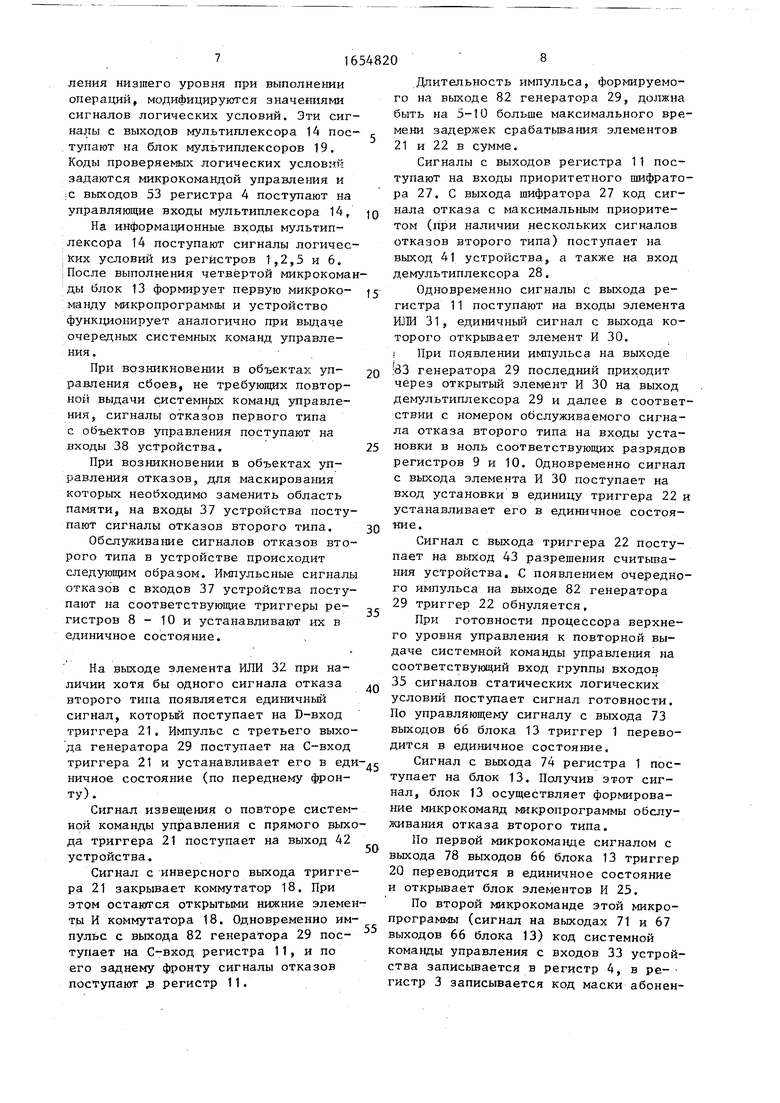

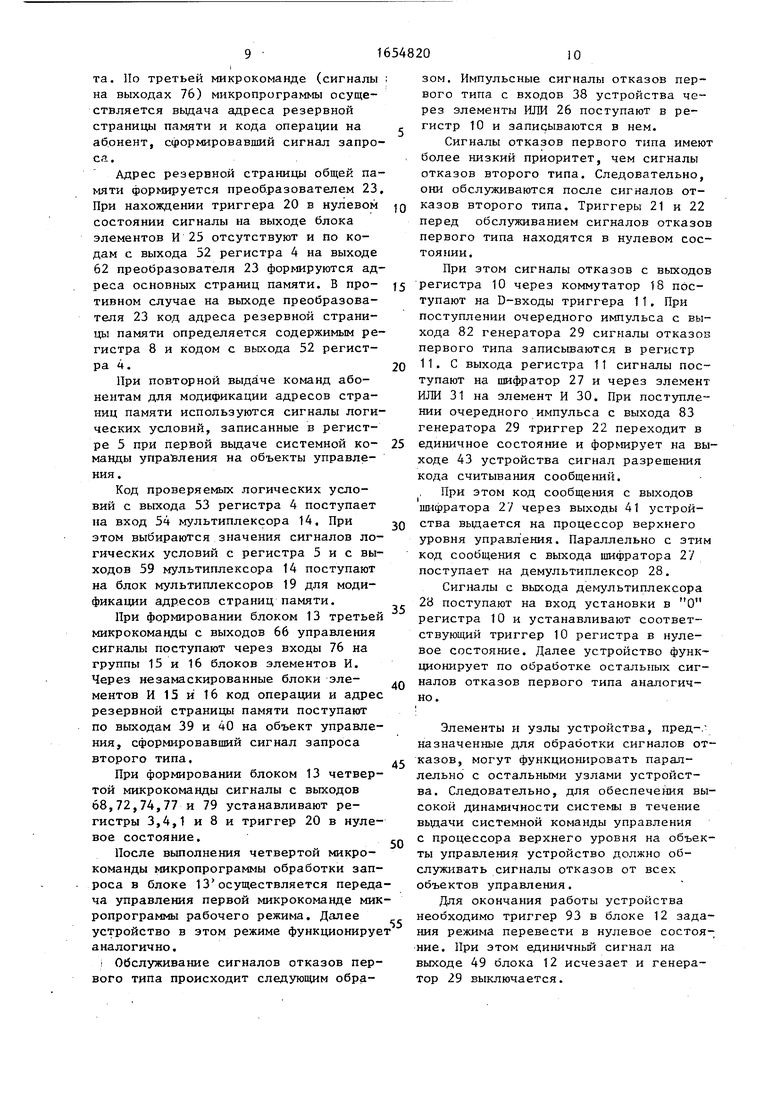

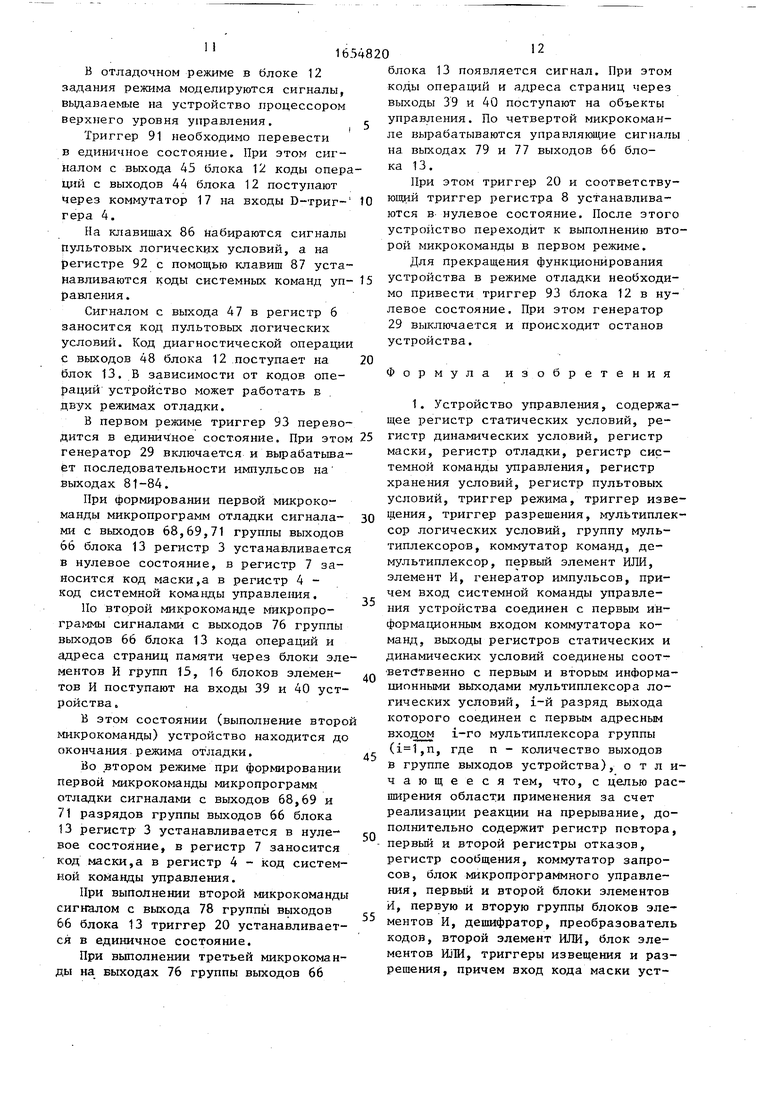

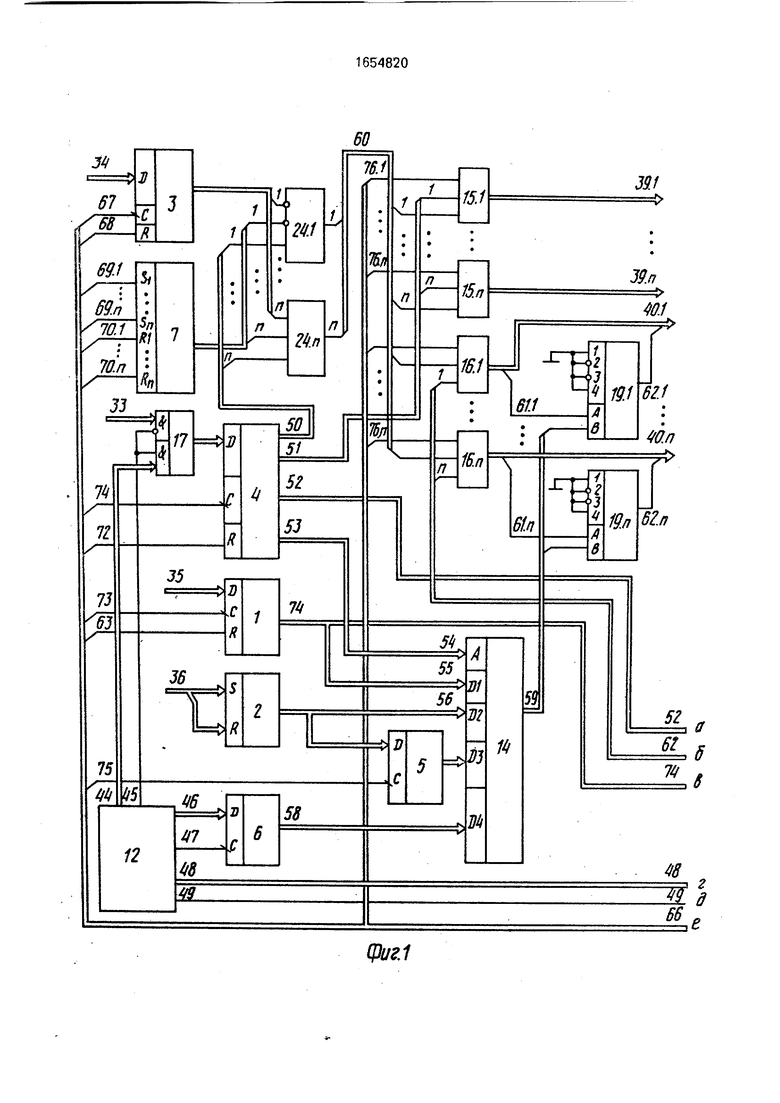

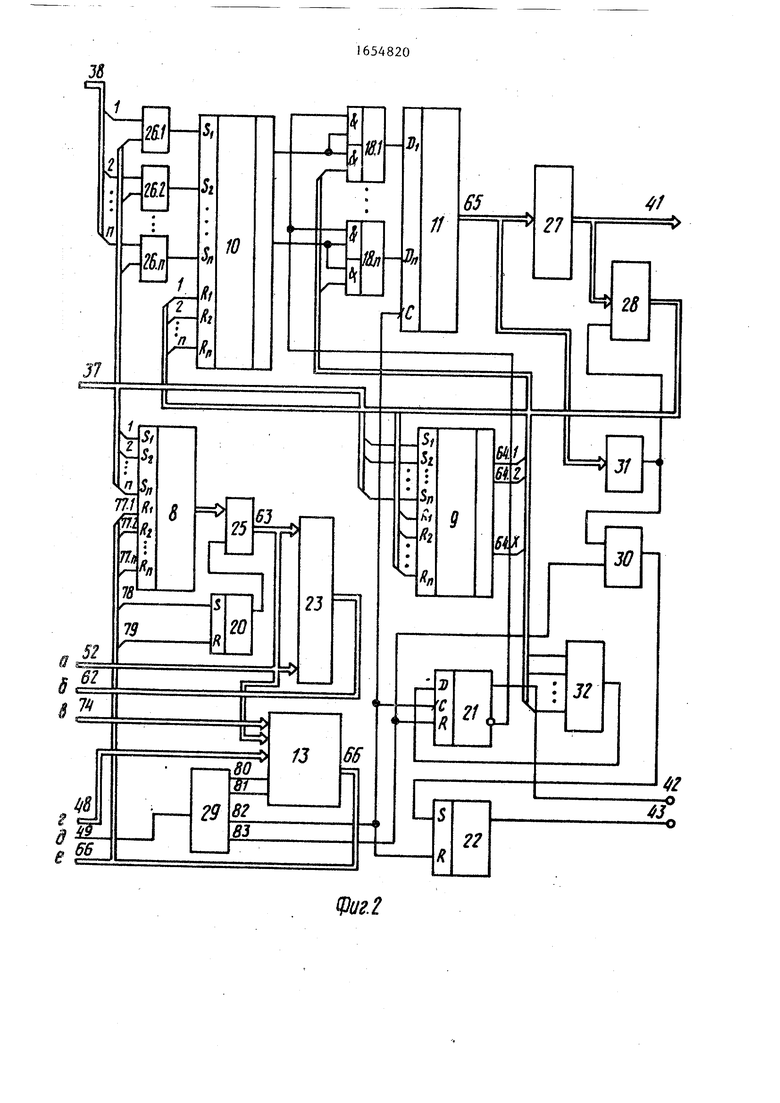

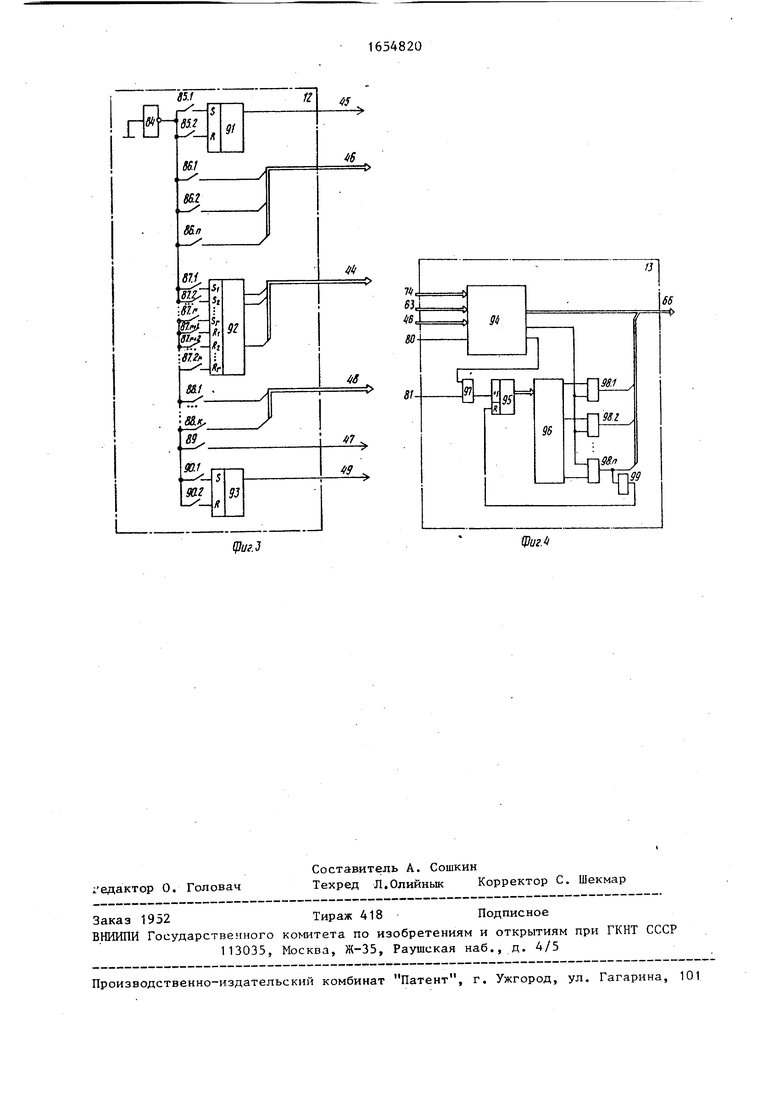

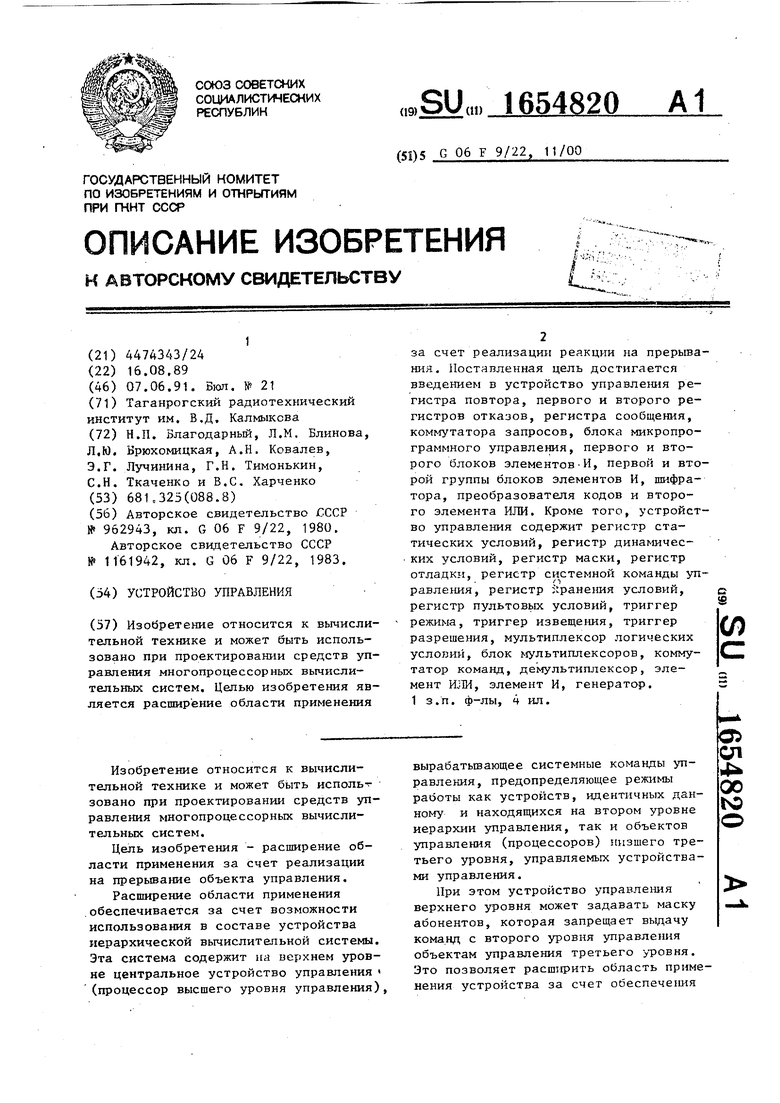

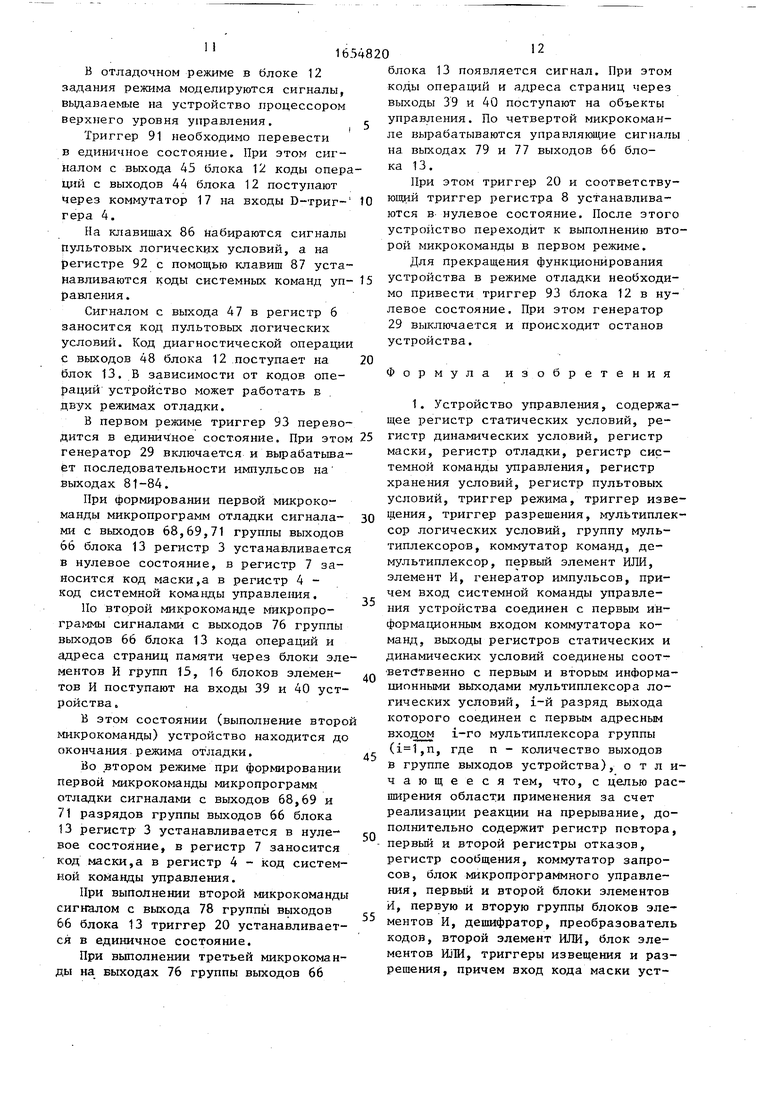

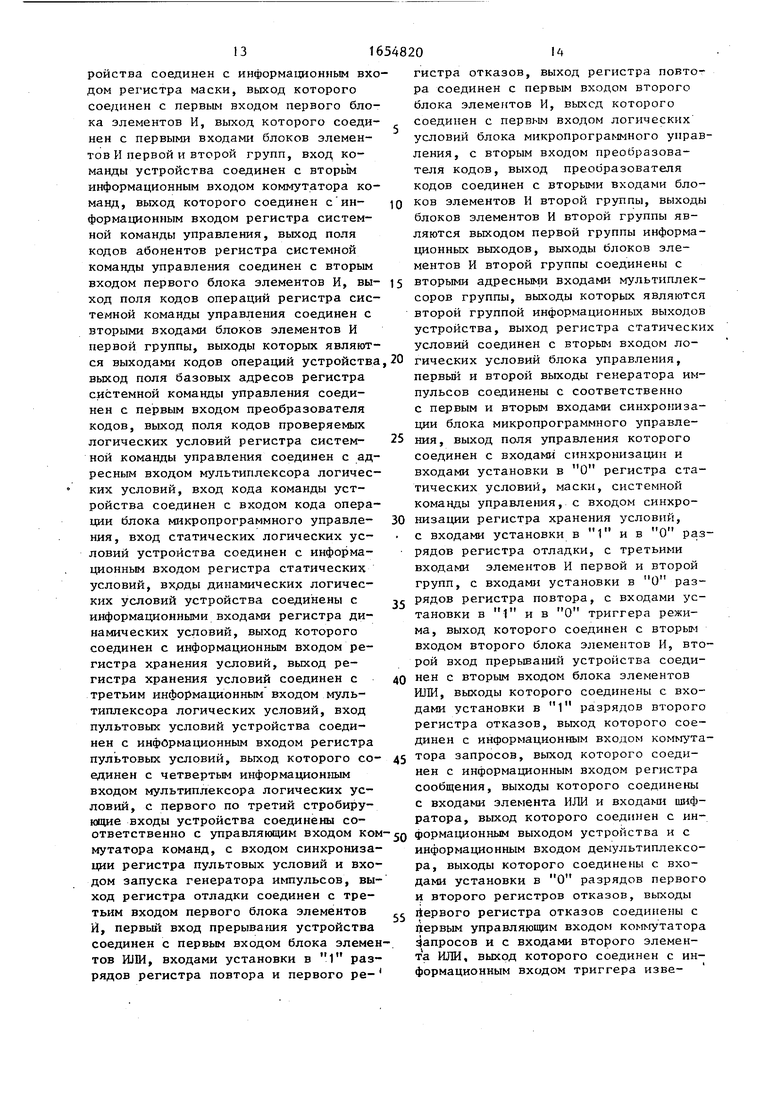

На фиг, 1 и 2 приведена функциональная схема устройства; на фиг. 3 - функциональная схема блока задания режима; на фиг, 4 - функциональная

15 схема блока управления.

Устройство управления (фиг. 1 и 2) содержит регистр 1 статических условий, регистр 2 динамичес.ких условий, регистр 3 маски5 регистр 4 системной

20 команды управления, регистр 5 хранения условий, регистр 6 пультовых условий, регистр 7 отладки, регистр 8 повтора, первьй 9 и второй 10 регист5

0

5

0

5

0

5

ры отказов, регистр 11 сообщения, блок 12 задания режимов, блок 13 микропрограммного управления, мультиплексор 14 логических условий, первую 15 и вторую 16 группы блоков элементов И, коммутаторы команд 17 и запросов 18, блок мультиплексоров 19, триггеры режима 20, извещения 21, разрешения 22, преобразователь 23 кодов, первый 24 и второй 25 блоки элементов И, блок элементов ИЛИ 26, шифратор 27, демультиплексор 28, генератор 29, элемент И 30, первый 31 и второй 32 элементы ИЛИ, входы 33 системной команды управления, входы 34 маскирования абонентов, входы 35 сигналов статических логических условий, входы 36 сигналов динамических логических условш первый вход 37 прерываний (входы сигналов отказов второго типа) второй вход 38 прерываний (входы сигналов отказов первого типа), группу выходов 39 кодов операций, группу 40 информационных выходов (выходов адресов страниц общей памяти), информационный выход 41, выход 42 извещения о повторе, выход 43 разрешения считывания кода сообщений, вход 44 команды устройства (первьй информационный выход 44 блока 12 задания режимов), первый стробирующий вход 45 устройства (первый управляющий выход 45 блока 12 задания режи- ма, вход 46 пультовых условий устрой ства (второй информационный выход 4,6 блока 12 задания режима), второй стробирующий вход 47 устройства (второй управляющий выход 47 блока 12 задания режима), вход 48 кода команды устройства (третий информационный выход 48 блока 12 задания режима), третий стробирующий вход 49 устройства (третий управляющий выход 49 блока 12 задания режимов), выходы 50-53 полей абонентовf кодов операций, адресов страниц общей памяти, кодов проверяемых логических условий регистра 4 системной команды управления, адресный вход 54 мультиплексора логических условий, с первого 55 по четвертый 58 информационные входы мультиплексора логических условий 14, выходы 59 мультиплексора логических условий 14, выходы 60 первого блока элементов И 24, группу модифицируемых разрядов адреса 61 группы блоков элементов И 16, группы выходов 62 модифицированных разрядов адресов страниц общей памяти, выход 63 блока элементов И 25,

10

пульсов. С выходов 80-81 импульсы пос тупают на блок 13. Блок 13 при этом на выход 6t выдает управляющие сигналы микропрограммы рабочего режима. Первая микрокоманда микропрограммы является микрокомандой ожидания. При ее выполнении с выхода 73 выходов 66 блока 13 на вход синхронизации регист ра 1 поступает импульс. По заднему фронту этого импульса с входов 35 устройства в регистр 1 записываются значения сигналов логических условий. При поступлении на соответствующий 15 вход группы входов 35 устройства сигнала выдачи на объекты управления системной команды управления соответствующий триггер регистра 1 устанавливается в единичное состояние. Сигнал с выхода этого триггера регистра 1 поступает на соответствующий вход первой группы входов логических уеловий блока 13. При этом блок 13 выходит из режима ожидания и формирует

20

30

35

выходы 64 первого регистра 9 отказов, 25 очередную микрокоманду микропрограм- выход 65 регистра 11 сообщения, выход 66 блока 13 управления, выходы 67-79 разрядов блока 13 управления с первого 80 по четвертый 83 выходы гег- нератора 29 импульсов.

Блок 12 заданий режимов (фиг. 3) содержит элемент НЕ 84, переключатели 85 - 90 режима, триггер 91 режима, регистр 92 кода операций и триггер -93 пуска.

Блок 13 микропрограммного управления (фиг, 4) содержит узел 94 микропрограммного управления, счетчик 95, дешифратор 96, группы элементов ИЛИ 98, элемент И 97 и одновибра- тор 99.

Устройство функционирует в двух режимах: рабочем и отладки.

Блоком 12 задается режим работы устройства.

Для задания рабочего режима триггер 91 устанавливается в нулевое сос40

мы. Сигналы микроопераций второй микрокоманды поступают на входы 67,/1 и 73 с регистров 1, 3 и 4.

При этом в регистр 3 с входов 34 устройства записывается маска абонентов, которым выдается системная команда управления. В регистр 4 через входы 33 и коммутатор 17 записывается код системной команды управления.В регистр 1 через входы 35 устройства записываются сигналы статических логи ческих условий.

При выполнении третьей микрокоманды управляющий сигнал с выходов 66 блока 13 через выход 75 поступает на С-вход регистра 5. При этом в регистр 5 переписывается содержимое регистра 2, отображающее состояние объектов управления перед выдачей им 45 системной команды управления.

Содержимое регистра 5 используется для перезапуска системной команды управления.

тояние, а триггер 93 - в единичное. В регистр 6 заносятся сигналы пультовых условий. Сигнал пуска с выхода 49 блока 12 поступает на генератор 29 и включает его. Одновременно сигнал с выхода 45 блока 12 подключает входы 33 устройства через коммутатор 17 к D-входам регистра 4.

Код операции с выхода 48 блока 12 поступает в блок 13.

Генератор 29 формирует на выходах 80-83 последовательности тактовых им

пульсов. С выходов 80-81 импульсы поступают на блок 13. Блок 13 при этом на выход 6t выдает управляющие сигналы микропрограммы рабочего режима. Первая микрокоманда микропрограммы является микрокомандой ожидания. При ее выполнении с выхода 73 выходов 66 блока 13 на вход синхронизации регистра 1 поступает импульс. По заднему фронту этого импульса с входов 35 устройства в регистр 1 записываются значения сигналов логических условий. При поступлении на соответствующий 5 вход группы входов 35 устройства сигнала выдачи на объекты управления системной команды управления соответствующий триггер регистра 1 устанавливается в единичное состояние. Сигнал с выхода этого триггера регистра 1 поступает на соответствующий вход первой группы входов логических уело- вий блока 13. При этом блок 13 выходит из режима ожидания и формирует

очередную микрокоманду микропрограм-

мы. Сигналы микроопераций второй микрокоманды поступают на входы 67,/1 и 73 с регистров 1, 3 и 4.

При этом в регистр 3 с входов 34 устройства записывается маска абонентов, которым выдается системная команда управления. В регистр 4 через входы 33 и коммутатор 17 записывается код системной команды управления.В регистр 1 через входы 35 устройства записываются сигналы статических логических условий.

При выполнении третьей микрокоманды управляющий сигнал с выходов 66 блока 13 через выход 75 поступает на С-вход регистра 5. При этом в регистр 5 переписывается содержимое регистра 2, отображающее состояние объектов управления перед выдачей им системной команды управления.

Содержимое регистра 5 используется для перезапуска системной команды управления.

Управляющие сигналы четвертой микрокоманды с выходов 76 группы выходов 66 блока 13 поступают на группы 15 и 16 блоков элементов И. При том осуществляется выдача кодов операции адресов страниц общей памяти на объекты управления соответственно через группы 15 и 16 блоков элементов И, группы выходов 39 и 40.

Адреса страниц общей памяти,с которыми должны работать объекты управления низшего уровня при выполнении операций, модифицируются значениями сигналов логических условий. Эти сигналы с выходов мультиплексора 14 поступают на блок мультиплексоров 19. Коды проверяемых логических условий задаются микрокомандой управления и с выходов 53 регистра 4 поступают на управляющие входы мультиплексора 14,

На информационные входы мультиплексора 14 поступают сигналы логических условий из регистров 1,2,5 и 6. После выполнения четвертой микрокоманды блок 13 формирует первую микрокоманду микропрограммы и устройство функционирует аналогично при выдаче очередных системных команд управления.

При возникновении в объектах управления сбоев, не требующих повторной выдачи системных команд управления, сигналы отказов первого типа с объектов управления поступают на входы 38 устройства.

При возникновении в объектах управления отказов, для маскирования которых необходимо заменить область памяти, на входы 37 устройства поступают сигналы отказов второго типа.

Обслуживание сигналов отказов второго типа в устройстве происходит следующим образом. Импульсные сигналы отказов с входов 37 устройства поступают на соответствующие триггеры регистров 8 - 10 и устанавливают их в единичное состояние.

10

15

20

25

40

На выходе элемента ИЛИ 32 при наличии хотя бы одного сигнала отказа второго типа появляется единичный сигнал, который поступает на D-вход триггера 21. Импульс с третьего выхода генератора 29 поступает на С-вход триггера 21 и устанавливает его в еди- ничное состояние (по переднему фронту) .

Сигнал извещения о повторе системной команды управления с прямого выхода триггера 21 поступает на выход 42 устройства.

Сигнал с инверсного выхода триггера 21 закрывает коммутатор 18. При этом остаются открытыми нижние элементы И коммутатора 18. Одновременно импульс с выхода 82 генератора 29 поступает на С-вход регистра 11, и по его заднему фронту сигналы отказов поступают .в регистр 11.

16548208

Длительность импульса, формируемого на выходе 82 генератора 29, должна быть на 5-10 больше максимального времени задержек срабатывания элементов 21 и 22 в сумме.

Сигналы с выходов регистра 11 поступают на входы приоритетного шифратора 27, С выхода шифратора 27 код сигнала отказа с максимальным приоритетом (при наличии нескольких сигналов отказов второго типа) поступает на выход 41 устройства, а также на вход демультиплексора 28.

Одновременно сигналы с выхода регистра 11 поступают на входы элемента ИЛИ 31, единичный сигнал с выхода которого открывает элемент И 30. i При появлении импульса на выходе 83 генератора 29 последний приходит через открытый элемент И 30 на выход демультиплексора 29 и далее в соответствии с номером обслуживаемого сигнала отказа второго типа на входы установки в ноль соответствующих разрядов регистров 9 и 10. Одновременно сигнал с выхода элемента И 30 поступает на вход установки в единицу триггера 22 и устанавливает его в единичное состояние.

Сигнал с выхода триггера 22 поступает на выход 43 разрешения считывания устройства, С появлением очередного импульса на выходе 82 генератора 29 триггер 22 обнуляется.

При готовности процессора верхнего уровня управления к повторной выдаче системной команды управления на соответствующий вход группы входов 35 сигналов статических логических условий поступает сигнал готовности. По управляющему сигналу с выхода 73 выходов 66 блока 13 триггер 1 переводится в единичное состояние.

Сигнал с выхода 74 регистра 1 поступает на блок 13. Получив этот сигнал, блок 13 осуществляет формирование микрокоманд микропрограммы обслуживания отказа второго типа.

Но первой микрокоманде сигналом с выхода 78 выходов 66 блока 13 триггер 20 переводится в единичное состояние и открывает блок элементов И 25.

По второй микрокоманде этой микропрограммы (сигнал на выходах 71 и 67 выходов 66 блока 13) код системной команды управления с входов 33 устройства записывается в регистр 4, в ре- гистр 3 записывается код маски абонен30

35

55

та. По третьей микрокоманде (сигналы на выходах 76) микропрограммы осуществляется выдача адреса резервной страницы памяти и кода операции на абонент, сформировавший сигнал запроса.

Адрес резервной страницы общей памяти формируется преобразователем 23. При нахождении триггера 20 в нулевом состоянии сигналы на выходе блока элементов И 25 отсутствуют и по кодам с выхода 52 регистра 4 на выходе 62 преобразователя 23 формируются адреса основных страниц памяти. В противном случае на выходе преобразователя 23 код адреса резервной страницы памяти определяется содержимым регистра 8 и кодом с выхода 52 регистра 4.

При повторной выдаче команд абонентам для модификации адресов страниц памяти используются сигналы логических условий, записанные в регистре 5 при первой выдаче системной команды управления на объекты управления.

Код проверяемых логических условий с выхода 53 регистра 4 поступает на вход 54 мультиплексора 14, При этом выбираются значения сигналов логических условий с регистра 5 и с выходов 59 мультиплексора 14 поступают на блок мультиплексоров 19 для модификации адресов страниц памяти.

При формировании блоком 13 третьей микрокоманды с выходов 66 управления сигналы поступают через входы 76 на группы 15 и 16 блоков элементов И. Через незамаскированные блоки элементов И 15 и 16 код операции и адрес резервной страницы памяти поступают по выходам 39 и 40 на объект управления, сформировавший сигнал запроса второго типа.

При формировании блоком 13 четвертой микрокоманды сигналы с выходов 68,72,74,77 и 79 устанавливают регистры 3,4,1 и 8 и триггер 20 в нулевое состояние.

После выполнения четвертой микрокоманды микропрограммы обработки запроса в блоке 13 осуществляется передача управления первой микрокоманде микропрограммы рабочего режима. Далее устройство в этом режиме функционируе аналогично.

i Обслуживание сигналов отказов первого типа происходит следующим обра0

5

0

5

зом. Импульсные сигналы отказов первого типа с входов 38 устройства через элементы ИЛИ 26 поступают в регистр 10 и записываются в нем.

Сигналы отказов первого типа имеют более низкий приоритет, чем сигналы отказов второго типа. Следовательно, они обслуживаются после сигналов отказов второго типа. Триггеры 21 и 22 перед обслуживанием сигналов отказов первого типа находятся в нулевом состоянии.

При этом сигналы отказов с выходов регистра 10 через коммутатор 18 поступают на D-входы триггера 11, При поступлении очередного импульса с выхода 82 генератора 29 сигналы отказов первого типа записываются в регистр 11. С выхода регистра 11 сигналы поступают на шифратор 27 и через элемент ИЛИ 31 на элемент И 30. При поступлении очередного импульса с выхода 83 генератора 29 триггер 22 переходит в единичное состояние и формирует на выходе 43 устройства сигнал разрешения кода считывания сообщений.

При этом код сообщения с выходов шифратора 27 через выходы 41 устройства выдается на процессор верхнего уровня управления. Параллельно с этим код сообщения с выхода шифратора 27 поступает на демультиплексор 28.

Сигналы с выхода демультиплексора 28 поступают на вход установки в О регистра 10 и устанавливают соответствующий триггер 10 регистра в нулевое состояние. Далее устройство функционирует по обработке остальных сигналов отказов первого типа аналогично.

Элементы и узлы устройства, пред-1 назначенные для обработки сигналов от- 5 казов, могут функционировать параллельно с остальными узлами устройства. Следовательно, для обеспечения высокой динамичности системы в течение выдачи системной команды управления с процессора верхнего уровня на объекты управления устройство должно обслуживать сигналы отказов от всех объектов управления.

Для окончания работы устройства необходимо триггер 93 в блоке 12 задания режима перевести в нулевое состояние. При этом единичный сигнал на выходе 49 блока 12 исчезает и генератор 29 выключается.

0

5

0

0

5

В отладочном режиме в блоке 12 задания режима моделируются сигналы, выдаваемые на устройство процессором верхнего уровня управления.

Триггер 91 необходимо перевести в единичное состояние. При этом сигналом с выхода 45 блока 12 коды операций с выходов 44 блока 12 поступают через коммутатор 17 на входы D-триг- гера 4.

На клавишах 86 набираются сигналы Пультовых логических условий, а на регистре 92 с помощью клавиш 87 устанавливаются коды системных команд уп- равления.

Сигналом с выхода 47 в регистр 6 заносится код пультовых логических условий. Код диагностической операции с выходов 48 блока 12 поступает на блок 13. В зависимости от кодов операций устройство может работать в двух режимах отладки.

В первом режиме триггер 93 переводится в единичное состояние. При этом генератор 29 включается и вырабатывает последовательности импульсов на выходах 81-84.

При формировании первой микрокоманды микропрограмм отладки сигналами с выходов 68,69,71 группы выходов 66 блока 13 регистр 3 устанавливается в нулевое состояние, в регистр 7 заносится код маски,а в регистр 4 - код системной команды управления.

По второй микрокоманде микропрограммы сигналами с выходов 76 группы выходов 66 блока 13 кода операций и адреса страниц памяти через блоки элементов И групп 15, 16 блоков элемен- тов И поступают на входы 39 и 40 устройства ,

В этом состоянии (выполнение второ микрокоманды) устройство находится до окончания режима отладки.

Во втором режиме при формировании первой микрокоманды микропрограмм отладки сигналами с выходов 68,69 и 71 разрядов группы выходов 66 блока 13 регистр 3 устанавливается в нуле

вое состояние, в регистр 7 заносится код маски,а в регистр 4 - код системной команды управления.

При выполнении второй микрокоманды сигналом с выхода 78 группы выходов 66 блока 13 триггер 20 устанавливается в единичное состояние.

При выполнении третьей микрокоманды на выходах 76 группы выходов 66

5

0

5

0

блока 13 появляется сигнал. При этом коды операций и адреса страниц через выходы 39 и 40 поступают на объекты управления. По четвертой микрокоман- ле вырабатываются управляющие сигнапы на выходах 79 и 77 выходов 66 блока 13.

При этом триггер 20 и соответствующий триггер регистра 8 устанавливаются в нулевое состояние. После этого устройство переходит к выполнению второй микрокоманды в первом режиме.

Для прекращения функционирования устройства в режиме отладки необходимо привести триггер 93 блока 12 в нулевое состояние. При этом генератор 29 выключается и происходит останов устройства.

Формула изобретения

1. Устройство управления, содержащее регистр статических условий, регистр динамических условий, регистр маски, регистр отладки, регистр системной команды управления, регистр хранения условий, регистр пультовых условий, триггер режима, триггер извещения, триггер разрешения, мультиплексор логических условий, группу мультиплексоров, коммутатор команд, де- мультиплексор, первый элемент ИЛИ, элемент И, генератор импульсов, причем вход системной команды управления устройства соединен с первым информационным входом коммутатора команд, выходы регистров статических и динамических условий соединены соответственно с первым и вторым информационными выходами мультиплексора логических условий, i-й разряд выхода которого соединен с первым адресным входом 1-го мультиплексора группы (,n, где п - количество выходов в группе выходов устройства), о т л и- чающееся тем, что, с целью расширения области применения за счет реализации реакции на прерывание, дополнительно содержит регистр повтора, первый и второй регистры отказов, регистр сообщения, коммутатор запросов, блок микропрограммного управления, первый и второй блоки элементов И, первую и вторую группы блоков эле- ментов И, дешифратор, преобразователь кодов, второй элемент ИЛИ, блок элементов ИЛИ, триггеры извещения и разрешения, причем вход кода маски уст0

5

45

50

ройства соединен с информационным входом регистра маски, выход которого соединен с первым входом первого блока элементов И, выход которого соединен с первыми входами блоков элементов И первой и второй групп, вход команды устройства соединен с вторым информационным входом коммутатора команд, выход которого соединен с ин- формационным входом регистра системной команды управления, выход поля кодов абонентов регистра системной команды управления соединен с вторым входом первого блока элементов И, вы- ход поля кодов операций регистра системной команды управления соединен с вторыми входами блоков элементов И первой группы, выходы которых являются выходами кодов операций устройства выход поля базовых адресов регистра системной команды управления соединен с первым входом преобразователя кодов, выход поля кодов проверяемых логических условий регистра систем- ной команды управления соединен с адресным входом мультиплексора логических условий, вход кода команды устройства соединен с входом кода операции блока микропрограммного управле- ния, вход статических логических условий устройства соединен с информационным входом регистра статических условий, вхрды динамических логических условий устройства соединены с информационными входами регистра динамических условий, выход которого соединен с информационным входом регистра хранения условий, выход регистра хранения условий соединен с третьим информационным входом мультиплексора логических условий, вход пультовых условий устройства соединен с информационным входом регистра пультовых условий, выход которого со- единен с четвертым информационным входом мультиплексора логических условий, с первого по третий стробиру- ющие входы устройства соединены соответственно с управляющим входом KOM мутатора команд, с входом синхронизации регистра пультовых условий и входом запуска генератора импульсов, выход регистра отладки соединен с третьим входом первого блока элементов И, первый вход прерывания устройства соединен с первым входом блока элементов ИЛИ, входами установки в 1 разрядов регистра повтора и первого ре-

Q 5 0 5 0 5 0 5 Q

5

гистра отказов, выход регистра повтора соединен с первым входом второго блока элементов И, выход которого соединен с первым входом логических условий блока микропрограммного управления, с вторым входом преобразователя кодов, выход преобразователя кодов соединен с вторыми входами блоков элементов И второй группы, выходы блоков элементов И второй группы являются выходом первой группы информационных выходов, выходы блоков элементов И второй группы соединены с вторыми адресными входами мультиплексоров группы, выходы которых являются второй группой информационных выходов устройства, выход регистра статических условий соединен с вторым входом логических условий блока управления, первый и второй выходы генератора импульсов соединены с соответственно с первым и вторым входами синхронизации блока микропрограммного управления, выход поля управления которого соединен с входами синхронизации и входами установки в О регистра статических условий, маски, системной команды управления, с входом синхронизации регистра хранения условий, с входами установки в 1 и в О разрядов регистра отладки, с третьими входами элементов И первой и второй групп, с входами установки в 0м разрядов регистра повтора, с входами установки в 1 и в О триггера режима, выход которого соединен с вторым входом второго блока элементов И, второй вход прерываний устройства соединен с вторым входом блока элементов ИЛИ, выходы которого соединены с входами установки в 1 разрядов второго регистра отказов, выход которого соединен с информационным входоь5 коммутатора запросов, выход которого соединен с информационным входом регистра сообщения, выходы которого соединены с входами элемента ИЛИ и входами шифратора, выход которого соединен с информационным выходом устройства и с информационным входом демультиплексо- ра, выходы которого соединены с входами установки в О разрядов первого и второго регистров отказов, выходы Первого регистра отказов соединены с Первым управляющим входом коммутатора Запросов и с входами второго элемента ИЛИ, выход которого соединен с информационным входом триггера извещения, прямой выход которого является выходом извещения о повторе команды устройства, инверсный выход триггера извещения соединен с вторым уп- равляющими входом коммутатора запросов, выход первого элемента ИЛИ соединен со стробирующими входом демуль- типлексора и с первым входом элемента И, выход которого соединен с вхо- дом установки в триггера разрешения выход которого соединен с вьГ- ходом разрешения считьюания на высший уровень управления устройства, третий выход генератора импульсов сое динен с входом синхронизации регистра сообщений и триггера извещений, с входом установки в О триггера разрешения, четвертый выход генератора импульсов соединен с вторым входом , элемента И и с входом установки в О триггера извещения.

2. Устройство по п. 1, отличающееся тем, что,блок микропрограммного управления содержит узел микропрограммного управления, счетчик дешифратор, группу элементов ИЛИ,

элемент И и одновибратор, причем вход кода операции, первый и второй входы, логических условий и первый вход синхронизации блока соединены соответственно с одноименными входами узла микропрограммного управления, первый выход микропрограммного управления является выходом поля управления блока, второй выход узла микропрограммного управления соединен с первыми входами элементов ИЛИ группы, выходы которых подключены к выходу поля управления блока, третий выход узла микропрограммного управления соединен с первым входом элемента И, выход которого соединен со счетным входом счетчика, информационный выход которого соединен с информационным входом дешифратора, выход которого соединен с вторыми входами элементов ИЛИ группы, выход первого элемента ИЛИ группы соединен с входом одновибратора, выход которого соединен с входом сброса счетчика, второй вход синхронизации блока соединен с вторым входом элемента И.

фиг.1

о

CM

00

r

v JS

«4,

I

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1983 |

|

SU1133595A1 |

| Микропрограммное устройство управления | 1986 |

|

SU1381506A1 |

| Микропрограммное устройство для контроля и управления | 1985 |

|

SU1325476A1 |

| Микропрограммное устройство управления с контролем | 1986 |

|

SU1305679A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1065855A1 |

| Адаптивный модуль микропрограммного устройства управления | 1984 |

|

SU1273926A1 |

| Микропрограммное устройство управления с контролем | 1985 |

|

SU1267414A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1130865A1 |

| Устройство для управления,контроля и диагностирования | 1985 |

|

SU1297063A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1140121A1 |

Изобретение относится к вычислительной технике и может быть использовано при проектировании средств управления многопроцессорных вычислительных систем. Целью изобретения является расширение области применения за счет реализации реакции на прерывания. Поставленная цель достигается введением в устройство управления регистра повтора, первого и второго регистров отказов, регистра сообщения, коммутатора запросов, блока микропрограммного управления, первого и второго блоков элементов И, первой и второй группы блоков элементов И, шифратора, преобразователя кодов и второго элемента ИЛИ. Кроме того, устройство управления содержит регистр статических условий, регистр динамических условий, регистр маски, регистр отладки, регистр системной команды управления, регистр Хранения условий, регистр пультовых условий, триггер режима, триггер извещения, триггер разрешения, мультиплексор логических условий, блок мультиплексоров, коммутатор команд, демультиплексор, элемент ИЛИ, элемент И, генератор. 1 з.п. ф-лы, 4 ил. с $ (Л

te «O qt

S S

фиг.З

80

96

№

f

фиг Л

| Микропрограммное устройство управления | 1981 |

|

SU962943A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Мультимикропрограммное устройство управления | 1983 |

|

SU1161942A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-06-07—Публикация

1989-08-16—Подача