Изобретение относится к импульсной технике и может быть использовано в устройствах вычислительной техники и систем управления.

Известно триггерное устройство (см. авторское свидетельство СССР №1753919 от 05.10.90, МКИ: Н 03 К 3/037 "Триггерное устройство", авторы Л.Б.Егоров, Г.И.Шишкин, опубл. 10.09.97, бюл. №25), содержащее первый и второй элементы памяти на магнитных сердечниках, выходы обмоток считывания которых соединены с общей шиной, входы обмоток записи соединены соответственно с прямым и инверсным выходами элемента "ИСКЛЮЧАЮЩЕЕ ИЛИ", первый и второй входы которого подключены к входной шине и выходу RS-триггера соответственно, входы установки и сброса которого соединены через соответственно первый и второй резисторы с входами обмоток считывания первого и второго элементов памяти соответственно. Первый вход блока управления соединен с входной шиной, второй и третий входы блока управления соединены соответственно с прямым и инверсным выходами элемента "ИСКЛЮЧАЮЩЕЕ ИЛИ", а первый и второй выходы блока управления соответственно через третий и четвертый резисторы соединены с выходами обмоток записи соответственно первого и второго элементов памяти.

Недостатком данного триггерного устройства является сравнительно низкая помехоустойчивость в условиях воздействия высокоинтенсивных электрических помех большой длительности, наведенных по цепям его связи.

Известно триггерное устройство (см. патент РФ №2106742 от 16.08.95, МКИ: Н 03 К 3/286 "Триггерное устройство", авторы Е.И.Рыжаков, Г.И.Шишкин, опубл. 10.03.98, бюл. №7), которое является наиболее близким по технической сущности к заявляемому объекту и выбрано в качестве прототипа, содержащее RS-триггер, входы установки и сброса которого соединены с первыми выводами первого и второго резисторов соответственно и через соответственно первый и второй конденсаторы - с общей шиной, а прямой и инверсный выходы соединены с первыми входами соответственно первого и второго элементов "ИСКЛЮЧАЮЩЕЕ ИЛИ", вторые входы которых подключены к входной шине триггерного устройства, а выходы соединены с входами обмоток записи соответственно первого и второго элементов памяти на магнитных сердечниках, входы обмоток считывания которых соединены с общей шиной, первый и второй элементы И-НЕ, третий и четвертый элементы "ИСКЛЮЧАЮЩЕЕ ИЛИ", третий, четвертый, пятый и шестой резисторы. RS-триггер выполнен на элементах И-НЕ. Выходы первого и второго элементов "ИСКЛЮЧАЮЩЕЕ ИЛИ" соединены с первыми входами соответственно третьего и четвертого элементов "ИСКЛЮЧАЮЩЕЕ ИЛИ", выходы которых через соответственно третий и четвертый резисторы соединены с выходами обмоток записи соответственно первого и второго элементов памяти, выходы обмоток считывания которых через соответственно пятый и шестой резисторы соединены с первыми входами соответственно первого и второго элементов И-НЕ, выходы которых соединены со вторыми выводами соответственно второго и первого резисторов и со вторыми входами соответственно четвертого и третьего элементов "ИСКЛЮЧАЮЩЕЕ ИЛИ". Вторые входы первого и второго элементов И-НЕ объединены и подключены к входной шине триггерного устройства.

Недостатком прототипа является сравнительно низкая помехоустойчивость в условиях воздействия высокоинтенсивных электрических помех большой длительности, наведенных по цепям его связи. Элементы памяти на магнитных сердечниках обеспечивают триггерному устройству свойство энергонезависимости, однако такое триггерное устройство устойчиво к воздействию электрических помех, наведенных по цепям его связи, длительность которых не превышает время перемагничивания сердечников. При выполнении элементов памяти в приемлемых габаритных размерах указанное время невелико (не превышает 10-20 микросекунд), следовательно, триггерное устройство будет сбиваться от помеховых импульсов большей длительности.

Задачей, решаемой заявляемым изобретением, является повышение помехоустойчивости триггерного устройства в условиях высокоинтенсивных электрических помех большой длительности.

Указанный технический результат достигается тем, что в триггерном устройстве, содержащем первый RS-триггер, устройство управления с, по крайней мере, тремя входами и тремя выходами, при этом первый и второй входы устройства управления соединены соответственно с прямым и инверсным выходами первого RS-триггера, третий вход - с входной шиной, а первый выход - с первыми входами первого и второго элементов совпадения, вторые входы которых соединены с первыми выводами соответственно первого и второго резисторов, первый и второй конденсаторы, первые выводы которых соединены с общей шиной, первый и второй элементы памяти на магнитных сердечниках с прямоугольной петлей гистерезиса, каждый из которых имеет, по крайней мере, одну обмотку, один из выводов обмотки первого и второго элементов памяти соединен с первым выводом соответственно третьего и четвертого резисторов, пятый и шестой резисторы, новым является выполнение первого и второго элементов совпадения в виде соответственно первого и второго элементов ИЛИ-НЕ, введение первого и второго диодов, третьего и четвертого конденсаторов, третьего и четвертого элементов ИЛИ-НЕ, второго RS-триггера, входы сброса и установки которого соединены соответственно со вторым и третьим выходами устройства управления, а прямой и инверсный выходы - с катодами соответственно второго и первого диодов, аноды которых соединены соответственно с первыми входами четвертого и третьего элементов ИЛИ-НЕ, вторые входы которых соединены соответственно с первыми выводами шестого и пятого резисторов, вторые выводы которых соединены соответственно со вторыми выводами первого и второго резисторов, выходы третьего и четвертого элементов ИЛИ-НЕ через соответственно третий и четвертый конденсаторы соединены со вторыми выводами соответственно пятого и шестого резисторов, катод первого диода соединен со вторым выводом четвертого резистора, с первым выводом шестого резистора и со входом обмотки первого элемента памяти, выход которой соединен с анодом первого диода, а вывод средней точки - с первым выводом третьего резистора, катод второго диода соединен со вторым выводом третьего резистора, с первым выводом пятого резистора и со входом обмотки второго элемента памяти, выход которой соединен с анодом второго диода, а вывод средней точки - с первым выводом четвертого резистора, входы сброса и установки первого RS-триггера соединены с выходами соответственно первого и второго элементов ИЛИ-НЕ, вторые входы которых соединены со вторыми выводами соответственно первого и второго конденсаторов.

Указанная совокупность существенных признаков позволяет повысить помехоустойчивость триггерного устройства за счет запоминания его состояния с помощью дополнительных емкостных элементов памяти с последующим его восстановлением.

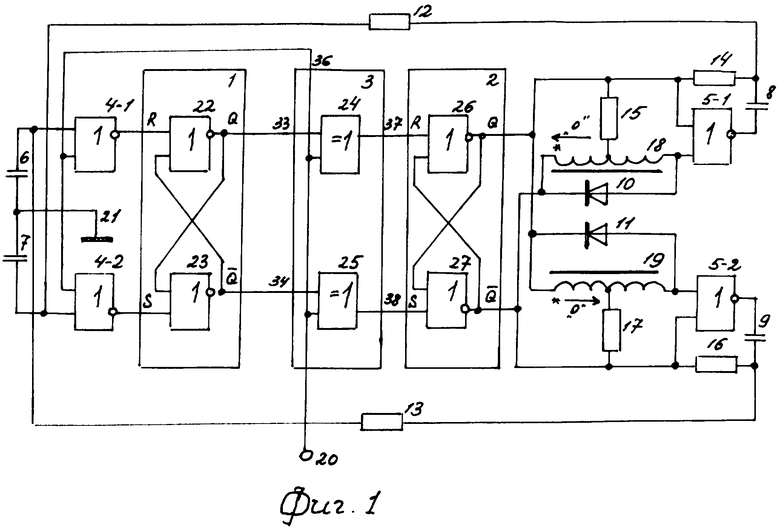

На фиг.1 представлена принципиальная электрическая схема триггерного устройства, управляемого по одной входной шине (счетное триггерное устройство). На фиг.2 представлена принципиальная электрическая схема устройства управления, позволяющего организовать RS-триггерное устройство, управляемое по двум входным шинам.

Счетное триггерное устройство (фиг.1) содержит RS-триггеры 1 и 2, устройство управления 3, логические элементы 4-1, 4-2, 5-1 и 5-2 ИЛИ-НЕ, конденсаторы 6, 7, 8 и 9, диоды 10 и 11, резисторы 12, 13, 14, 15, 16 и 17, элементы 18 и 19 памяти на магнитных сердечниках с прямоугольной петлей гистерезиса (ППГ) с одной обмоткой, имеющей отвод от средней точки, входную шину 20 и общую шину 21. Входы сброса (R-вход) и установки (S-вход) RS-триггера 1 соединены соответственно с выходами элементов 4-1 и 4-2 ИЛИ-НЕ. Прямой (Q) и инверсный  выходы RS-триггера 1 соединены соответственно с первым и вторым входами устройства управления 3, третий вход которого соединен с входной шиной 20, первый выход соединен с первыми входами элементов 4-1 и 4-2 ИЛИ-НЕ, а второй и третий выходы соединены соответственно с входами сброса и установки RS-триггера 2. Второй вход элемента 4-1 через конденсатор 6 соединен с общей шиной 21 и через резистор 13 - с точкой соединения резистора 16 и конденсатора 9. Второй вход элемента 4-2 через конденсатор 7 соединен с общей шиной 21 и через резистор 12 - с точкой соединения резистора 14 и конденсатора 8. Прямой (Q) выход RS-триггера 2 соединен со входом обмотки элемента 19 памяти, с катодом диода 11, с одним из выводов резистора 15 и со свободным выводом резистора 14. Инверсный

выходы RS-триггера 1 соединены соответственно с первым и вторым входами устройства управления 3, третий вход которого соединен с входной шиной 20, первый выход соединен с первыми входами элементов 4-1 и 4-2 ИЛИ-НЕ, а второй и третий выходы соединены соответственно с входами сброса и установки RS-триггера 2. Второй вход элемента 4-1 через конденсатор 6 соединен с общей шиной 21 и через резистор 13 - с точкой соединения резистора 16 и конденсатора 9. Второй вход элемента 4-2 через конденсатор 7 соединен с общей шиной 21 и через резистор 12 - с точкой соединения резистора 14 и конденсатора 8. Прямой (Q) выход RS-триггера 2 соединен со входом обмотки элемента 19 памяти, с катодом диода 11, с одним из выводов резистора 15 и со свободным выводом резистора 14. Инверсный  выход RS-триггера 2 соединен со входом обмотки элемента 18 памяти, с катодом диода 10, с одним из выводов резистора 17 и со свободным выводом резистора 16. Анод диода 10 соединен с выходом обмотки элемента 18 памяти и с первым входом элемента 5-1, второй вход которого соединен с прямым (Q) выходом RS-триггера 2, а выход соединен со свободным выводом конденсатора 8. Анод диода 11 соединен с выходом обмотки элемента 19 памяти и с первым входом элемента 5-2, второй вход которого соединен с инверсным

выход RS-триггера 2 соединен со входом обмотки элемента 18 памяти, с катодом диода 10, с одним из выводов резистора 17 и со свободным выводом резистора 16. Анод диода 10 соединен с выходом обмотки элемента 18 памяти и с первым входом элемента 5-1, второй вход которого соединен с прямым (Q) выходом RS-триггера 2, а выход соединен со свободным выводом конденсатора 8. Анод диода 11 соединен с выходом обмотки элемента 19 памяти и с первым входом элемента 5-2, второй вход которого соединен с инверсным  выходом RS-триггера 2, а выход соединен со свободным выводом конденсатора 9. Свободные выводы резисторов 15 и 17 соединены со средними точками соответственно элементов 18 и 19 памяти.

выходом RS-триггера 2, а выход соединен со свободным выводом конденсатора 9. Свободные выводы резисторов 15 и 17 соединены со средними точками соответственно элементов 18 и 19 памяти.

RS-триггер 1 содержит элементы 22 и 23 ИЛИ-НЕ, при этом первые входы элементов 22 и 23 являются соответственно входами сброса и установки RS-триггера 1, выходы элементов 22 и 23 являются соответственно прямым и инверсным выходами RS-триггера 1, вторые входы элементов 22 и 23 соединены соответственно с выходами элементов 23 и 22. Устройство управления 3 содержит элементы 24 и 25 "ИСКЛЮЧАЮЩЕЕ ИЛИ", при этом первые входы элементов 24 и 25 являются соответственно первым и вторым входами устройства управления 3, вторые входы элементов 24 и 25 объединены и являются третьим входом и первым выходом устройства управления 3, а выходы элементов 24 и 25 являются соответственно вторым и третьим выходами устройства управления 3. RS-триггер 2 содержит элементы 26 и 27 ИЛИ-НЕ, при этом первые входы элементов 26 и 27 являются соответственно входами сброса и установки RS-триггера 2, выходы элементов 26 и 27 являются соответственно прямым и инверсным выходами RS-триггера 2, вторые входы элементов 26 и 27 соединены соответственно с выходами элементов 27 и 26.

Устройство управления 3, позволяющее организовать RS-триггерное устройство, содержит (фиг.2) элементы 28, 29, 30 и 31 ИЛИ-НЕ, элемент 32 "ИСКЛЮЧАЮЩЕЕ ИЛИ", при этом первые входы элементов 28 и 29 являются соответственно первым (33) и вторым (34) входами устройства управления 3, а выходы соединены соответственно с первыми входами элементов 30 и 31. Второй вход элемента 29 соединен со вторым входом элемента 30, с первым входом элемента 32 и является третьим (35) входом устройства управления 3, выполняющим в триггерном устройстве роль R-входа. Выход элемента 32 является первым (36) выходом устройства управления 3. Выходы элементов 30 и 31 являются соответственно вторым (37) и третьим (38) выходами устройства управления 3. Второй вход элемента 31 соединен со вторыми входами элементов 28 и 32 и является четвертым (39) входом устройства управления 3, выполняющим в триггерном устройстве роль S-входа.

Триггерное устройство в счетном режиме работает следующим образом. При включении питания (цепи питания логических элементов 4-1, 4-2, 5-1, 5-2, 22, 23, 24, 25, 26 и 27 для упрощения на чертеже не показаны) триггерное устройство установится в состояние, соответствующее состоянию элементов 18 и 19 памяти, которое они приобрели в предыдущем цикле работы. Рассмотрим случай, когда элементы памяти 18 и 19 были намагничены в состояние "лог.0", что соответствует направлению протекания тока в обмотке элемента 18 памяти от ее средней точки к началу, а в обмотке элемента 19 памяти - от начала обмотки к ее средней точке. Входы обмоток на чертеже обозначены знаком (*). В режиме хранения информации на входной шине 20 поддерживается сигнал "лог.0". Если после включения питания RS-триггер 1 установился в нулевое состояние, при котором на его прямом (Q) выходе - сигнал "лог.0", а на инверсном выходе - сигнал "лог.1", на втором (37) и третьем (38) выходах устройства управления 3 и соответственно на R- и S-входах RS-триггера 2 установятся сигналы соответственно "лог.0" и "лог.1", устанавливающие в единичное состояние RS-триггер 2, при этом на его прямом (Q) выходе - сигнал "лог.1", на инверсном  выходе - сигнал "лог.0". Через резистор 15 и полуобмотку элемента 18 памяти потечет ток, подтверждающий нулевое состояние элемента 18 памяти, при этом на выходе обмотки этого элемента может сформироваться короткий импульс помехи положительной полярности относительно общей шины 21, связанный с непрямоугольностью петли гистерезиса сердечника элемента 18, который будет шунтирован диодом 10. Под полуобмоткой элементов 18 и 19 памяти здесь и в дальнейшем будем понимать часть обмотки соответствующего элемента памяти от ее входа до средней точки и от средней точки до выхода. На выходе элемента 5-1 установится сигнал "лог.0", поскольку на второй вход этого элемента поступает сигнал "лог.1" с Q-выхода RS-триггера 2. Конденсатор 8 начнет заряжаться через резистор 14 до напряжения, близкого к Е, в процессе заряда на втором входе элемента 4-2 - сигнал "лог.0", на S-входе RS-триггера 1 - сигнал "лог.1". Через резистор 17 и полуобмотку элемента 19 памяти потечет ток, подтверждающий нулевое состояние элемента 19 памяти, при этом на выходе обмотки этого элемента также может сформироваться короткий импульс помехи отрицательной полярности относительно напряжения питания (Е), с амплитудой, достигающей величины напряжения питания. На выходе элемента 5-2 может сформироваться короткий сигнал "лог.1", который пройдет через конденсатор 9, но будет подавлен интегрирующей цепью, составленной из резистора 13 и конденсатора 6. Постоянная времени указанной цепи выбирается с таким расчетом, чтобы подавлять короткие импульсы электрических помех, возникающих в переходных режимах работы схемы, но пропускать рабочие импульсы, формируемые при полном перемагничивании сердечников. В дальнейшем на выходе элемента 5-2 установится сигнал "лог.0", конденсатор 9 останется разряженным, на выходе элемента 4-1 и на R-входе RS-триггера 1 - сигнал "лог.1". В результате, в процессе заряда конденсатора 8 на R- и S-входах RS-триггера 1 одновременно действуют сигналы "лог.1", на его прямом и инверсном выходах установятся сигналы "лог.0", не влияющие на состояние RS-триггера 2. После заряда конденсатора 8 на втором входе элемента 4-2 установится сигнал "лог.1", на S-входе RS-триггера 1 - сигнал "лог.0", RS-триггер 1 вернется в исходное нулевое состояние. На этом переходные процессы в триггерном устройстве при его включении заканчиваются, описанное состояние триггерного устройства является устойчивым.

выходе - сигнал "лог.0". Через резистор 15 и полуобмотку элемента 18 памяти потечет ток, подтверждающий нулевое состояние элемента 18 памяти, при этом на выходе обмотки этого элемента может сформироваться короткий импульс помехи положительной полярности относительно общей шины 21, связанный с непрямоугольностью петли гистерезиса сердечника элемента 18, который будет шунтирован диодом 10. Под полуобмоткой элементов 18 и 19 памяти здесь и в дальнейшем будем понимать часть обмотки соответствующего элемента памяти от ее входа до средней точки и от средней точки до выхода. На выходе элемента 5-1 установится сигнал "лог.0", поскольку на второй вход этого элемента поступает сигнал "лог.1" с Q-выхода RS-триггера 2. Конденсатор 8 начнет заряжаться через резистор 14 до напряжения, близкого к Е, в процессе заряда на втором входе элемента 4-2 - сигнал "лог.0", на S-входе RS-триггера 1 - сигнал "лог.1". Через резистор 17 и полуобмотку элемента 19 памяти потечет ток, подтверждающий нулевое состояние элемента 19 памяти, при этом на выходе обмотки этого элемента также может сформироваться короткий импульс помехи отрицательной полярности относительно напряжения питания (Е), с амплитудой, достигающей величины напряжения питания. На выходе элемента 5-2 может сформироваться короткий сигнал "лог.1", который пройдет через конденсатор 9, но будет подавлен интегрирующей цепью, составленной из резистора 13 и конденсатора 6. Постоянная времени указанной цепи выбирается с таким расчетом, чтобы подавлять короткие импульсы электрических помех, возникающих в переходных режимах работы схемы, но пропускать рабочие импульсы, формируемые при полном перемагничивании сердечников. В дальнейшем на выходе элемента 5-2 установится сигнал "лог.0", конденсатор 9 останется разряженным, на выходе элемента 4-1 и на R-входе RS-триггера 1 - сигнал "лог.1". В результате, в процессе заряда конденсатора 8 на R- и S-входах RS-триггера 1 одновременно действуют сигналы "лог.1", на его прямом и инверсном выходах установятся сигналы "лог.0", не влияющие на состояние RS-триггера 2. После заряда конденсатора 8 на втором входе элемента 4-2 установится сигнал "лог.1", на S-входе RS-триггера 1 - сигнал "лог.0", RS-триггер 1 вернется в исходное нулевое состояние. На этом переходные процессы в триггерном устройстве при его включении заканчиваются, описанное состояние триггерного устройства является устойчивым.

Если после включения питания RS-триггер 1 установился в состояние "лог.1" (на его выходе Q сигнал "лог.1"), RS-триггер 2 установится в нулевое состояние (на его выходе Q сигнал "лог.0"). В этом случае ток через обмотку элемента 18 памяти потечет от ее начала к средней точке, элемент 18 памяти начнет перемагничиваться в противоположное (единичное) состояние, при этом на выходе обмотки этого элемента сформируется импульс напряжения отрицательной полярности относительно напряжения питания (Е) с амплитудой, определяемой соотношением числа витков в полуобмотках элемента 18 памяти и величиной сопротивления резистора 15. Длительность импульса равна времени перемагничивания сердечника элемента 18 памяти. Величины сопротивлений резисторов 15 и 17 выбираются с таким расчетом, чтобы при перемагничивании сердечников в полуобмотках элементов 18 и 19 памяти, подключенных к источнику сигнала, возникал импульс напряжения с амплитудой, примерно равной Е/2; при равном числе витков в полуобмотках элементов 18 и 19 памяти на выходе соответствующей обмотки амплитуда импульса напряжения будет близка к величине Е. Следовательно, на обоих входах элемента 5-1 будут присутствовать сигналы "лог.0", на выходе указанного элемента появится сигнал "лог.1", который через конденсатор 8 поступит на второй вход элемента 4-2 и сформирует сигнал "лог.0" на S-входе RS-триггера 1. Ток через обмотку элемента 19 памяти потечет через резистор 17 от средней точки к началу обмотки, при этом на выходе указанной обмотки сформируется импульс положительной полярности относительно общей шины 21, который будет шунтирован диодом 11. Поскольку на втором входе элемента 5-2 поддерживается сигнал "лог.1", на его выходе - сигнал "лог.0", конденсатор 9 начинает заряжаться через резистор 16 до напряжения, близкого к Е. В процессе заряда на выходе элемента 4-1 и на R-входе RS-триггера 1 присутствует сигнал "лог.1". RS-триггер 1 под действием указанных сигналов переключится в нулевое состояние и вызовет переключение в единичное состояние RS-триггера 2, изменятся направления токов в полуобмотках элементов 18 и 19 памяти, при этом будет подтверждаться первоначальное состояние их намагниченности. В дальнейшем переходные процессы в триггерном устройстве связаны с зарядом конденсатора 8 через резистор 14, как это было уже описано выше, при этом в процессе заряда на R- и S-входах RS-триггера 1 присутствуют сигналы "лог.1", после заряда конденсатора 8 RS-триггер 1 возвратится в нулевое состояние. Таким образом, произойдет восстановление состояния триггерного устройства в соответствии с состоянием элементов 18 и 19 памяти, и, как было показано выше, это состояние триггерного устройства является устойчивым. Аналогичным образом триггерное устройство при включении питания принимает состояние "лог.1", если элементы 18 и 19 памяти были предварительно намагничены в состояние "лог.1".

Для переключения триггерного устройства на входную шину 20 подается тактовый сигнал с уровнем "лог.1". Этот же сигнал с выхода 36 устройства управления 3 поступает на входы элементов 4-1 и 4-2 ИЛИ-НЕ, на их выходах будут постоянно удерживаться сигналы "лог.0", обеспечивая нахождение RS-триггера 1 в состоянии, которое он имел до поступления тактового сигнала. Элементы 24 и 25 начинают работать в режиме инверторов, обеспечивая переключение RS-триггера 2 в состояние, противоположное тому, которое он имел до поступления тактового сигнала. Пусть, например, в исходном состоянии RS-триггеры 1 и 2 находились в состояниях соответственно "лог.0" и "лог.1" (нулевое состояние триггерного устройства). При подаче тактового сигнала на входную шину 20 на выходах элементов 24 и 25 появятся сигналы соответственно "лог.1" и "лог.0", RS-триггер 2 переключится в нулевое состояние (сигнал "лог.0" на выходе Q и сигнал "лог.1" на выходе Q). Под действием токов, протекающих через полуобмотки элементов 18 и 19 памяти, указанные элементы перемагничиваются в состояние "лог.1", при этом импульсы, возникающие на выходах обмоток этих элементов, не проходят на R- и S-входы RS-триггера 1, так как на последних в этом режиме поддерживается сигнал "лог.0". Длительность тактового сигнала должна быть достаточной для полного перемагничивания сердечников элементов 18 и 19 памяти и перезаряда конденсаторов 8 и 9 через резисторы соответственно 14 и 16 в соответствии с новым состоянием RS-триггера 2. После окончания тактового сигнала на шине 20 сигналы на выходах 37 и 38 устройства управления 3 изменятся на противоположные, вследствие этого RS-триггер 2 переключится в единичное состояние, изменятся направления токов в полуобмотках элементов 18 и 19 памяти. На выходе обмотки элемента 18 памяти появится импульс положительной полярности относительно общей шины 21, который шунтируется диодом 10. На выходе элемента 5-1 - сигнал "лог.0", который передается через конденсатор 8 на второй вход элемента 4-2 и вызывает появление сигнала "лог.1" на S-входе RS-триггера 1.

Одновременно с этим на выходе обмотки элемента 19 памяти появится импульс отрицательной полярности относительно напряжения питания (Е), который вызовет появление сигнала "лог.1" на выходе элемента 5-2. Указанный сигнал вызовет появление "лог.0" на R-входе RS-триггера 1. В результате RS-триггер 1 переключится в состояние "лог.1" и вызовет переключение RS-триггера 2 в состояние "лог.0". Токи в полуобмотках элементов 18 и 19 памяти изменятся на противоположные и будут соответствовать направлению их намагниченности. Короткий импульс помехи положительной полярности, возникающий на выходе обмотки элемента 18 памяти вследствие непрямоугольности петли гистерезиса его сердечника и частичного размагничивания его сердечника, будет подавлен интегрирующей цепью, составленной из резистора 12 и конденсатора 7, поэтому не окажет влияния на состояние схемы. На этом процесс переключения триггерного устройства заканчивается, оно переходит в новое устойчивое состояние. Аналогичным образом происходит процесс переключения триггерного устройства очередным тактовым сигналом из состояния "лог.1" в состояние "лог.0".

Организация работы RS-триггерного устройства осуществляется с помощью устройства управления 3, представленного на фиг.2. В режиме хранения информации на R-входе (вход 35) и на S-входе (вход 39) устройства управления 3 - сигналы "лог.0", поэтому сигналы со входа 33 на выход 37 и со входа 34 на выход 38 устройства управления передаются в режиме повторителей, на выходе элемента 32 "ИСКЛЮЧАЮЩЕЕ ИЛИ" и на выходе 36 устройства управления 3 - сигнал "лог.0". В результате триггерное устройство в режиме хранения информации функционирует точно так же, как было описано выше. При необходимости установить триггерное устройство в единичное состояние на его входную шину 40 подается сигнал "лог.1", в результате на выходе элемента 32 появляется сигнал "лог.1", блокирующий элементы 4-1 и 4-2 с состояниях с "лог.0" на их выходах; на выходе элемента 30 и на выходе 37 устройства управления 3 появляется сигнал "лог.1", поступающий на R-вход RS-триггера 2; на выходе элемента 31 появляется сигнал "лог.0", поступающий на S-вход RS-триггера 2. RS-триггер 2 установится в нулевое состояние, при этом в обмотках записи элементов 18 и 19 памяти потекут токи, соответствующие намагниченности сердечников этих элементов в состояние "лог.1". Одновременно с перемагничиванием элементов 18 и 19 памяти произойдет перезаряд конденсаторов 8 и 9 (если до этого триггерное устройство находилось в состоянии "лог.1"), длительность сигнала на шине 40 должна быть достаточной для завершения указанных процессов. После снятия сигнала установки с шины 40 RS-триггер 1 установится в состояние "лог.1" сигналом "лог.0", формируемым на выходе цепи, составленной из резистора 14 и конденсатора 8, после перезаряда конденсатора 8. Это состояние триггерного устройства является устойчивым.

При необходимости установить триггерное устройство в нулевое состояние на его входную шину 20 подается сигнал "лог.1". В результате, на выходе элемента 32 "ИСКЛЮЧАЮЩЕЕ ИЛИ" появляется сигнал "лог.1", блокирующий элементы 4-1 и 4-2 в состояниях с "лог.0" на их выходах, на выходе элемента 30 (выход 37) появляется сигнал "лог.0", на выходе элемента 31 (выход 38) - сигнал "лог.1". RS-триггер 2 переключится в единичное состояние, при этом в обмотках записи элементов 18 и 19 памяти потекут токи, соответствующие намагниченности сердечников этих элементов в состояние "лог.0". Одновременно с перемагничиванием элементов 18 и 19 памяти происходит перезаряд конденсаторов 8 и 9 (если до этого триггерное устройство находилось в состоянии "лог.0"). После снятия сигнала сброса с шины 20 RS-триггер 1 установится в состояние "лог.0" сигналом, формируемым на выходе цепи, составленной из резистора 16 и конденсатора 9, после перезаряда конденсатора 9. Это состояние триггерного устройства также является устойчивым.

Восстановление состояния триггерного устройства, находящегося в режиме хранения информации, в случае его сбоя под действием помехи осуществляется импульсами с выходов соответствующих обмоток считывания в соответствии с состояниями элементов 18 и 19 памяти, а при помехах, длительность которых превышает время перемагничивания сердечников элементов 18 и 19 памяти, - за счет энергии, накопленной в конденсаторах 8 и 9. Длительность допустимой помехи в этом случае определяется постоянными времени цепей, составленных из резисторов 14 и 16 и конденсаторов 8 и 9.

Таким образом, как следует из описания работы триггерного устройства, оно автоматически восстанавливает информацию в условиях воздействия электрических помех, длительность которых превышает время перемагничивания элементов 18 и 19 памяти, следовательно, это триггерное устройство обладает более высокой помехоустойчивостью.

Испытания лабораторного макета триггерного устройства подтвердили осуществимость и практическую ценность заявляемого устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| ТРИГГЕРНОЕ УСТРОЙСТВО | 2003 |

|

RU2250554C1 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 2003 |

|

RU2248663C1 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 2003 |

|

RU2250555C1 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 2002 |

|

RU2248662C2 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 1983 |

|

SU1145890A1 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 2003 |

|

RU2237967C1 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 2003 |

|

RU2250556C1 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 2001 |

|

RU2207716C2 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 1995 |

|

RU2106742C1 |

| ЭНЕРГОНЕЗАВИСИМАЯ ЯЧЕЙКА ПАМЯТИ | 1999 |

|

RU2215337C2 |

Изобретение относится к области импульсной техники. Технический результат заключается в повышении помехоустойчивости в условиях высокоинтенсивных электрических помех большой длительности. Триггерное устройство содержит RS-триггер (1, 2) на элементах ИЛИ-НЕ (22, 23, 26, 27), элементах ИЛИ-НЕ (4-1, 4-2, 5-1, 5-2), устройства управления (3), диоды (10, 11), резисторы (Р) (12-17), конденсаторы (6-9), элементы памяти на магнитных сердечниках с прямоугольной петлей гистерезиса (ЭП) (18, 19), имеющие отводы от средней точки, соединенные с Р (15, 17), по крайней мере, одну входную шину (20) и общую шину (21). Технический результат достигнут выполнением обмоток записи и считывания ЭП (18, 19) в виде одной обмотки с выводом ее средней точки и введением новых связей между элементами. 2 ил.

Триггерное устройство, содержащее первый RS-триггер, устройство управления с, по крайней мере, тремя входами и тремя выходами, при этом первый и второй входы устройства управления соединены соответственно с прямым и инверсным выходами первого RS-триггера, третий вход - с входной шиной, а первый выход - с первыми входами первого и второго элементов совпадения, вторые входы которых соединены с первыми выводами соответственно первого и второго резисторов, первый и второй конденсаторы, первые выводы которых соединены с общей шиной, первый и второй элементы памяти на магнитных сердечниках с прямоугольной петлей гистерезиса, каждый из которых имеет, по крайней мере, одну обмотку, один из выводов обмотки первого и второго элементов памяти соединен с первым выводом соответственно третьего и четвертого резисторов, пятый и шестой резисторы, отличающееся тем, что первый и второй элементы совпадения выполнены в виде соответственно первого и второго элементов ИЛИ-НЕ, введены первый и второй диоды, третий и четвертый конденсаторы, третий и четвертый элементы ИЛИ-НЕ, второй RS-триггер, входы сброса и установки которого соединены соответственно со вторым и третьим выходами устройства управления, а прямой и инверсный выходы - с катодами соответственно второго и первого диодов, аноды которых соединены соответственно с первыми входами четвертого и третьего элементов ИЛИ-НЕ, вторые входы которых соединены соответственно с первыми выводами шестого и пятого резисторов, вторые выводы которых соединены соответственно со вторыми выводами первого и второго резисторов, выходы третьего и четвертого элементов ИЛИ-НЕ через соответственно третий и четвертый конденсаторы соединены со вторыми выводами соответственно пятого и шестого резисторов, катод первого диода соединен со вторым выводом четвертого резистора, с первым выводом шестого резистора и со входом обмотки первого элемента памяти, выход которой соединен с анодом первого диода, а вывод средней точки - с первым выводом третьего резистора, катод второго диода соединен со вторым выводом третьего резистора, с первым выводом пятого резистора и со входом обмотки второго элемента памяти, выход которой соединен с анодом второго диода, а вывод средней точки - с первым выводом четвертого резистора, входы сброса и установки первого RS-триггера соединены с выходами соответственно первого и второго элементов ИЛИ-НЕ, вторые входы которых соединены со вторыми выводами соответственно первого и второго конденсаторов.

| ТРИГГЕРНОЕ УСТРОЙСТВО | 1995 |

|

RU2106742C1 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 1990 |

|

SU1753919A1 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 2001 |

|

RU2207716C2 |

| US 3786282, 15.01.1974 | |||

| КАРКАСНЫЙ АРБОЛИТ | 2000 |

|

RU2243188C2 |

Авторы

Даты

2005-04-20—Публикация

2003-09-29—Подача