Изобретение относится к технике связи, может использоваться в системах передачи дискретной информации и является усовершенствованием известного изобретения, описанного в авт. св. N 502518. По основному авт. св. N 502518 известен демодулятор дискретных сигналов с фазоразностной модуляцией, содержащий входные ключевые перемножителн, соединенные с соответствующими интеграторами-сумматорами и подключенные управляющими входами к выходам компараторов, на сигнальные входы которых поданы сигналы, задержанные на одну посылку, а управляюише входы подключены к выходу генератора линейно изменяющего ся напряжения и сумматсфы аналоговых вели чин, входы которых подключены к выходам соответствующих интеграторов-сумматоров, а выходы - к решающему блоку, содержащий также блок вычисления модулей входных сигналов, соединенный с дополните;а ш 1М сумматором, выход которото подключен к генера тору линейно изменяющегося напряжения {1. Однако известный демодулятор дискретных сигналов имеет низкую помехоустойчивость. Цель изобретеття - повышение помехоустойчивости. Для зтого в известный демодулятор дискретных сигиалов с фазоразностной модуляцией, содержащий входные ключевые перемножнтелн, соединенные с соответствующими интеграторами-сумматорамн н подключенные управляющнми входами к выходам компараторов, на снгнальные входы которых поданы снгиалы, задержанные на одну посылку, а управляющие входа, подключены к выходу генератора линейно изменяющегося напряжения, и сумматоры аналоговых величин, входы которых подключены к выходам соответств)аощих интеграторов-сумматоров, а выходы - к решающему блоку, содержащий также блок вычисления модулей входных сигналов, соединенный с допошсительным сумматором, выход которого подключен к генератору линейно нзменяющегося напряжения, введены пороговые детекторы, аналоговые ключи н вычитающий блок, выход которого подключен к первым входам

ороговых детекторов, выходы которых соеинены с управляющими входами соответству- . щих аналоговых ключей, сигнальные входы выходы которых соединены соответственно выходами интеграторов-сумматоров и входаи сумматоров аналоговых величин. При этом ыходы дополнительных сумматоров подклюены к входам вычитающего блока, а вторые ходы пороговых детекторов являются управяющими входами.

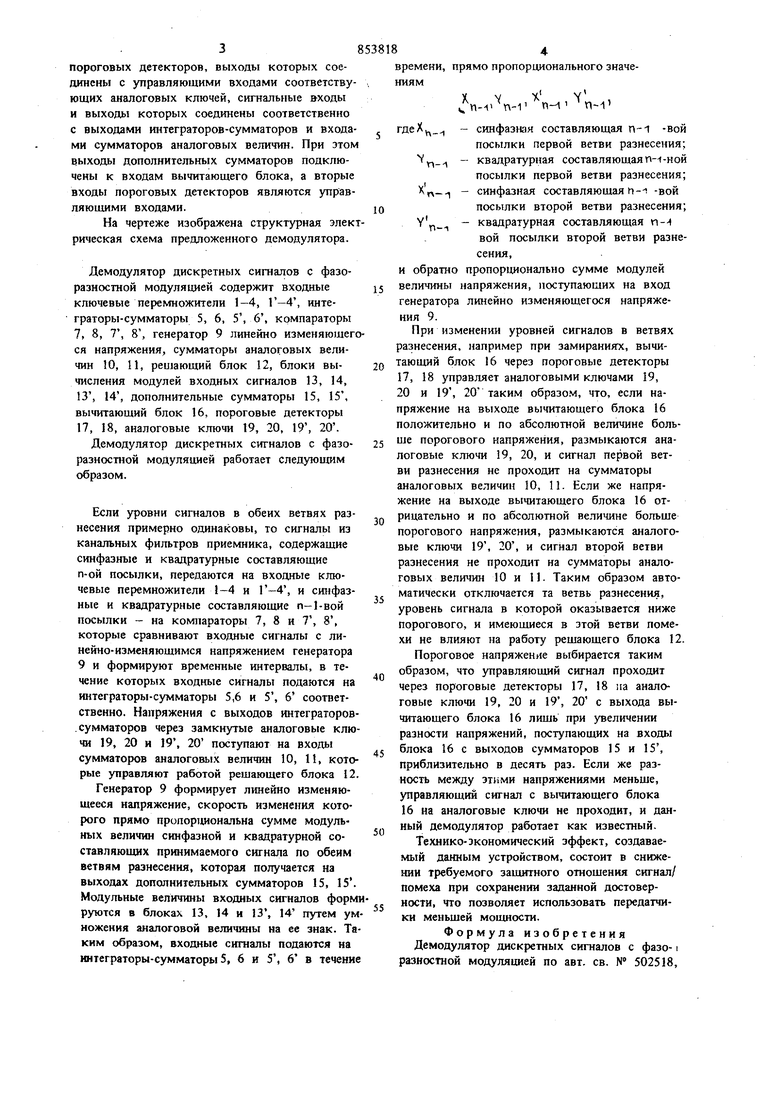

На чертеже изображена структурная электрическая схема предложенного демодулятора.

Демодулятор дискретных сигналов с фазоразностной модуляцией содержит входные ключевые пертемножители 1-4, Г-4, интеграторы-сумматоры 5, 6, 5, 6, крмпараторы 7, 8, 7, 8, генератор 9 линейно изменяющегося напряжения, сумматоры аналоговых величин 10, 11, решающий блок 12, блоки вычисления модулей входных сигналов 13, 14, 13, 14, дополнительные сумматоры 15, 15, вычитающий блок 16, пороговые детекторы 17, 18, аналоговые ключи 19, 20, 19, 20.

Демодулятор дискретных сигналов с фазоразностной модуляцией работает следующим образом.

Если уровни сигналов в обеих ветвях разнесения примерно одинаковы, то сигналы из канальных фильтров приемника, содержащие синфазные и квадратурные составляющие п-ой посылки, передаются на входные ключевые перемножители 1-4 и Г-4, и синфазные и квадратурные составляющие п-1-вой посылки - на компараторы 7, 8 и 7, 8, которые сравнивают входные сигналы с линейно-изменяющимся напряжением генератора 9 и формируют временные интервалы, в течение которых входные сигналы подаются на интеграторы-сумматоры 5,6 и 5, 6 соответственно. Напряжения с выходов интеграторов. сумматоров через замкнутые аналоговые ключи 19, 20 и 19, 20 поступают на входы сумматоров аналоговых величин 10, 11, которые управляют работой рещающего блока 12.

Генератор 9 формирует линейно изменяющееся напряжение, скорость изменения которого прямо пропорциональна сумме модульных величин синфазной и квадратурной составляющих принимаемого сигнала по обеим ветвям разнесения, которая получается на выходах дополнительных сумматоров 15, 15. Модульные величины входных сигналов формируются в блоках 13, 14 и 13, 14 путем умножения аналоговой величины на ее знак. Таким образом, входные сигналы подаются на интеграторы-сумматоры 5, 6 и 5, 6 в течение

прямо пропорционального значеч:

tt. ПП-1

гдеХу - синфазная составляющая п-1 -во посылки первой ветви разнесения квадратурная составляющая п-(-но

посылки первой ветви разнесения

синфазная составляющая n-i -вой

rv-i посылки второй ветви разнесения

Y квадратурная составляющая nп-1вой посылки второй ветви разнесения,

и обратно пропорционально сумме модулей величины напряжения, поступающих на вход генератора линейно изменяющегося напряжения 9.

При изменении уровней сигналов в ветвях разнесения, например при замираниях, вычитающий блок 16 через пороговые детекторы 17, 18 управляет аналоговыми ключами 19, 20 и 19, 20 таким образом, что, если напряжение на выходе вычитающего блока 16 положительно и по абсолютной величине больше порогового напряжения, размыкаются аналоговые ключи 19, 20, и сигнал первой ветви разнесения не проходит на сумматоры аналоговых величин 10, 11. Если же напряжение на выходе вычитающего блока 16 отрицательно и по абсолютной величине больше порогового напряжения, размыкаются аналоговые ключи 19, 20, и сигнал второй ветви разнесения не проходит на сумматоры аналоговых величин 10 и 11. Таким образом автоматически отключается та ветвь разнесения, уровень сигнала в которой оказывается ниже порогового, и имеющиеся в этой ветви помехи не влияют на работу решающего блока 12

Пороговое напряжение выбирается таким образом, что управляющий сигнал проходит через пороговые детекторы 17, 18 иа аналоговые ключи 19, 20 и 19, 20 с выхода вычитающего блока 16 лишь при увеличении разности напряжений, поступающих на входы блока 16 с выходов сумматоров 15 и 15, приблизительно в десять раз. Если же разность между этими напряжениями меньше, управляющий сигнал с вычитающего блока 16 на аналоговые ключи не проходит, и данный демодулятор работает как известный.

Технико-экономический эффект, создаваемый данным устройством, состоит в снижении требуемого защитного отношения сигнал/ помеха при сохранении заданной достоверности, что позволяет использовать передатчики меньшей мощности.

Формула изобретения Демодулятор дискретных сигналов с фазо-1 разностной модуляцией по авт. св. N 502518,

| название | год | авторы | номер документа |

|---|---|---|---|

| Демодулятор дискретных сигналов с фазоразностной модуляцией | 1982 |

|

SU1107325A1 |

| Демодулятор сигналов с фазоразностной модуляцией | 1978 |

|

SU720782A1 |

| СИСТЕМА ВЫСОКОСКОРОСТНОЙ ДЕКАМЕТРОВОЙ РАДИОСВЯЗИ | 2014 |

|

RU2608554C2 |

| Частотный дискриминатор | 1980 |

|

SU984020A1 |

| Устройство для детектирования сигналов с фазоразностной манипуляцией | 1978 |

|

SU769759A1 |

| АВТОМАТИЗИРОВАННОЕ УСТРОЙСТВО ПОВЫШЕНИЯ КАЧЕСТВА КАНАЛА ПЕРЕДАЧИ ДАННЫХ | 2014 |

|

RU2603493C2 |

| Демодулятор сигналов с фазоразностной модуляцией | 1978 |

|

SU790361A1 |

| Демодулятор дискретных сигналов с фазоразностной модуляцией | 1974 |

|

SU502518A1 |

| Автокорреляционный демодулятор псевдослучайных сигналов с относительной фазовой модуляцией второго порядка | 2017 |

|

RU2660594C1 |

| СПОСОБ ДЕМОДУЛЯЦИИ СИГНАЛОВ С ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ МАНИПУЛЯЦИЕЙ И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2000 |

|

RU2168869C1 |

Авторы

Даты

1981-08-07—Публикация

1979-11-16—Подача