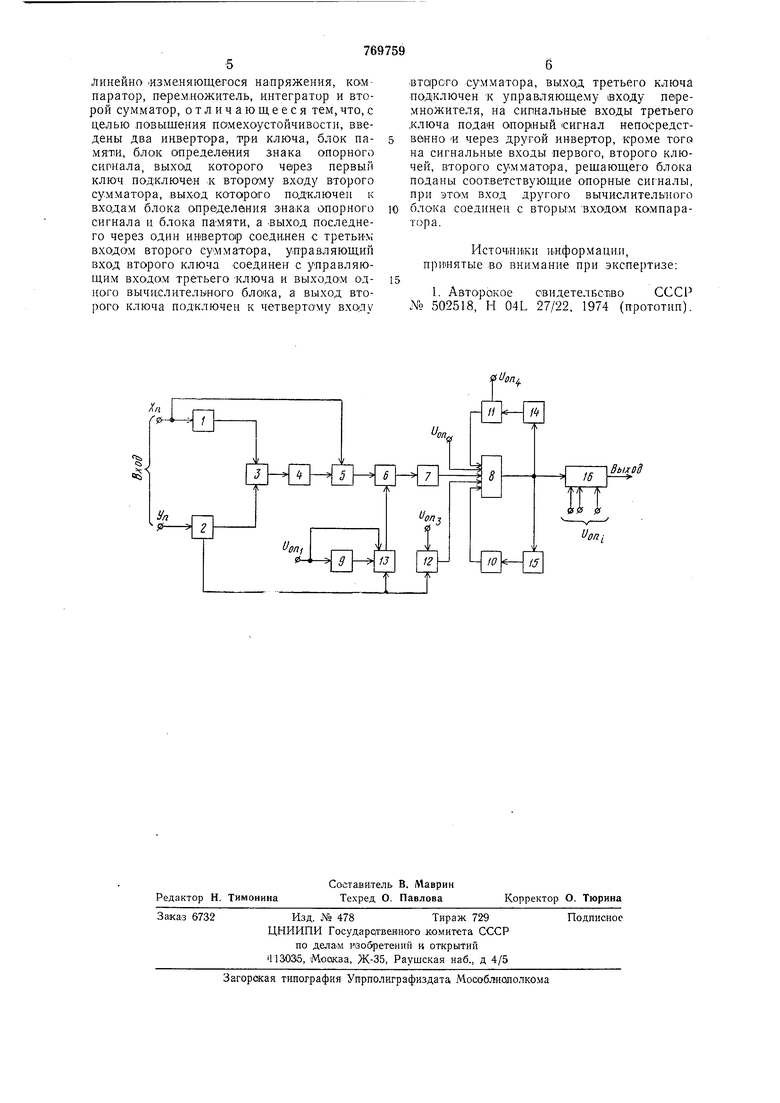

леиия знака олроногосигнала, блок 15 памяти, решающий блок 16.

Устройство работает следующим образом.

Поступающие на вход устройства из блока вычисления карреляции (неиоказанного иа чертеже) сиифаз.ная и квадратурная составляющие сигнала принимаемой посылки понадают на соответствующие вычислительные блоки 1, 2. Выходы вычислительных блоков 1, 2 объединены иа суммато;ре 3, в :котор0м определяют сумму модулей этих составляющих.

Сигнал с выхода сумматора 3 управляет генератором 4 Лииейио изменяю1дего1ся напрял- ения, где заданной величине наиряжения ставится в соответствие наклон прямой нропорцисхнального изменения напряжения. Это, изменяющее но линейному закону -напряжение из генератора 4, по падает со1вместио со значением одной из составляющих сигнала на компаратор 5, где по соиоставлению -напряжений, нодаваемых на его входы вырабатывают интервал времени т (фп ), пропорциональный фазе принимаемой иосылки (фп).

Далее, во временнам интервале, прямо пропорциональном одной из составляющих входного сигнала и обратно пропорциоиальном сумме модулей обеих составляющих входного сигнала, на перемнол ителе 6 производят перемножение опорного напряжения, которое подают через ключ 13 непосредственно или через инвертор 9, iB зависимости от знака другой составляющей входного сигнала. Знак иостулает из вычислительного блока 2. Напряжение с выхода иеремножштеля 6 ири обрабо тке принимаемой посылки нака-пливается за оговоренный нромежутак времени интегратором 7, нропорцианальным функции f (фп ) Такое же нaпpяJkeниe ифп-.i fa (фп-i ) для задержаииой посылки получают далее за счет хранения ранее вычисленного иапряжения в блоке 15. памяти.

На второй сумматор 8 аналоговых велич1И1Н кроме напряжения с выхода интегратора 7 подают целый ряд других напряжений. Перемножитель 6 « второй сумматор 8 позволяют произвести все необходимые вычисления по определению разности фаз (ифп - ифп-1 ). При этом опорное напряжение U опг f (0) поступает непосредственно на второй сумматор 8, опориое напряжение U опз 2f (0) подают через управляемый знаком другой составляющей входного сигнала, который поступает из вычИслительното блока 2, второй ключ 12, опорное напряжение Оощ 4i (0) приходит на вход второго сумматора 8 через -первый ключ 11, управляемый блоком 14 определения знака, котОрый в зависимости от знака напряжения на выходе второго сум.матора 8 соответствующим образом включает это опорное напряжение.

Запомненное в блоке 15 памяти напряжение, пропорциональное задержаи-ной посылке через Инвертор 10 с зиаком нротивоположнЫМ вычисленному подают на второй сумматор 8, тем самым вычитая его из вычисленного, поступающего на второй сум-матор 8 из интегратора 7.

Следует отметить, что асе иеречислениые onqpHbie напряжения на схеме могут быть поданы от одного источника onoppfiro наиряжеиия через общий делитель напряжений, выполняющий необходимое масщтабиравание иапряжений под конкретные параметры вычислительных схем.

Обработку сигнала в данном устройстве производят последовательно во времени, что, KaiK указывалось, невозможно осуществить в устройотве-протоггипе. Очевидно, что последовательная обработка сама по себе несет существенную экономию оборудования, кроме того, поЗ(Воляет почти урав|Нять вычислительные попрещ ности при обработке принимаемой и воссоздании задержаииой посылки.

С выхода второго сумматора 8 напряжение, пропорциональное разности фаз соседних посылок подают иа решающий блок 16, где производится сравнение полученного Напряжения с этало.иами напряжений, проиорцнональньши заданным углам манипуляции, и на основа-НИИ порогового решения выявляют переданные символы информации.

По существу вычисления в решающем блоке 16 СВОДЯТСЯ к установлению однозначного соответствия между полученным яапряжением пропарциаиальным сум-марной угловой мере, с совокунностью т вариантов разностей фаз, априорно известных на нриеме. Объем совокупности вариантов разности фаз, в общем случае, определяется кратностью маиипуляции и видом манипуляционного кода, заложенного «а передаче.

Таким образом, введеиие в объекты новых, атличиых от прототипа операций и изменение структурной схемы устройства позволяют расширить динамический диапазон приемника, и тем самым улучшить его иомехоустойчивость.

Кроме того, достигнута универсальность устройства блатодаря возможности приема фазома ииул.ироваииых сигналов с нроизвольной кратностью манипуляции и любым манинуляционньм кодом.

Формула изобретения

Устройство для детектирования сигналов с фазоразностной манипуляцией, содержащее вычислительные блоки, соединенные с первым сумматором, выход которого подключен к рещающему блоку через последовательно соединенные генератор

Линейно изменяющегося напряжения, комнаратор, перем.ножитель, интегратор и второй сумматор, отличающееся тем,что,с целью ловыщения помехоустойчивости, введены два инвертора, три ключа, блок намяти, блок определения знака опорного сирнала, выход которого через первый ключ подключен .к второму входу второго сумматора, выход которого подключен к входам блока определения Зна1ка опорного сигнала и блока памяти, а -выход последнего через один инвертор соедилен с третьил; входом второго сумматора, управляющий вход второго ключа соединен с управляющим входом третьего Ключа и выходом одного вычислителиного блока, а выход второго ключа подключен к четвертому вхолу

6

второго сумматора, выход третьего ключа подключен К управляющему входу перемножителя, на сипнальные входы третьего .ключа подшн опорный сигнал непосредственно И через другой инвертор, кроме того на сигнальные входы первого, второго ключей, второго сумматора, рещающего блока поданы соответствующие опорные сигналы, при этом вход другого вычислительного блока соединен с вторым входом компаратора.

Ист04iHи ки И|Нформади.и, принятые во внимание при экспертизе:

I. Авторокое овидетелБство СССР № 502518, Н 04L 27/22, 1974 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для детектирования дискретных сигналов с фазоразностной манипуляцией | 1978 |

|

SU786046A1 |

| Многоканальный модулятор-демодулятор с фазоразностной модуляцией | 1985 |

|

SU1282350A1 |

| Частотно-фазовый дискриминатор | 1978 |

|

SU758559A1 |

| Демодулятор сигналов с фазоразностной модуляцией | 1984 |

|

SU1216834A1 |

| Корреляционный демодулятор сигналов с угловой модуляцией | 1983 |

|

SU1166338A1 |

| Многолучевая система радиосвязи | 1979 |

|

SU801280A1 |

| Демодулятор дискретных сигналовС фАзОРАзНОСТНОй МОдуляциЕй | 1979 |

|

SU853818A2 |

| Синхронный приемник фазоманипулированных сигналов | 1978 |

|

SU771887A1 |

| Демодулятор фазоманипулированных сигналов с компенсацией помех | 1987 |

|

SU1545332A1 |

| Анализатор сигнала тактовой синхронизации | 1982 |

|

SU1125763A2 |

Вылод

Авторы

Даты

1980-10-07—Публикация

1978-10-18—Подача