(54) двоичный УМНО/КИТЕЛЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

| Устройство для умножения | 1990 |

|

SU1753471A1 |

| Устройство для адресации процессора быстрого преобразования Фурье | 1985 |

|

SU1298765A1 |

| Устройство для умножения 12N-разрядных двоичных чисел | 1988 |

|

SU1589271A1 |

| Устройство для умножения | 1985 |

|

SU1278838A1 |

| ДВОИЧНЫЙ УМНОЖИТЕЛЬ | 1992 |

|

RU2006918C1 |

| Вычислительное устройство | 1983 |

|

SU1080137A1 |

| Масштабно-временной преобразователь | 1982 |

|

SU1045218A1 |

| Множительно-делительное устройство | 1978 |

|

SU746511A1 |

| Генератор функций | 1984 |

|

SU1241219A1 |

1

Изобретение относится к вычисли- тельной технике и автоматике и может

быть применено в устройствах, выполняющих математические операции, и в устройствах управления, например устройствах числового nporpcJMмного управления станками.

Известно устройство, содержащее счетчик, дифференцирующие каскады, элементы селекции импульсных последовательностей, элемент ИЛИ и позволяющее производить умножение частоты импульсной последовательности на число, пропорциональное множителю, записанному параллельным . кодом i .

Однако применение дифференцирующих каскадов неудобно при современной элементной базе, крометого, выходные импульсы умножителя не синхронизированы импульсами исходной последовательности, что в ряде случаев требует введения устройст- , ва синхронизации.

Наиболее близким по технической сущности и достигаемому результату является устройство, содержсццее источник исходной импульсной последовательности, двоичный счетчик, элементы И, элемент ИЛИ, мультивибратор, элементы задержки, триггер обратной связи, причем источник исходной импульсной последовательности подключен ко входу мультивиВратора, счетному входу счетчика и входу синхррнизации триггера обратной связи, прямые выходы разрядов счетчика подключены к первым входам элементов И, кодовая шина множителя - ко вторым входам элементов И, выход мультивибратора к цепи элементов задержки, выходы . которых подключены к третьим входам элементов И, выход триггера обратной связи - к четвертым входам элементов И, а инверсные, выходы счетчика подключены к последующим входам элементов И всех последующих разрядов 2 .

Однако данное устрюйство является сложным, имеет нерегулярную по разрядам структуру и, кроме того, содержит элементы з&держки, что затрудняет его вьтолнение при современной элементной базе.

Цель изобретения - упрощение устройства и повышение регулярности его структуры.

Поставленная цель достигается тем, что в двоичный умножитель, содержа30 ВДИй п счетных триггеров (п - разрядность умножителя)/первую группу элементов И, при этом первые входы i-x элементов И первой группы (, , . . ,п) соединены с входг ми соответственно (n-i+1)-x разрядов кода множителя, вторые входы - с нулевыми выходами i-X счетных триггеров, а выходы - с соответствующими входами элементов ИЛИ, выход которого является выходом устройства, счетные входы счетных триггеров соединены с входом прямой импульсной последовательности умножителя, введена вторая группа элементов И, причем первые входы i-x элементов И второй группы соединены с единичными выходами соответствующих счетных триггеров, выход каждого j-ro элемента И второй группы (j 1,...,п-1) соединен со BTopHfJi входом (j + 1)-ro элемента И второй группы, входом управления (j+1)-ro счетного триггера и третьим входом (J + O-ro элемента И первой группы, четвертые входы (j+1)-x и третий вход первого элементов И первой группы соединены со входом инверсной импульсной последовательности умножителя.

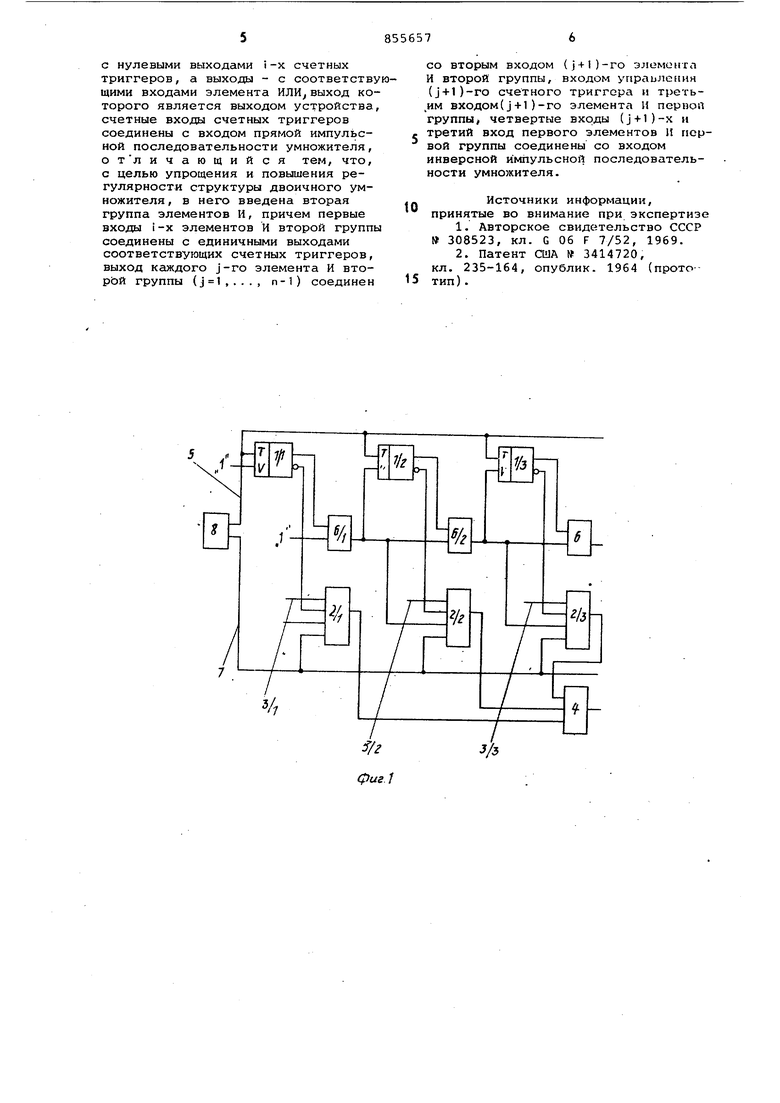

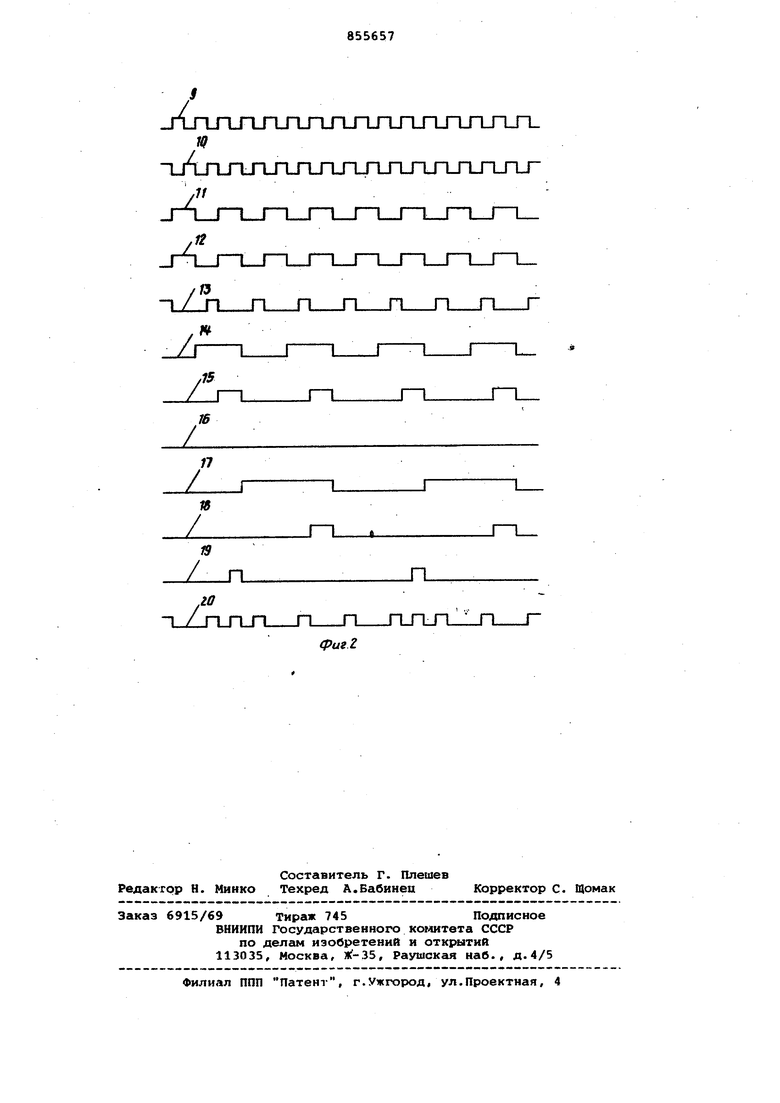

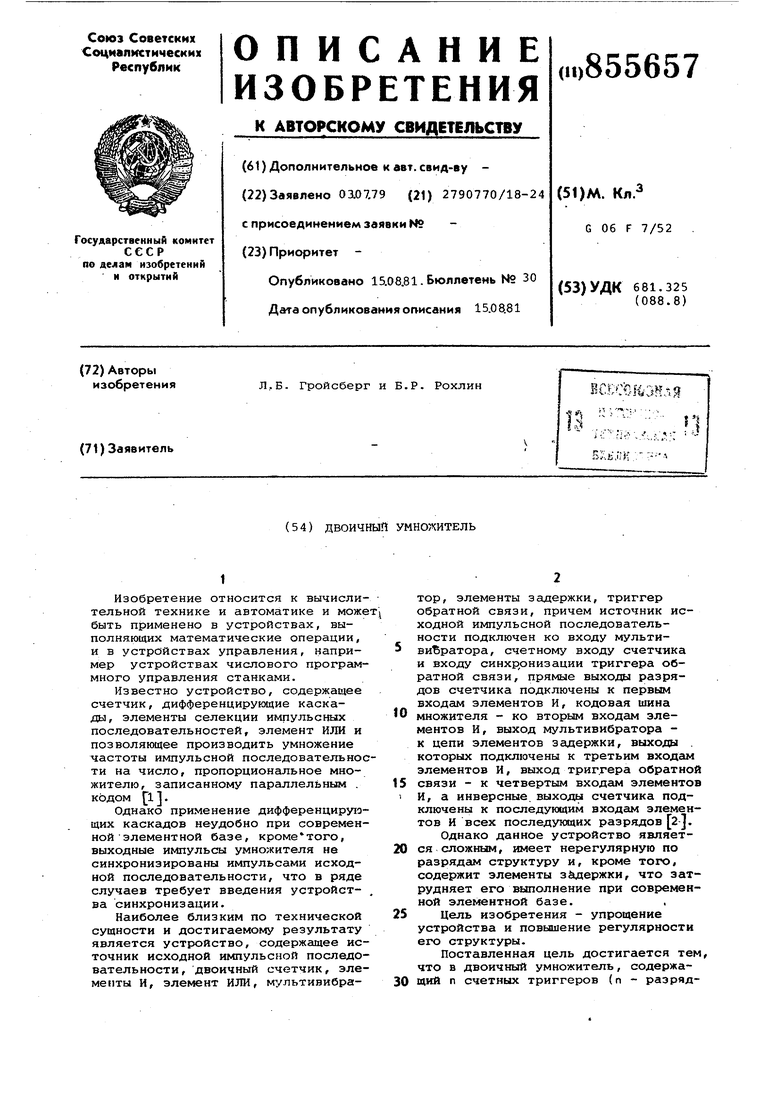

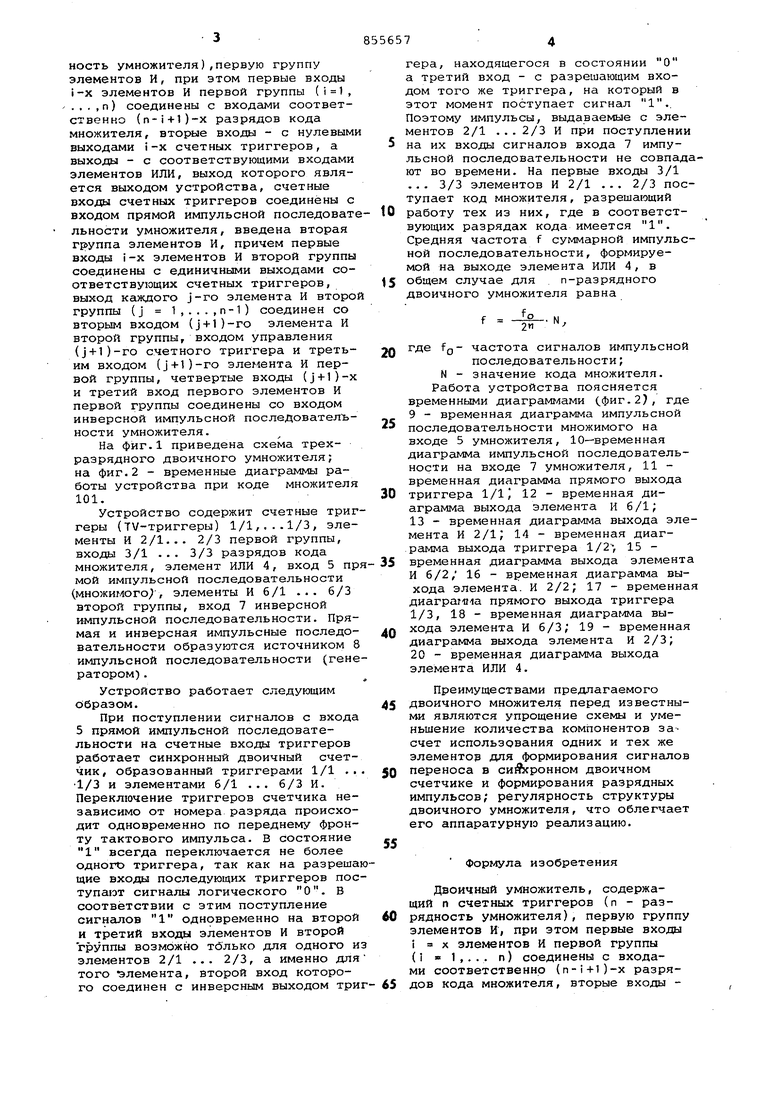

На фиг.1 приведена схема трехраэрядного двоичного умножителя; на фиг.2 - временные диаграммы работы устройства при коде множителя 101.

Устройство содержит счетные триггеры (ТУ-триггеры) 1/1,...1/3, элементы И 2/1... 2/3 первой группы, входы 3/1 ... 3/3 разрядов кода множителя, элемент ИЛИ 4, вход 5 прямой импульсной последовательности множимого , элементы И 6/1 ... 6/3 второй группы, вход 7 инверсной импульсной последовательности. Прямая и инверсная импульсные последовательности образуются источником 8 импульсной последовательности (генератором) .

Устройство работает следующим Образом.

При поступлении сигналов с входа 5 прямой импульсной последовательности на счетные входы триггеров работает синхронный двоичный счетчик, образованный триггерарли 1/1 ... 1/3 и элементами 6/1 ... 6/3 И. Переключение триггеров счетчика независимо от номера разряда происходит одновременно по переднему фронту тактового импульса. В состояние 1 всегда переключается не более одного триггера, так как на разрешающие входы последующих триггеров поступают сигналы логического О. В соответствии с этим поступление сигнсшов 1 одновременно на второй и третий входы элементов И второй группы возможно тблько для одного из элементов 2/1 ... 2/3, а именно для того элемента, второй вход которого соединен с инверсным выходом триггера, находящегося в состоянии О а третий вход - с разрешающим входом того же триггера, на который в этот момент поступает сигнал 1.. Поэтому импульсы, выдаваемые с элементов 2/1 ... 2/3 И при поступлении 5 на их входы сигналов входа 7 импульсной последовательности не совпадают во времени. На первые входы 3/1 ... 3/3 элементов И 2/1 ... 2/3 поступает код множителя, разрешающий

o работу тех из них, где в соответствующих разрядах кода имеется 1. Средняя частота f суммарной импульсной последовательности, формируемой на выходе элемента ИЛИ 4, в

5 общем случае для п-разрядного двоичного умножителя равна

N,

2и

где fg- частота сигналов импульсной

последовательности; N - значение кода множителя. Работа устройства поясняется временными диаграмгу5ами (фиг. 2), где 9 - временная диаграмма импульсной

последовательности множимого на входе 5 умножителя, 10-временная диаграмма импульсной последовательности на входе 7 умножителя, 11 временная диаграмма прямого выхода

триггера 1/1J 12 - временная диаграмма выхода элемента и 6/1; 13 - временная диаграмма выхода элемента И 2/1; 14 - временная диаграмма выхода триггера 1/2 15 временная диаграмма выхода элемента И 6/2, 16 - временная диаграмма выхода элемента. И 2/2; 17 - временная диагра1П1а прямого выхода триггера 1/3, 18 - временная диаграглма выхода элемента И 6/3; 19 - временная диаграмма выхода элемента И 2/3; 20 - временная диаграмма выхода элемента ИЛИ 4.

Преимуществами предлагаемого двоичного множителя перед известными являются упрощение схемы и уменьшение количества компонентов засчет использования одних и тех же элементов для формирования сигналов переноса в сийхронном двоичном счетчике и формирования разрядных импульсов; регулярность структуры двоичного умножителя, что облегчает его аппаратурную реализацию.

Форглула изобретения

Двоичный умножитель, содержащий п счетных триггеров (п - разрядность умножителя), первую группу элементов И, при этом первые входы i X элементов И первой группы (i « 1 , . . . п ) соединены с входами соответственно (n-i+l)-x разрядов кода множителя, вторые входы с нулевыми выходами i-х счетных триггеров, а выходы - с соответствущими входами элемента ИЛИ выход которого является выходом устройства, счетные входы счетных триггеров соединены с входом прямой импульсной последовательности умножителя, отличающийся тем, что, с целью упрощения и повышения регулярности структуры двоичного умножителя, в него введена вторая группа элементов И, причем первые входы i-X элементов И второй группы соединены с единичными выходами соответствующих счетных триггеров, выход каждого j-ro элемента И вторйй группы (,..., п-1) соединен

со вторым входом (i+)-ro элемента И второй группы, входом упраьле 1ин (j+1)-ro счетного триггера и третьим входом(j+l)-го элемента И первоп группы четвертые входы (j+1)-x и третий вход первого элементов И первой группы соединены со входом инверсной импульсной последовательности умножителя.

Источники информации, принятые во внимание при экспертизе

кл. 235-164, опублик. 1964 (прото-тип).

jTJiJijanjTJTj janjTjnjT

19 oAjlJlJTJlJlJlJTJT-riJTJ JlJ

15

/

16

I

17

/

W

/ n

n

Авторы

Даты

1981-08-15—Публикация

1979-07-03—Подача