Изобретение относится к области гзычислительной техники м может использоваться в арифмети,ческ1гх устроствах ЭВМ средне произг1О,цитель юс ти.

Целью изобретения является повышение быстродействия устройства.

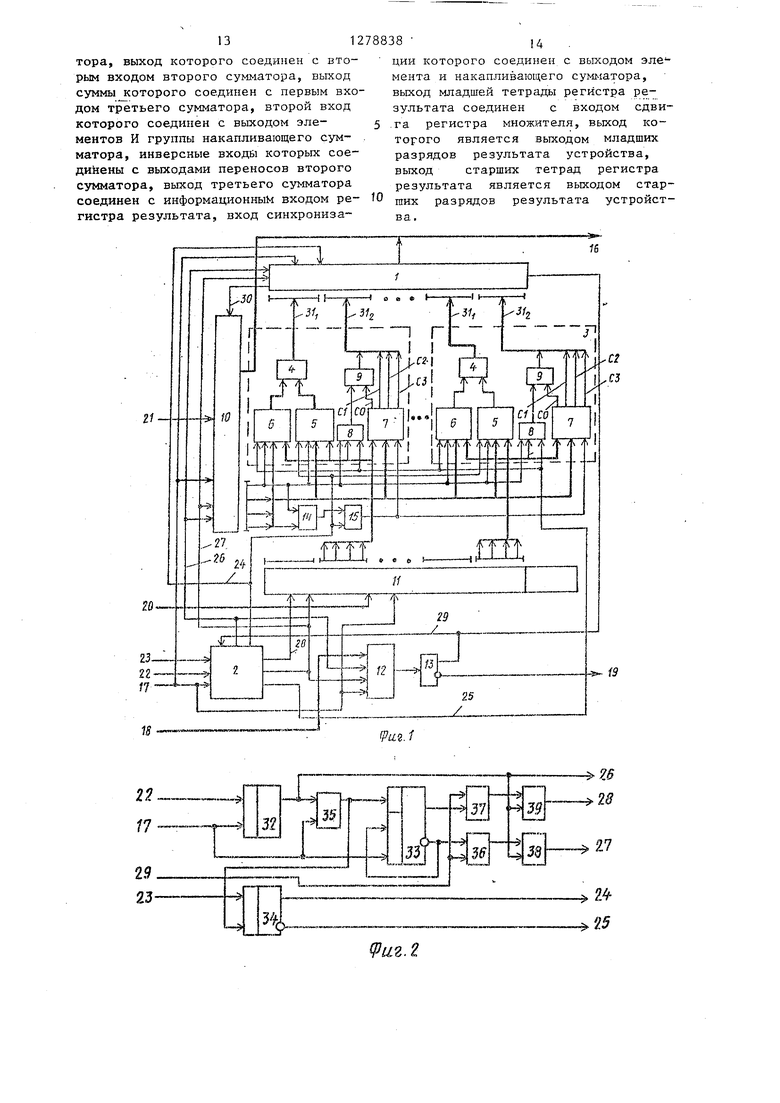

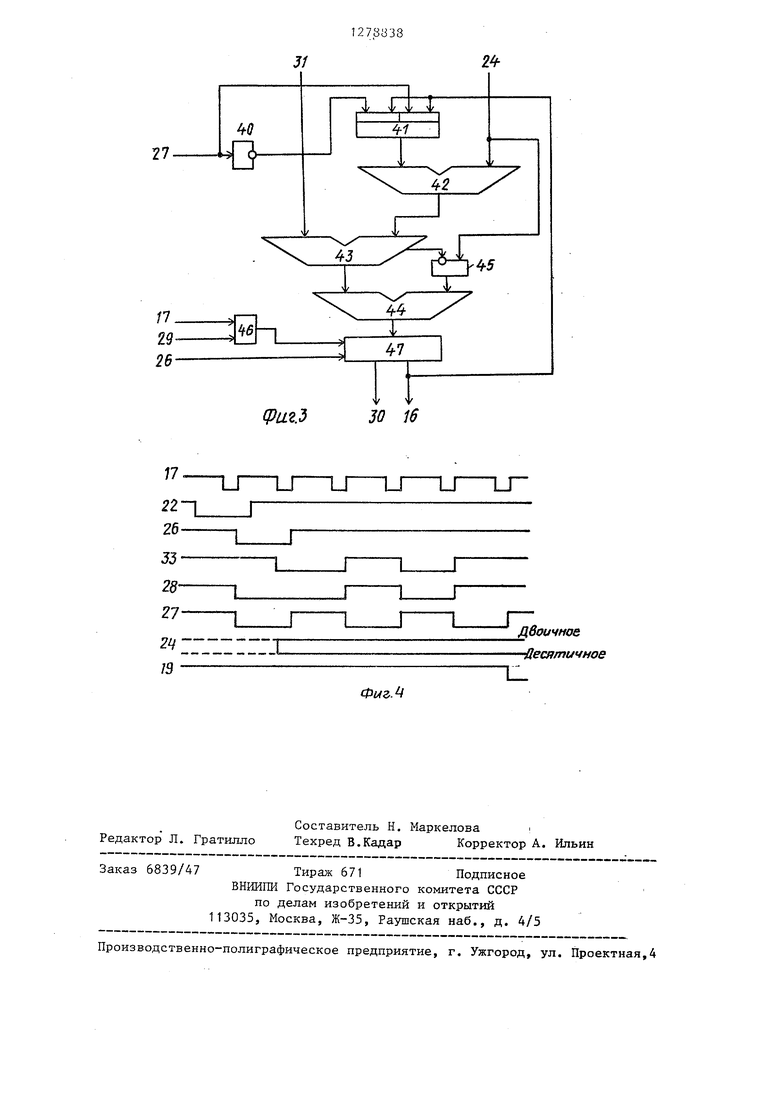

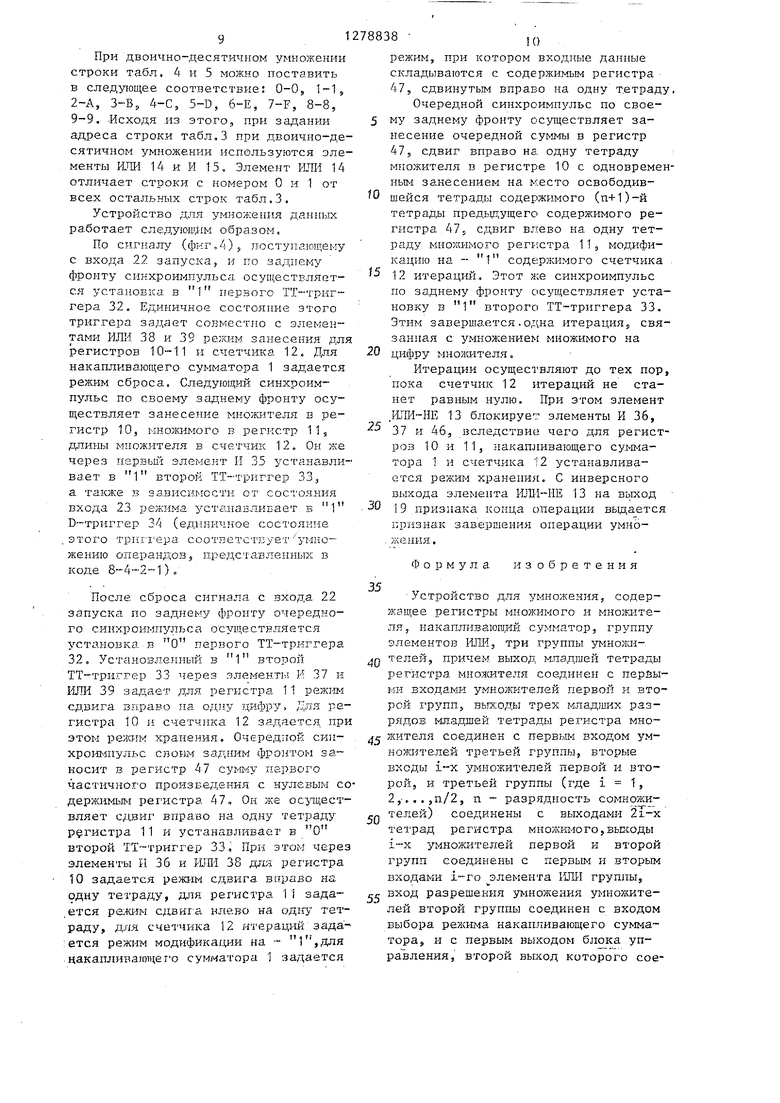

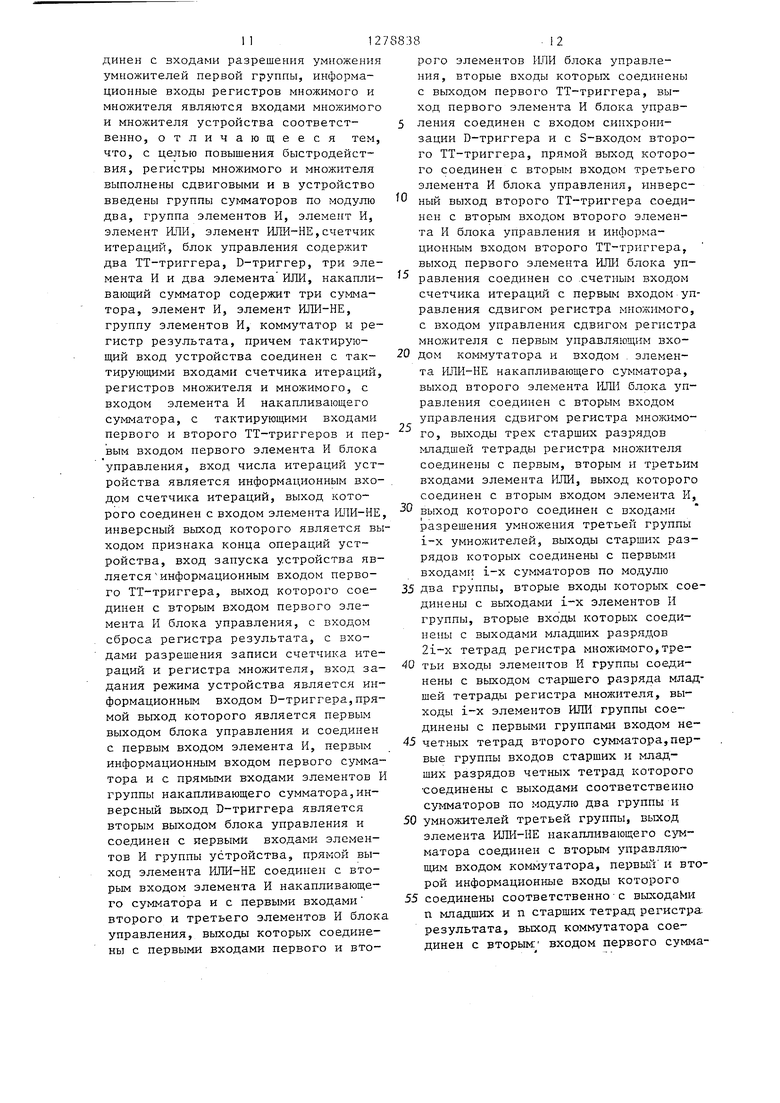

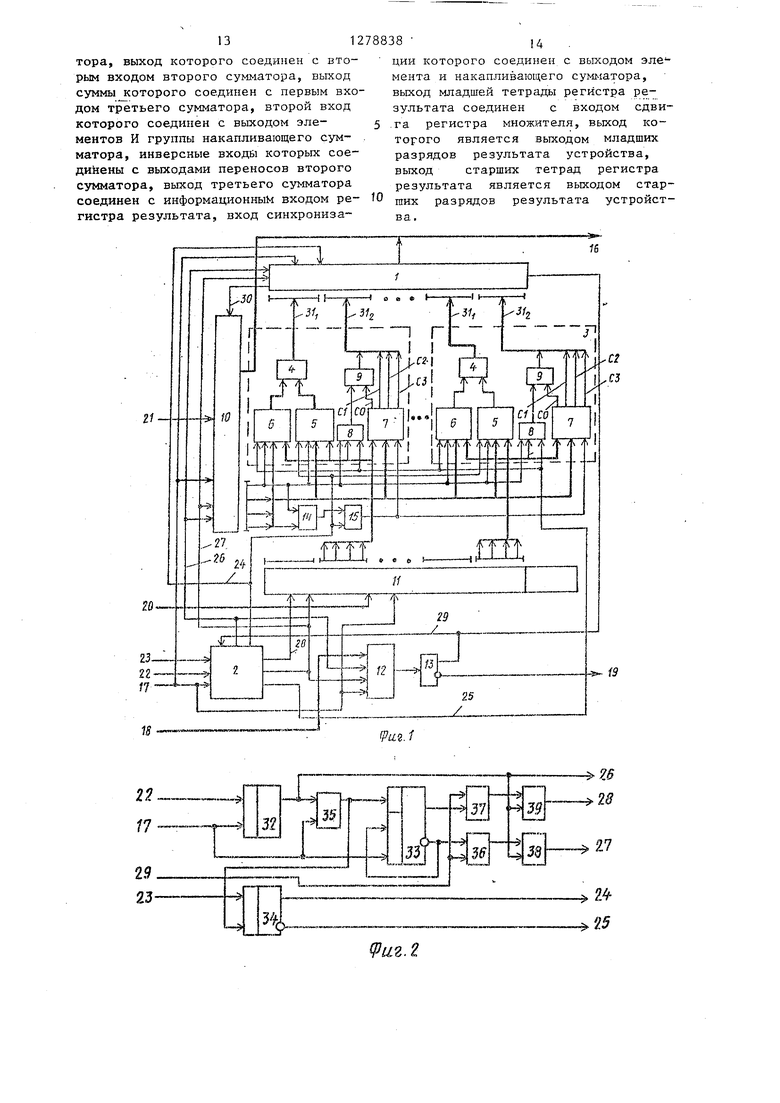

На фиг,1 изображена функциональная схема устройства для умножения , на фиг „2 - блок уиравленР1Я5 па фиг 3 накапливающи11 сумматорj на фиг,4 временная др агра1ама рггботь:: устройст , ва.

Устройство для умножения данных (фиг, 1) содержит нака1 ливаю;1р1й сумматор, состоящий из п тетрад, блок управлеиня грушту из п/2 умножителей ,3, каждый из газторых содержит 3JieMeHT ИЛИ i, умножитель 5 нервой группы-, умножитель б второй группы умнож1-гге1п 7 третье I pyrmbi, элемент И 8j сумматор но модулю два 9, регистр 10 множителя, состояшд из п тетрад, регистр 11 мпо;кимого, сос тоянгдй из п+1 тетрад с -гетчик 12 итераций.элемент ИЛК-Н 13, элемент ИЛИ 14 элемент И 15,выход, 16 результат тактирующий вход 17,вход 18 числа итераций s выход, 19 признака конца опера- ции, входы 20-21 множи-мого и множителя, вход 22 запуска, вход 23 задания pe iU iMa, первый выход 24 блока 2, второй выход 25 б.1.ока 2. третш, четвер ый и иятый выходы 26-28 блок 2, вход 29 блокировки блока. 2, выход 30 младшей тетра,цы накашп ваю- щего сумматора, входы 31,-312, нечетных и четных тетрад сумматора 1 о

Блок 5 ггравления (фиг, 2) содержит первый ТТ--триггер 325 второй ТТ-три гер 335 Т триггер 34,, первый элемент И 35, второй э.м.емент 11 36. гре тий элег-юнт И 37, nepebiii э: 1емепт ИЛ1 1 38, вторсй элемен,т .ИЛИ 39,

Паклтглг ваюгдий (фшчЗ) содержит .чн5;ертор 40, коммутатор 41 первый сумматор 42, второй cyм гaтop 43, третш сумматор 44 (все торы из а тетрад),. I pynny элементов И 45, элемент И 4б,регистр 47 результата, содержаш,нй тетрад .

Регистр 10 является двухтактным и изменяет свое состояние по заднему фронту синхроимпульса в за.виси-- мости от состояния своих угфавляю- щпх вход,ов. Регистр 10 содержит п тетрад 1 прндпазначек для хранения

o

5

0

0

информации, представленной в шестнад- цатеричном коде ил. в коде 8-4-2-1 (двоично-десятичном коде), В исходном состоянии регистр 10 хранит множитель, В процессе работы регистр 10 формирует младшую часть произведения. и в зависимости от состояния своих управляющих входов может находргться в следующих режимах:

S, - хранение,

8,5,, 11 - занесение,

- сдвиг информации вправо н.а одну цифру,

Регистр 11 являе тся двухтактньм и изменяет свое состояние по заднему фронч у синхрозп.шулЬ Сг в зависимости от состоу 1 ия своих управляю цих входов. Регистр 11 со,и,ер;-кит (п+1) тетраду и предназначен для хранения информации, предстаз,г;енной в шестнад- цатеричном коде илк в коде 8-4-2-1 (двоич:но-десятичнок коде) , Тетрада (п.+ 1)-я регистра 11 является вспомо- г,ательпой В iicxof,HOM состоянии множимое заноси1ч;я в старшие п тетрад, Рег пстр 11 условно разбивается на п/2 регистров, со,цержащ;1Х по две тетрады, причем на умножители 3 подаются млад11;ие тетрады этих регистров. Поэтому умножение на цифру множителя осувдествляется в ,цва такта.

В первом такте осуществляется ум- Ho/icein-ie младших тетрад регистров на цифру мнол ителя и сгуммирование полученного произведения наканлизается сумматором 1, после чего осуществляется сдвиг множимого вправо на одну цифру. При этом цифрь занимают позиции младших цифр, а самая младшая цифра множимого занимает позицию тетрады (ит i, «

Во втором 7 ак ге С С у1ч,естэ.ГЯ;ОТСя 5 умножение старпятк тщфр на цифру мпо- ;;ителя и суммирогавие п элyчeIПIoгo произведения пакапливаюпщм суг мато- ром 1, посла чего осуществляется сдвиг множимого влево па одну цифру 0 При этом мно:-к;-г.1ое г реобретает свой первопачальньш вид. Режимы работы рег истра 1 определяются состоянием его управл.Я1ощих входов; хранение, занесение

сдвиг информации вправо на О7дну цифру; сдвиг информации влево на одну цифру.

5

S, 3, S,S,11 S,

8,

Счетчик 12 итераций определяет условие завершения операции умножения. Перед началом работы в него заносится длина множителя в цифрах. После умножения множимого на цифру множителя из содержимого счетчика 12 итераций вычитается - 1,Режимы работы счетчика 12 итераций определяются состоянием его управляющих входов:

S| - хранение;

- занесение;

S, - модификация .

Накапливающий сумматор 1 предназначен для формирования произведения путем суммирования содержимого регистра 47 с входными данными, поступающими с выхода умножителей 3. Регистр 47 является двухтактным и изменяет свое состояние по заднему фронту синхроимпульса. Регистр 47 содержит п+1 тетрад. Накапливающий сумматор 1 содержит три сумматора 42 44. Сумматор 43 является основным. Сумматор 42 предназначен для коррекций входных данных сумматора 43 на + б при десятичном умножении. При шест- надцатеричном умножении сумматор 42 не изменяет входные данные. Сумматор 44 предназначен для коррекции результата сумматора 43 на + 10 в тех тетрадах, которые не имеют при суммировании выходного переноса (формирования констант 10 осуществляют элементы 45 запрета). С коммутатора 41 подается на вход сумматора 42 содержимое регистра 47. Если с содер- йсимым регистра 47/складывается произведение четных цифр множимого на цифру множителя, то на вход сумматора 42 подаются младшие п тетрад регистра 47. Если с содержимым регистра 47 складывается произведение нечетных цифр множимого на цифру мнолсителя, то на вход сумматора 42 подаются п старших тетрад регистра 47. Младшая (п+1)-я тетрада регистра 47 при этом подается на выход вьщвигаемых данньгх накапливающего сумматора 1. Инвертор 40 определяет условие подачи содержимого регистO

5

0

5

0

5

0

5

0

pa 47 на вход сумматора 42. Элемент И 46 управляет синхронизацией ре- гистра 47. Стробирование регистра 47 осуществляется до полного обнуления счетчика 12 итераций. В этом случае элемент ШШ-НЕ 13 блокирует эле- чент И 46, благодаря чему накапливающий сумматор переходит в режим хранения.

Блок 2 управления определяет временную диаграмму работы предлагаемого устройства. Первьй ТТ-триггер 32 определяет режим занесения исходной информации в устройство (при этом для накапливающего сумматора задается режим сброса). Второй ТТ-триггер 33 управляет умножением операндов под управлением счетчика 12 итераций. Умножение осуществляется до тех пор, пока счетчик 12 итераций не обнулится. После этого блок 2 управления задает для регистров 10 и 11, а также для счетчика 12 итераций режим хранения.

Умножители 5-7 первой, второй и третьей групп представляют собой ПЗУ, выдающие в зависимости от содержимого входных данных, которые являются адресом, частичные произведения.

Входными данными умножителей 5-6 . являются четырехбитная младшая тетрада множителя (,) и четырехбитные четные тетрады множимого (BgBjB B). Умножители 5 первой группы формируют старшую цифру десятичного произведения тетрады множителя а(,а, на соответствутащие тетрады множимого . Умножители 6 второй группы формируют старшую цифру шестнадцатеричноЪо произведения тех же тетрад. В зависимости от состояния D-триггера 34 блокируется одна из двух групп умножителей 5 или 6-и элементы ИЛИ 4 пропускают на вход накапливающего сумматора 1 старшие цифры либо шестнаДцатеричного, либо двоично-десятичного произведения. Кодируется ПЗУ умножителя 5 в соответствии с табл.1. ПЗУ умножителя 6 кодируются в соответствии с табЛ42.

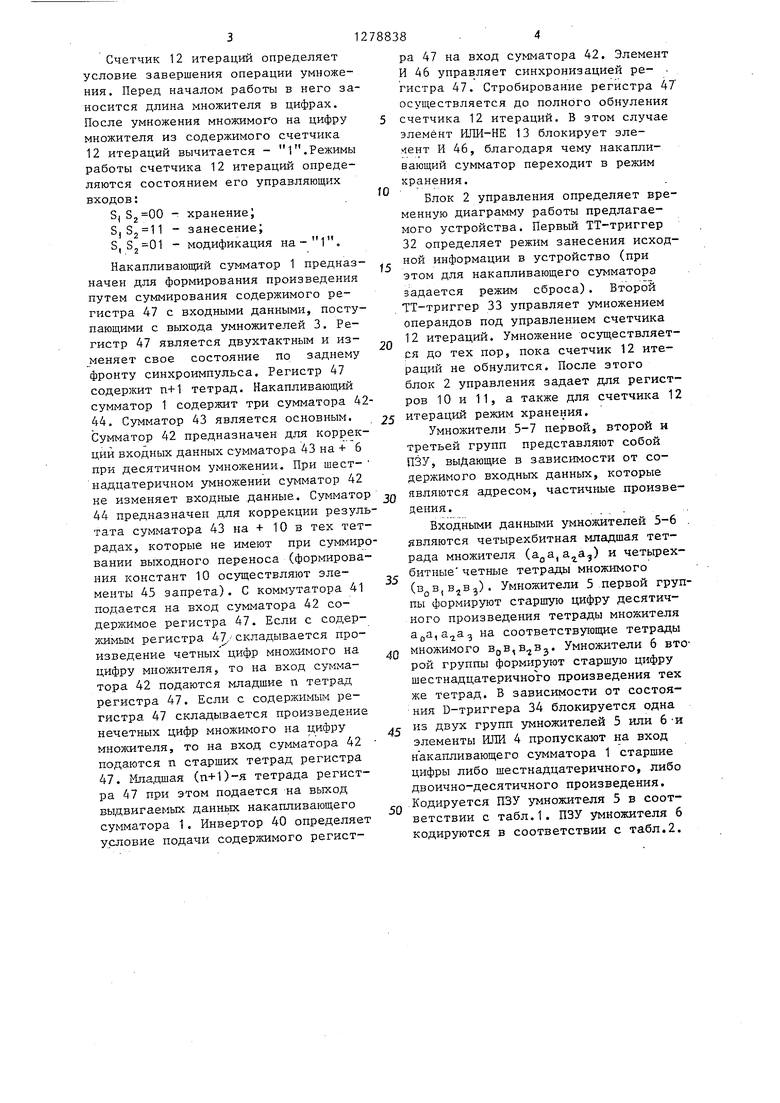

Таблица 1

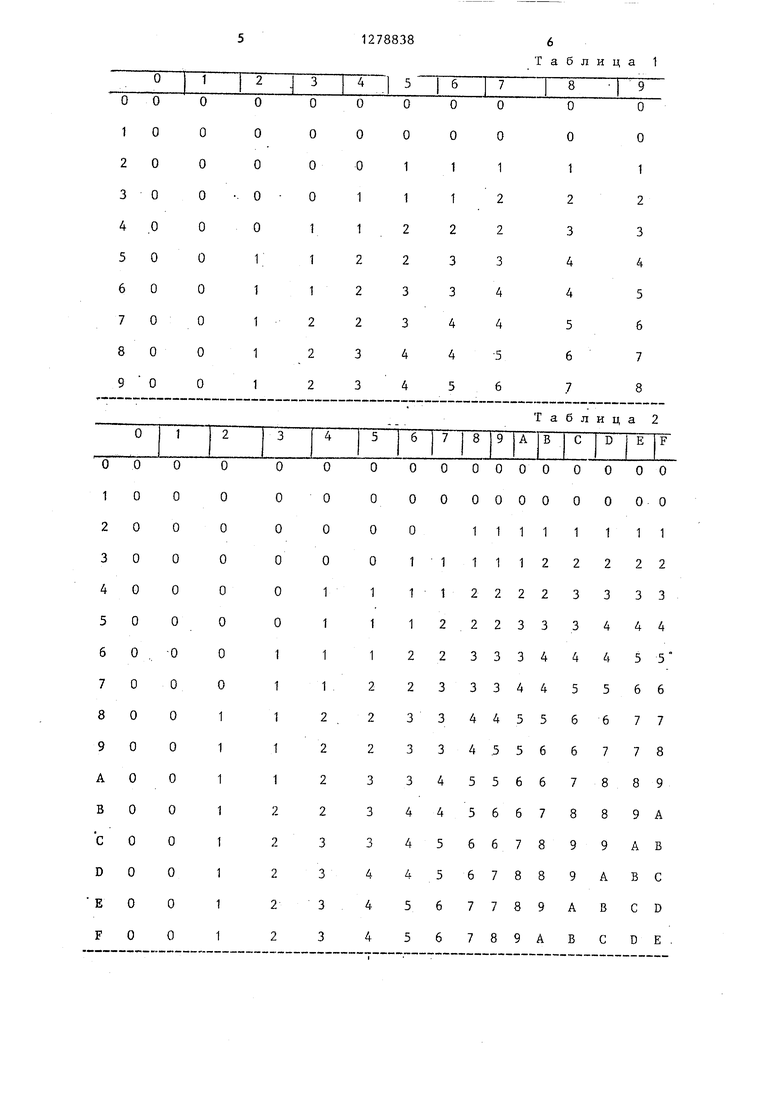

Таблица 2

712788388

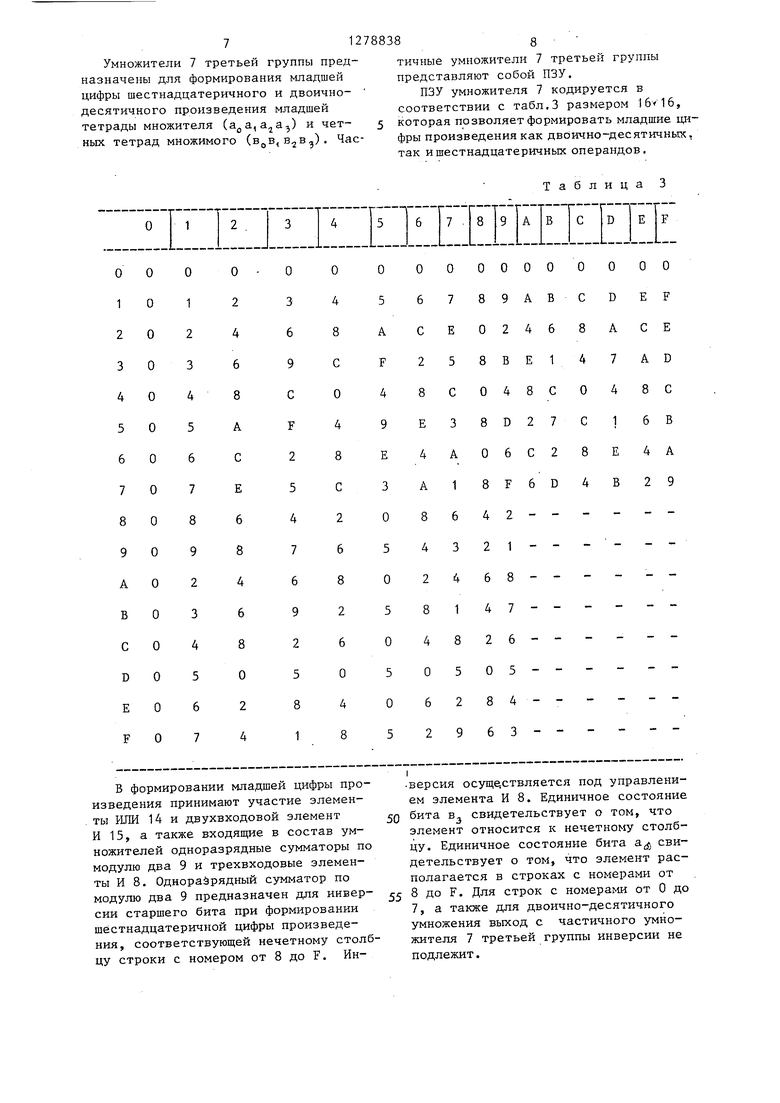

Умножители 7 третьей группы пред- тичные умножители 7 третьей группы назначены для формирования младшей представляют собой ПЗУ. цифры шестнадцатеричного и двоично- ПЗУ умножителя 7 кодируется в десятичного произведения младшей соответствии с табл.З размером , тетрады множителя (. и чет- 5 которая позволяет формировать младшие ци- ных тетрад множимого (,). Час- фры произведения как двоично-десятичных,

так ишестнадцатеричных операндов.

В формировании младшей цифры произведения принимают участие элементы ИЛИ 14 и двухвходовой элемент И 15, а также входящие в состав умножителей одноразрядные сумматоры по модулю два 9 и трехвходовые элементы И 8. Одноразрядный сумматор по модулю два 9 предназначен для инверсии старшего бита при формировании шёстнадцатеричной цифры произведения, соответствующей нечетному столбцу строки с номером от 8 до F. ИнТаблица 3

версия осуще ствляется под управлением элемента И 8. Единичное состояние

бита B,j свидетельствует о том, что элемент относится к нечетному столбцу. Единичное состояние бита а свидетельствует о том, что элемент располагается в строках с номерами от

8 до F. Для строк с номерами от О до 7, а также для двоично-десятичного умножения выход с частичного умножителя 7 третьей группы инверсии не подлежит.

g

При двоично-десятичном умножении строки табл. 4 и 5 можно поставиттз в следующее соответствие: 0-0, 1-1 s 2-А, 3-В, 4-С, 5-D, 6-Е, 7-F, 8-8, 9-9. Исходя ,из этого, при задании адреса строки табл.3 при двоично-десятичном умножении используются элементы ИЛИ 14 и И 15. Элемент РШИ 14 отличает строки с номером О и 1 от всех остальных строк табл.З,

Устройство для умножения данных работает следуюшдпу обра.зом.

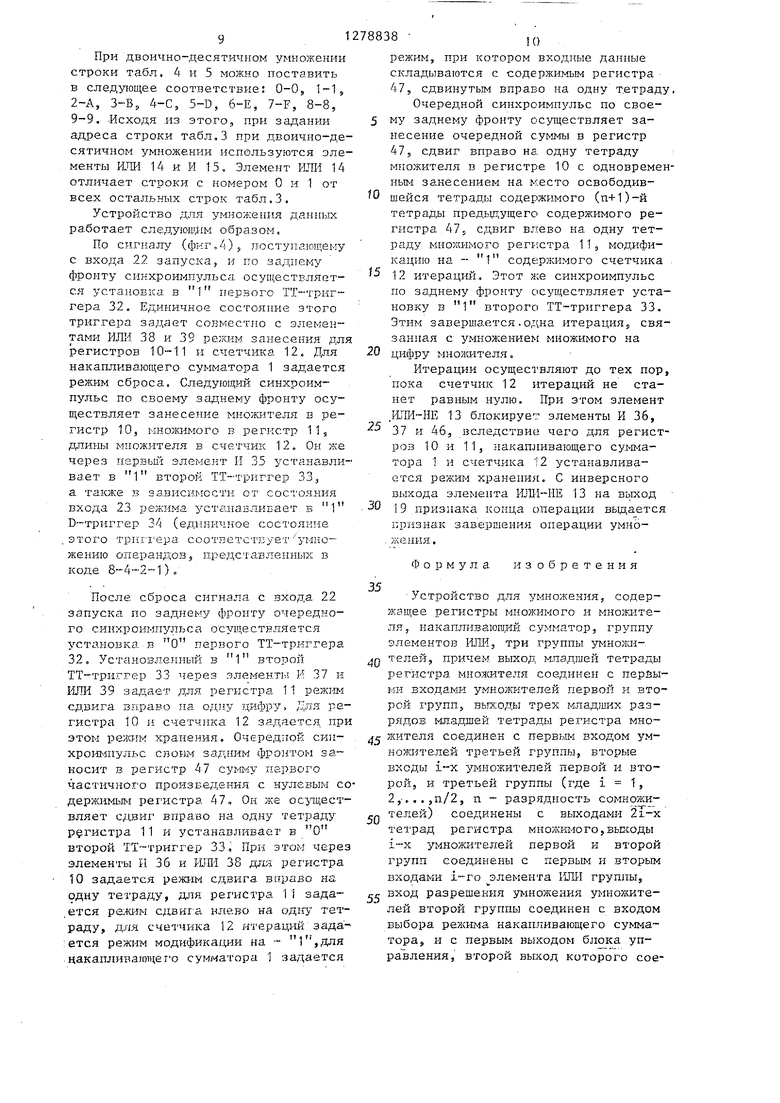

По (фиг,4) 5 поступаюи .ему с входа .22 запуска, и по заднему фронту синхроимпульса осуществляется устан.овка в 1 первого ТТ-триггера 32, Единичное состояние этого триг.гера задает совместно с элементами ИЛИ 38 и 39 режим занесения дл регистров 10-11 и счетчика 12. Для накапливающего сумматора 1 задается режим сброса. Следу ощ.ий синхроимпульс по своему заднему фронту осуществляет занесение множителя в регистр 10, множимого в регистр 11, длины множителя в счетчик 12. Он через первый элемент И 35 устанавливает в 1 второй ТТ-тритгер 33, а также в зависимости от сосч ояния входа 23 режима устапавливает в 1 D-триггер 3 (единичное состояние этого Tpiii i epa соотлетствует умножению операндов, представленных в коде 8 4-2-1).

После сброса сигнала с входа 22 запуска по заднему фронт - очередного синхроимпульса осуществляется установка в О первого ТТ-триггера 32ф Установленный в 1 второй ТТ-триггер 33 через элементы И 37 и lirai 39 задает для регистра 1 1 рела сдвига вправо на од.ну цифру. Для регистра 10 н счетчпка 12 задается, при этом режим хранения, Очеред1юй сип- кроимпульс озоим задЕП-1м франтом заносит в регистр 47 cyi-му первого частичного произведения с нулевым со дерлшмым регистра 47„ Он же ос зацест- вляет сдвиг вправо на одну тетраду регистра 11 и устанавливает в О второй ТТ-триггер 33, При этом через элементы П 36 и ШШ 38 для регистра 10 задается режим сдвига, вправо на одну тетраду, для регистра 11 задается ре:ким сдвига плево на одьт тетраду, для счетчика 12 итераций зада : ется режим модификации на - 1,для накашшвагащег о cyMjMaTopa 1 задается

5

838

5

К)

режим, при котором входные да1П1ые складываются с содержимым регистра 47, сдвинутым вправо на одну тетраду,

Очередной синхроимпульс по своему заднему фронту осуществляет занесение очередной суммы в регистр 47, сдвиг вправо на. одну тетраду множителя в регистре 10 с одновременным занесением на место освободившейся тетрады содержимого (п+1)-й тетрады предьздущего содержимого регистра 47, сдвиг влево на одну тетраду множимого регистра 11,, модификацию на - 1 содержимого счетчика 12 итераций. Этот же синхроимпульс по заднему фронту осуидествляет установку в 1 второго ТТ-триггера 33. Этим завершается.одна итерация, свя- .эанпая с умножением множимого на 0 цифру мнолсителя.

Итерации осуществляют до тех пор, пока счетчик 12 итераций не станет равным нулю. При этом элемент КГШ-ИЕ 13 блокирует элементы И 36, 37 и 46, вследствие чего для регистров 10 и 11, накапливающего сумматора 1 и счетчика 12 устанавливается релшм хранение. С инверсного выхода ШБ1-ИЕ 13 на выход 19 признака конца операции вьщается признак завершения онерации умножения .

0

Формула изобретения

Устройство для умножения, содержащее регистры множимого и множлте- ля, накапливаюгд-тй сумматор j группу элементо)з ИЛИ, три группы умнолш- телей, причем выход младшей тетрады регистра мноясителя соединен с первыми входами умножителей первой и второй групп, выходы трех младших разрядов младшей тетрады регистра множителя соединен с первым входом ум- нош телей третьей группы, вторые входы i-x умножителей первой и второй, и третьей группы (где , 2,,,.,п/2, п - разрядность сомножителей) соединены с выходами 2Т-х тетрад регистра множимого,ВЬЕСОДЫ i-x умножителей первой и второй групп соединены с первым и вторым вход,ами i-ro элемента 1ШИ группы, ВХОД разрешения умножения умножителей второй группы соединен с входом выбора режима накапливающего сумматора, и с первым выходом блока управления, второй Бькод которого соеи1278838

динен с входами разрешения умножения умножителей первой группы, информационные входы регистров множимого и множителя являются входами множимого и множителя устройства соответственно, отличающееся тем, что, с целью повышения быстродейст20 д

ВИЯ, регистры множимого и множителя выполнены сдвиговыми и в устройство введены группы сумматоров по модулю два, группа элементов И, элемент И, элемент ИЛИ, элемент ИЛИ-НЕ,счетчик итерац.ий, блок управления содержит два ТТ-триггера, D-триггер, три элемента И и два элемента ИЛИ, накапливающий сумматор содержит три сумматора, элемент И, элемент ИЛИ-НЕ, группу элементов И, коммутатор и регистр результата, причем тактирующий вход устройства соединен с тактирующими входами счетчика итераций, регистров множителя и множимого, с входом элемента И накапливающего сумматора, с тактирующими входами первого и второго ТТ-триггеров и первым входом первого элемента И блока управления, вход числа итераций устройства является информационным вхо- дом счетчика итераций, выход которого соединен с входом элемента ИЛИ-НЕ инверсный выход которого является выходом признака конца операций устройства, вход запуска устройства является информационным входом первого ТТ-триггера, выход которого соединен с вторым входом первого элемента И блока управления, с входом сброса регистра результата, с входами разрешения записи счетчика итераций и регистра множителя, вход задания режима устройства является информационным входом D-триггера,прямой выход которого является первым выходом блока управления и соединен с первым входом элемента И, первым информационным входом первого сумматора и с прямыми входами элементов И группы накапливающего сумматора,инверсный выход D-триггера является вторым выходом блока управления и соединен с первыми входами элементов И группы устройства, прямой выход элемента ИЛИ-НЕ соединен с вторым входом элемента И накапливающего сумматора и с первыми входами второго и третьего элементов И блока управления, выходы которых соединены с первыми входами первого и вто12

рого элементов ИЛИ блока управления, вторые входы которых соединены с выходом первого ТТ-триггера, выход первого элемента И блока з прав- ления соединен с входом синхронизации D-триггера и с S-входом второго ТТ-триггера, прямой выход которого соединен с вторым входом третьего элемента И блока управления, инверсный выход второго ТТ-триггера соединен с вторым входом второго элемента И блока управления и информационным входом второго ТТ-триггера, выход первого элемента ИЛИ блока управления соединен со -счетным входом счетчика итераций с первым входом управления сдвигом регистра множимого, с входом управления сдвигом регистра множителя с первым управляющим вхо- дом коммутатора и входом , элемента ИЛИ-НЕ накапливающего сумматора, выход второго элемента ИЛИ блока управления соединен с вторым входом управления сдвигом регистра множимо

го, выходы трех старшргх разрядов

30

младшей тетрады регистра множителя соединены с первым, вторым и третьим входами элемента ИЛИ, выход которого соединен с вторым входом элемента И, выход которого соединен с входами разрешения умножения третьей группы i-x умножителей, выходы старших раз- РЯДО13 которых соединены с первьми входами i-x сумматоров по модулю

35 два группы, вторые входы которых соединены с выходами i-x элементов И группы, вторые входы которых соединены с выходами младших разрядов 2i-x тетрад регистра мнoж iмoгo,тpe40 тьи входы элементов И группы соед,и- нены с выходом старшего разряда младшей тетрады регистра множителя, выходы i-x элементов ИШi группы соединены с первыми rpynnaMii входом не45 четных тетрад второго сумматора,первые группы входов старш их и млад,- ших разрядов четных тетрад которого соединены с выходами соответственно сумматоров по модулЕо два группы и

50 умножителей третьей группы, выход элемента ИЛИ-НЕ накапливающего суи- матора соединен с вторым управляющим входом коммутатора, первый и второй информационные входы которого

55 соединены соответственнос выходами п младших и п старших тетрад регистра результата, выход коммутатора соединен с вторык входом первого сумматора, выход которого соединен с вторым входом второго сумматора, выход суммыКОТОРОГО соединен с первым входом третьего сумматора, второй вход которого соединен с выходом элементов И группы накапливающего сум- матера, инверсные входБ которых сое- днйены с выходами переносов второго сумматора, выход третьего сумматора соединен с информационным входом регистра результата, вход синхрониза

ции которого соединен с выходом мента и накапливающего сумматора, выход младшей тетрады регистра результата соединен с входом сдви- .га регистра множителя, выход которого является выходом младших разрядов результата устройства, выход старших тетрад регистра результата является выходом стар- тих разрядов результата устройства.

i9

Ри.2. 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения данных переменной длины | 1985 |

|

SU1291972A1 |

| Устройство для умножения десятичных чисел | 1984 |

|

SU1182514A1 |

| Арифметическое устройство | 1985 |

|

SU1287144A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Устройство для умножения десятичных чисел | 1984 |

|

SU1236462A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Устройство для умножения | 1987 |

|

SU1495785A1 |

| Арифметическое устройство | 1971 |

|

SU522497A1 |

| Устройство для умножения | 1988 |

|

SU1578711A1 |

| Устройство для умножения | 1988 |

|

SU1670685A1 |

Изобретение относится к вычислительной технике. Целью изобретения является повышение быстродействия .устройства. Устройство содержит регистры множимого и множителя, накапливающий сумматор, блок умножителей, блок управления. Для достижения поставленной цели устройство содержит три группы умножителей, выполненных на блоках памяти, два из которых предназначены для формирования старшей цифры частичного произведения, третье - для формирования младшей цифры произведения. Сущность изобретения состоит в том, что на вход блока умножителей подаются операнды в двоичн о-десятичном или двоично- шестнадцатеричном коде. Блоки памяти закодированы таким образом, что в зависимости от режима и незначительной схемной корректировки на выходе имеется результат частичного произведения в заданном коде. Старщая часть произведения накапливается в накапливающем сумматоре, а младшая - за- мещает содержимое регистра множителя. 4 ил., 3 таб. с &

U2.2

(Раг.

27

2Z/ /3Редактор Л. Гратилло

Составитель Н. Маркелова

Техред В.Кадар Корректор А. Ильин

6839/47

Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная,4

30 16

Двоичное Десятичное

Фиг.

| Устройство для умножения | 1977 |

|

SU769539A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Матричное устройство для умножения | 1979 |

|

SU842800A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-12-23—Публикация

1985-07-26—Подача