Изобретение относится к вычислительной технике и может быть использовано при проектировании арифметических устройств, оперирующих информацией, представленной с высокой точностью, для высокопроизводительных мультимикропроцессорных вычислитель- ньпс систем (ММПВС) , а также в качестве арифметического расширителя универсальных процессоров.

Целью изобретения является п.овы- шение точности и быстродействия.

Сущность данного технического решения заключается в том, что, используя способность известного микропроцессора выполнять операцию умножения в двоичном знакоразрядном коде над двенадцатиразрядными операндами без потери значащих разрядов и специфическое качество знакоразрядной системы счисления, заключающееся в определении знака числа знаком первого значащего бита, удается сформировать и аппаратно реализовать алгоритмы умножения операндов, состоящих из I2N бит, с минимальными затратами времени, обеспеченными распараллеливанием вычислительного процесса, и с сохранением способности прототипа к конве-: йерной обработке информации.

CJH 00

со ю

C«J

315892714

Входные операнды X и Y в двоичной , гух быть представлены в виде: 3HaKopa3 f H(oft системе счисления мо; iXz --V 2n- X,.,.X...X, Z Xj2- ;

Y,Y,Y,...Y,...Y,,,...Y,,...Y,...Y,, i Y,2-

-fI

где X, Y j принимают значения j-I , 0, .Очевидно, что эти операнды могут

Ij; N 3,4,...N; п 12. быть преобразованы следующим образом;

It

X ,Х,Х....Х„0...0...0...0. .. .

V.«) °°- °Vl4- - ° - - °- 1/

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО УМНОЖЕНИЯ | 1998 |

|

RU2148270C1 |

| Устройство для выполнения быстрого преобразования Фурье | 1988 |

|

SU1640709A1 |

| Устройство для деления @ -разрядных чисел | 1984 |

|

SU1223224A1 |

| Устройство для умножения чисел | 1990 |

|

SU1714595A1 |

| Устройство для умножения | 1984 |

|

SU1226447A1 |

| Вычислительное устройство | 1988 |

|

SU1532917A1 |

| Устройство для умножения | 1987 |

|

SU1411733A1 |

| Устройство для умножения | 1989 |

|

SU1612295A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Вычислительное устройство | 1988 |

|

SU1647553A1 |

Изобретение относится к вычислительной технике и может быть использовано при проектировании арифметических устройств, оперирующих информацией, представленной с высокой точностью, для высокопроизводительных мультипроцессорных вычислительных систем (ММПВС), а также в качестве арифметического расширителя универсальных процессоров. Цель изобретения - повышение точности и быстродействия. Устройство позволяет сформировать и аппаратно реализовать алгоритмы умножения операндов, состоящих из 12 бит, с минимальными затратами времени, обеспеченными распараллеливанием вычислительного процесса при конвейерной обработке информации. Для реализации операции произведения при условии максимально возможного распараллеливания вычислительного процесса требуется 0,5N(N+1) двенадцатиразрядных умножителей и 0,5N(N+1)-1 сумматоров неограниченной разрядности. 5 з.п.ф-лы, 3 ил.

,-i „-М/«

(,..ОО...О...ОХ,уХ,...Хз,0...0... |Х.2- .2- .

«. i.

X,ОО...О...О...ОХэ7Х ....Х4.0...0... 1 Х.2 .2 2 -Х.

(4rt-3n/3 314t(ti fit

V(M.)n -°°--° -°- -a.H,.. |.2- .X,.2-

: .X

; X - X, X(,.,,4- Х(з,.,„,+ Х(,„.,,-ь....(,. Х„ ,+ 2-.Хз„ :-Jr. -(N-l)n

: + 2 x,+...+2

; no аналогии - Y Y + ,„ + 2 X j + 2 Y +...+2 Y. „ С .I

где X . , YU - 1 2-разрядные операнды тели« нетрудно получить выражение для

N И п

ДЛЯ всех значении N. Q Z из произведения Представляя таким образом сомножиZ X.Y X,.Y + + YJ +.2-(Х,. Y + ,) +

-3n.-4n

+ 2 (X.Y4«4 X.,,-Y3,4- X3,. )-b 2 (Х„. X n Y + X ..„-Y -Jn,

X..Y..+ .-b X..Y,- X,,.-b

. Xj,-Y) + 2 (X.Y X.Y.,,

-()n.

Ч- X.Y) ... + 2 (X,-Y,-b X,Y.,+ X,.Y(,.,,-b.... Xj.,J,

.- - ,,.Y,. X,,Y(.,,.... («.„Л b . . ... -2- «- :x,,.Y,,.(1)

определяющее точный 2N„-разрядной ре- Действительно, величина первого

зультат. Ограничиваясь членом, содер-отбрасьшаемого члена не превышает вежащим сомножитель , можно сфор- личины 2-(), поэтомировать (N+1)-п-разрядный результат,му подсуммирование его к принятому

.как минимум (11,5N - 1,5) разрядов(N+1)п-разрядному результату произвекоторого - точные,дения может начаться не раньше, чем

,-i „-М/«

|Х.2- 2-

с (11,5N + 0,5)-го разряда основной суммы, а учитьшая, что при суммировании старшими разрядами вперед (в зна коразрядной системе счисления) перенос единицы в сторону старших разрядов возможен не более чем на два разряда, получим приведенное выше выражение, определяющее гарантированное количество.точных разрядов в произведении. Последнее обстоятельство определяет также отсутствие влияния на принятый результат младших отбрасываемых членов произведения (1).

Анализируя выражение (1), можно определить, что для аппаратной реализации произведения с принятой выше точностью двух 12Ы-разрядных операндов при условии максимально возможного распараллеливания вычислительного процесса требуется 0,5N(N+1) I2-раз- рядных умножителей и 0,5N(N+1 )-1 J сумматоров неограниченной разрядности. Микропроцессор К1815ВФЗ содержит один такой умножитель и один независимый от умножителя сумматор неорганической разрядности, поэтому количество потребных корпусов микропроцессорных СБИС для реализации предлагаемого устройства определяется выражением 0,5N(N+1), причем один сумматор, не задействованный в реализации (1), используется как независимый вычислитель, сохраняя таким образом функциональную, аналогию с прототипом

Для определенности положим, что устройство оперирует 48-разрядными словами, т.е. . Принимая п 12, m 2п, р Зп, q 4п, запишем алгоритм вычисления произведения сорокавосьмиразрядных операндов:

Z + (X,. Х„.„) + + 2-( + X. XpYn) + + 2( -ь X.Yp + Xp-Y - -f,) 2-(X.Y XpY +

Ограничиваясь членом, содержащим множитель 2 , получим 60-разрядный результат, сорок четыре разряда которого - точные.

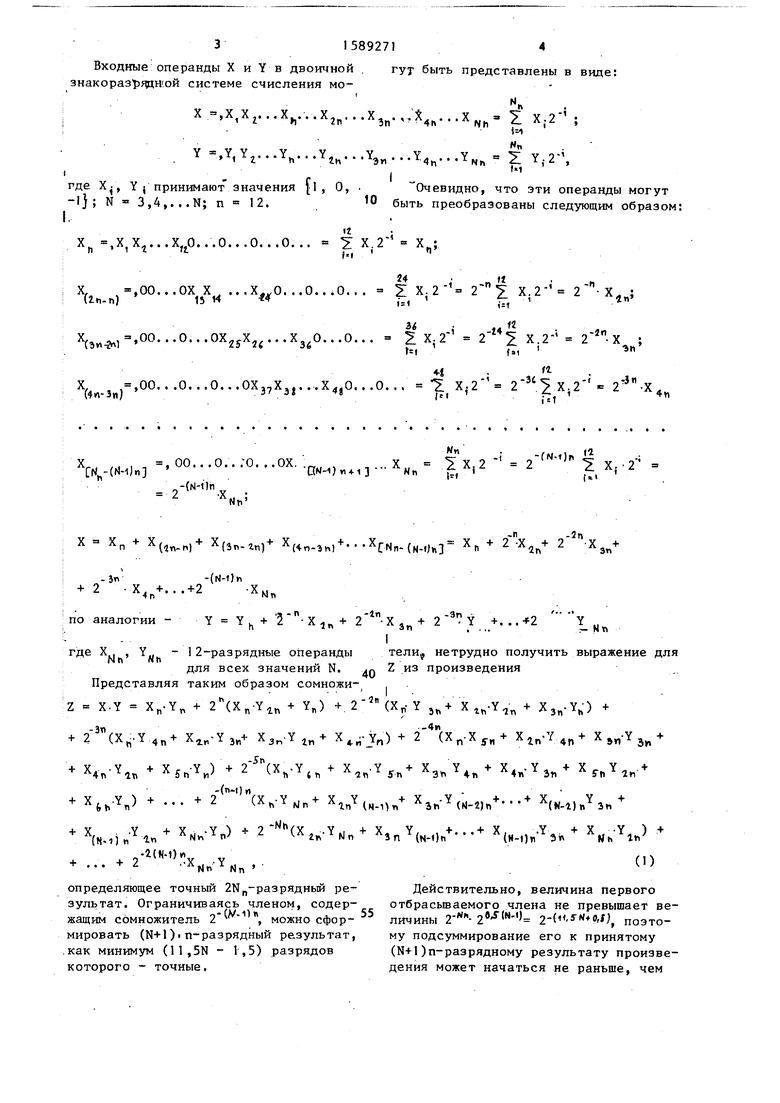

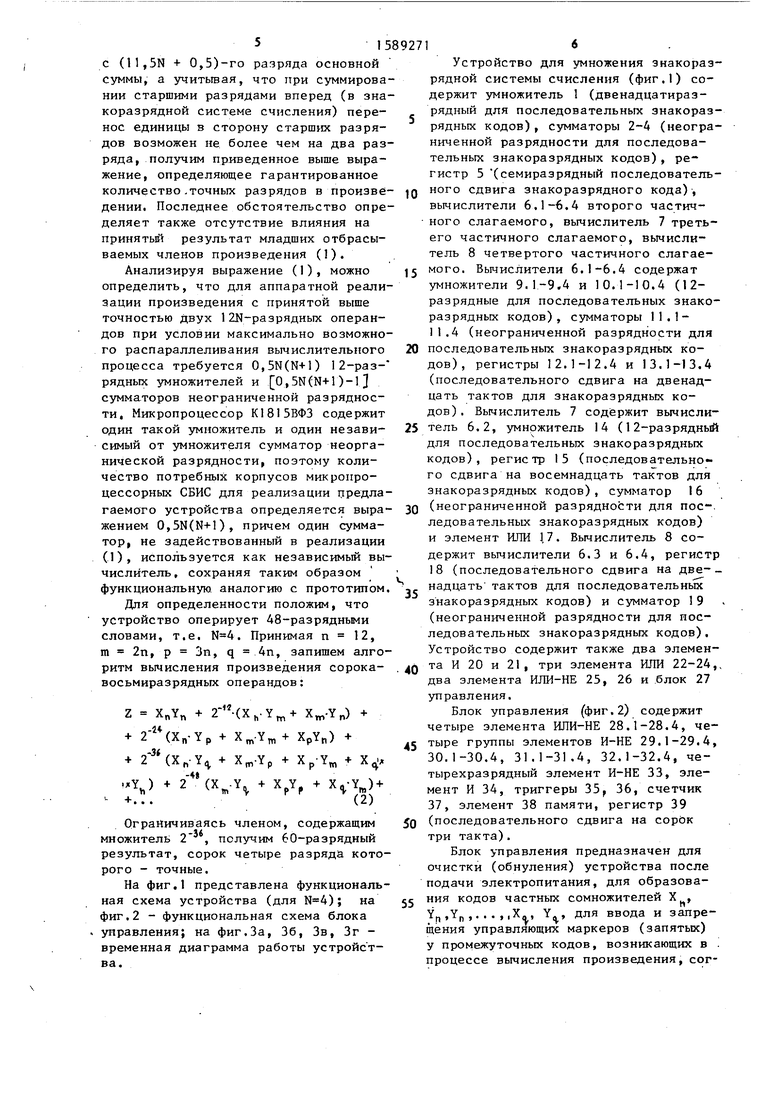

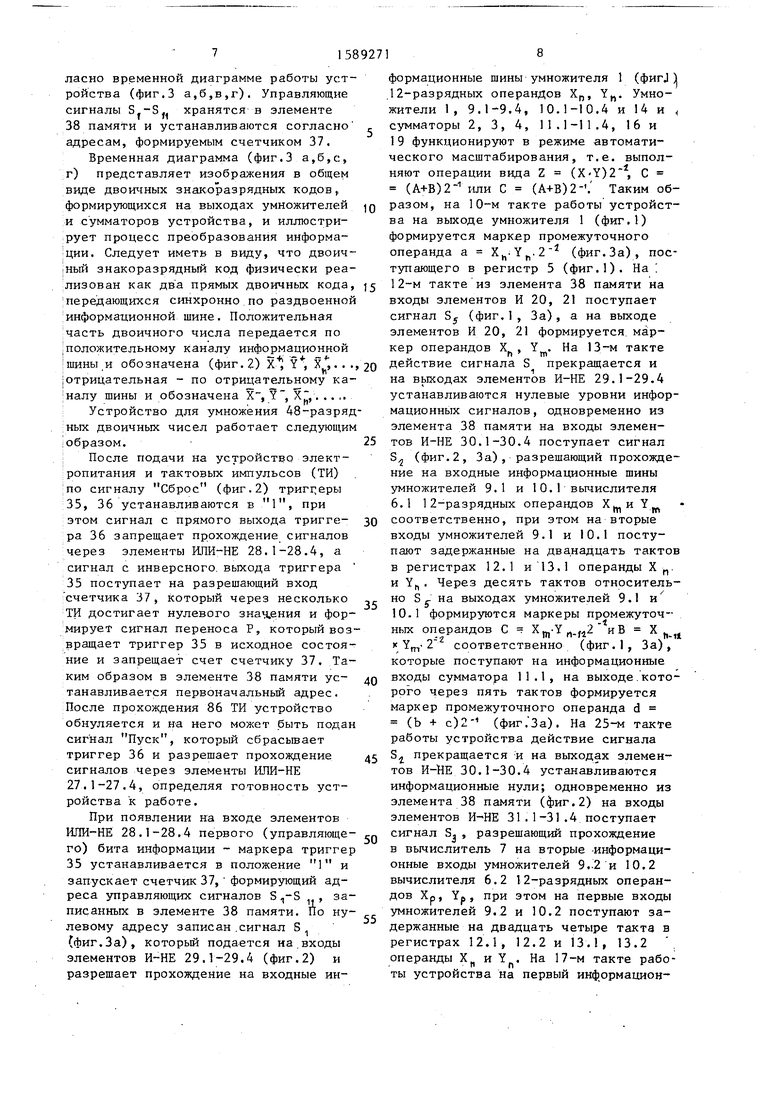

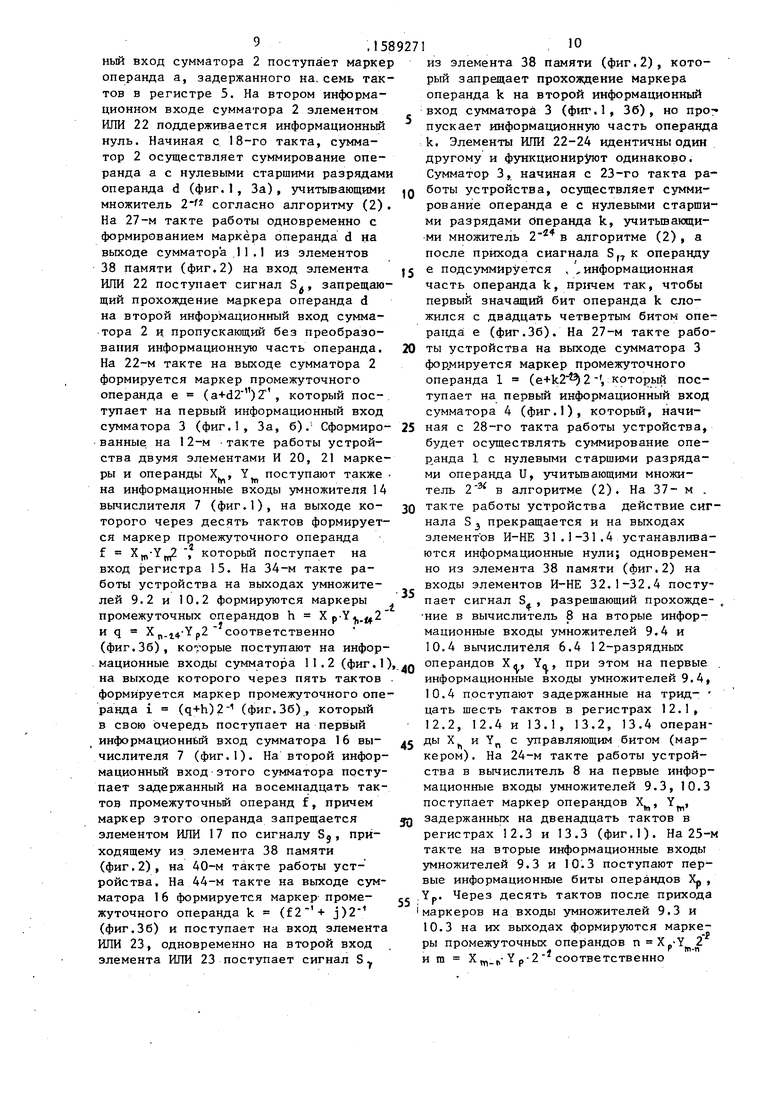

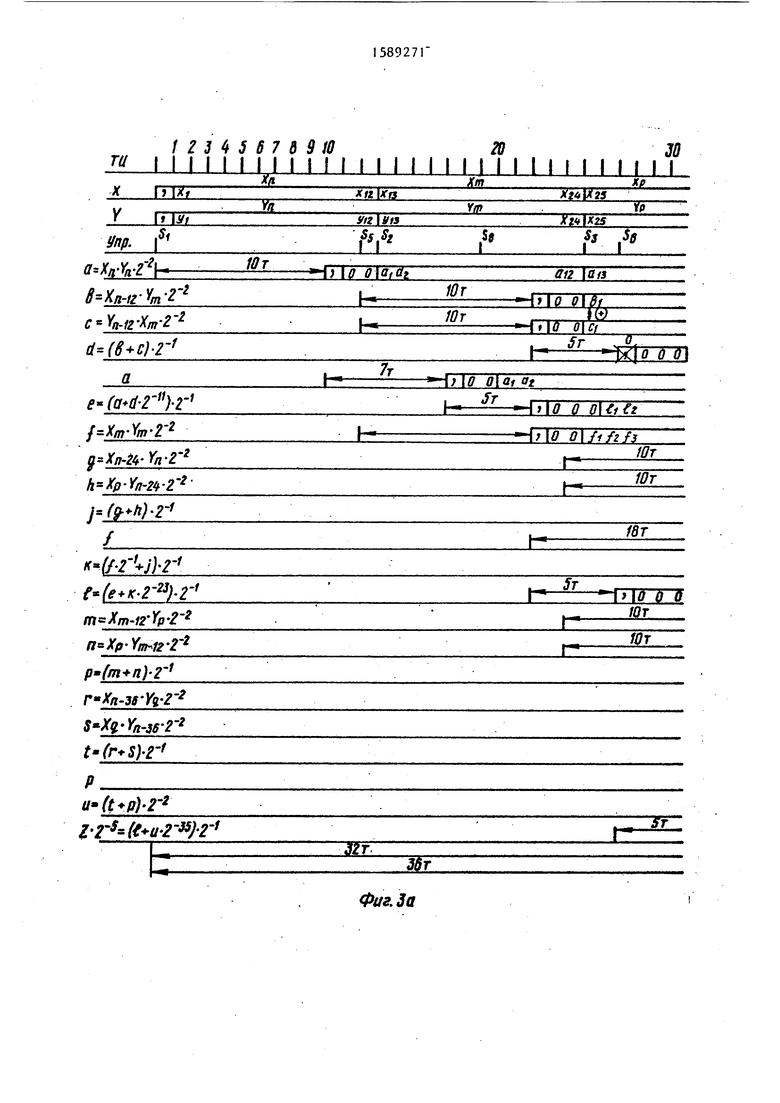

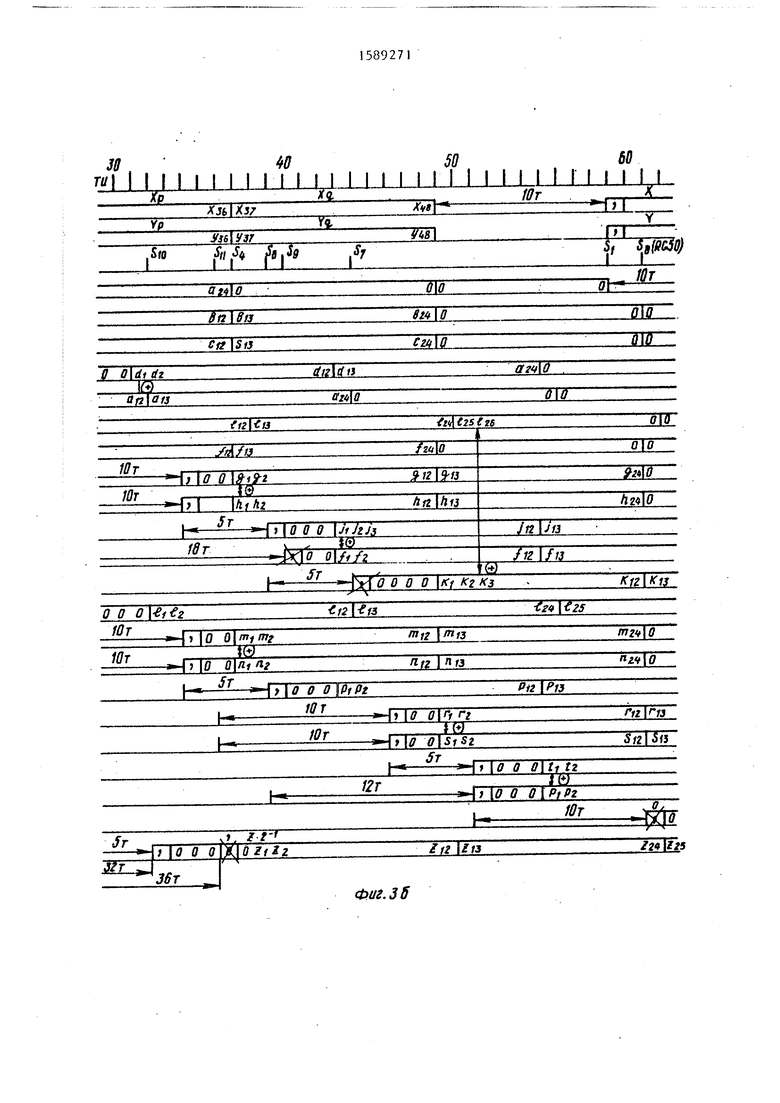

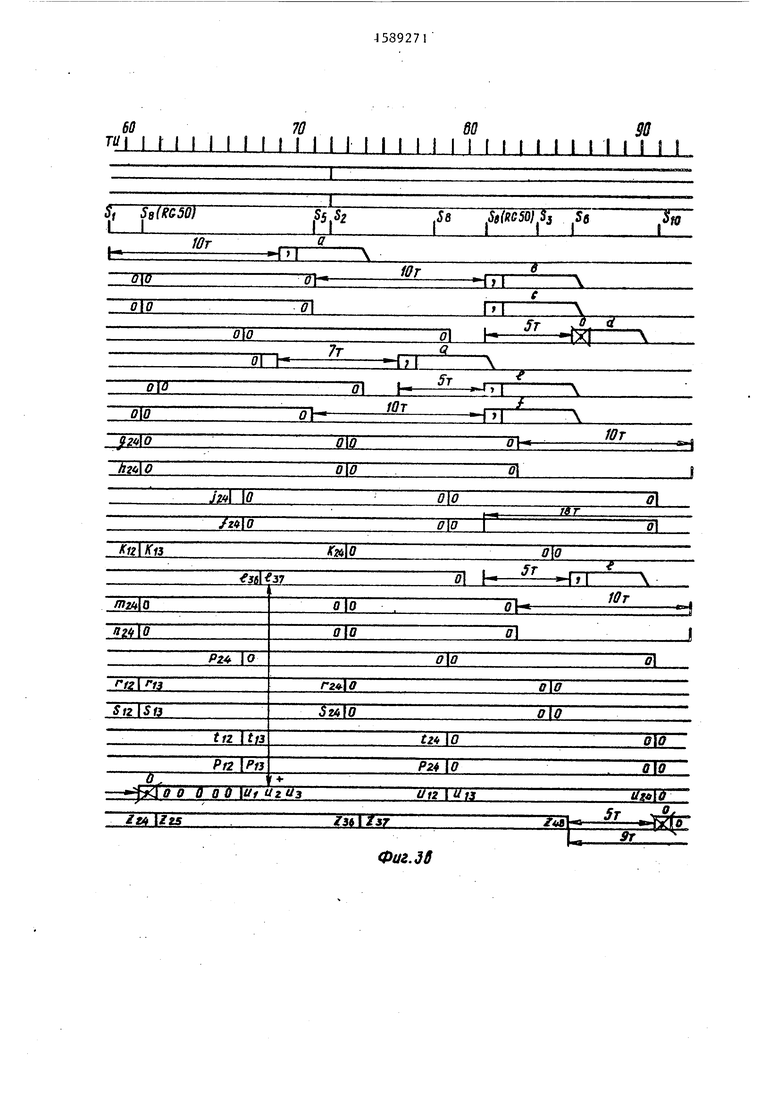

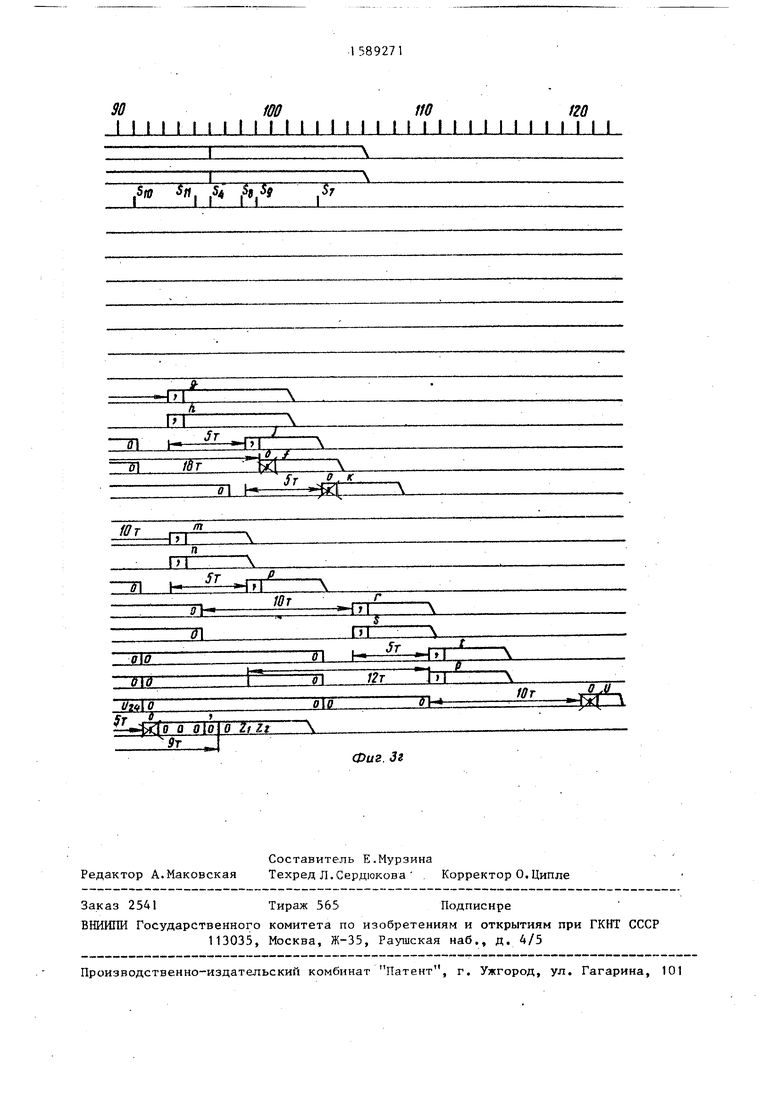

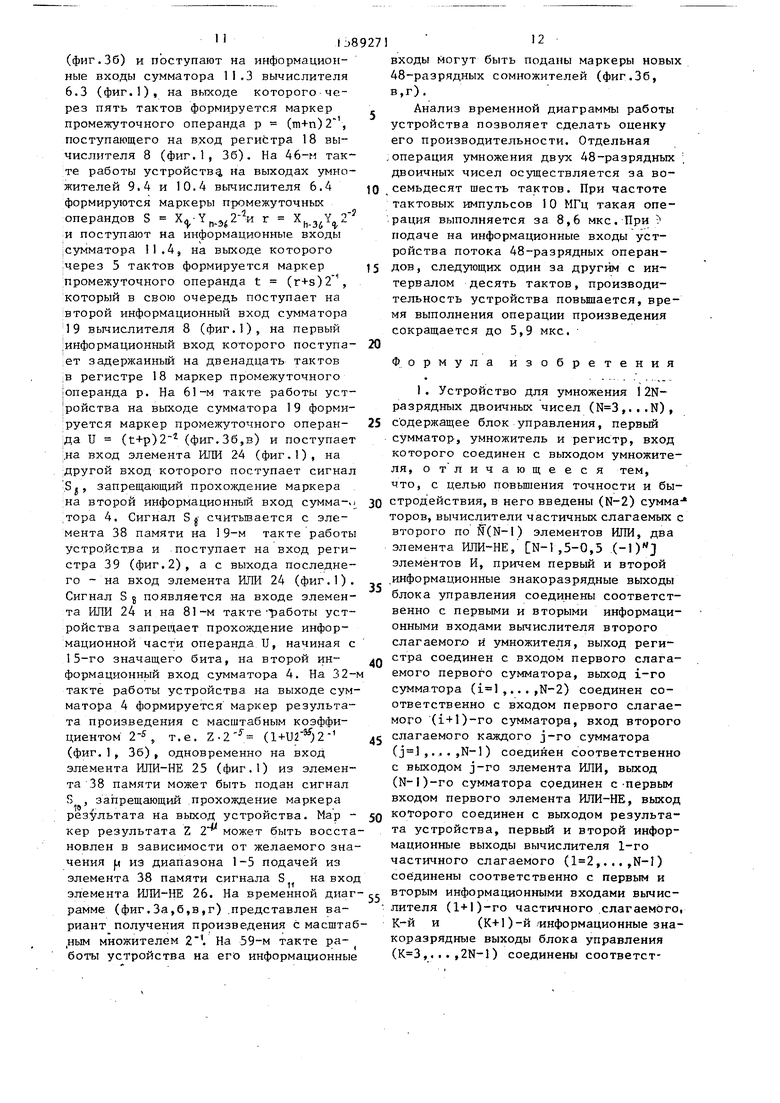

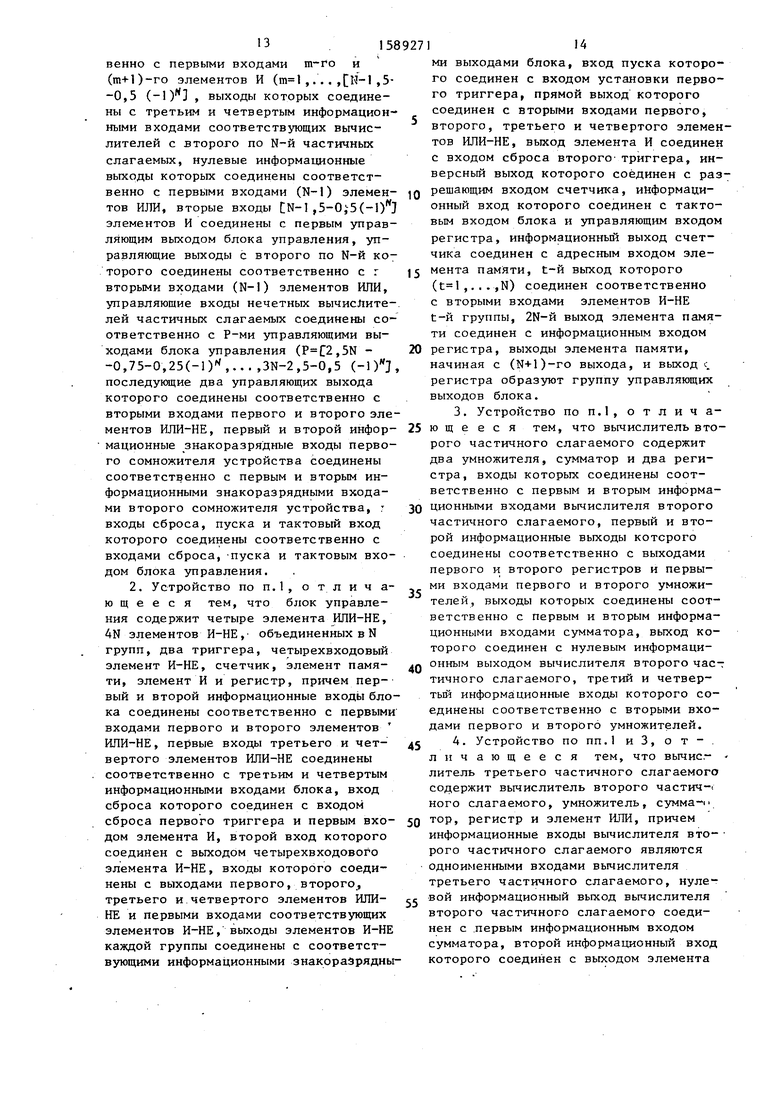

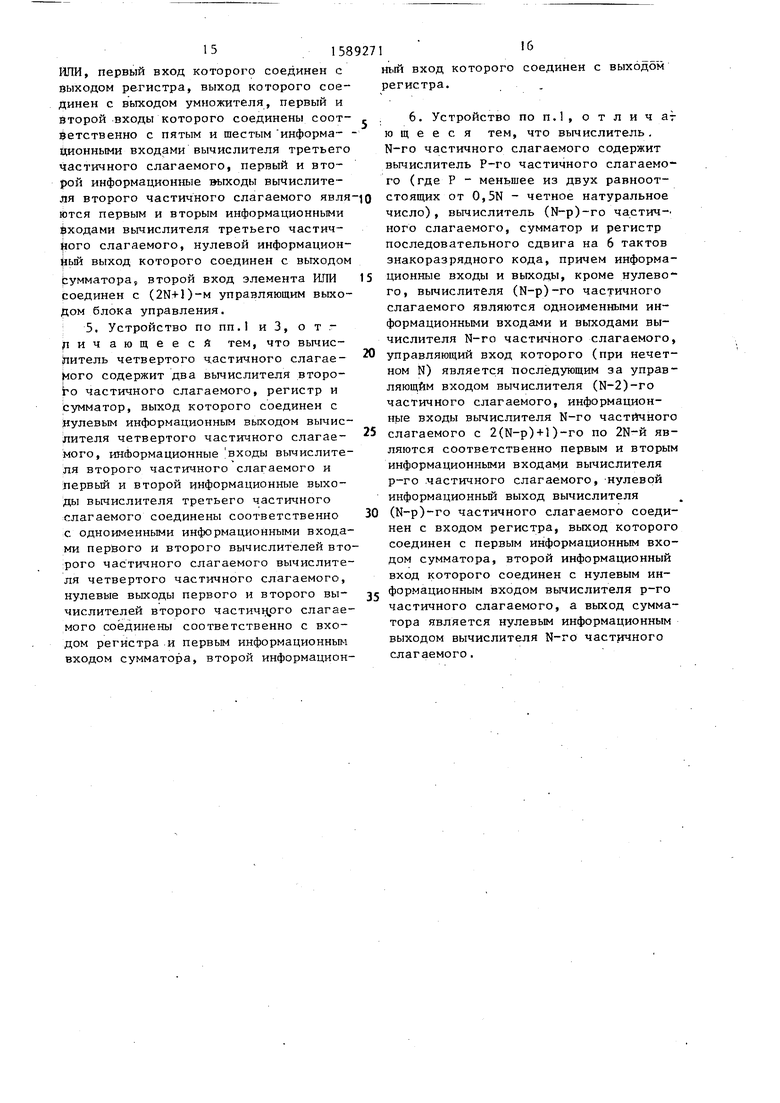

На фиг,1 представлена функциональная схема устройства (для ); на фиг.2 - функциональная схема блока управления; на фиг.За, 36, Зв, Зг - временная диаграмма работы устройства.

Устройство для умножения знакораз- рядной системы счисления (фиг.1) содержит умножитель 1 (двенадцатиразрядный для последовательных знакораз- рядных кодов), сумматоры 2-4 (неограниченной разрядности для последовательных знакоразрядных кодов), регистр 5 (семиразрядный последовательQ ного сдвига знакоразрядного кода), вычислители 6.1-6.4 второго частичного слагаемого, вычислитель 7 третьего частичного слагаемого, вычислитель 8 четвертого частичного слагае5 мого. Вычислители 6.1-6.4 содержат умножители 9.1-9,4 и 10.1-10.4 (12- разрядные для последовательных знакоразрядных кодов), сумматоры 11.1- 11.4 (неограниченной разрядности для

0 последовательных знакоразрядных кодов), регистры 12.1-12.4 и 13.1-13.4 (последовательного сдвига на двенадцать тактов для знакоразрядных кодов). Вычислитель 7 сод1ержит вычисли5 тель 6.2, умножитель 14 (12-разрядный для последовательных знакоразрядных кодов), регистр 15 (последовательного сдвига на восемнадцать тактов для знакоразрядных кодов), сумматор 16

0 (неограниченной разрядности для пос-. ледовательных знакоразрядных кодов) и элемент ИЛИ 1,7. Вычислитель 8 содержит вычислители 6.3 и 6.4, регистр 18 (последовательного сдвига на две-надцать тактов для последовательных знакоразрядных кодов) и сумматор 19 (неограниченной разрядности для последовательных знакоразрядных кодов). Устройство содержит также два элемен0 та И 20 и 21, три элемента ИЛИ 22-24,, два элемента ИЛИ-НЕ 25, 26 и блок 27 управления.

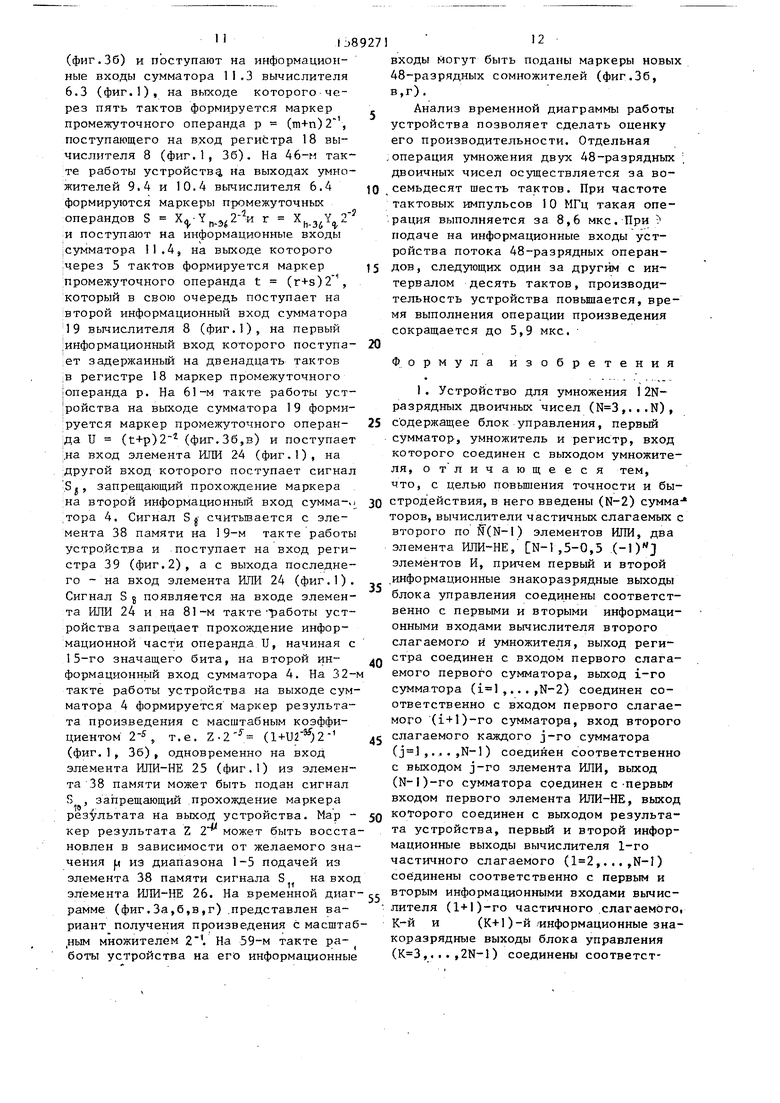

Блок управления (фиг. 2) содержит четыре элемента ИЛИ-НЕ 28.1-28.4, че5 тыре группы элементов И-НЕ 29.1-29.4, 30.1-30.4, 31.1-31.4, 32.1-32.4, четырехразрядный элемент И-НЕ 33, элемент И 34, триггеры 35, 36, счетчик 37, элемент 38 памяти, регистр 39

о (последовательного сдвига на сорбк три такта).

Блок управления предназначен для очистки (обнуления) устройства после подачи электропитания, для образовас НИН кодов частных сомножителей Х,

Yn,Yn,. .. ,,X,j,, Y, для ввода и запрещения управляющих маркеров (запятых) у промежуточных кодов, возникающих в . процессе вычисления произведения, согласно временной диаграмме работы устройства (фиг.З а,б,в,г). Управляющие сигналы S.-Sj. хранятся в элементе 38 памяти и устанавливаются согласно адресам, формируемым счетчиком 37.

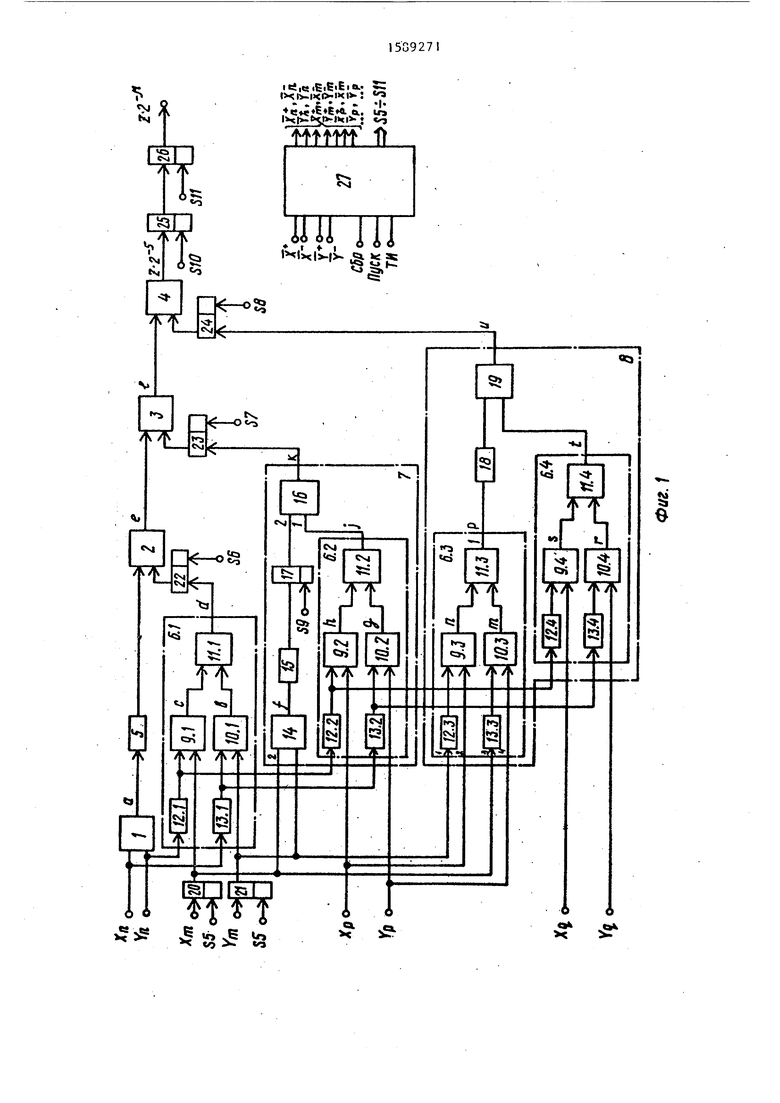

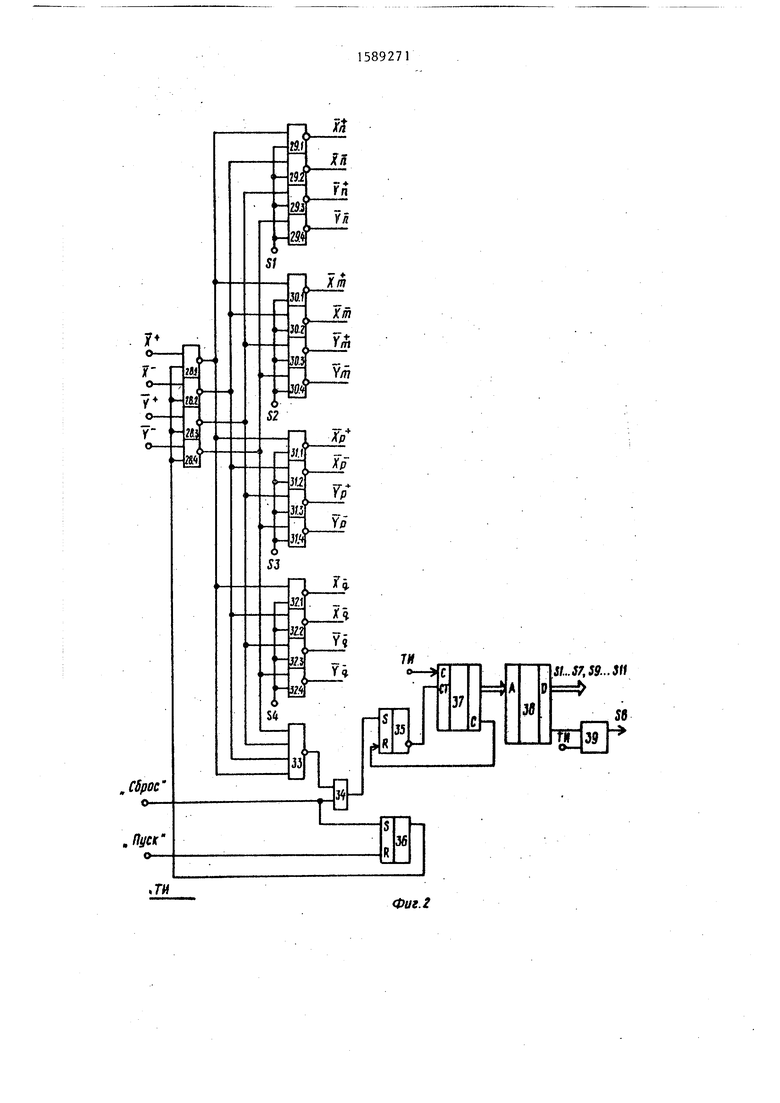

Временная диаграмма (фиг.З а,б,с, г) представляет изображения в общем виде двоичных знакоразрядных кодов,, формирующихся на выходах умножителей и сумматоров устройства, и иллюстрирует процесс преобразования информа- ции. Следует иметв в виду, что двоич- |ный знакоразрядный код физически реализован как два прямых двоичных кода, передающихся синхронно по раздвоенной информационной шине. Положительная часть двоичного числа передается по I положительному каналу информационной iшины,и обозначена (фиг. 2) X Y iотрицательная - по отрицательному шины и обозначена Х, Y, Х,

Устройство для умножения 48-разряд ;ных двоичных чисел работает следующим :Образом.

; После подачи на устройство элект- ;ропитания и тактовых импульсов (ТИ) ;по сигналу Сброс (фиг. 2) тригг еры 35, 36 устанавливаются в 1, при этом сигнал с прямого выхода тригге- ра 36 запрещает прохождение сигналов через элементы ИЛИ-НЕ 28.1-28.4, а сигнал с инверсного, выхода триггера 35 поступает на разрешающий вход счетчика 37, который через несколько ТИ достигает нулевого знач.ения и формирует сигнал переноса Р, который возвращает триггер 35 в исходное состояние и запрещает счет счетчику 37. Таким образом в элементе 38 памяти ус- танавливается первоначальньй адрес. После прохождения 86 ТИ устройство обнуляется и на него может быть подан сигнал Пуск, который сбрасьшает триггер 36 и разрешает прохождение сигналов через элементы ИЛИ-НЕ 27.1-27.4, определяя готовность устройства к работе.

При появлении на входе элементов ИЛИ-НЕ 28.1-28.4 первого (управляюще- го) бита информации - маркера триггер 35 устанавливается в положение 1 и запускает счетчик 37, формирующий адреса управляющих сигналов , записанных в элементе 38 памяти. По нулевому адресу записан .сигнал S (фиг.За), которьй подается на входы элементов И-НЕ 29.1-29.4 (фиг.2) и разрешает прохождение на входные ин

формационные шины умножителя 1 (фигJ) 12-разрядных операндов Х,, Y. Умножители 1, 9.1-9.4, 10.1-10.4 и 14 и , сумматоры 2, 3, 4, 11.1-11.4, 16 и 19 функционируют в режиме автоматического масштабирования, т.е. выполняют операции вида Z (X Y)2, С (А+В)2- или С (А+В)2-. Таким образом, на 10-м такте работы устройства на выходе умножителя 1 (фиг.1) формируется марквр промежуточного операнда а X.Y.2 (фиг. За), поступающего в регистр 5 (фиг.1). На . 12-м такте из элемента 38 памяти на входы элементов И 20, 21 поступает сигнал Sj (фиг.1. За), а на выходе элементов И 20, 21 формируется, маркер операндов Х , Y. На 13-м такте действие сигнала S прекращается и на вькодах элементов И-НЕ 29.1-29.4 устанавливаются нулевые уровни информационных сигналов, одновременно из элемента 38 памяти на входы элементов И-НЕ 30.1-30.4 поступает сигнал S.2 (фиг. 2, За) , разрешающий прохождение на входные информационные шины умножителей 9.1 и 10.1 вычислителя 6.1 12-разрядных операндов Х,и Yj соответственно, при этом на вторые входы умножителей 9.1 и 10.1 поступают задержанные на два.надцать тактов в регистрах 12.1 и 13.1 операнды X „. и Y. Через десять тактов относительно S ,- на выходах умножителей 9.1 и 10.1 Формируются маркеры промежуточных операндов С .,2 иВ X к Yfr,-2 соответственно (фиг.1, За), которые поступают на информационные входы сумматора 11.1, на выходе.которого через пять тактов формируется маркер промежуточного операнда d (b + с)2- (фиг. За). На 25-м такте работы устройства действие сигнала S.J прекращается и на выходах элементов И-НЕ 30.1-30.4 устанавливаются информационные нули; одновременно из элемента 38 памяти (фиг.2) на входы элементов 31.1-31.4 поступает сигнал S, , разрешающий прохождение в вычислитель 7 на вторые -информационные входы умножителей 9.2 и 10.2 вычислителя 6.2 12-разрядных операндов Хр, YP, при этом на первые входы умножителей 9.2 и 10.2 поступают задержанные на двадцать четыре такта в регистрах 12.1, 12.2 и 13 .1 , 13 .2 операнды Х„ и Y . На 17-м такте рабо- п П

ТЫ устройства на первый информацион .158927

ньй вход сумматора 2 поступает маркер операнда а, задержанного на,семь тактов в регистре 5. На втором информационном входе сумматора 2 элементом ИЛИ 22 поддерживается информационный нуль. Начиная с 18-го такта, сумматор 2 осуществляет суммирование операнда а с нулевыми старшими разрядами операнда d (фиг,1, За), учитывающими JQ множитель согласно алгоритму (2) . На 27-м такте работы одновременно с формированием маркера операнда d на выходе сумматор а .11.1 из элементов 38 памяти (фиг.2) на вход элемента j ИЛИ 22 поступает сигнал S, запрещающий прохождение маркера операнда d на второй информационный вход сумматора 2 и. пропускающий без преобразования информационную часть операнда. 20 На 22-м такте на выходе сумматора 2 формируется маркер промежуточного операнда е (a+d2 )Z , который поступает на первый информационный вход сумматора 3 (фиг.1. За, б). Сформиро- 25 ванные на 12-м такте работы устройства двумя элементами И 20, 21 маркеры и операнды X , Y поступают также на информационные входы умножителя 14 вычислителя 7 (фиг.1), на выходе ко- зо торого через десять тактов формируется маркер промежуточного операнда f , который поступает на вход регистра 15. На 34-м такте работы устройства на выходах умножителей 9.2 и 10.2 формируются маркеры промежуточных операндов h Xp-Y,2 и q X . f2 соответственно (фиг.36), когорые поступают на инфор- мационные входы сумматора 11.2 (фиг.1), дд на выходе которого через пять тактов . формируется маркер промежуточного операнда i (q+h)2 (фиг.36), который в свою очередь поступает на первый информационный вход сумматора 16 вы- j числителя 7 (фиг.1). На второй инфорационный входэтого сумматора постуает задержанный на восемнадцать тактов промежуточньй операнд f, причем аркер этого операнда запрещается jg элементом ИЛИ 17 по сигналу Sj, приодящему из элемента 38 памяти (фиг.2), на 40-м такте работы устойства. На 44-м такте на выходе суматора 16 формируется маркер проме- ее , уточного операнда k (f2 + j) (фиг.36) и поступает на вход элемента ЛИ 23, одновременно на второй вход элемента ИЛИ 23 поступает сигнал Sy

35

-i

8927

р JQ . j 2025 зо ), дд . jgее ,

35

i

1,10

из элемента 38 памяти (фиг.2), который запрещает прохождение маркера операнда k на второй информационный вход сумматора 3 (фиг.1, 36), но про пускает информационную часть операнда k. Элементы ИЛИ 22-24 идентичны один другому и функционируют одинаково. Сумматор 3, начиная с 23-го такта работы устройства, осуществляет суммирование операнда е с нулевыми старщи- ми разрядами Операнда k, учитьшающи- ми множитель 2 в алгоритме (2), а после прихода сиагнала S, к операнду е подсуммируется , , информационная часть операнда k, причем так, чтобы первый значащий бит операнда k сложился с двадцать четвертым битом опе- рагзда е (фиг.36). На 27-м такте работы устройства на выходе сумматора 3 формируется маркер промежуточного операнда 1 (e+k2 2, который поступает на первый информационный вход сумматора 4 (фиг.1), который, начиная с 28-го такта работы устройства, будет осуществлять суммирование операнда 1 с нулевыми старшими разрядами операнда U, учитьшающими множитель 2 в алгоритме (2). На 37- м . такте работы устройства действие сигнала S } прекращается и на выходах элементов И-НЕ 31.1-31.4 устанавливаются информационные нули; одновременно из элемента 38 памяти (фиг,2) на входы элементов И-НЕ 32.1-32.4 поступает сигнал S. , разрешающий прохожде- ние в вычислитель 8 на вторые информационные входы умножителей 9.4 и 10.4 вычислителя 6.4 12-разрядных операндов Х-, YO, при этом на первые . информационные входы умножителей 9.4, 10.4 поступают задержанные на трид- цать шесть тактов в регистрах 12.1, 12.2, 12.4 и 13.1, 13.2, 13.4 операнды Х п управляющим битом (маркером). На 24-м такте работы устройства в вычислитель 8 на первые информационные входы умножителей 9.3, 10.3 поступает маркер операндов Х, Y , задержанньт на двенадцать тактов в регистрах 12.3 и 13.3 (фиг.1). На 25-м такте на вторые информационные входы умножителей 9.3 и 10.3 поступают первые информационные биты операндов Хр, Yp. Через десять тактов после прихода маркеров на входы умножителей 9.3 и 10.3 на их выходах формируются маркеры промежуточных операндов n Xp-Y| 2 ига р-2 соответственно

IJ8

(фиг.Зб) и поступают на информационные входы сумматора 11,3 вычислителя 6.3 (фиг.1), на выходе которого через пять тактов формируется маркер промежуточного операнда р ()2, поступающего на вход регистра 18 вычислителя 8 (фиг.1, 36). На 46-м такте работы устройству, на выходах умножителей 9.4 и 10.А вычислителя 6.4 формируются маркер1з1 промежуточных операндов S Х.У„., г X.. и поступают на информационные входы :Сумматора 11.4, на выходе которого через 5 тактов формируется маркер промежуточного операнда t (r+s), который в свою очередь поступает на :второй информационный вход сумматора 19 вычислителя 8 (фиг.1), на первый информационный вход которого поступа- ет задержанный на двенадцать тактов ;В регистре 18 маркер промежуточного |операнда р. На 61-м такте работы уст- :ройства на выходе сумматора 19 форми- :руется маркер промежуточного операн- :да и (t+p)2 (фиг.36,в) и поступает ;.на вход элемента ИЛИ 24 (фиг.1), на другой вход которого поступает сигнал Sj, запрещающий прохождение маркере , на второй информационный вход сумма-.i тора 4. Сигнал S j- считывается с элемента 38 памяти на 19-м такте работы устро.йстза и поступает на вход регистра 39 (фиг.2), а с выхода последнего - на вход элемента ИЛИ 24 (фиг.1). Сигнал S 5 появляется на входе элемента ИЛИ 24 и на 81-м такте работы устройства запрещает прохождение информационной части операнда и, начиная с 15-го значащего бита, на второй ин- формационный вход сумматора 4. На 32такте работы устройства на выходе сумматора 4 формируется маркер результата произведения с масштабным коэффициентом 2-, т.е. Z.2 ( (фиг.1, 36), одновременно на вход элемента ИЛИ-НЕ 25 (фиг.1) из элемента 38 памяти может быть подан сигнал S , запрещающий прохождение маркера рез у льтата на выход устройства. Map - кер результата Z 2 может быть восстановлен в зависимости от желаемого значения р из диапазона 1-5 подачей из элемента 38 памяти сигнала S на вход элемента ИЛИ-НЕ 26. На временной диаг рамме (фиг.За,б,в,г) .представлен на- риант получения произведения с масштабным множителем . На такте ра- боты устройства на его информационные

12

входы могут быть поданы маркеры новых 48-разрядных сомножителей (фиг.Зб, в,г).

Анализ временной диаграммы работы устройства позволяет сделать оценку его производительности. Отдельная ; операция умножения двух 48-разрядных двоичных чисел осуществляется за восемьдесят шесть тактов. При частоте тактовых импульсов 10 МГц такая операция выполняется за 8,6 мкс. При подаче на информационные входы устройства потока 48-разрядных операндов , следующих один за другим с интервалом десять тактов, производительность устройства повьшается, время выполнения операции произведения сокращается до 5,9 мкс.

Формула изобретения

венно с первыми входами т-го и (т+1)-го элементов И (,...,К-1,5- -0,5 (-1) , выходы которых соединены с третьим и четвертым информационными входами соответствующих вычислителей с второго по N-й частичньк слагаемых, нулевые информационные выходы которых соединены соответственно с первыми входами (N-1) элемен- тов ИЛИ, вторые входы N-1 ,5-0,5(-1) элементов И соединены с первым управляющим выходом блока управления, управляющие выходы с второго по N-й которого соединены соответственно с г вторыми входами (N-1) элементов ИЛИ, управляющие входы нечетных вычислителей частичных слагаемых соединены соответственно с Р-ми управляющими выходами блока управления (,5N - -0,75-0,25(-1),...,3N-2,5-0,5 (-I)} последующие два управляющих выхода которого соединены соответственно с вторыми входами первого и второго элементов ИЛИ-НЕ, первый и второй инфор- мационные знакоразрядные входы первого сомножителя устройства соединены соответственно с первым и вторым информационными знакоразрядными входами второго сомножителя устройства, 7 входы сброса, пуска и тактовый вход которого соединены соответственно с входами сброса, пуска и тактовым входом блока управления.

ми выходами блока, вход пуска которого соединен с входом установки первого триггера, прямой выход которого соединен с вторыми входами первого, второго, третьего и четвертого элементов ИЛИ-НЕ, выход элемента И соединен с входом сброса второго- триггера, инверсный выход которого соединен с разрешающим входом счетчика, информационный вход которого соединен с такто- вым входом блока и управляющим входом регистра, информационный выход счетчика соединен с адресным входом элемента памяти, t-й выход которого (,...,N) соединен соответственно с вторыми входами элементов И-НЕ t-й группы, 2N-й выход элемента памяти соединен с информационным входом регистра, выходы элемента памяти, начиная с ()-ro выхода, и вьжод с регистра образуют группу управляющих выходов блока.

А. Устройство по ПП.1 и 3, о т - . л п чающееся тем, что вычис- литель третьего частичного слагаемого содержит вычислитель второго частич-i ного слагаемого, умножитель, сумма-п тор, регистр и элемент ИЛИ, причем информационные входы вычислителя второго частичного слагаемого являются одноименными входами вычислителя третьего частичного слагаемого, нулевой информационный выход вычислителя второго частичного слагаемого соединен с .первым информационным входом сумматора, второй информационный вход которого соединен с выходом элемента

15

1589271

IIIIH, первый вход которого соединен с выходом регистра, выход которого соединен с выходом умножителя, первый и второй входы которого соединены COOT- етственно с пятым и шестым информа- угионными входами вычислителя третьего частичного слагаемого, первый и второй информационные выходы вычислителя второго частичного слагаемого явля ютея первым и вторым информационными уходами вычислителя третьего частич- його слагаемого, нулевой информацион- jibM выход которого соединен с выходом Ьумматора, второй вход элемента ИЛИ соединен с (2N+1)-M управляющим выхо Дом блока управления.

пичающеесй тем, что вьгчис- |питель четвертого частичного слагаемого содержит два вычислителя второ- Ьо частичного слагаемого, регистр и сумматор, выход которого соединен с Нулевым информационным выходом вычислителя четвертого частичного слагаемого, информационные входы вычислителя второго частичного слагаемого и первый и второй информационные выходы вычислителя третьего частичного слагаемого соединены соответственно с одноименными информационными входами первого и второго вычислителей второго частичного слагаемого вычислителя четвертого частичного слагаемого, нулевые выходы первого и второго вычислителей второго частичного слагаемого соединены соответственно с входом регистра и первым информационным входом сумматора, второй информацион1

16

ный вход которого соединен с выходом регистра.

5

0 управляющий вход которого (при нечетном N) является последующим за управляющим входом вычислителя (N-2)-ro частичного слагаемого, информационные входы вьмислителя N-ro частичного

5 слагаемого с 2(N-p)+l)-ro по 2N-й являются соответственно первым и вторым информационными входами вычислителя р-го .частичного слагаемого, -нулевой информационньй выход вычислителя

0 (N-p)-ro частичного слагаемого соединен с входом регистра, выход которого соединен с первым информационным входом сумматора, второй информационный вход которого соединен с нулевым ин-,- формационным входом вьиислителя р-го частичного слагаемого, а выход сумматора является нулевым информационным выходом вычислителя N-ro частичного слагаемого.

itJ,«.,E,6«Eia.. IXl. o

(.

,t,,ggi,v nttttt D

J

to

e

,ги

Фиг. 2

t г 3 5 87 6 9 W2030

I И I I I И И I I i I И I I И 1 I I И I I I М I

ЛЯXmKP

ii() f

e ( ,1,1/7 /7 .

f Xm- tn-Z H it 10 0 /ifz/3

-Хп-г -Уп-г JC :

h Xp-Yn. i .

j,)

fST

/

K ffTMirL

f fe if 2-) 2 J--

.g-).i

n-Xp-Ym 12 2 ji

/7- On+flJk 2

r- r«-3fKg-f-

t-(r S} l

u()

l 2 () . t

I,jzr

I Jgr

Фиг. За

f-ri-f, , - TT-lUJ 10 Q 0

7т

10 Olat at

fST

- 1ТГЗГТТ

5Т

jg 05060

И I I I I I 1 I i I 11 I I I I I 11 1 M II 1 I M I I I

6070водо

1 И t I I I И ( ( I i I I I М } I I f I I I I I t I М М

5в(К050)

I

м

fffr

-LL

:sr

010

ж.

oW

or

7r

g|g

S:

Ж

оЖ

/Н |g

/241 g

1Ш

/« l/zs

гзИ/зг

SB 5(ке50)5з Se

Юг

±L

Л

I

HI

Л

Hb

ffr

ill

fOT

Л.

Ibt

Л7г

Ж

Г

ЖЕ:

Ж

Щ

TZe

5г

ЛФаг, 36

90 100 110 120 1 I И I I М I I I I 1 I I И I I I I I I I I I

,1 .. . ....,

j% ff| f ,y

JH

Jr

I . .

,f/ --

r

g1

Л7г

/17

ilL

.УГ

H

WT

Tbi :

Фиг. Зг

| Бобков В.А., Сухопаров А.И | |||

| и др | |||

| Электрический конденсатор переменной емкости | 1925 |

|

SU1815A1 |

| - Микропроцессорные средства и системы | |||

| Пневматический водоподъемный аппарат-двигатель | 1917 |

|

SU1986A1 |

Авторы

Даты

1990-08-30—Публикация

1988-10-24—Подача