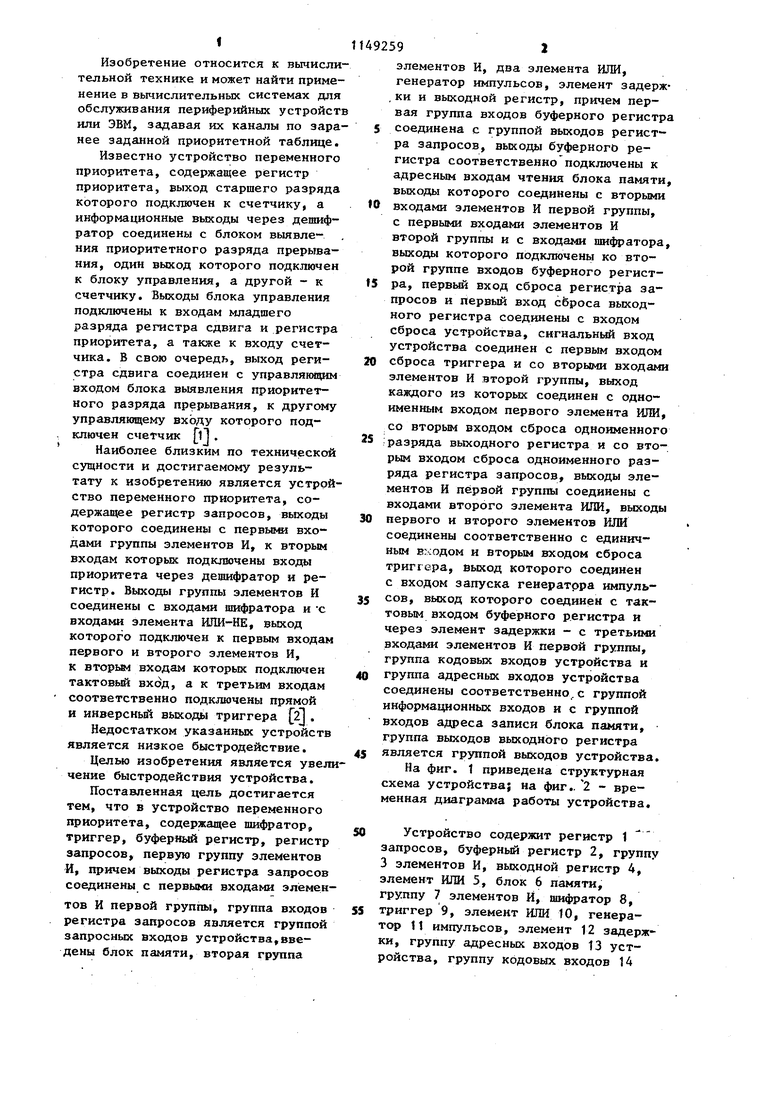

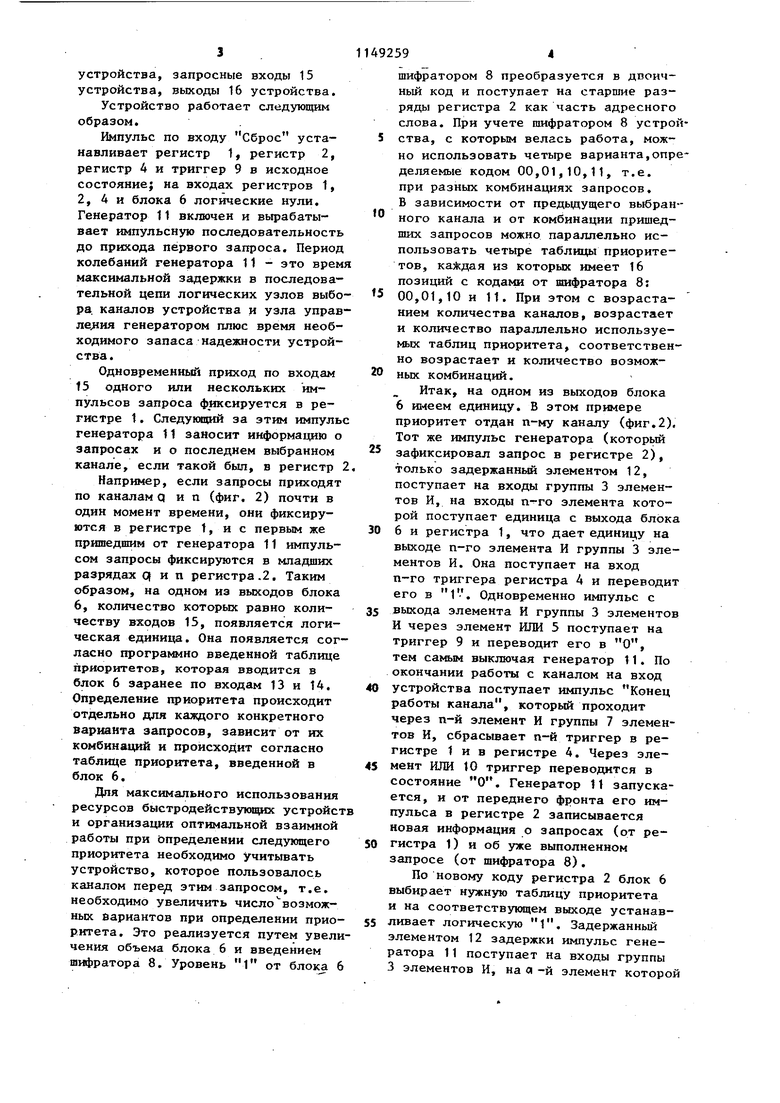

t Изобретение относится к вычисли тельной технике и может найти применение в вычислительных системах для обслуживания периферийных устройст или ЭВМ, задавая их каналы по зара нее заданной приоритетной таблице. Известно устройство переменного приоритета, содержащее р(агистр приоритета, выход старшего разряда которого подключен к счетчику, а информационные выходы через дешифратор соединены с блоком выявления приоритетного разряда прерывания, один выход которого подключен к блоку управления, а другой - к счетчику. Выходы блока управления подключены к входам младшего разряда регистра сдвига и регистра приоритета, а также к входу счетчика. В свою очередь, выход регистра сдвига соединен с управляющим входом блока выявления приоритетного разряда прерывания, к другому управляющему входу которого под, ключей счетчик l1 . Наиболее близким по технической сущности и достигаемому результату к изобретению является устрой ство переменного приоритета, содержащее регистр запросов, выходы которого соединены с первыгет входами группы элементов И, к вторым входам которых подключены входы приоритета через дешифратор и регистр. Выходы группы элементов И соединены с входами ошфратора и с входами элемента ШШ-НЕ, выход которого подключен к первым входам первого и второго элементов И, к вторым входам которых подключен тактовый вход, а к третьим входам соответственно подключены прямой и инверсный Быходь триггера 2 . Недостатком указанных устройств является низкое быстродействие. Цепью изобретения является увел чение быстродействия устройства. Поставленная цель достигается тем, что в устройство переменного приоритета, содержащее шифратор, триггер, буферный регистр, регистр запросов, первую группу элементов И, причем выходы регистра запросов соединены с первыми входами элемен тов И первой группы, группа входов регистра запросов является группой запросных входов устройства,введены блок памяти, вторая группа 92 элементов И, два элемента ИЛИ, генератор импульсов, элемент задержки и выходной регистр, причем первая группа входов буферного регистра соединена с группой выходов регистра запросов, выходы буферного регистра соответственно подключены к адресным входам чтения блока памяти, выходы которого соединены с вторыми входами элементов И первой группы, с первы№1 входами элементов И второй группы и с входами шифратора, выходы которого подключены ко второй группе входов буферного регистpa, первый вход сброса регистра запросов и первый вход сброса выходного регистра соединены с входом сброса устройства, сигнальный вход устройства соединен с первым входом сброса триггера и со вторыми входами элементов И второй группы, выход каждого из которых соединен с одноименным входом первого элемента ИЛИ, со BTOpbw входом сброса одноименного разряда выходного регистра и со вторым входом сброса одноименного разряда регистра запросов, выходы элементов И первой группы соединены с входами второго элемента ИЛИ, выходы первого и второго элементов ИЛИ соединены соответственно с единичным вкодом и вторым входом сброса триггера, выход которого соединен с входом запуска генератора импульсов, выход которого соединен с тактовым входом буферного регистра и через элемент задержки - с третьими вxoдa 0f элементов И первой группы, группа кодовьк входов устройства и группа адресных входов устройства соединены соответственно с группой информационных входов и с группой входов адреса записи блока памяти, группа выходов выходного регистра является группой выходов устройства. На фиг. 1 приведена структурная схема устройства; на фиг.. 2 - временная диаграмма работы устройства. Устройство содержит регистр 1 запросов, буферный регистр 2, группу 3 элементов И, выходной регистр 4, элемент ИЖ 5, блок 6 памяти, группу 7 элементов И, шифратор 8, триггер 9, элемент ИЖ 10, генератор 11 импульсов, элемент 12 задержки, группу адресных входов 13 устройства, группу кодовых входов 14

устройства, запросные входы 15 устройства, выходы 16 устройства.

Устройство работает следующим образом.

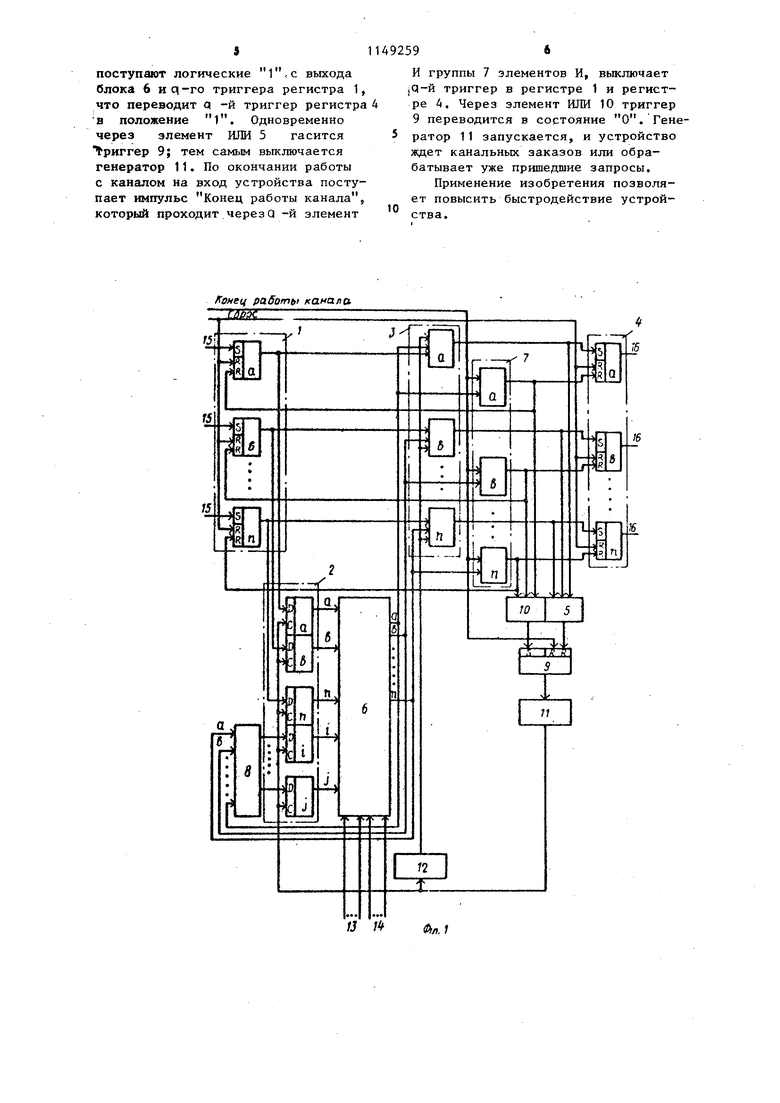

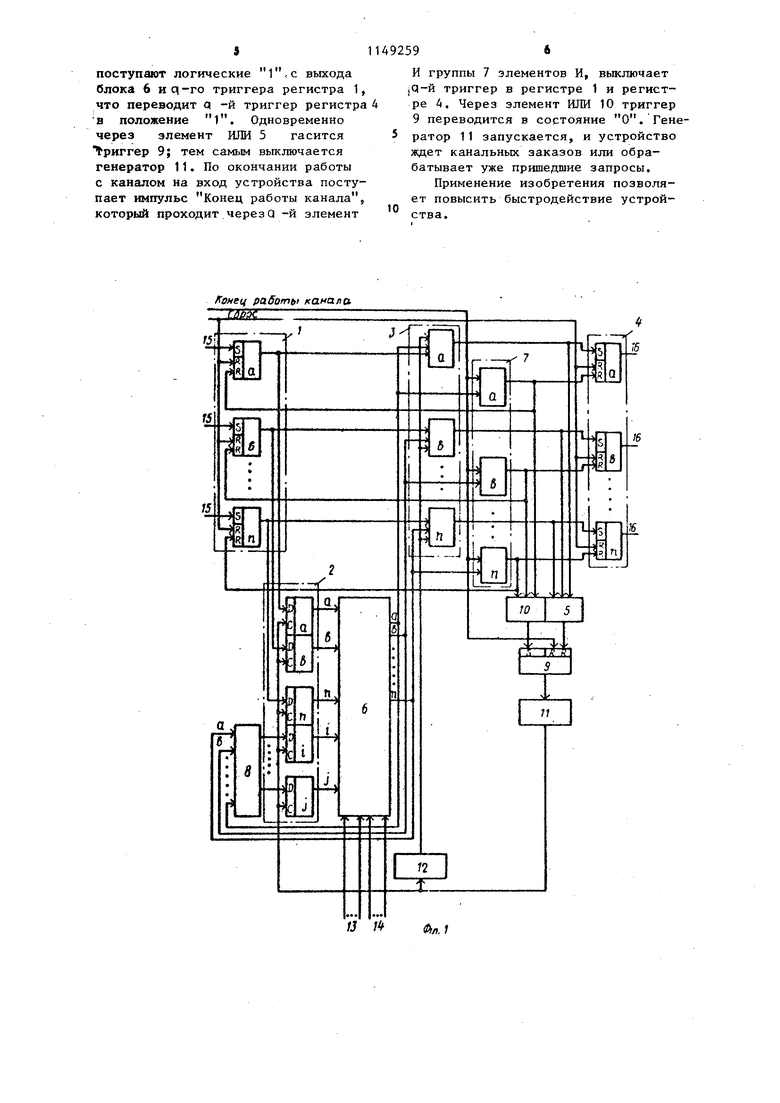

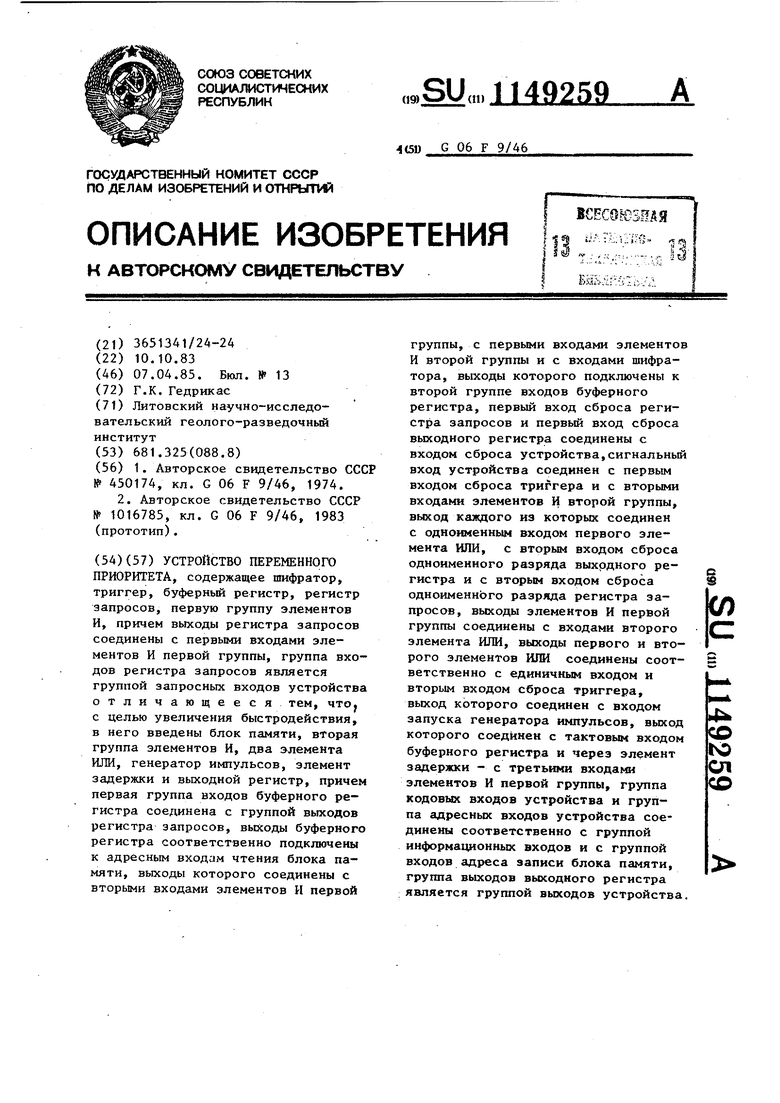

Импульс по входу Сброс устанавливает регистр 1, регистр 2, регистр 4 и триггер 9 в исходное состояние; на входах регистров 1, 2, 4 и блока 6 логические нули. Генератор 11 включен и вьфабатывает импульсную последовательность до прихода первого запроса. Период колебаний генератора 11 - это врем максимальной задержки в последовательной цепи логических узлов выбора, каналов устройства и узла управлед1ия генератором плюс время необходимого запаса надежности устройства .

Одновременный приход по входам 15 одного или нескольких импульсов запроса фиксируется в регистре 1. Следующий за этим импуль генератора 11 заносит информацию о запросах и о последнем выбранном канале, если такой бьш, в регистр

Например, если запросы приходят по каналам Q и п (фиг. 2) почти в один момент времени, они фиксируются в регистре 1, и с первым же пришедшим от генератора 11 импульсом запросы фиксируются в младших разрядах Q и п регистра .2. Таким образом, на одном из выходов блока 6, количество которых равно количеству входов 15, появляется логическая единица. Она появляется согласно программно введенной таблице приоритетов, которая вводится в блок 6 заранее по входам 13 и 14. Определение приоритета происходит отдельно для каждого конкретного варианта запросов, зависит от их комбинаций и происходит согласно таблице приоритета, введенной в блок 6.

Для максимального использования ресурсов быстродействующих устройс и организации оптимальной взаимной работы при Определении следующего приоритета необходимо учитывать устройство, которое пользовалось каналом этим запросом, т.е. необходимо увеличить число возможных вариантов при определении приоритета. Это реализуется путем увелчения объема блока 6 и введением шифратора 8. Уровень 1 от блока

шифратором 8 преобразуется в дпоичный код и поступает на старшие разряды регистра 2 как часть адресного слова. При учете шифратором 8 устройства, с которым велась работа, можно использовать четьфе варианта,определяемые кодом 00,01,10,11, т.е. при разных комбинациях запросов. В зависимости от предьщущего выбранного канала и от комбинации пришедших запросов можно параллельно использовать четьфе таблицы приоритетов, каждая из которых имеет 16 позиций с кодами от шифратора 8:

5 00,01,10 и 11. При этом с возрастанием количества каналов, возрастает и количество параллельно используемых таблиц приоритета, соответственно возрастает и количество возможных комбинаций.

Итак, на одном из выходов блока 6 шчеем единицу. В этом примере приоритет отдан п-му каналу (фиг.2), Тот же импульс генератора (которьш

5 зафиксировал запрос в регистре 2), только задержанный элементом 12, поступает на входы группы 3 элементов И, на входы п-го элемента которой поступает единица с выхода блока

0 6 и регистра 1, что дает единицу на выходе п-го элемента И группы 3 элементов И. Она поступает на вход п-го триггера регистра 4 и переводит его в 1. Одновременно импульс с

5 выхода элемента И группы 3 элементов И через элемент ИЛИ 5 поступает на триггер 9 и переводит его в О, тем саьым выключая генератор 11. По окончании работы с каналом на вход

0 устройства поступает импульс Конец работы канала, который проходит через п-й элемент И группы 7 элементов И, сбрасывает п-й триггер в регистре 1 и в регистре 4. Через элемент ИЛИ 10 триггер переводится в состояние О. Генератор 11 запускается, и от переднего фронта его импульса в регистре 2 записывается новая информация о запросах (от регистра 1) и об уже выполненном запросе (от шифратора 8).

По новому коду регистра 2 блок 6 выбирает нужную таблицу приоритета и на соответствукицем выходе устанавливает логическую 1. Задержанный элементом 12 задержки импульс генератора 11 поступает на входы группы 3 элементов И, на а-и элемент которой поступают логические выхода блока 6 триггера регистра 1, что переводит а -и триггер регистра в положение 1. Одновременно через элемент ИЛИ 5 гасится триггер 9; тем самым выключается генератор 11. По окончании работы с каналом на вход устройства поступает нмпульс Конец работы канала, который проходит черезQ -и элемент 9 И группы 7 элементов И, выключает Q-u триггер в регистре 1 и регистре 4. Через элемент ИЛИ 10 триггер О. Гене9 переводится в состояние ратор 11 запускается, и устройство ждет канальных заказов или обрабатывает уже пришедшие запросы. Применение изобретения позволяет повысить быстродействие устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство для обработки прерываний | 1983 |

|

SU1126956A1 |

| Устройство для программного управления технологическим оборудованием | 1989 |

|

SU1714575A1 |

| Устройство для распределения групповых заявок по процессорам | 1985 |

|

SU1254485A1 |

| Устройство для связи процессоров в вычислительной системе | 1988 |

|

SU1515170A1 |

| Устройство для обмена информацией в мультипроцессорной вычислительной системе | 1985 |

|

SU1312597A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1990 |

|

SU1702380A1 |

| Устройство для распределения заданий процессорам | 1987 |

|

SU1453406A1 |

| Устройство маршрутизации | 1988 |

|

SU1695329A1 |

| Устройство для сопряжения процессоров в вычислительной системе | 1985 |

|

SU1332327A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1136162A1 |

УСТРОЙСТВО ПЕРЕМЕННОГО ПРИОРИТЕТА, содержащее шифратор, триггер, буферный регистр, регистр запросов, первую группу элементов И, причем выходы регистра запросов соединены с первыми входами элементов И первой группы, группа входов регистра запросов является группой запросных входов устройства отличающееся тем, что с целью увеличения быстродействия, в него введены блок памяти, вторая группа элементов И, два элемента ИЛИ, генератор импульсов, элемент задержки и выходной регистр, причем первая группа входов буферного регистра соединена с группой выходов регистра запросов, выходы буферного регистра соответственно подключены к адресным входам чтения блока памяти, выходы которого соединены с вторыми входами элементов И первой группы, с первыми входами элементов И второй группы и с входами шифратора, выходы которого подключены к второй группе входов буферного регистра, первый вход сброса регистра запросов и первый вход сброса выходного регистра соединены с входом сброса устройства,сигнальный вход устройства соединен с первым входом сброса триггера и с вторыми входами элементов И второй группы, выход каждого из которых соединен с одноименным входом первого элемента ИЛИ, с вторым входом сброса одноименного разряда выходного регистра и с вторым входом сброса одноименного разряда регистра за(Л просов, выходы элементов И первой группы соединены с входами второго элемента ИЛИ, выходы первого и второго элементов ИЛИ соединены соответственно с единичным входом и вторым входом сброса триггера, выход которого соединен с входом 4 СО запуска генератора импульсов, выход которого соединен с тактовым входом ю ел буферного регистра и через элемент задержки - с третьими входами ;о элементов И первой группы, группа ходовых входов устройства и группа адресных входов устройства соединены соответственно с группой информационных входов и с группой входов адреса записи блока памяти, группа выходов выходного регистра является группой выходов устройства.

раВоть хапала

а / .1

л

Инпильсы

ffjfodoffS ffa&i)odt peiucittfXL запросов f Ha Вых. VMS pamopa n om. fyxeda , pewcm: 3onp.i N a I u/u9fp.8 Ha Sbixo SflOKQ. Лг f.r noHJitnuS Ha Выход элеме задержки 12 На Выходе ipyhnbiM. из имп.-конец работы коноп На быходе группы 9а. И7 Ha&ffjfodsKS триггера Э на выходе Выходного регист/за t

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство переменного приоритета | 1972 |

|

SU450174A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство переменного приоритета | 1982 |

|

SU1016785A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-04-07—Публикация

1983-10-10—Подача