(54) АНАЛИЗАТОР ПЕРИОДИЧЕСКОЙ ПОСЛЕДОВАТЕЛЬНОСТИ

сигаАлов

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1981 |

|

SU984041A1 |

| Устройство для регистрации информации | 1984 |

|

SU1234858A1 |

| Устройство для передачи телеметрической информации | 1982 |

|

SU1030830A1 |

| Устройство для воспроизведения функций | 1982 |

|

SU1119041A1 |

| Устройство для измерения и контроля нелинейности амплитудной характеристики квазилинейных систем | 1981 |

|

SU974298A1 |

| Устройство для кодирования звуковых сигналов с инерционным компандированием | 1985 |

|

SU1356233A1 |

| Устройство для исследования цветового зрения | 1985 |

|

SU1261620A1 |

| Устройство для преобразования малокадрового телевизионного стандарта | 1985 |

|

SU1256245A1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО ПОИСКА КАНАЛОВ РАДИОСВЯЗИ | 2014 |

|

RU2563145C1 |

| Устройство для передачи телеизмерений | 1982 |

|

SU1018140A2 |

1

Изобретение относится к импульс1ной технике и может быть использовано для автоматического контроля функционирования радиотехнических устройств.

Известно устройство для сравнеш-1я периода следования импульсов с заданной нормой, содержащее вентиль, первый вход которого соединен со входом всего устройства, а также со входами двух линий задержек, причем выход первой .пинии задержки через триггер подключен ко второму входу вентиля, а выход второй линии задержки через второй триггер подключен к первому входу схемы И, выход которой через третью линию задержки соединен с сбросовыми входами второго и третьего триггеров, вход ..третьего триггера подключен к выходу вентиля, первый выход третьего триггера соединен со вторым входом схемы И, а второй выход через цепочку сопротивлений соединен с первым

ВХОДОМ схемы И, средняя точка цепочки сопротивлений, с параллельно включенной к ней интегрирующей емкостью, является выходом всего устройства. На выходе устройства формируется сигнал, амплитуда которого прямо пропорциональна из(4внению периода входной последовательности l.

Однако это устройство не реагирует на кратковременные изменения,

Ш происходящие во входном сигнале.

Наиболее близким по технической сущности к предлагаемому является устройство контроля шшульсных последовательностей, содержащее два

15 счетчика, два триггера, четыре схемы И, схему НЕ и схему ИЛИ. На выходе устройства появляется сигнал, если число сбоев входной последовательности превышает заданн то ве20личину 2 J.

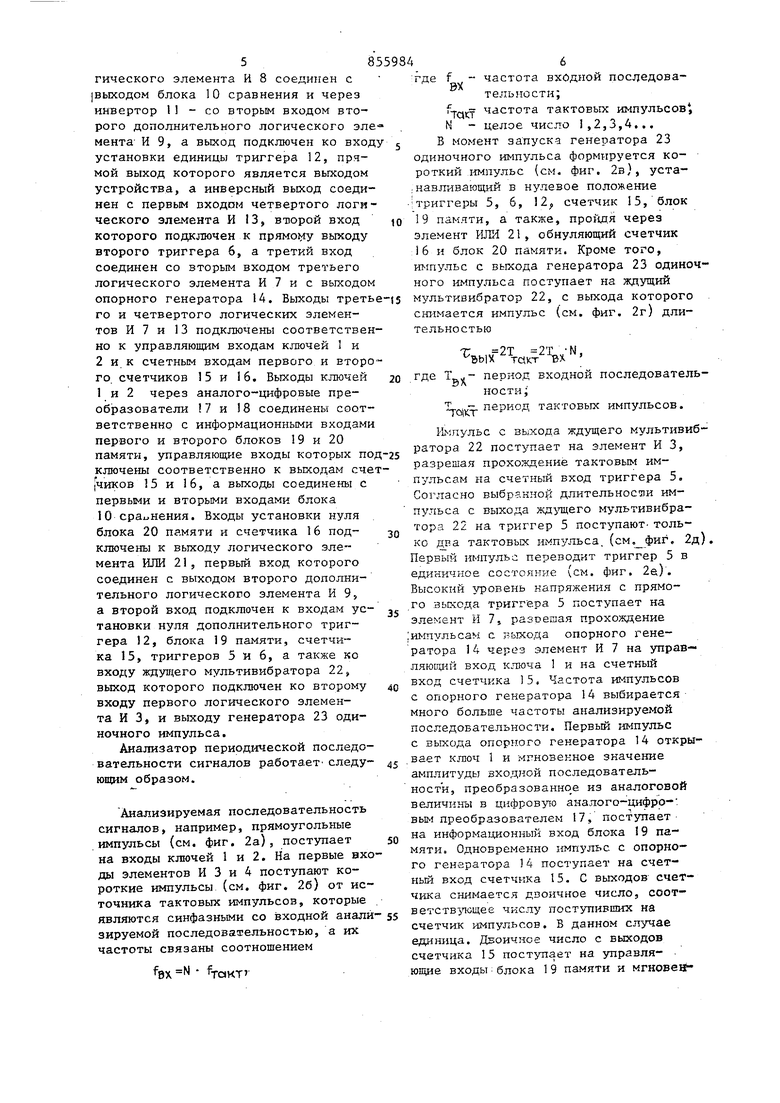

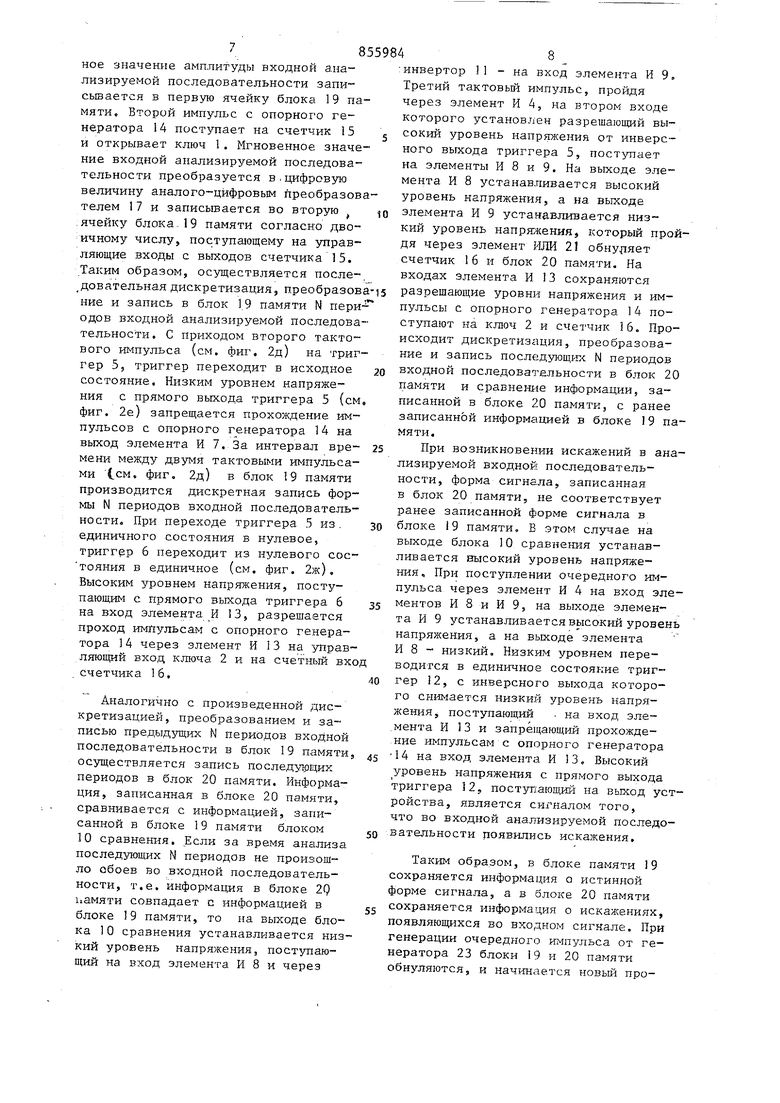

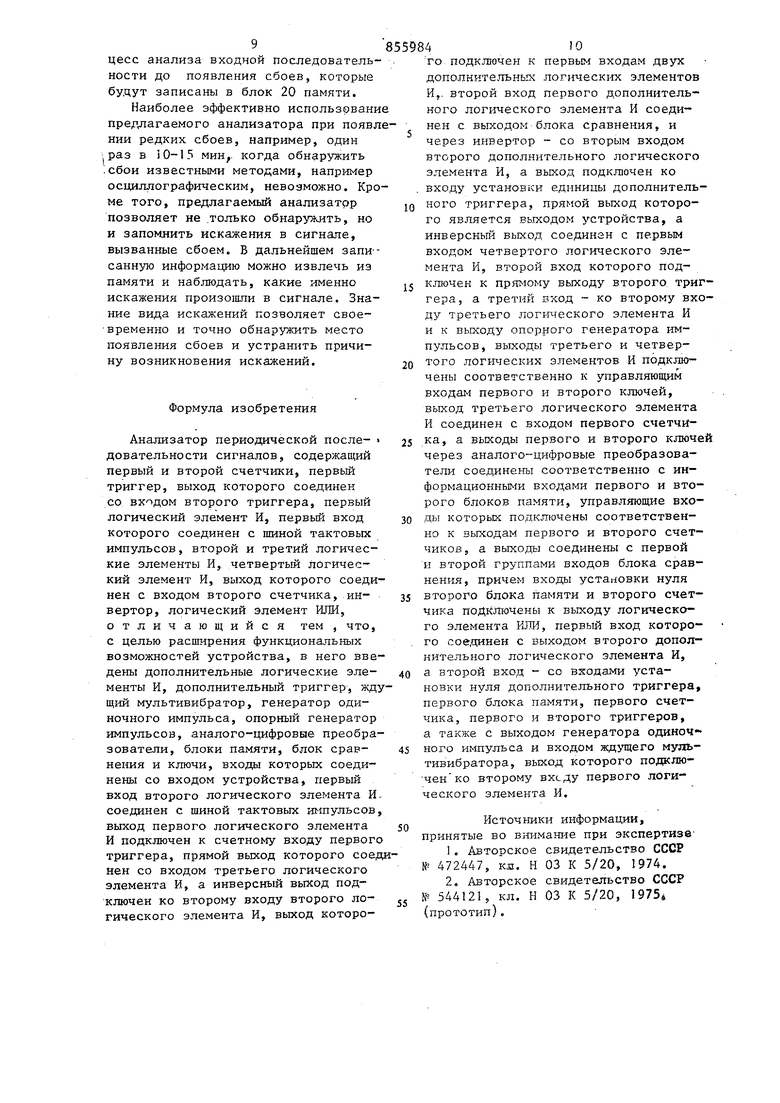

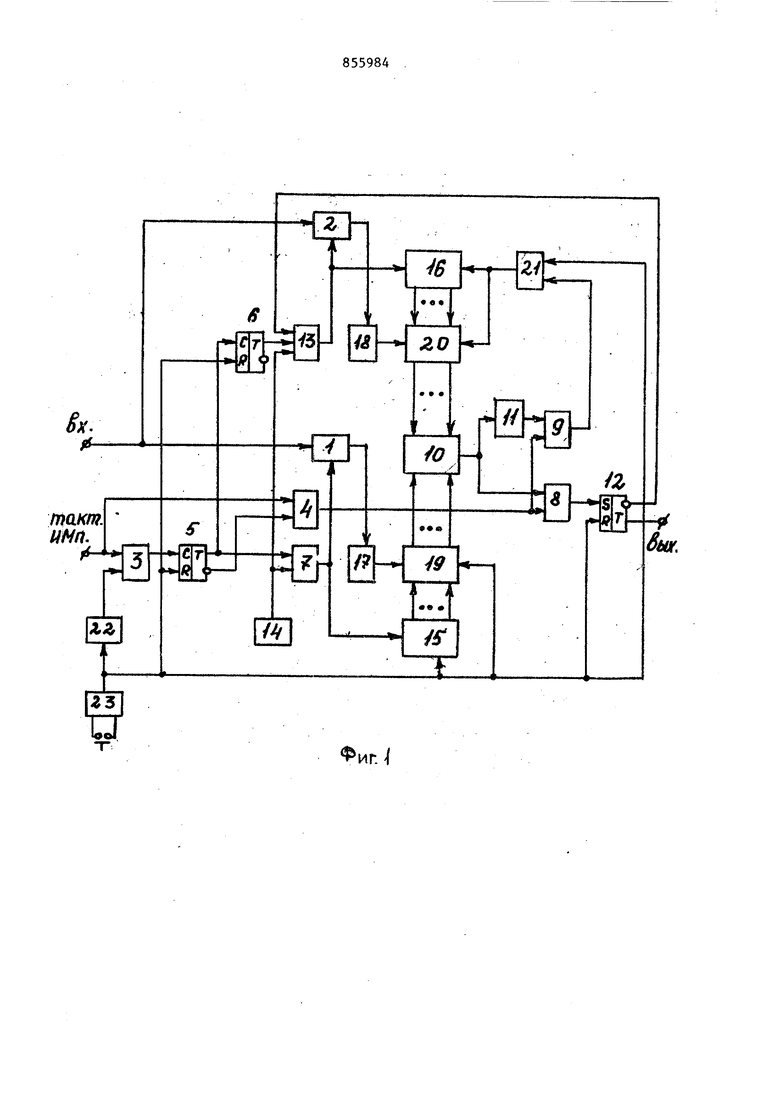

Однако такое устройство не анализирует форму сигна.па. При его использовании невозможно произвести качественный анализ входной последовательности и достаточно точно установить, какой сбой произошел в сигнале, какие параметры изменились в контролируемом сигнале. В указанном устройстве анализ входной последовательности осуществляется недостаточно полно по объему получаемой информации. Кроме того, устройство является недостаточно универсальным, его невозможно использовать для анализа аналоговых периодических сигналов таких как, например, гармонический сигнал, сигнал треугольной формы, линейно-изменяющийся сигнал и т.п. Цель изобретения - расширеш-ie функциональных возможностей. Поставленная цель достигается тем что в анализатор периодической последовательности сигналов, содержащи первый и второй счетчики, первый TpHrrfap, выход которого соединен со входом второго триггера, первый логический элемент И, первый вход кото рого соединен с шиной тактовых импульсов, второй и третий логич:еские элементы И, четвертый логический эле мент И, выход которого соединен со входом второго счетчика, инвертор, логический элемент ИЛИ, введены допо нительные логические элементы И, дополнительный триггер, ждущий мультивибратор, генератор одиночного импульса, опорный генератор импульсов аналого-цифровые преобразователи, бл ки памятиj блок сравнения и кхпочи, входы которых соединены со входом устройства, первый вход второго логи ческого элемента И соединен с шиной тактовых импульсов, выход первого л гического элемента И подключен к сч ному входу первого триггера, прямой выход которого соединен со входом третьего логическсоо элемента И, а версный выход подключен ко второму входу второго логического элемента И, выход которого подключен к первы входам двух дополнительных логических элементов И,.второй вход первого дополнительного логического элемента И соединен с выходом блока ср нения, и через инвертор - со вторым входом второго дополнительного логи ческого элемента И, а выход, подключ ко входу установки единицы дополнительного триггера, прямой выход которого является выходом устройства, а инверсный выход соединен с первым входом четвертого логического элемента И, второй вход которого подключен к прямому выходу второго триггера, а третий вход - ко второму входу третьего логического элемента И и к выходу опорного генератора импульсов, выходы третьего и четвертого логических элементов И подключены соответственно к управляющим входам первого и второго ключей, выход третьего логического элемента И соединен с входом первого счетчика, а выходы первого и второго ключей через аналого-цифровые преобразователи соединены соответственно с информационными входами первого и второго блоков памяти, управляющие входы которых подключены соответственно к выходам первого и второго счетчико, а выходы соединены с первой и второй группами входов блока сравнения, причем входы установки нуля второго блока памяти и-второго счетчика подключены к выходу логического элемента ИЛИ, первый вход которого соединен с выходом второго дополнительного логического элемента И, а второй вход - со входами установки нуля дополнительного триггера, первого блока памяти, первого счетчика, первого и второго триггеров, а также с выходом генератора одиночного импульса и входом ждущего мультивибратора, выход которого подключен ко второму входу первого логического элемента И,. На фиг, 1 приведена принципиальная электрическая схема анализатора периодической последовательности сигналов , на фиг, 2 - временные диаграммы, поясняющие принцип работы устройства. Анализатор периодической последова- тельности сигналов содержит ключи 1 и 2, входы которых соединены со входом устройства, первый и второй логические элементы И 3 и 4, первые входы которых соединены с источ шком тактовых импульсов. Выход первого логического элемента И 3 подключен к счетному входу первого триггера 5, прямой выход которого соединен со счетным входом второго триггера 6 и со входом третьего логического элемента И 7, а инверсный выход подключен ко второму входу логического элемента И 4, выход которого подключен к первь входам первого и второго .логических элементов И 8 к 9 , Вто.рой вход первого дополнительного ло58гического элемента И 8 соединен с ВЫХОДОМ блока 10 сравнения и через инвертор 1 - со вторым входом второго дополнительного логического элв мента И 9, а выход подключен ко вход установки единицы триггера 12, прямой выход которого является выходом устройства, а инверсный выход соединен с первым входам четвертого логического элемента И 13, второй вход которого подключен к прямому выходу второго триггера 6, а третий вход соединен со вторым входом третьего логического элемента И 7 и с выходом опорного генератора 14, Выходы трет го и четвертого логических элементов И 7 и 13 подключены соответстве но к управляющим входам ключей I и 2 и к счетным входам первого и втор го счетчиков 15 и 16. Выходы ключей 1 и 2 через аналого-цифровые преобразователи 7 и 18 соединены соот ветственно с информационньми входами первого и второго блоков 9 и 20 памяти, управляющие входы которых по ключены соответственно к выходам сче чиков 15 и 16, а выходы соединены с первыми и вторыми входами блока 10 срао нения. Входы установки нуля блока 20 памяти и счетчика 16 подключены к выходу логического элемента ИЛИ 21, первый вход которого соединен с выходом второго дополнительного логического элемента И 9, а второй вход подключен к входам установки нуля дополнительного триггера 12, блока 19 памяти, счетчика 15, триггеров 5 и 6, а также ко входу ждущего мультивибратора 22, выход которого подключен ко второму входу первого логического элемента И 3, и выходу генератора 23 одиночного импульса. Анализатор периодической последовательности сигналов работаетследующим образом. Анализируемая последовательность сигналов, например, прямоугольные импульсы (см, фиг, 2а), поступает на входы ключей 1 и 2, На первые вхо ды элементов И 3 и 4 поступают короткие импульсы (см, фиг, 26) от источника тактовых импульсов, которые являются синфазными со входной аналй зируемой последовательностью, а их частоты связаны соотношением f«4 N fгде f - частота входной последовательмости;f-(y частота тактовых импульсов, Н - целое число 1,2,3,4,,, В момент запуска генератора 23 одиночного импульса формируется короткий импульс (см. фиг, 2в}, устанавливающий в нулевое положение триггеры 5, 6, 2f счетчик 5, блок 19 памяти, а также, провдя через элемент РШИ 21, обнуляющий счетчик 16 и блок 20 памяти. Кроме того, импульс с выхода генератора 23 одиночного импульса поступает на ждущий мультивибратор 22, с вь1хода которого снимается импульс (см, фиг, 2г) длительностью2х 2Т -N, такт БХ где период входной последовательности;TTQ. период тактовых импульсов. Импульс с выхода ждущего мультивибратора 22 поступает на элемент И 3, разрешая прохождение тактовым импульсам на счетный вход триггера 5, Согласно выбранной длительност1и импульса с выхода жд тцего мультивибратора 22 на триггер 5 поступают- толь ко дра тактовых импзшьса, (см,фиг, 2д), Первый импульс переводит триггер 5 в единичное состояние (см. фиг, 2е), Высокий уровень напряжения с прямого выхода триггера 5 поступает на элемент И 7, разоешая прохождение :импульсам с ; ькода опорного генератора 14 через элемент И 7 на управ- ляюидай вход ключа 1 и на счетный вход счетчика 15, Частота импульсов с опорного генератора 14 выбирается много больше частоты анализируемой последовательности. Первый импульс с выхода опорного генератора 14 открывает ключ 1 и мгновенное значение амплитудь входной последовательности, преобразованное из аналоговой величины в цифровую аналого-цифрр-. вым преобразователем 17, поступаетна информац;ионный вход блока 19 памяти. Одновременно нмпульс с опорного генератора 14 поступает на счетный вход счетчика 15, С выходов счетчика снимается двоичное число, соответств тощее числу поступивших на счетчик импульсов, В данном случае единица. Двоичное число с выходов счетчика 15 поступает на управля- ющие входы: блока 1 9 памяти и мгновев 78ное значение амплитуды входной анализируемой последовательности записьюается в первую ячейку блока 19 па мяти. Второй импульс с опорного генератора 14 поступает на счетчик 5 и открывает ключ 1 . Мгновенное; значе ние входной анализируемой последовательности преобразуется в,цифровую величину аналого-цифровым преобразов телем 17 и записывается во вторую .ячейку блока-19 памяти согласно двоичному числу, поступающему на управляющие входы с выходов счетчика 15. Таким образом, осуществляется после довательная дискретизация, преобразов ние и запись в блок 1.9 памяти N пери одов входной анализируемой последова тельности. С приходом второго тактового импульса (см. фиг. 2д) на триг гер 5, триггер переходит в исходное состояние. Низким уровнем напряжения с прямого выхода триггера 5 (см фиг. 2е) запрещается прохождение им пульсов с опорного генератора 14 на выход элемента И 7. За интервал времени между двумя тактовыми импульсами tcM, фиг. 2д) в блок 19 памяти производится дискретная запись формы N периодов входной последовательности. При переходе триггера 5 из. единичного состояния в нулевое, триггер 6 переходит из нулевого состояния в единичное (см. фиг. 2ж). Высоким уровнем напряжения, поступающим с прямого выхода триггера б на вход элемента И 13, разрешается проход импульсам с опорного генератора 14 через элемент И 13 на -управляющий вход ключа 2 к на счетный вх счетчика 16. Аналогично с произведенной дискретизацией, преобразованием и записью предыдущих N периодов входной последовательности в блок 19 памяти осуществляется запись последу1ощих периодов в блок 20 памяти. Информация, записанная в блоке 20 памяти, сравнивается с информацией, записанной в блоке 19 памяти блоком 10 сравнения. Если за время анализа последующих N периодов не произошло обоев во входной последовательности, т.е. информация в блоке 2Q ьамяти совпадает п информацией в блоке 19 памяти, то на выходе блока 10 сравнения устанавливается низ кий уровень напряжения, поступающий на вход элемента И 8 и через инвертор 1 - на вход элемента И 9. Третий тактовьй импульс, пройдя через элемент И 4, на втором входе которого установлен разрешающий высокий уровень напрялсения от инверсного выхода триггера 5, поступает на элементы И 8 и 9. На выходе элемента И 8 устанавливается высокий уровень напряжения, а на выходе элемента И 9 устанй.вливается низкий уровень напрялсения, которьш пройдя через элемент ИЖ 21 счетчик 16 и блок 20 памяти. На входах элемента И 13 сохраняются разрешающие уровни напряжения и импульсы с опорного генератора 14 поступают на ключ 2 и счетчик 16. Происходит дискретизация, преобразование и запись последующ - х N периодов входной последовательности в блок 20 памяти и сравнение информации, записанной в блоке 20 памяти, с ранее записанной информацией в блоке 19 памяти. При возникновении искажений в анализируемой входной последовательности, форма сигнала, записанная в блок 20 памяти, не соответствует ранее записанной форме сигнала в блоке 19 памяти, В этом случае на выходе блока 10 сравнетшя устанавливается высокий уровень напряжения. При поступлении очередного импульса через элемент И 4 на вход элементов И 8 и И 9, на выходе элемента И 9 устанавливается высокий уровень напряжения, а на выходе элемента И 8 - низкий. Низким уровнем переводится в единичное состояние триггер 12, с инверсного выхода которого снимается низкш уровень напряжения, поступающий на вход эле.мента И 13 и запрещающий прохождение импульсам с опорного генератора 14 на вход элемента И 13, Высокий уровень напряжения с прямого выхода триггера 12., поступающий на выход устройства, является сигналом того, что во входной анализируемой последовательности появились искажения. Таким обра.зом, в блоке памяти 19 сохраняется информация о истинной форме сигнала, а в блоке 20 памяти сохраняется информация о искажениях, появляющихся во входном сигнале. При генерации очередного импульса от генератора 23 блоки 19 и 20 памяти обнуляются, и начинается новый процесс анализа входной последователь нести до появления сбоев, которые будут записаны в блок 20 памяти. Наиболее эффективно использовани предлагаемого анализатора при появл нии редких сбоев, например, один раз в iO-15 мин. когда обнаружить Сбои известными методами, например осциллографическим, невозможно. Кро ме того, предлагаемый анализатор позволяет не .только обнаружить, но и запомнить искажения в сигнале, вызванные сбоем. Б дальнейшем записанную информацию можно извлечь из памяти и наблюдать, какие именно искажения произошли в сигнале. Знание вида искажений позволяет своевременно и точно обнаружить место появления сбоев и устранить причину возникновения искажений. Формула изобретения Анализатор периодической последовательности сигналов, содержащий первый и второй счетчики, первьй триггер, выход которого соединен со входом второго триггера, первый логический элемент И, первый вход которого соединен с шиной тактовых импульсов, второй и третий логические элементы И, четвертый логический элемент И, выход которого соеди нен с входом второго счетчика, инвертор, логический элемент ИЛИ, отличающийся тем , что, с целью расширения функциональных возможностей устройства, в него вве дены дополнительные логические элементы И, дополнительный триггер, жд щий мультивибратор, генератор одиночного импульса, опорный генератор импульсов, аналого-цифровые преобра зователи, блоки памяти, блок сравнения и ключи, входы которых соединены со входом устройства, первый вход второго логического элемента И соединен с шиной тактовых импульсов выход первого логического элемента И подключен к счетному входу первог триггера, прямой выход которого соед нен со входом третьего логического элемента И, а инверсный выход подключен ко второму входу второго догического элемента И, выход которого подключен к первым входам двух дополнительных логических элементов И,, второй вход первого дополнительного логического элемента И соединен с выходом блока сравнения, и через инвертор - со вторым входом второго дополнительного логического элемента И, а выход подключен ко входу установки единицы дополнительного триггера, прямой выход которого является выходом устройства, а инверсный вьгход соединен с первым входом четвертого логического элемента И, второй вход которого подключен к прямому выходу второго, триггера, а третий вход ко второму входу третьего логического элемента И и к выходу опорного генератора импульсов, выходы третьего и четвертого логических элементов И подключены соответственно к управляющим входам первого и второго ключей, выход третьего логического элемента И соединен с входом первого счетчика, а выходы первого и второго ключей через аналого-цифровые преобразователи соединены соответственно с информационными входами первого и второго блоков памяти, управляющие входы которых подключены соответственно к выходам первого и второго счетчиков , а выходы соединены с первой и второй группами входов блока сравнения, причем входы установки нуля второго блока памяти и второго счетчика подключены к выходу логического элемента ИЛИ, первый вход которого сое.сщнен с выходом второго дополнительного логического элемента И, а второй вход - со входами установки нуля дополнительного триггера, первого блока памяти, первого счетчика, первого и второго триггеров, а также с выходом генератора одиноч ного импульса и входом ждущего мультивибратора, выход которого подключенко второму вхсду первого логического элемента И. Источники информации, принятые во внимание при экспертизе1.Авторское свидетельство СССР № 472447, кл. Н 03 К 5/20, 1974. 2.Авторское свидетельство СССР К 544121, кл. Н 03 К 5/20, 1975 (прототип).

цт. ,.

s

HrJ

VJUL...JUI...JLJI...JU1

VrL

У

У /.

1L

/

K.

Фиг.2

Авторы

Даты

1981-08-15—Публикация

1979-11-19—Подача