преобразователь 3, усилитель 4, пер- вый. регистр 5, аналого-цифровой преобразователь 6, блок 7 выборки максимума 5 дешифратор 8, мультиплексор 9 второй регистр 10, цифровой сумматор 11J первый и второй запоминающие бло ки 12 и 14 вьтолненпые в виде ОЗУ) адресный счетчик 13, буферный накопитель 15s узел 16 блокировки тактового генератора, тактовый генератор 17, блок 18 управления, первый, второй и третий входы 19, 20 и 24 считывания, вход 21 для разрешения запуска блока 18 управления 5 вход 22 для запуска блока 18 управления, вход 23 для синхропнзап.ии блока 18 управлеУстройство относится к измерительной технике и может быть использовано для регистрации информации в искровой и лазерной масс-спектрометрии с целью исследования состава твердых тел о

Целью изобретения является уменьшение погрешности измерения средних значений случайных величин с различными динамическими диапазонами изме- рения,

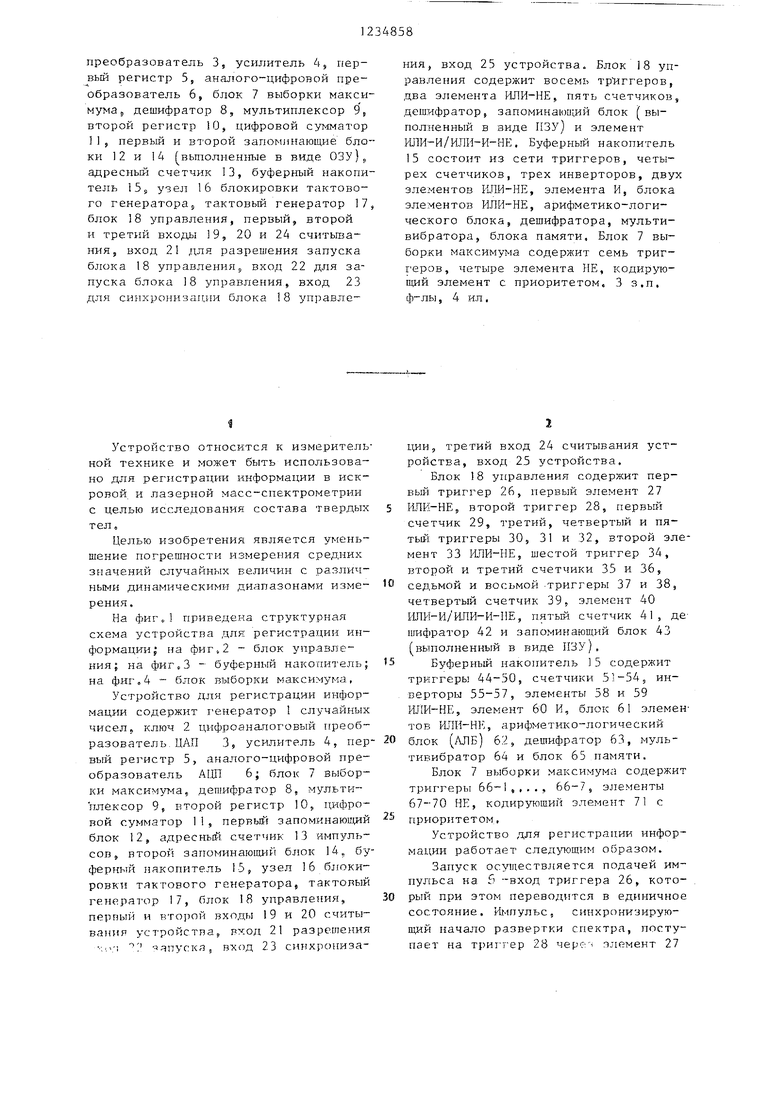

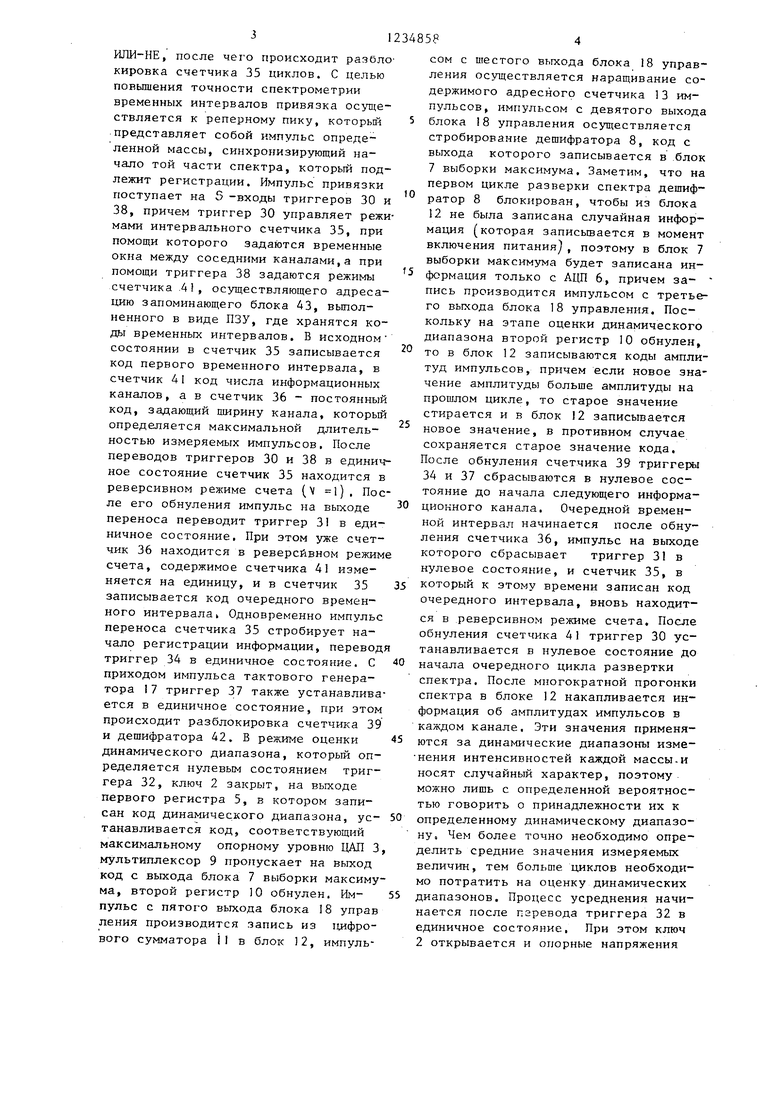

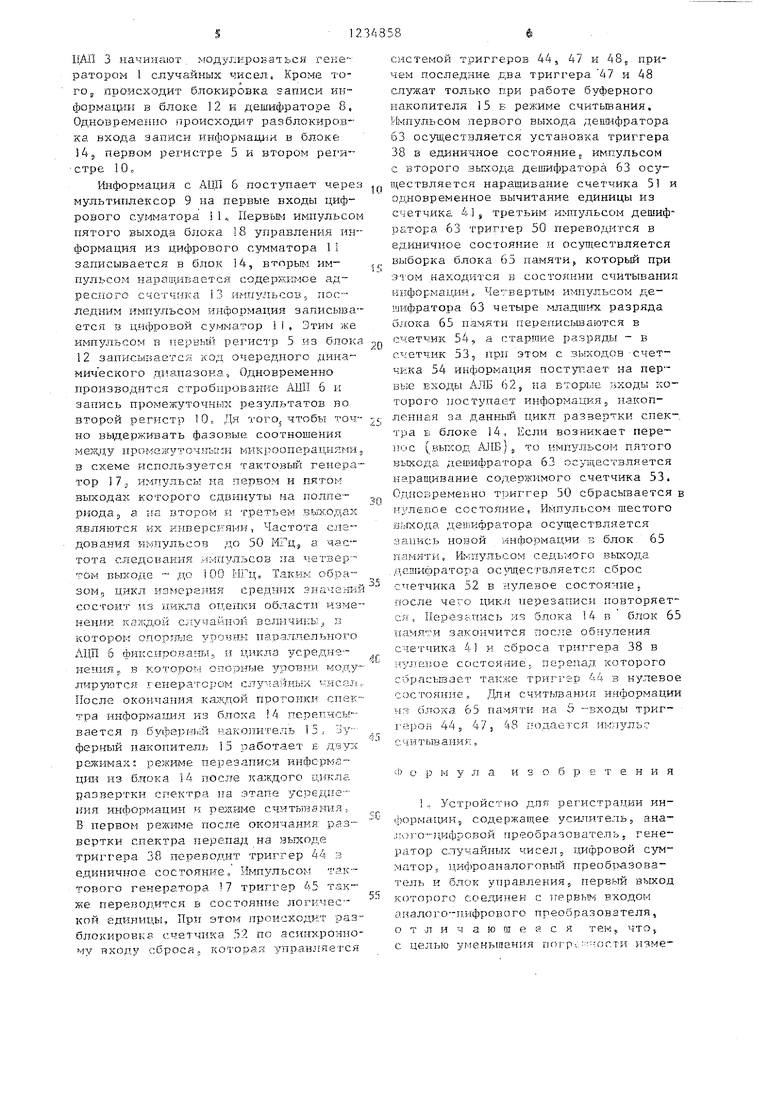

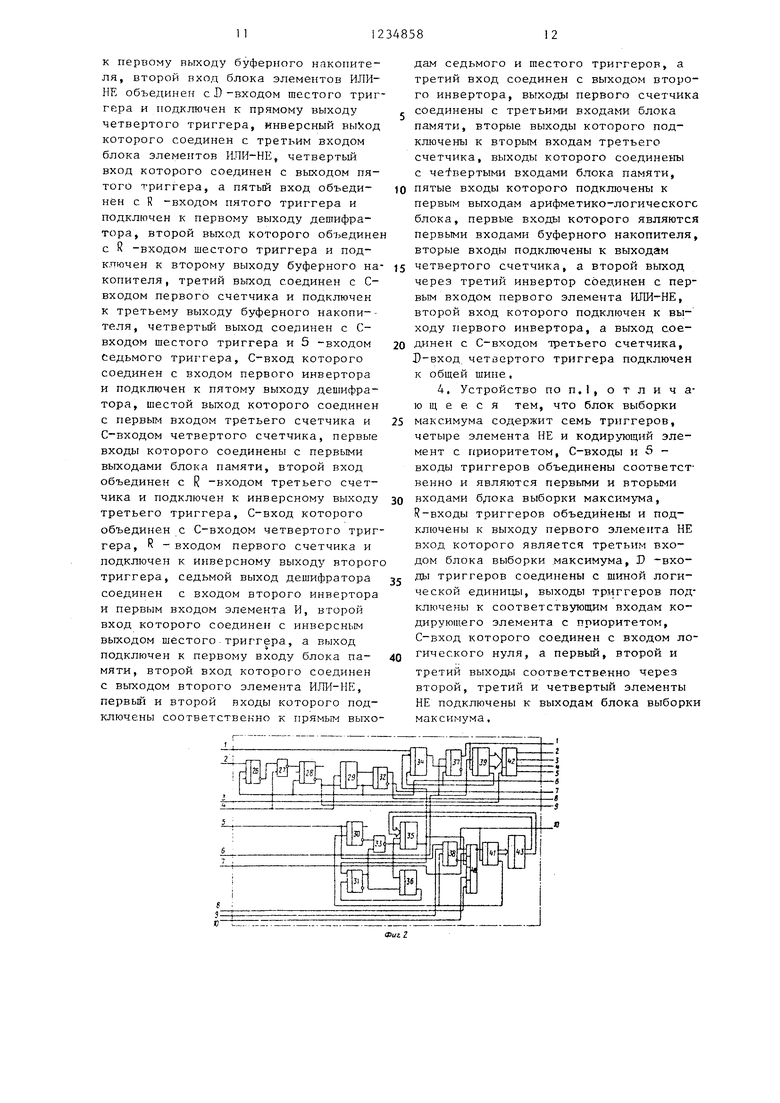

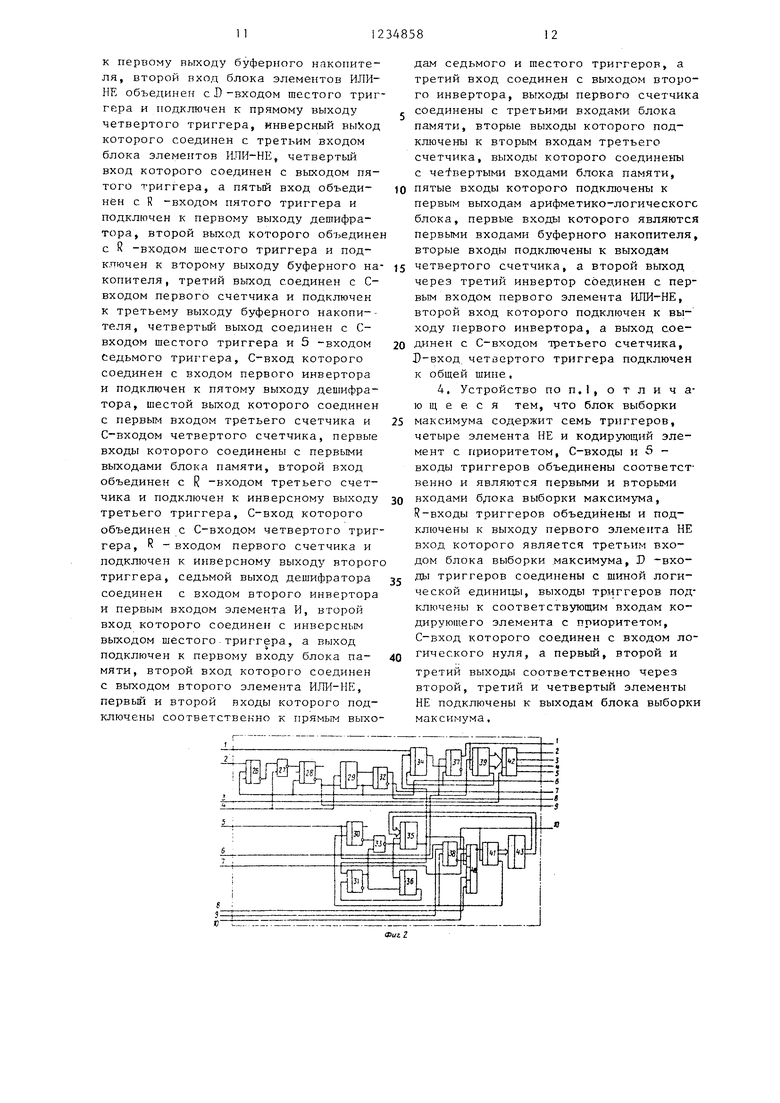

На фиг„1 приведена структурная схема устройства для регистрации информации; на фиг.2 - блок управления; на фиг.З - буферный накопитель; на фиг о 4 - блок выборки максимума,

Устройство для регистрации информации содержит генератор 1 случайных чисел, ключ 2 цифроаналоговый яреоб- разователь,ЦАП 3, усилитель 4, пер- вый регистр 5, аналого-цифровой преобразователь АЦП 6; блок 7 выборки максимума, дешифратор 8, мультиплексор 9, второй регистр 10, цифровой сумматор 115 первый запоминающий блок 12, адресный счетчик 13 импульсов j второй запоминаю щ-Н1 блок 14., буферный накопитель 15, узел 16 блокировки тактового генератора, тактовый генератор 17, блок 18 управления, первый и второй вход, 19 и 20 считывания устройства, вход 21 разрешения ; чапускя, вход 23 синхронизания, вход 25 устройства. Блок 18 управления содержит восемь тр иггеров, два элемента ИЛИ-НЕ, пять счетчиков, дешифратор, запоминаюищй блок (выполненный в виде ПЗУ) и элемент Шта-И/ИЛИ-И-НЕ. Буферный накопитель 15 состоит из сети триггеров, четырех счетчиков, трех инверторов, двух элементов , элемента И, блока элементов ИЛИ-НЕ, арифметико-логического блока, дешифратора, мультивибратора, блока памяти. Блок 7 выборки максимума содержит семь триггеров, четыре элемента НЕ, кодирующий элемент с приоритетом. 3 з.п, ф-лы, 4 ил,

ции, третий вход 24 считывания устройства, вход 25 устройства.

Блок 18 управления содержит первый триггер 26, первый элемент 27 ИПИ-НЕ, второй триггер 28, первый счетчик 29, третий, четвертый и пятый: триггеры 30, 31 и 32, второй элемент 33 ИЛИ-ЦЕ, шестой триггер 34, второй и третий счетчики 35 и 36, седьмой и восьмой триггеры 37 и 38, четвертый счетчик 39. элемент 40 ИЛИ-И/И.ПИ-И-ПЕ, пятый счетчик 41, ДВ шифратор 42 и запоминающий блок 43 (выполненный в виде ПЗУ).

Буферный накопитель 15 содержит триггеры 44-50, счетчики 51-54, инверторы 55-57, элементы 58 и 59 ИЛИ-НЕ, элемент 60 И, блок 61 элементов ИЛН-НЕ, арифметико-логический блок (АЛБ) 62, дешифратор 63, мультивибратор 64 и блок 65 памяти.

Блок 7 выборки максимума содержит триггеры 66-1,,.., 66-7, элементы 67-70 НЕ, кодирующий элемент 71 с приоритетом.

Устройство для регистрании информации работает след пощим образом.

Запуск осу цествляется подачей импульса на 5 -вход триггера 26, который при этом переводится в единичное состояние, И1-1пульс, синхронизирующий начало развертки спектра, поступает на тригтер 28 чере элемент 27

ИЛИ-НЕ, после чег о происходит разбло кировка счетчика 35 циклов. С целью повышения точности спектрометрии временных интервалов привязка осуществляется к реперному пику, который представляет собой импульс определенной массы, синхронизирующий начало той части спектра, который подлежит регистрации. Импульс привязки поступает на 5 -входы триггеров 30 и 38, причем триггер 30 управляет режимами интервального счетчика 35, при помощи которого заданзтся временные окна между соседними каналами,а при помощи триггера 38 задаются режимы счетчика ,4, осуществляющего адресацию запоминающего блока 43, выполненного в виде ПЗУ, где хранятся коды временных интервалов. В исходном состоянии в счетчик 35 записывается код первого временного интервала, в счетчик 41 код числа информационных каналов, а в счетчик 36 - постоянный код, задающий ширину канала, который определяется максимальной длительностью измеряемых импульсов. После переводов триггеров 30 и 38 в единичное состояние счетчик 35 находится в реверсивном режиме счета (V 1), После его обнуления импульс на выходе переноса переводит триггер 31 в единичное состояние, При этом уже счетчик 36 находится в реверсивном режиме счета, содержимое счетчика 41 изме

няется на единицу, и в счетчик 35 записывается код очередного временного интервала Одновременно импульс переноса счетчика 35 стробирует начало регистрации информации, переводя триггер 34 в единичное состояние. С приходом импульса тактового генератора 17 триггер 37 также устанавливается в единичное состояние, при этом происходит разблокировка счетчика 39 и дешифратора 42. В режиме оценки динамического диапазона, который определяется нулевым состоянием триггера 32, ключ 2 закрыт, на выходе первого регистра 5, в котором записан код динамического диапазона, устанавливается код, соответствующий максимальному опорному уровню ЦАП 3, мультиплексор 9 пропускает на выход код с выхода блока 7 выборки максимума, второй регистр 10 обнулен. Им- пульс с пятого выхода блока 18 управ ления производится запись из вого сумматора М в блок 12, импуль

10

20

25

35

45

о 55

348584

сом с шестого выхода блока 18 управления осуществляется наращивание содержимого адресного счетчика 13 импульсов, импульсом с девятого выхода блока 18 управления осуществляется стробирование дешифратора 8, код с выхода которого записывается в блок 7 выборки максимума. Заметим, что на первом цикле разверки спектра дешифратор 8 блокирован, чтобы из блока 12 не была записана случайная информация (которая записьтается в момент включения питания, поэтому в блок 7 выборки максимума будет записана ин- 5 формация только с АЦП 6, причем за- пись производится импульсом с третьего выхода блока 18 управления. Поскольку на этапе оценки динамического диапазона второй регистр 10 обнулен, то в блок 12 записываются коды амплитуд импульсов, причем если новое значение амплитуды больше амплитуды на прошлом цикле, то старое значение стирается и в блок 12 записывается новое значение, в противном случае сохраняется старое значение кода. После обнуления счетчика 39 тригге 34 и 37 сбрасываются в нулевое состояние до начала следующего информационного канала. Очередной временной интервал начинается после обнуления счетчика 36, импульс на выходе которого сбрасывает триггер 31 в нулевое состояние, и счетчик 35, в который к этому времени записан код очередного интервала, вновь находится в реверсивном режиме счета. После обнуления счетчика 41 триггер 30 устанавливается в нулевое состояние до начала очередного цикла развертки спектра. После многократной прогонки спектра в блоке 12 накапливается информация об амплитудах импульсов в каждом канале. Эти значения применяются за динамические диапазоны изме- нения интенсивностей каждой массы.и носят случайный характер, поэтому можно лишь с определенной вероятностью говорить о принадлежности их к определенному динамическому диапазону. Чем более точно необходимо определить средние значения измеряемых величин, тем больше циклов необходимо потратить на оценку динамических диапазонов. Процесс усреднения начинается после перевода триггера 32 в единичное состояние. При этом ключ 2 открывается и опорные напряжения

30

50

lifiH 3 начинают модулнроваться генератором 1 случайных чисел. Кроме того,, происходит блокировка записи ин- формахщи в блоке 12 к дешифраторе 8, Одновременно происходит разблокировка входа эаписи кнфорьтщ и в блоке 14з первом регистре 5 и втором рег и- стре 101

Информация с АЦП 6 поступает через мультиплексор 9 на первые входы цифрового сумматора 11„ Первым импульсом пятого выхода блока 18 управления информация из цифрового сумматора 1 ; записывается в блок 14, вторым им- пульсом наращивается содержимое адресного счетчика 13 импульсов, ледним импульсом информация записывается в цифровой сумматор i I, Этим же импульсом в первый рег истр 5 из блока 12 записывается код очередного дина- мич еекого диапазона. Одновременно производится стробнрование AUII 6 и запись промежуточных результатов во второй регистр 10, Дя того чтобы точ- но выдерживать фазовые соотношения промежуточяыг:и г.5Икроопера:циями в схеме используется тактовый генератор J7j импульсы на первом и пятом выходах которого сдвинуты на полпе- риода 5 а на втором :я третьем выходах являются их иршерскяни. Частота следования импульсов до 50 МГц, а частота следования импульсов на четвертом вьпсоде - до 100 МГц, Таким обрасостоит из цтикла оцеггки области изменения каждой случайной вeличш5:ь:;J Б котором опортгтле уровни параллельного ЛИД 6 фиксирова-ш,. и цикла усредне- нения J в которогл опорные уровни модулируются генератором соту-шйньзх чисел После око1 :чания каждой прогонки спектра информапия из блока 4 перепись -- вается в буферный накопитель 15 Зу- ферный накопителт; 15 работает Б двух режимах: режиме перезаписи информации из блока 14 после каждого дитсла развертки спектра на этапе усреднения информации и режиме сч г тьтзния, В первом режиме после окончания, развертки перепад на зьшоде трип ера 38 переводит триггер 44 з единичное состояние, Имп л:ьсо:-- тактового генератора 17 триггер 45 также переводится в состояние логической , При этом проиеходкт разблокировка счетчика 52 по асинхронному входу сброса.; которая управляется

. ,. «Q .и- -,

,,. .

й

системой триггеров 44, 4/ и 48 причем последние два триггера 47 и 48 слзгокат только при работе буферного накопителя 15 Б режиме считьшания. Импульсом первого выхода депшфратора 63 осуществляется установка триггера 38 в еди:ничное состояние,, импульсом с второго выхода дешифратора 63 осуществляется наращивание счетчика 51 и одновременное вычитание единицы из счетчика 41, третьим импульсом дешифратора 63 триг.гер 50 переводится в единичное состояние и осугг ествляется выборка блока 65 памяти, который при э гом находится в состоянии считывания информации. Четвертым импульсом дешифратора 63 четыре младших разряда блока 65 памяти переписЕзшаются в счетчик 54, а старшие разряды - в счетчик 53, при этом с выходов счетчика 54 информация поступает на пер- вь;е входы АЛБ 62, на вторые входь: которого поступает информация н.акоп- ленная за данный цикл развертки спек-. тра в блоке 14, Если возникает пере- li jc (выход /UIE) 5 то импульсом пятого выхода дешифратора 63 осутцествл/чется наращивание содержимого счетчика 53. Однов-ременно триггер 50 сбрасывается в нулевое состояние. Импульсом EtecToro в: 1хода дешифратора осуществляется :; аг1ись новой информации в блок 65 памят -. Импульсом седьмого выхода дешифратора ос пцествляется сброс счетчика 52 в -чулевое состояние, люсле чего цик.п перезаписи повторяется. Перезапись из блока 14 в блок 65 памяти закончится nocjie обну.пения счетчика 41 и. сброса триггера 38 в 1-гулевое состояние, перепад, которого сбрасывает также триггер 44 в нулевое состоя.ние. Дик считывания информации ИЗ блока 65 памяти на 5 -входь триг- repo.ti 44, 47, 48 г-одается имлульс считывания,

; о {5 м у л а и з о б р е т е н и я

1„ Устройство для регистрации ин- фop aции5 содержащее усилитель, ана ,|; ,)г о--цифровой преобразователь5 генератор случайных чисел, цифровой сумматор, цифроаналогопый преоб|.азова- тель и блок управленияS первый выход которого соединен с ттервьм входом аналого-п.ифрового преобразователя, о т -л и ч а 10 ш е е с я TeMj что с целью уменьшения пг:ч-р; : :чости изме

рения средних значений случайш гх величин, в него введены ключ, первьш и второй регистры, блок выборки максимума, мультиплексор, адресный счетчик иьшульсов, первый и второй запоминаю- щие блоки, буферный накопитель, узел блокировки тактового генератора, тактовый генератор и дешифратор, выход генератора случайных чисел соединен с первым входом ключа, второй вход которого объединен с первьм входом дешифратора, первым входом мультиплексора, первым входом второго запоминающего блока, первьм входом буферного накопителя и подключен к второму выходу блока управления, выход ключа соединен с первым входом цифро- аналогового преобразователя, вторые входы которого соединены с выходами лервого регистра, первый и второй выходы цифроаналогового преобразователя соединены соответственно с первым и вторым входами аналого-цифрового преобразователя, третий вход которо- го подключен к выходу усилителя, вход которого является входом устройства, четвертый вход аналого-цифрового преобразователя объединен с первым входом первого регистра, первым входом второго регистра, первым входом первого запоминающего блока и подключен к первому выходу блока управления, пятый вход аналого-цифрового преобразователя соединен с первым выходом тактового генератора, первые выходы аналого-цифрового преобразователя соединены с первыми входами блока выборки максимума, а вторые выходы подключены к вторым входам мультиплексора, третьи входы которого сое- диненъ с выходами блока выборки максимума, выходы мультиплексора подключены к первым входам цифрового сумматора, вторые входы которого соединены с выходами второго регистра, а третий вход объединен с вторым входом первого регистра и подключен к третьему выходу блока управления, первые выходы цифрового сумматора подключены к вторым входам первого и второго запоминающих блоков, а вторые выходы - к вторым входам второго регистра, третий вход второго запоминающего блока объединен с вторым входом буферного накопителя, вторым вхо дом дешифратора и подключен к четвертому выходу блока управления, четвертый вход второго запоминающего бло

0

5

0

5

5

5

0

ка объединен с третьим входом первого запоминающего, блока и подключен к пятому выходу блока управления, пятые входы второго запоминающего блока объединены с четвертыми входами первого запоминающего блока и подключены к выходам адресного счетчика им- пулъсоБ, выходы второго запоминающего блока подключены к третьим входам первого регистра и дешифратора, выходы которого соединены с вторыми входами блока выборки максимума, первый вход адресного счетчика импульсов соединен с шестым выходом блока управления, второй вход - с вторьм выходом тактового генератора, а третий вход объединен с третьим входом буферного накопителя, входом узла блокировки тактового генератора, третьим входом дешифратора и подключен к седьмому выходу блока управления, выход узла блокировки тактового генератора соединен с входом тактового генератора, выходы первого запоминающего блока подключены к четвертым входам буферного накопителя, первый выход которого соединен с четвертым входом первого запоминающего блока, а второй и третий выходы соединены соответственно с первым и вторым входами блока управления, восьмой выход которого подключен к третьим входам блока выборки максимума и второго регистра, а девятый и десятый выходы - соответственно к четвертому и пятому входам дешифратора, третий и четвертый входы блока управления подключены соответственно к третьему и четвертому выходам тактового генератора, пятый выход которого соединен с четвертым входом второго регистра и с пятым входом блока управления, пятый вход буферного накопителя является первым входом считывания.устройства, шестой вход блока управления является вторым входом считывания устройства, седьмой вход блока управления является входом разрешения, восьмой вход является входом запуска, девятый вход - входом синхронизации, а десятый вход - третьим входом считьшания устройства,

2, Устройство по п.1, о т л и ч а- ю щ е е с я тем, что блок управления содержит первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой триггеры, первый и второй элементы ИЛИ-НЕ, первый, второй.

третий, четвертый и пятый счетчики, дешифратор, запоминающий блок и элементы ИЛИ-И/ИЛИ-И-НЕ, 5 -вход первого триггера подключен к седьмому входу блока управления, а инверсный выход соединен с первым входом первого элемента ИЛИ-НЕ, второй вход которого объединен с С-входом первого счетчика и подключен к восьмому входу блока управления, а выход соединен с С-входом второго триггера, инверсный выход которого объединен с R -входом первого счетчика и подключен к четвертому выходу блока управления, первый выход первого счетчика об единен с С-входом первого триггера, R -входами второго и пятого триггеров и подключен к десятому выходу блока управления, второй выход первого счетчика соединен с 5 -входом пятого триггера, пряъюй и инверсный выходы которого соединены соответственно с вторым и первым выходами блока управления, первый 5 -вход шестого триггера i подключен к шестому входу блока управления, а второй 5 -вход объединен с S-входом четвертого триггера, первым входом элемента ИЛИ-И/ИЛИ-И-НЕ и подключен к выходу второго счетчика, первые входы которого соединены с выходами запоминающего блока, Y -вход подключен к инверсному выходу второго элемента ИЛИ-НЕ, а С-вход объединен с С-входом третьего счетчика, вторым входом элемента ИЛИ-И/ИЛ1Т-И-НЕ и подключен к четвертому входу блока управления, первь Й вход второго элемента ИЛИ-НЕ соединен с инверсным выходом третьего триггера, 5 -вход которого объединен с 5 -входом восьмого триггера и подключен к девятому входу блока управления, С-вход третьего триггера объединен с D -входом восьмого триггера и подключен к выходу переполнения пятого счетчика, выходы которого соединены с входами запоминающего блока, а С-вход подключен к инвepcнo ry выходу элемента ЙЛИ-И/ИЛИ-И-НЕ, третий вход которого объединен с Y -входом пятого счетчика, соединен с прямым выходом восьмого триггера и подключен к седьмому выходу блока управления, С-вход вось мого триггера сЬединен с первым входом блока управления, а инверсный выход подключен к четвертому входу элемента ИЛИ-И/ИЛИ-И-НЕ, пятый и шестой входы которого соединены соответ

ственно с вторым и десятьп входами блока управления, второй вход второго элемента ИЛИ-НЕ объединен с Y - входом третьего счетчика и подключен к выходу четвертого триггера, С- вход которого соединен с выходом- тре. счетчика, пятый вход блока управления соединен с С-входами седьмого триггера и четвертого счетчика, вьшоды которого подключены к входам дешифратора, С-вход которого соединен с третьим входом блока управления, а первый, второй, третий и чет- вертьш выхода подключены соответственно к пятому, шестомур девятому и треть€ .му выходам блока управления, R-входы шестого и седьмого триггеров объединены и подклЕочены к выходу переполнения четвертого счетчика,, V вход которого соединен с выходом седьмого триггера и подключен к восьмому выходу блока управления, выход шестого триггера соединен с Т) -входом седьмого триггера,

3. Устройство по п.1, о т л и ч а ю ш; е е с я тем что буферный накопитель содержит первый, второй, тре- тий,, четвертый, пятый, шестой и седьмой триггеры,, первый, второй, третий и четвертый счетчики, первый, второй и третий инверторы, первьй и второй элементы ИЛИ-НЕ, блок элементов ИЛИ-НЕ, элемент И, арифметико-логи- чйский блок, дешифратор, мультивибратор и блок памяти, S -вход первого триггера по,цклточен к инверсному вы- хо,цу этого триггера, а С-вход и первьй R -вход подключены соответственно к второму и третьему входам буферного накопителя, 5 -входы первого, четвертого и пятого триггеров объе- ,цинены и подключены к пятому входу буферного накопителя, второй R -вход первого триггера объединен с R -входом третьего триггера и подключен к четвертому входу буферного накопи- . теля, прямой выход первого триггера соединен с Э -входом второго триггера, С-вход которого ггодключен к инверсному выходу мул,. гиБибратора, прямой ,г; которого соединен с С-входом второго счетчика и первым входом дешифратора, вторые входы которого подключены к выходам второго счетчика, R -вход которого соединен с выходом блока элементов ИЛИ-НЕ, первый вход которого соединен с прямым выходом второго триггера и по,цключен

к первому выходу буферного накопителя, второй вход блока элементов ИЛИ- НЕ объединен сD-входом гаестого триггера и подк;дачен к прямому выходу четвертого триггера, инверсный выход которого соединен с третьим входом блока элементов ИЛИ-НЕ, четвертый вход которого соединен с выходом пятого триггера, а пятый вход объеди- нен с R -входом пятого триггера и подключен к первому выходу дешифратора, второй выход которого объедине с R -входом шестого триггера и подключен к второму выходу буферного на копителя, третий выход соединен с С- входом первого счетчика и подключен к третьему выходу буферного накопи-- теля, четвертый выход соединен с С- входом шестого триггера и 5 -входом седьмого триггера, С-вход которого соединен с входом первого инвертора и подключен к пятому выходу дешифратора, шестой выход которого соединен с первым входом третьего счетчика и С-входом четвертого счетчика, первые входы которого соединены с первыми выходами блока памяти, второй вход объединен с R -входом третьего счетчика и подключен к инверсному выходу третьего триггера, С-вход которого объединен с С-входом четвертого триггера, R -входом первого счетчика и подключен к инверсному выходу второг триггера, седьмой выход дешифратора соединен с входом второго инвертора и первым входом элемента И, второй вход которого соединен с инверсным выходом шестого.триггера, а выход подключен к первому входу блока па- мяти, второй вход которого соединен с выходом второго элемента ИЛИ-НЕ, первый и второй входы которого подключены соответственно к прямым выходам седьмого и шестого триггеров, а третий вход соединен с выходом второго инвертора, выходы первого счетчика соединены с третьими входами блока памяти, вторые выходы которого подключены к вторым входам третьего счетчика, выходы которого соединены с четвертыми входами блока памяти, пятые входы которого подключены к первым выходам арифметико-логического блока, первые входы которого являются первыми входами буферного накопителя, вторые входы подключены к выходам четвертого счетчика, а второй выход через третий инвертор соединен с первым входом первого элемента ЮШ-НЕ, второй вход которого подключен к выходу первого инвертора, а выход сое- с С-входом третьего счетчика, D-ВХОД четвертого триггера подключен к общей шине,

4, Устройство по п,1, о т л и ч а- ю щ е е с я тем, что блок выборки максимума содержит семь триггеров, четыре элемента НЕ и кодирующий элемент с приоритетом, С-входы и 5 - входы триггеров объединены соответственно и являются первыми и вторыми входами бдока выборки максимума, R-входы триггеров объединены и подключены к выходу первого элемента НЕ вход которого является третьим входом блока выборки максимума, D -входы триггеров соединены с шиной логической единицы, выходы триггеров подключены к соответствующим входам кодирующего элемента с приоритетом, С-вход которого соединен с входом логического нуля, а первый, второй и

третий выходы соответственно через второй, третий и четвертый элементы НЕ подключены к выходам блока выборки максимума,

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

| РЕГИСТРАТОР ПАРАМЕТРОВ АВАРИЙНЫХ СИТУАЦИЙ В ЭЛЕКТРИЧЕСКИХ СЕТЯХ ПОВЫШЕННОЙ ТОЧНОСТИ (ВАРИАНТЫ) | 2008 |

|

RU2376625C1 |

| Многоканальное устройство для регистрации аналоговых и цифровых сигналов | 1988 |

|

SU1564649A1 |

| Устройство для ввода информации | 1983 |

|

SU1145336A1 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ СИГНАЛОВ С ПРОГРАММНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 1997 |

|

RU2110890C1 |

| Многоканальное буферное запоминающее устройство | 1990 |

|

SU1721631A1 |

| Буферное оперативное запоминающее устройство | 1988 |

|

SU1559379A1 |

| Декодирующее устройство кода Рида-Соломона | 1988 |

|

SU1640830A1 |

| Устройство для управления вводом изображения | 1989 |

|

SU1751738A1 |

| Буферное запоминающее устройство | 1980 |

|

SU932566A1 |

Устройство относится к измерительной технике для представления измеряемых величин в цифровой форме и может быть использовано для регист- ращш информации в искровой и лазерной масс-снектрометрии с целью исследования состава твердых тел. Изобретение позволяет уменьшить погрешность измерения средних значений случайных величин с различными динамическими дианазонами измерения. Устройство для регистрации информации содер;кит генератор I случайных чисел, аналоговьй ключ 2, цифроаналоговый (Л е ю со CXD СП 00

li

JL

71

SH

S5-1

70

П

Редактор M. Циткина

Составитель О, Тюрина

Техред И.Поповт . Корректор А, Тяско

Заказ 2987/52 Тираж 67 Подписное

ВИИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д.4/5

Произнодственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Cpus.

| Ковалеров Г.И,, Мандельштам С.Н | |||

| Введение в информационную тгюрию измерения | |||

| М,: Энергия, 1974, с | |||

| Способ получения морфия из опия | 1922 |

|

SU127A1 |

| Бахтиаров Г.Д | |||

| Мащинин В.В., Школин В.П, Аналого-цифровые нреобра- зователи | |||

| М.: Сов.радио, 1980, с.211, Авторское сгзидетельствр СССР № 528583, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-05-30—Публикация

1984-08-06—Подача