1

Изобретение относится к области автоматики и вычислительной техники и может быть использовано в синтезаторах и анализаторах сложных сигналов различного назн:чения, в частное ти для формирования и обработки многочастотных сигналов в многоканальных моделях.

Известен цифровой генератор синусоидальных колебаний (синтезатор спектра), содержащий адресное устрой ство, состоящее из накопителей,постоянное запоминающее устройство для цифровых образцов мгновенных значений четверти периода синусоиды колебания основной частоты и выходное устройство, включающее цифроаналоговый преобразователь, фильтр нижних частот и усилитель низкой частоты с переменным коэффициентом усиления, предназначенный для формирования отдельных базисных функций или группового сигнала нескольких функций (спектра) l Наиболее близким техническим pelne нием к предлагаемому изобретению Является цифровой генератор базисных функций, содержащий генератор такто.вых импульсов, делитель частоты,сумматоры по модулю, блок преоСразования прямого кода в инверсный, геггистр управляющих сигналов и коммутаторы 2 .

Однако известные генераторы синте- зируют базисные функции с неизменными параметрами, что. сужает их функциональные возможности.

Цель изобретения - эасширение функциональных возможностей цифрового

to генератора базисных функций, состоящее в возможности регулировки параметров базисных функций.

Поставленная цель достигается тем, что цифровой генератор базисных функций, содержащий генератор тактовых импульсов, делитель частоты, первый, второй и третий сумматоры по модулю 2 (S - целое число), блок преобразования прямого кода в инверсный, блок

20 памяти, сумматор по модулю два, регистр управляющих сигналов, первый и второй коммутаторы, причем первый выход генератора тактовых импульсов подключен к входу делителя частоты,

-25 к тактовому входу первого сумматора по модулю 2 и управляющему входу первого коммутатора, выход делителя частоты подключен к тактовым входам второго и третьего сумматоров по мо30 дулю 2 и к управляющему входу второго.коммутатора, выход первого сумматора по модулю 2 подключен к первому входу второго коммутатора,выход второго сумматора по модулю 2 подключен к его первому входу и к второму входу второго коммутатора, выход которогоподключен к первому входу первого сумматора по модулю 2, выхо третьего uyr iaTopa по модулю 2S под ключен к его первому входу и второму 1ВХОДУ первого сумматора по модулю 2, первый вход сумматора по модулю два подключген к первому входу пе&вого коммутатора, второй вход сумматора по модулю два - к управляющему входу блока преобразования прямого кода в инверсный, выход сумматора по модулю два.подключен к второму входу первого коммутатора, выход которого является выходом знака функции генераторабазисных функций, выход блока преобразования прямого кода в инверсный подключен к адресному входу блока памяти, выход которого является выходом генератора базисных функций, содержит накопительный сумматор, четвертый, пятый, шестой,седьмой и восьмой сумматоры по модулю 2, причем выход числа базисных функций регистра управляющих сигналов подключен к входу накопительного сумматора, выход которого подключен к входу управления коэффициентом делителя частоты, выход делителя частоты подключен к тактовым входам четвертого, пятого, шестого и седьмого сумматоров по модулю 2, выход параметра частоты регистра управляющих сигналов подключен к первому входу четвертого сумматора по модулю 2 , выход которого подключен к его второму входу и первому входу пятого сумматора по МОДУЛЮ 2, выход фазы группового сигнала регистра управляющих сигналов подключен к второму входу пятого сумматора по модулю 2 , выход которого подключен к второму входу второго сумматора по модулю 2®, выход параметра разноса частоты составляющих группового сигнала регистра управляющих сигналов подключен к первому входу шестого сумматора по модулю 2, выход которого подключен к его второму входу и первому входу седьмого сумматора по модулю 2, выход задержки группового сигнала регистра управляющих сигналов подключен к второму входу седьмого сумматора по модулю 2 , выход которого подключен к второму входу третьего сумматора по модулю 2, выход фазы отдельных базовых функций регистра управляющих сигналсэв подключен к первому входу восьмого сумматора по модулю 2, тактовый вход восьмого сумматора по модулю 2 подключен к второму вьюсоду генератора тактовых импульсов, выходы разрядов с первого по (5-2)-й (со стороны младших

разрядов) восьмого сумматора по модулю 2 подключены к входам блока преобразования прямого кода в инверсный, а разрядов (S-l)-ro и S-ro - к входам сумматора по модулю два.

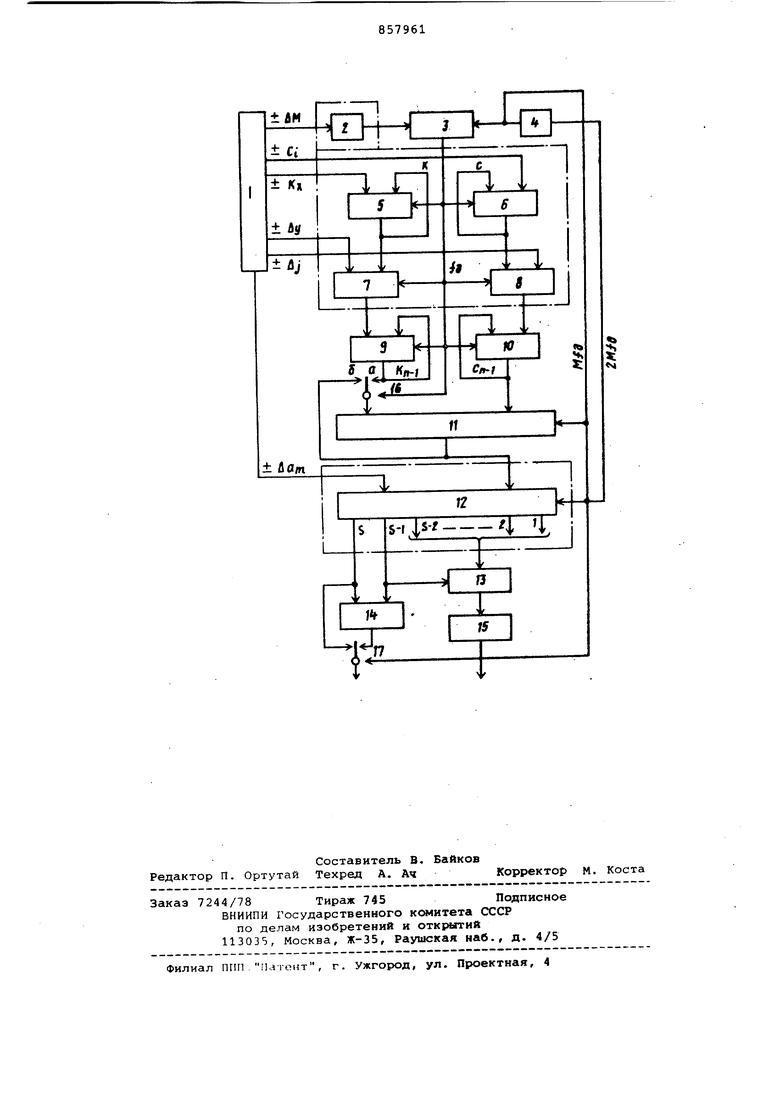

На чертеже представлена функциональная схема цифрового генератора базисных функций.

Он содержит регистр 1 управляющих сигналов, накопительный сумматор 2, делитель 3 частоты, генератор 4 тактовых импульсов, сумматоры 5-12 по модулю 2, блок 13 преобразования прямого кода в инверсный, сумматор 14 по модулю два, блок 15 памяти (ПЗУ), коммутаторы 16 и 17.

Генератор базисных функций работает следующим образом.

Число М генерируемых синфазных и квадратурных составляющих группового сигнала (общее число базисных функций - 2 М) хранится в накапливающем cyrviMaTope 2 и может изменяться под действием Управляющего си5нала с одного из выходов регистра 1 управляющих сигналов.

Цифровые образцы выборок, рассчитанные для дискретных фаз

-(,,--. ()

в пределах первой четверти периода синусоиды, хранятся в ПЗУ. Такое расположение выборок позволяет, управляя адресом, изменять фазу базисных функций на любые величины с точность до Д Ч 2Т/2.

Общее выражение развертки адресов поступающих на вход ПЗУ, определяется следующим равенством:

..,®

i(c®AC,),q

где ± - суммирование по модулю 2 , индексы X, у, i, j характеризуют время присутствия команд управления; п - текущая координата дискретного времени; m - текущий номер базисной функции в интервале строчной развертки; К и С - значения гармонических коэффициентов после очередного их изменения, характеризующих значение частоты первой (по оси частот) функции и разноса частоты между соседними функциями соответственно ;AKj(., й., д.- - приращения, получаемые этими коэффициентами в независимые моменты времени (в начале любой строки развертки) в процессе формирования адресов.

Интервал одной строки развертки определяется континуумом адресов образцов мгновенных значений всех составляющих одной выборки группового сигнала. Интервал одного кадра развертки заключен между изменениями одного из параметров выходного сигнала

Частота строк fd задается на выходе делителя 3 частоты, развертка адресов всех составляющих осуществляется с частотой 2М-ЕЭ , а синфазных (или квадратурных) составляющих с частотой Mf Э ,и синхронизируется импульсами с выхода генератора 4 тактовых импульсов.

Рассмотрим последовательность операций формирования гщресов а,,у„ при отсутствии команд управления. В исходном состоянии коммутатор 16 находится в положении а , и на входах блоков присутствуют следуилдие сигналы: сумматор 9 - сигнал Kj,; сумматор 10 - сигнал Cy.; сумматоры 5 и 7 - сигнал к; сумматоры 7 и 8 - сигнал С, на всех выходах регистра 1 сигналы отсутствуют.

Очередность следования операций для п-;ой строки представлена следующими выражениями: при (коммутатор 16 в положении d)

а„/(к„.®к)®(с„,@с),

при m 2, 3, 4,.,., М (коммутатор 16 в положении 5}

, ,OihaQ H

-nw vi(.tA-4)®

Аналогично, для (п+1)-ой строки имеем: при m 1 (коммутатор 16 в положении а)

,))®(c,(

М (коммутатор

при m 2, 3, 4, . . . 16 в положении d )

°Сии)г - (пи).

()3 emi)z®

(.VltlllVv CV1Vl)(M-x|)® t-l

и так далее.

Очевидно, что формирование адресов при наличии команд управления будет осуществляться по аналогичным aj.ropHTMaM с учетом приращений,определяемых командами управления:

а)при изменении частоты одновременно всех базисных функций на величину ± Af

х)® (с ®c«-iV,;

б)при изменении значения разноса частот между всеми соседними ба.зисными функциями

Опт ®

Bj при изменении фазы колебания группового сигнала

алу„--С(,-11®Сс®С,

г) при независимом изменении фаз колебаний любых составляющих группового сигнала

0„ .,)®(С®Си.-,)©

ИУЛ|

д) при изменении времени задержки группового сигнала

а,--и©к„-,)®(с®л)©Си-,,.

0

Значения приращений ±ДК и лС -запоминаются и на все последующие строки развертки, а приращения l и ±д учитьшаются только в той строке развертки, в начале которой они посту5пили . Этим и определяется различие конечного результата и воздействия на изменение параметров выходного сигнала.

При необходимости одновременного

0 изменения нескольких параметров выходного группового сигнала в начале строки вводятся одновременно соответствующие приращения.

Управление параметрами выходного

5 сигнала делает предлагаемый генератор пригодным для использования в широком классе устройств синтезу и анализа сложных сигналов, существенно упрощает их схемы, так как для управления параметрами сигнала необ0ходимы только датчики сигналов-команд управления. Эффективность такого генератора особенно проявляется в устройствах,где требуется осуществление автоматического управления па5раметрами сигнала (фазовый манипулятор, устройство тактовой синхронизации, автоматическая подстройка частоты, формирователь сигналов для криптоизлучений и др.).

0

Формула изобретения

Цифровой генератор базисных функЦий, содержащий генератор тактовых импульсов, делитель частоты, первый, второй и третий сумматоры по модулю 2 (S - целое число), блок преобразования прямого кода в инверсный,

блок памяти, сумматор по модулю два, регистр управляющих сигна тов, первый и второй коммутаторы, причем первый выход генератора тактовых импульсов (подключен к входу делителя частоты, к тактовому входу первого сут адатора

по модулю 2 и управляющему входу первого коммутатора, выход делителя частот ; подключен к тактовым входам второго и третьего сумматоров по модулю 2 и к управляющему входу второго

коммутатора, выход первого сумматора по Модулю 2 подключен к первому входу второго коммутатора, выход второго сумматора по модулю.2 подключен к его первому входу и к второму вхоДУ второго коммутатора, выход которого подключен к первому входу первого сумматора по модулю 2 , выход третьего сумматора по модулю 2® подключен к его первому входу и второму входу первого сумматора по модулю 2, первый вход сумматора по модулю два подключен к первому входу первого коммутатора, второй вход сумматора по модулю два - к управляющему входу блока преобразования прямого кода в инверсный, выход сумматора по модулю два подключен к второму входу первого коммутатора, выход которого является выходом знака функции генератора базисных Функций, выход блока преобразования, прямого кода в инверсный подключен к адресному входу блока памяти, выход которого является выходом генератора базисных функций, отличаю ц ийс я тем, что, с целью расширения функциональHbjx возможностей, состоящего в возможности регулировки параметров базисных функций, он содержит накопительный сумматор, четвертый,пятый, шестой, седьмой и восьмой сумматоры по модулю 2, причем выход числа базисных функций регистра управляющих сигналов подключен к входу накопительного сумматора, выход которого подк }1ючен к входу управления коэффициентом деления делителя частоты, выход делителя частоты подключен к тактовым входам четвертого, пятого, шестого и седьмого сумматоров по модулю 2 , выход параметра частоты регистра управляющих сигналов подключен к первому входу четвертого сумматора по модулю 2 , выход которого подключен к его второму входу и первому входу пятого сумматора по модулю 2 , выход фазы группового сигнала регистра управляющих сигналов подключен к второму входу пятого сумматора по модулю 2, выход которого подключен к второму входу второго сумматора по модулю 2, выход параметра разноса частоты составляющих группового сигнала регистра управляющих сигналов подключен к первому входу шестого сулматора по модулю 2 ®, выход которого подключен к его второму входу и первому входу седьмого сумматора по модулю 2, выход задержки группового сигнала регистра управляющих сигналов подключен к второму входу седьмого сумматора по модулю 2, выход которого подключен к второму входу третьего сумматора по модулю 2, выход фазы отдельных базовых функций регистра управляющих сих-налов подключен к первому входу восьмого сумматора по модулю 2, тактовый вход восьмвго сумматора по модулю 2 подключен к второму выходу генератора тактовых импульсов, выходы разрядов с первого по (5-2)-й

(со стороны младших разрядов) восьмого сумматора по модулю 2 подключены к входам блока преобразования прямого кода в инверсный, а разрядов

(S-l)-ro и 5-го - к входам сумматора по модулю два.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 466499, кл. G 06 F 1/02, 1973.

2 Патент США 373.5269, кл. 328-14, 1973 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой генератор базисных функций | 1980 |

|

SU968796A1 |

| Устройство отображения информации на экране телевизионного индикатора | 1986 |

|

SU1425768A1 |

| Устройство для ортогонального преобразования цифровых сигналов по функциям Хаара | 1983 |

|

SU1116435A1 |

| Преобразователь телевизионных стандартов | 1987 |

|

SU1506591A1 |

| Устройство для разложения цифровых сигналов по Уолшо-подобным базисам | 1983 |

|

SU1108461A1 |

| Цифровой преобразователь координат | 1979 |

|

SU873239A1 |

| Устройство для двумерной пространственной фильтрации электрических сигналов | 1981 |

|

SU970399A1 |

| СИСТЕМА ЦИФРОВОГО ЦВЕТНОГО ТЕЛЕВИДЕНИЯ | 1993 |

|

RU2103839C1 |

| Устройство для измерения координат центра тяжести изображения объекта | 1988 |

|

SU1660208A1 |

| Устройство синхронизации по групповому сигналу в многоканальных системах связи | 1984 |

|

SU1314471A1 |

15

Авторы

Даты

1981-08-23—Публикация

1979-08-20—Подача