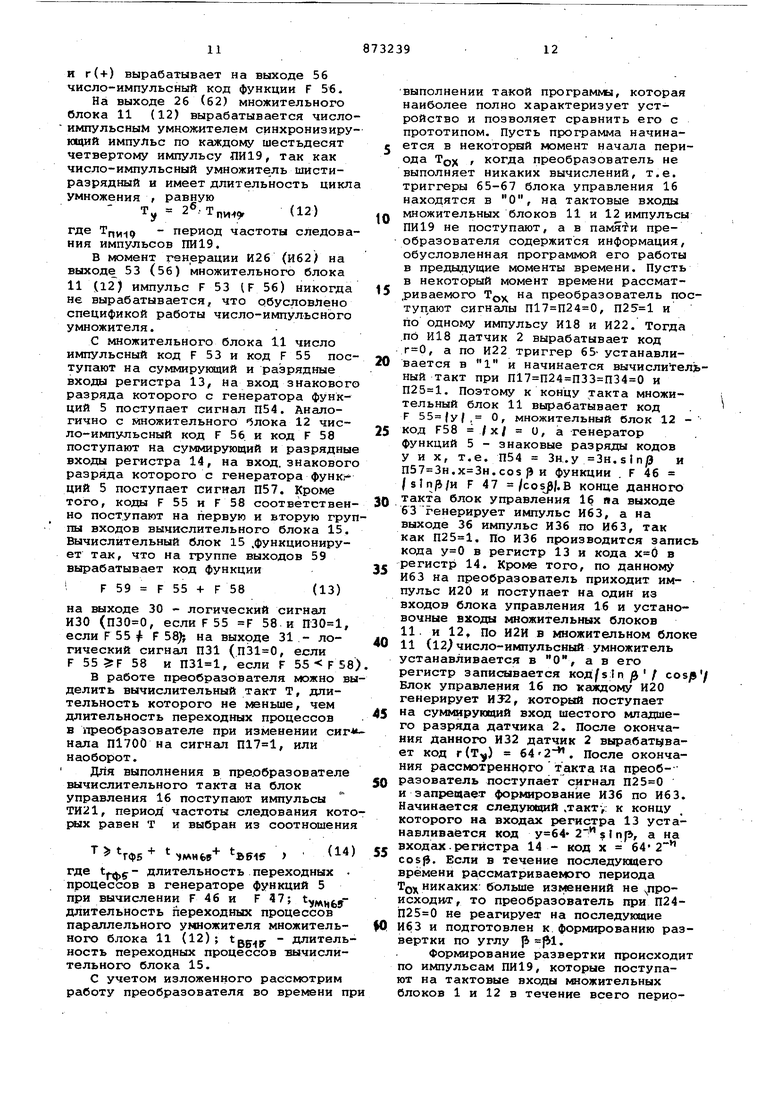

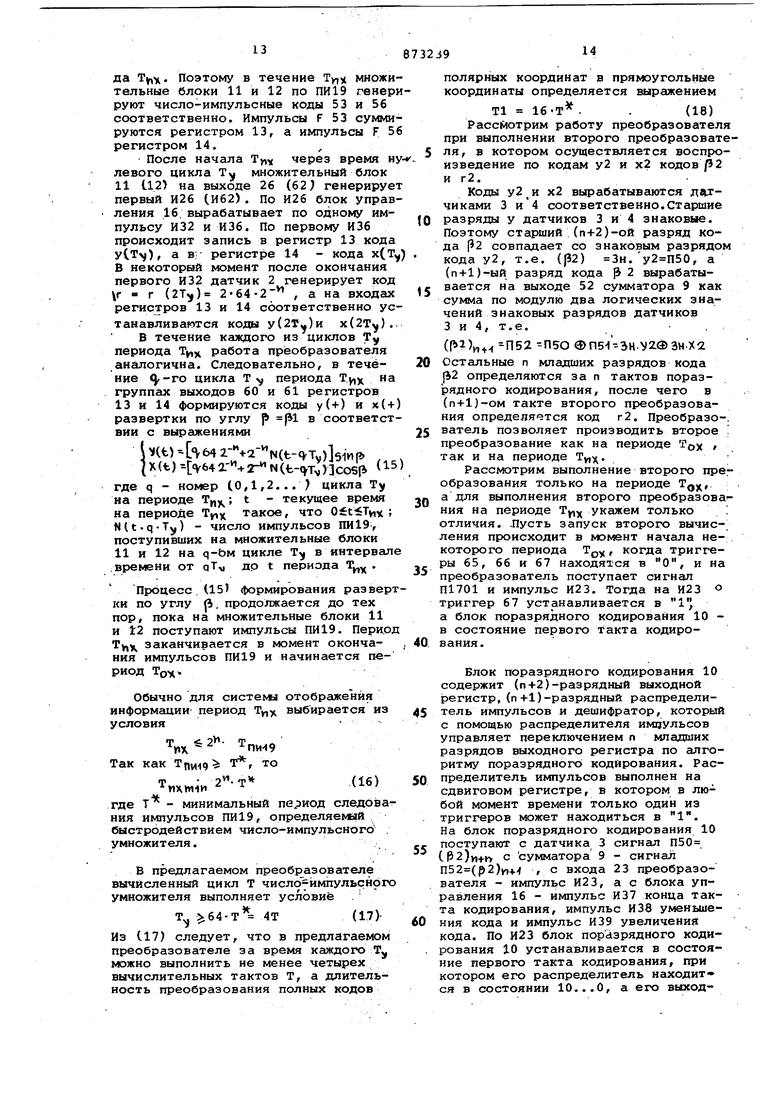

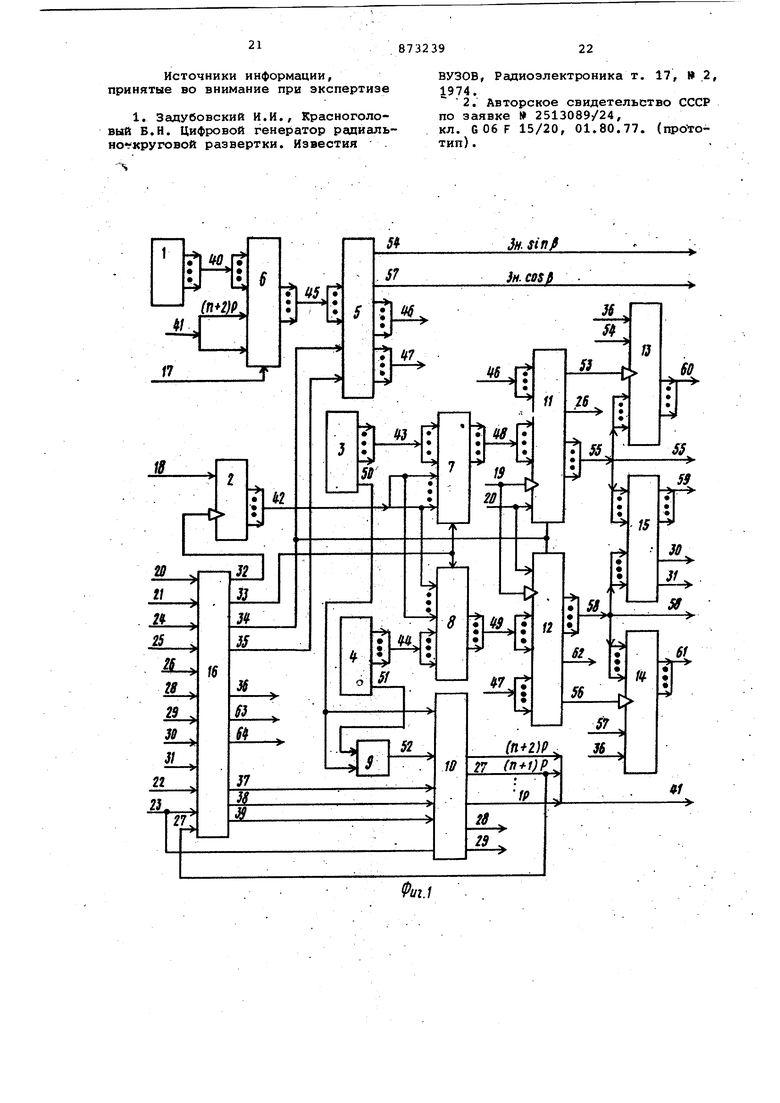

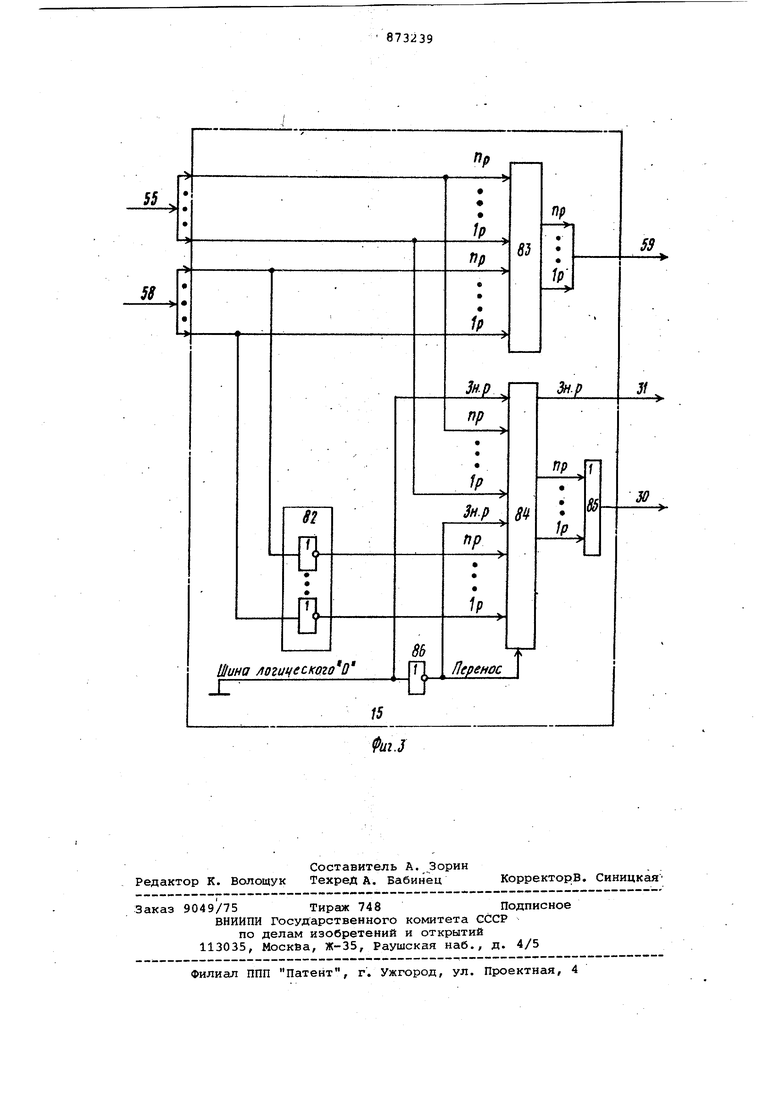

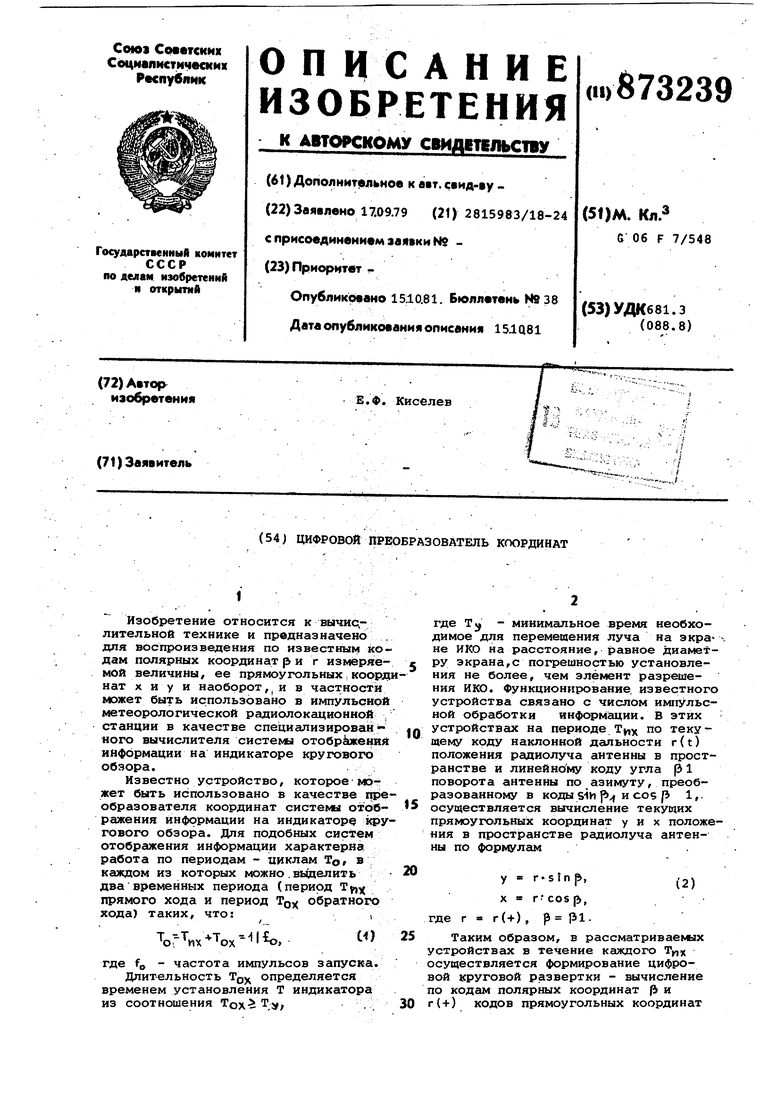

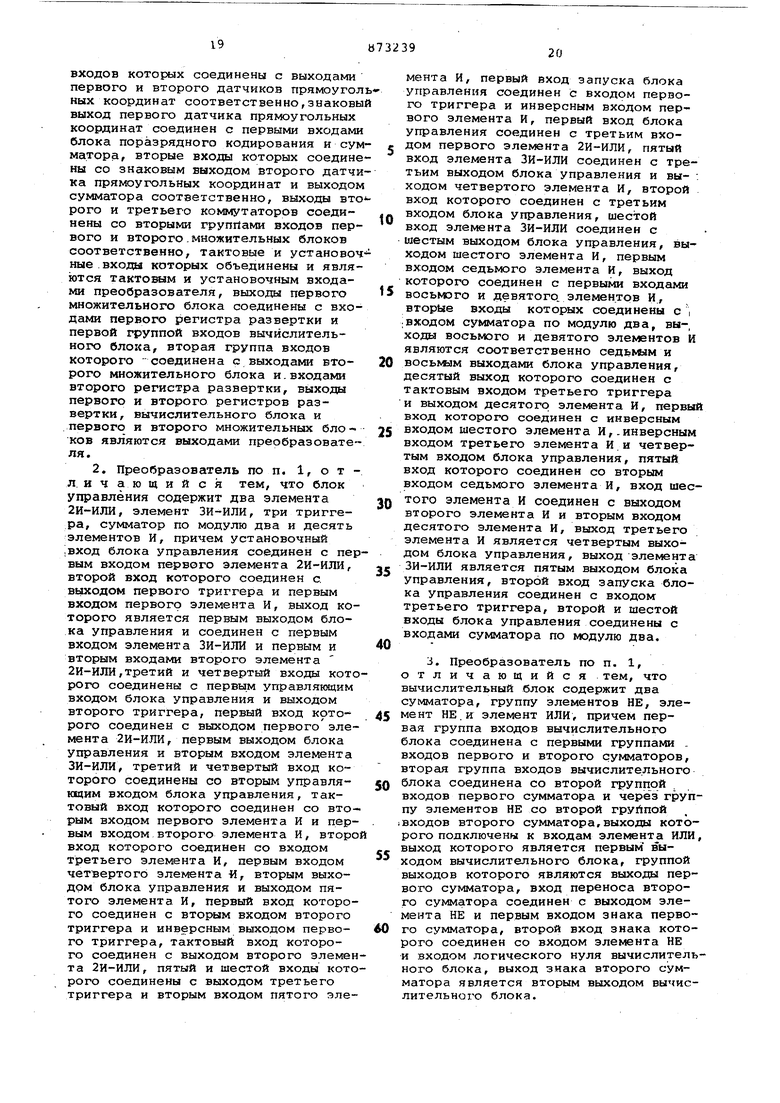

1 . ., , Изобретение относится к вычис,лительной технике и предназначено для воспроизведения по известным ко дам полярных координатри г измеряемой величины, ее прямоугольных;коорд нат х и у и наоборот,, и в частности может быть использовано в импульсной метеорологической радиолокационной станции в качестве специализированного вычислителя систекы отобрсисения информации на индикаторе кругового обзора. Известно устройство, которое мрг жет быть использовано в качестве пре образователя координат системы отображения информации на индикаторе 1ФУ гового обзора. Для подобных систем отображения информации характериа работа по периодам - циклам То в каждом из которых можно .вьщелить два временных периода (период Т, прямого хода и период TQX обратного хода) таких, что: ,i ТоГ-Т„х Гох-. частота импульсов запуска. Длительность ToJ определяется временем установления Т индикатора из соотношения ./ Ci) где Ту - минимальное время необходимое для перемещения луча на экра- не ИКС на расстояние, равное диаметру экрана,с погрешностью установления не более, чем злёмент разрешения ИКО. Функционирование, известного устройства связано с числом импульсной обработки информации. В этих устройствах на периоде Т„х о текущему коду наклонной дальности r(t) положения радиолуча антенны в пространстве и линейно му коду угла р 1 поворота антенны по азимуту, преобразованному в коды sin р и cos р 1, осуществляется вычисление текущих прямоугольных координат у и х положения в пространстве радиолуча антенны по формулам у я г-SfП р, X rcosp, r(-f), р Р1Таким образом, в рассматриваемых устройствах в течение каждого осуществляется формирование цифровой КРУГОВОЙ развертки - вычисление по кодам полярных координат ft я г(+) кодов прямоугольных координат у и X. Причем, координаты у и х вырабатываются первоначально в числоимпульсных кодах ЧИКУ и ЧИКХ, так как именно число-импульсная обработка информации позволяет получить наи большее быстродействие при формировании цифровой круговой развертки. В дальнейшем вычислительный процесс (2 в течение Ту, приг г( + );И постоянном р будем называть формированием развертки по углу р ClJ . В известном устройстве число-импульсные коды X и у генерируются одновременно и поступают на цифроаналоговые блоки, которые формируют в течение Т сигналы, управляющие положением луча на экране индикатора в соответствии с положением радиолуча антенны в пространстве. Однако функциональные возможности этого устройства не высоки, так как в них не предусмотрена работа с датчиком цифровых координат маркера. Известно также устройство, в котором имеется возможность работы с датчиком цифровых координат маркера 1.. Но оно имеет невысокий коэффициент использования оборудования, так как его формирователь цифровой круговой развертки и датчик кодов цифровых координат маркера выполнены независимо, т.е. без учета друг друга. Наиболее близким к предлагаемому по технической -сущности является уст ройство , содержащее первый и второй датчики полярных координат, первый коммутатор, генератор синусно-косинусных функций, блок управления, пер вый и второй датчики прямоугольных , координат, первый и второй множител ные блоки, первый и второй регистры разверток, блок поразрядного кодирования II сумматор г причем выходы блока поразрядного кодирования соединены с первой группой входов первого коммутатора, вторая группа вхо дов которого соединена с выходами пе вбго датчика полярных координат, выходы первого коммутатора соединены с группой входов генератора си нусно-косинусных функций, первая и вторая группы выходов которого соеди нены с первыми группами входов соот ветственно первого и второго множительных блоков, управлянядий вход йервого коммутатора является входом аз ов ат е л я 31. Недостатком известного устройств является низкое быстродействие. Цель изобретения - повышение быс тродействия. Поставленная цель достигается те что в устройство, содержащее первый и второй датчики полярных координат первый коммутатор, генератор синусно-косинусныхфункций, блок управлеНИН, первый И второй датчики прямоугольных координат, первый и второй лаожительные блоки, первый и второй регистры разверток, блок поразрядного кодирования и сумматор, причем выходы блока поразрядного кодирования соединены с первой группой входов первого коммутатора, вторая группа входов которого соединена с выходами первого датчика полярных координат, выходы, первого коммутатора соединены с группой входов генератора синусно-косинусных функций, первая и вторая группы выходов которого .соеди нены с первыми группами входов соот- , ветственно первого и второго множительных блоков, управляющий вход первого коммутатора.является входом преобразователя, дополнительно введены второй и третий коммутаторы и вычислительный блок, причем установочный, тактовый, ;первый и второй управляющий входы блока управления являются входами преобразователя, первый, второй, третий и четвертый входы блока управления соединены соот- ; ветственно с синхронизирующим выходом первого множительного блока, первым, вторым и третьим управляющими выходами блока поразрядного кодирования, пятый и шестой входы блока управления соединены с перЪым и вторым управляющими выходами вычислительного блока, первый и второй входы запуска блока управления являются входами преобразователя, второй вход запуска блока управления соединен с установочным входом блока поразрядного кодирования, первый выход блока управления соединен с суммирунндим входом второго датчика полярных координат , управляющий вход которого является входом преобразователя, второй вход блока управления соединен с управляющими входсши второго и третьего коммутаторов, третий выход блока управления.соединен с первым управляющим входом гененатора синусно-косинусных функций и управляющими входами первого и второго множительных блоков, четвертый выход .блока управления соединен со втором у 1равлякхцим входом генератора синусно-косинусных функций, пятый выход блока управления соединен с входами записи.первохю и второго регистров развертки, шестой, .седьмой и восьмой выходы блока управления соединены соответственнос входом импульса конца кодирования, входом импульса уменьшения кода и входом импульса увеличения кода поразрядного кодирования, девятый и десятый выходы блока управления являются выходами преобразователя, первый и второй знаковые выходы генератора синусно-косинусных функций соединены со знаковыми входами соответственно первохю и второго регистров развертки, суммирующие входы которых соединены с числоимпульсными входами соответственно первого и второго множительных блоков, синхронизирующий выход второ-го множительного блока является выходом преобразователя, выходы второго датчика полярных координат соединен с первыми группами входов второго и третьего коммутаторов, вторые гру пы входов которых соединены с выходами первого и второго датчиков прямоугольных координат соответстве но, знаковый выход первого датчика прямоугольных координат соединен с первыми входами блока поразрядного кодирования и сумматора, вхо ды которых соединены со-знаковым выходом второго датчика прямоугольных координат и выходом сумматора .соответственно, выходы второго-и третьего коммутаторов соединены со вторыми группами входов первого и второго множительных блоков соответ ственно, тактовые и установочные входы которых объединены и являются тактовым и установочным входами пре образователя, выходы первого множительного блока соединены с входами первого регистра развертки и первой группой входов вычислительного блок вторая группа входов которого соеди нена с выходами второго множительно блока и входами второго регистра развертки, выхода первого и второго регистров развертки, вычислительног блока и первого и второго множитель ных блоков являются выходами преобразователя. . Блок управления содержит два элемента 2И-ИЛИ/ элемент ЗИ-ИЛИ, три триггера, сумматор по модулю и десять элементов И, причем установочный вход блока управления соединен С первым входом первого элемента 2ИЙЛИ, второй вход которого соединен с выходом первого триггера и первым входом первого элемента И, выход .которого является первым выходом блока управления и соединен с первым входо элейента ЗИ-ИЛИ и первым и вторым вх дами второго элемента 2И-ИЛИ, третий чётвертый входы которого соединены с первым управляющим входом блока управления и выходом второго триггера, первый вход которого соединен с выходом первого элемента 2И-ИЛИ, первым выходом блока упрабления и вторым входом элемента ЗИ-ИЛИ, третий и четвертый вход которого соединены со вторым управляющим, входом блока управления, тактовый вход кото рого соединен со вторым входом первого элемента И и первым входом второго элемента И, второй вход кото рого соединен со входом третьего эле мента И, первым входом четвертого элемента И, вторым выходом блока управления и выходом пятого элемента И, первый вход которого соединен с вторым входом второго триггера и инверсным выходом первого триггера, тактовый вход.которого соединен с выходом второго элемента 2И-ИЛИ, пятый и шестой входы которого соединены с выходом третьего триггера и входом пятого элемента И, первый вход, запуска блока управления соединен с входом первого триггера и инверсным входом первого элемента И, первый вход блока управления соединен с третьим входом первого элемента 2И-ИЛИ, пятый вход элемента ЗИ-ИЛИ соединен с третьим выходом блока управления и выходом четвертого элемента И, второй вход которого соединен с третьим входом блока управления, шестой вход элемента ЗИ-ИЛИ соединен с шестым выходом блока-управления, выходом шестого элемента И, первым входом седьмого элемента И, выход которого соединен с первыми входами восьмого и девятого элементов И, вторые входы которых соединены с выходом сумматора по модулю два, выходы восьмого и девятого элементов И являются соответственно седьмым и восьмым выходами блока управления,, десятый выход которого соединен с тактовым входом третьего триггера и выходом десятого элемента И, первый вход которого соединен с инверсным входам шестого элемента И, инверсным входом третьего элемента И и четвертым входом блока управления, пятый вход которого соединен со вторым входом седьмого элемента И, вход шестого элемента И соединен с выходом второго элемента И и вторым входом десятого элемента И, выход, третьего элемента И является четвертым выходом блока управления, выход элемента ЗИ-ИЛИ является пятым выходом блока управления, второй вход запуска блока управления соединен с входом третьего триггера, второй и шестой входы блока управления соединены с входами сумматора по модулю два. Вычислительный блок содержит два сумматора, группу элементов НЕ, элег мент НЕ и элемент ИЛИ, причем первая группа входов вычислительного бло к а соединена с первыми группами входов первого и второго сумматоров, вторая группа входов вычислительного блока соединена со второй группой входов первого сумматора и через группу элементов НЕ со второй группой входов второго сумматора, выходы которого подключены к входам элемента ИЛИ, выход которого является первым выходом вычислительного блока, группой выходов которого являются выходы первого сумматора, вход переноса второго сумматора соединен с выходом элемента НЕ и первым входом знака первого сумматора, второй ход знака которого соеДинен со вхоом элемента НЕ и входом логическоГО нуля вычислительного блока, выход знака второго сумматора является вто рым выходом вычислительного блока. На фиг. 1 представлена блок-схема устройства; на фиг. 2 и 3-- блоксхема бло1са управления и вычислитель ного блока. Устройство содержит датчики 1 и 2 полярных координат, датчики 3 и 4 прямюугольных координат, генерато синусно-косинусных функций 5, комму татори б, 7 и 8, сумматор 9, блок поразрядного кодирования 10, множи:тельные блоки 11 и 12, регистры 13 и 14 развертки, вычислительный блок 15, блок управления 16, управляющие входы 17 и 18 первого коммутатора и второго датчика полярных координат, тактовый вход 19 множите шых блоков, установочный вход 20 .устройства, -.входы 21-31 блока управления, выходы 32-39 блока управления,входы 40 и 41 перво.й и второй групп первого коммутатора, входы 42 и 43 первой и второй групп второго коммутатора, входы 44 второ группы третьего коммутатора, выходы 45 первого коммутатора, выходы 46 и 47 первой и второй групп генератора функций, выходы 48 и 49 второго и третьего коммутаторов, выходы 50 и 51 3Haka первого и второго датчиков прямоугх)Л)ьных координат, выход 52 сумматора, выход 53 число-импульсно го кода первого множительного блока выход 54 знака синуса генератора функций, выходы 55 первого множител ного блока, выход 56 число-импульсного кода, выход 57 знака косинуса генератора функций, выходр 59 вычис лительного блока, выходы 60 и 61 пе вого и второго регистров развертки, выход 62 синхронизации второго мно1жителБНого блока, выходы 63 и 64 бл ка управления. Блок управления содержит триггеры 65-67, сумматор 68 по модулю два логические элементы 69-81. Вычислительный блок содержит группу 82 элементов НЕ, первый и второй сумматоры 83 и 84, элемент ИЛИ 85 и элемент НЕ 86. Сумматоры 9 и 71 одинаковы и каждый из них реализует операцию сумми рования по модулю два двух логических переменных. Каждый из датчиков 1, 2 или 3, 4, в простейшем случае представляет собой или счетчик или регистр, а в более сложных случаях в.датчике может иметься несколько регистров счет.чиков и коммутатор. Генератор функции 5 выполнен на основе цифрового синусно-косинусного преобразователя. Коммутаторы 6, 7 и 8 одинасховы и каждый из них содержит (п+2)12 элементов 2 И-2И-ИЛИ и .инвертор и работает так, что в зависимости от значения логического сигнала на управляквдем входе, коммутатор пропускает на выходы сигналы кода с первой или второй групп входов коммутатора. Регистры 13 и 14 одинаковы и каждый из них содержит триггер знака и счетчик, в который может приниматься информация как числоимпульсным, так и параллельным кодом. Преобразователь выполнен на базе потенциальных цифровых элементов, триггеры которой переключаются в некоторые моменты времени после окончания импульсов на их синхронизирующих- входах. Преобразователь может выполнять как первое преобразо- j вание - воспроизведение по (п+2) разрядному коду (3 и п-разрядному коду г(п+1)-разрядных крдов у и х так и второе преобразование - воспро йзведение по (п+1)-разрядным кодам у2 и х2 (п+2)-разрядного кода р 2 и п-разрядного кода г2. Вес стараего разряда кода р равен Т , а старшие разряды у кодов у и X знаковые. Коды у, X и г прямые и нормированы так, что каждому из них соответствует п-разрядное двоичное число (т.е. число у, X и г) модуль которого может изменяться в пределах 0.- 1 -2 с весом младаюго разряда 2 . Выполнение в преобразователе первого преобразования основано на одновременном решении по формулам 42 ). Второе преобразование выполняется в преобразователе за (h+1) тактов. Первые п тактов второго преобразования являются тактелш поразрядного кодирования для нахождения угла кого, для которого наиболее точно выполняется -приближенное -равенство 2С05р,-Х251Ир) (3) где риц. - угол, (п+2) -разрядный код которого снимается с группы выходов 41 блока поразрядного кодирования 10 в (п+1)-ом такте второго преобразования. Яри точном выполнении равенства (3| Ри.ГР в (п+1)-ом faKTe второго преобразования находится код координаты.. г2 в соответствии с формулой r2-V251h|J2.fX2c05fb2(4) В процессе работы преобразователя коды.у2 и х2, а также все результаты первого преобразования (коды у и х) могут быть сняты как с групп выходов 60 и 61 регистров 13 и 14, так и с разрядных входов этих, регистров, т.е. знаковые разряды с выходов 54, 57 генератора функций 5, остальные разряды с групп выходов 55 и 58 множительных блоков 11 и 12 соответственно. Результат второго вычисления код Р2 и код г2 снимаются с. группы выходов 41 блока поразрядного кодирования 10 и с группы выходов 59 вычислительного блока 15 соответствен но.Предлагаемый преобразователь пре Яусматриваетвозможность программног выполненияво времени первого и второго преобразований с приоритетом для первого преобразования. Про рамма работы преобразователя осуществляется по приходящим на входы 17 ,24 и 25 управляющим логическим сигналам П17, А24, П25, на входы 18 и 20 - установочным импульсам И18 и И20, на вход 19 - последовательности импульсов ПИ19, на вход 21 - тактовым импульсам ТИ21 и на входы 22 и 23 - импульсам запуска И22 и И23 первого и второго преобра ,зований соответственно. Каждый из входных импульсов (исключение.могут составить только импульсы ПИ1Щ) обя зательно совпадает по времени с одним -из импульсов ТИ21. Длительность каждого из импульсов ТИ21 или 11И19 выбрана по возможности наиболее короткой, но и достаточной для того, чтобы обеспечить надежное срабатыва ние цифровых схем преобразователя. Для импульсов ПИ19 характерно также и то, что они поступают на преобразователь только в течение периода T В процессе работы блок управлени 16вырабатывает на выходах 32, 36, 37, 38, 39, 63 и 64 импульсы И32, И26, И37, И38, И39, И63 И64, а на выходах 33, 34 и 35 - логические уп равляющие сигналы ПЗЗ, П34 и П35. Сигнал П17 управляет работой коммутатора 6, а сигнал ПЗЗ - работой ко мутаторов 7 и 8. На коммутатор 6 поступают с вход 17преобразователя сигнал П17, с группы выходов 40 датчика 1 - код угла jil а с группы выходов. 41 блока поразрядного кодирования Ю - код угла PJ. Коммутатор 6 по сигналу П17 и кодам PI и pj на группе вых дов 45 вырабатывает код угла |3 такой , что р)тГ7|Ъ{ Ш7М (5) На коммутатор 7 поступает с выхо да 33 блока управления 16 сигнал ПЗЗ, с группы выходов 42 датчика 2 код г, а с группы выходов 43 датчика 3 - код }у2|. Коммутатор 7 по сигналу ПЗЗ и кодам г и (y2J на группе выходов 48 вырабатывает код ;функции F48 в соответствии с выражениемF48--n 3r4n 3JVi/ (б) На коммутатор 8 поступают с выход 33 блока управления 16 сигнал ПЗЗ, с группы выходов 42 датчика 2 - код гас группы выходов 44 датчика 4 код Ix2f .Коммутатор 8 по сигналу ПЗЗ и кодам г и /х2; на группе выходов 19 вырабатывает код функции F 49 в соответствии с выражением .( (7J С группы выходов 4Ь коммутатора 6 код J) поступает на входы аргумента генератора функции 5, на управляющие входы которого с блока управления 16 поступают сигналы П34 и П35. Генератор (функций 5 i по коду j5 вырабатывает на выходе 54знаковый разряд кода SiH р, выходе 57 - знаковый разряд кода СО9|3. Кроме того, генератор, функций 5 по коду р и сигналам П34 и П35 вырабатывает на группах выхо-, дов 46 и 47 п-разрядные коды функций F 46 и F 47 в соответствии с выражениямиF46-П34СпТв /61И Ь/1П 35Icosft/)- V (8) Р47 П54(пТ5/С05р/ + ПЭ5(91И|Ъ()+ - ПM«-2-) С генератора функций 5 коды F 46 и F 47 поступают на первые группы входов множительных блоков 11 и 12, на вторые группы входов которых с коммутаторов 7 и 8 поступают коды F48 и F 49 соответственно.Кроме того, на корректирующие входы множительных блоков 11 и 12 подается с блока управления 16 сигнал П34, а на установочные и тактовые входы - соответственно И20 и ПИ19 с входов 20 и 19. Множительный блок 11 по кодам F 46 и F48 и сигналу П34 вырабатывает на группе выходов 55 код функции F 55, а множительный блок 12 по кодам F 47 и F 49 и сигналу П34 - код функции F 58. В связи с этим работу параллельных умножителей 65 множительных блоков 11 и 12 можно записать выражениямиF55 Р46Р48+П34СР48)и2 Р5в F47 F49 -« П 34 CF49)h 27 гдe(F 48)и (F 49)- разрядные цифры старшего п-го разряда кода F 48 и кода F 49 соответственно. В правых частях выражений (,10) и (11) вторые слагаемые являются корректирующими и именно с их помощью при получаем F 55 / у2/ и F 58 I х2| . Во время каждого в регистре множительного блока 11 (.12) содержится (/Со&р/ шести старших разрядов кода /б1и15/((со5р() , а на чис-. о-импульсный умножитель поступают импульсы ПИ19, представляющие собой на периоде число-импульсный код г( + ), каждый импульс которого имеет вес 2, Поэтому во-время каждого Тих множительный блок 11 по кодам |eihp/ и г( + ) вырабатывает на выходе 53 чис- , ло-импульсный код функции F 53, а ножительный блок 12 по кодам| cosр|

и r(+) вырабатывает на выходе 56 число-импульсный код функции F 56. На выходе 26 (62) множительного блока 11 (12) вырабатывается числоимпульсныМ умножителем синхронизирующий импульс по каждому шестьдесят четвертому импульсу ПИ19, так как число-импульсный умножитель шистиразрядный и имеет длительность цикла умножения , равную

- Т,, 26..Tnvn9r (12)

где Тпи19 период частоты следования импульсов 11И19.

В момент генерации И26 (И62/ на выходе 53 (56) множительного блока 11 (12) импульс F 53 IF 56) никогда не вырабатывается, что обусловлено спецификой работы число-импульсного умножителя.

С множительного блока 1,1 число импульсный код F 53 и код F 55 поступают на суммирукнций и разрядные входы регистра 13, На вход знакового разряда которого с генератора функций 5 поступает сигнал П54. Аналогично с множительного блока 12 число-импульсный код F 56 и код F 58 поступают на суммирующий и разрядные входы регистра 14, на вход, знакового разряда которого с генератора функ;ций 5 поступает сигнал П57. Кроме того, коды F 55 и F 58 соответственно поступают на первую и вторую группы входов вычислительного блока 15. Вычислительный блок 15 .функционирует так, что на группе выходов 59 вырабатывает код функции

(13)

F 59 F 55 + F 58

на выходе 30 - логический сигнал ИЗО (, если F55 F 58 и , если Г 55 F 58)j на выходе 31 - логический сигнал П31 (, если F 553;F 58 и , если F ) В работе преобразователя можно выделить вычислительный такт Т, длительность которого не меньше, чем длительность переходных процессов в преобразователе при изменении сиг «нала П170й на сигнал , или наоборот.

Для выполнения в преобразователе вычислительного такта на блок управления 16 поступают импульсы ТИ21, период частоты следования которлх равен Т и выбран из соотношения

(14) 55

гф5 чмнбв bei5

где - длительность переходных . процессов в генераторе функций 5 при вычислении F 46 и F 47; ty jдлительность переходных процессов параллельного умножителя множительного блока 11 (12); tgg - длительность переходных процессов вычислительного блока 15.

С учетом изложенного рассмотрим работу преобразователя во времени пр

выполнении такой программы, которая наиболее полно характеризует устройство и позволяет сравнить его с прототипом. Пусть программа начинается в некоторый момент начала периода TOX , когда преобразователь не выполняет никаких вычислений, т.е. триггеры 65-67 блока управления 16 находятся в О, на тактовые входы множительных блоков 11 и 12 импульсы ПИ19 не поступают, а в памяти преобразователя содержится информация, обусловленная программой его работы в предыдущие моменты времени. Пусть в некоторый момент времени рассматриваемого TQ) на преобразователь потудают сигналы , и по одному импульсу И18 и И22. Тогда .по И18 датчик 2 вырабатывает код г 0, а по И22 триггер 65- устанавливается в 1 и начинается вычислителный такт при и . Поэтому к концу такта множительный блок 11 вырабатывает код г . О, множительный блок 12 код F58 /X/ и, а генератор функций 5 - знаковые разряды кодов у и X, т.е. П54 Зн.у 3H.sln/J и ..со5р и функции . F 46 /slnp/и F 47 .B конце данного такта блок управления 16 яа выходе 63 генерирует импульс ИбЗ, а на выходе 36 импульс И36 по ИбЗ, так как . По ИЗб производится запис кода в регистр 13 и кода в регистр 14. Кроме того, по данном}/ И63 на преобразователь приходит импульс И20 и поступает на один из входов блока управления 16 и установочные входы множительных блоков 11. и 12, По И2И в множительном блок 11 (12 число-импульсный умножитель устанавливается в О, а в его регистр записывается Kojijslnftf cos Блок управления 16 по каждому И20 генерирует И32, который поступает на суммируюошй вход шестого младшего разряда датчика 2. После окончания данного И32 датчик 2 вырабат1 вает код г(Т) 642 . После окончания рассмотренного тракта на преобразователь поступает сигнал и запрещает формирование ИЗб по ИбЗ. Начинается следующий .такту к концу которого на входах регистра 13 устанавливается код S I п|5, а на входс1зс.регистра 14 - код х 642 cos. Если в течение последующего времени рассматриваемого периода ох никаких: больше изменений не происходит, то преобразователь при П24П25 0 не реагирует на последующие ИбЗ и подготовлен к формированию развертки по углу .

Формирование развертки происходи по импульсам ПИ19, которые поступают на тактовые входы множительных блоков 1 и 12 в течение всего периода f. Поэтому в течение множи тельные блоки 11 и 12 по ПИ19 генер руют число-импульсные коды 53 и 56 соответственно. Импульсы F 53 сумми руются регистром 13, а импульсы F 5 регистром 14. После начала через время н левого цикла Т множительный блок 11 (.12) на выходе 26 (62) генерируе первый И26 СИ62). По И26 блок управ ления 16. вырабатывает по одному импульсу И32 и И36. По первому И36 происходит запись в регистр 13 кода уСт), а в: регистре 14 - кода х(Ту В некоторЕ1й момент после окончания первого И32 датчик 2 генерирует код г - г (2Т) 2-64-2 , а на входах регистров 13 и 14 соответственно ус танавливаются коды у(2Т)и х(2Ти). В течение каждого из циклов Ту периода Т|, работа преобразователя аналогична. Следовательно, в течёиие -го цикла Т периода Ту, на группах выходов 60 и 61 регистров 13 и 14 формируются коды у(+) и х(+ развертки по углу р ( в соответст вии с выражениями b(t) 2-%а-Кь-ЧТ..)51игг. jX(t)%642.(b-.T)C05J 15 где q - номер (0,1,2... ) цикла Ту на периоде t - текущее время на периоде такое, что J N(t.q-Ty) - число импульсов ПИ19, поступивших на множительные блоки 11 и 12 на q-bM цикле Т в интервале ;времени от qT ДО t периода Т . Процесс, (15) формирования разверт ки по углу р. продолжается до тех пор, пока на множительные блоки 11 и 12 поступают импульсы ПИ19. Перирд f заканчивается в момент окончания импульсов ПИ19 и начинается период TOX Обычно для систе1 1 отображения информации- период Т, выбирается из условия. чг. Tnv,9 Так как Тцу,д Т, то Т HXWIH где Т - минимсшьный период следования импульсов ПИ19, определяемай быстродействием число-импульсного . умножителя. В предлагаемом преобразователе вычисленный цикл Т число ймпульсного умножителя выполняет условие . Т 64-т 4Т Из (17) следует, что в предлагаемом преобразователе за время каждого Т можно выполнить не менее четырех вычислительных тактов Т, а длительность преобразования полных кодов (16) (17) полярных координат в прямоугольные координаты определяется выражением Т1 16Т . . (18) Рассмотрим работу преобразователя при выполнении второго преобразователя, в котором осуществляется воспроизведение по кодам у2 и х2 кодов /32 и г2. Коды у2 и х2 вырабатываются датчиками 3 и4 соответственно.Старшие разряды у датчиков 3 и 4 зиаковые. Поэтому старший (п+2)-ой разряд кода С2 совпадает со знаковым разрядом кода у2, т.е. (р2) 3н., а (п+1)-ый разряд кода 2 вырабатывается на выходе 52 сумматора 9 как сумма по модулю два логических значений знаковых разрядов датчиков 3 и 4, т.е. . ()„ П52 -П5О ®n5-|-3H.V2®3H.X2 Остальные п младших разрядов кода %2 определяются за п тактов поразрядного кодирования, после чего в (п+1)-ом такте второго преобразования определяется код г2. Преобразо-. ватель позволяет производить второе . преобразование как на периоде T{jy , так и на периоде ). Рассмотрим выполнение второго преобразования только на периоде T0J, а для выполнения второго преобразова ния на периоде Tji укажем только : отличия. .Пусть запуск второго вычисления происходит в момент начала некоторого периода , когда триггеры 65, 66 и 67 находятся в О, и на преобразователь поступает сигнал П1701 и импульс И23. Тогда на И23 о триггер 67 устанавливается в 1 а блок поразрядного кодирования 10 в состояние первого такта кодирования. Блок поразрядного кодирования 10 содержит (п+2)-разрядный выходной регистр,(п+1)-разрядный распределитель импульсов и дешифратор, который с помощью распределителя имцульсов управляет переключением п млададих разрядов выходного регистра по алгоритму поразрядного кодирования. Распределитель импульсов выполнен на сдвиговом регистре, в котором в любой момент времени только один из триггеров может находиться в 1. На блок поразрядного кодирования 10 поступают с датчика 3 сигнал П50 СЭ2))ц. с сумматора 9 - сигнал П52(р2)и-|-« , с входа 23 преобразователя - импульс И23, ас блока управления 16 - импульс И37 конца такта кодирования, импульс ИЗБ уменьшения кода и импульс И39 увеличения кода. По И23 блок поразрядного кодирования 10 устанавливается в состояние первого такта кодирования, при котором его распределитель находится в состоянии 10...О, а его выходной регистр в состоянии, соответствующем углу ((2 VsL (p2V+-f .-ИС |4 В процессе выполнения второго преобразования распределитель производит распределение блока поразрядного кодирования имцульсов И38 и И39 таким образом, что в каждом j-oM такте кодирования осуществляет переключение .триггеров выходного регисра так, что в выходном регистре по Й38 триггер разряда ()- j и разряда (п-|) устанавливаются в .. О и в 1 соответственно, а поИ 39 триггер разряда (п+1)- j остается в состояние 1 итриггбр разряда (n-j) переключается из О в 1 В процессе второго преобразования «лок поразрядного кодирования 10 вырабатывает на выходе 28 признак И28 первого такта кодирования, на выходе 29 -признак П29 . (п+1)-го такта второго преобразования, на вы ходе 27 - (п+1)-ый разряд кода JJ2, а на группе выходов 41 - код лj, В течение второго преобразования на .преобр.азователь поступает сигнс1л , а блок управления 16 вырабатывает сигналы П3301, , . Второе преобразование запускается по И23, по которому начин ется первый такт кодирования. Б теч ние первого такта кодирования блок: поразрядного кодирования 10 вырабатывает сигналы , , И27 (Р2)и+1 и код . В конце каждого такта .второго преобразования, кроме последнего ( такта, блок управления 16 по ТИ 21 генерирует импульс И37 конца такта кодирования. К концу первого такта кодирования . вырабатываются ;генератором синусно-косинусных функ ций 5 сигналы . у2, . х и коды F 46 F , множительным блоками 11 и 12 - код ко F , а вычислительным блоком 15 - сигнал ПЗО (, если/у2/ /х и , если/у2/ #/х2Ли сигнал (, если / и , есл /у2/ /х2 Л . В конце первого такта кодирования блок управления 16 по И при генерирует И36, по которо му в регистры 13 и 14 заносятся коды у2 и х2 для отображения через вр мя Т координатной точки (у2, х2). Кроме того, в первом такте, как в любом другом такте поразрядного кодирования, блок управления 16 по И37 при генерирует И38 либо И39. Причем, при , И38 и И39 не вырабатываются, так как ft2 при и П27 4- вырабатывается И38, означая, что ftj fft2 при и П27 вырабатывается И3 означая, что|9 р5. Поэтому в конце каждого j-ro такта поразрядного кодирования по И38 (или И39) для последующего Tj+D-ro такта второго преобразования устанавливается код Р (или ). Каждый J-й такт кодирования при отличается от первого такта только тем, что в этих тактах управление работой генератора функций 5 произ водйтся по сигналам и . Поэтому к концу j-ro такта кодирования (при ) вычислительный блок 15 вырабатывает сигнал ПЗО , если y2-cospj x2stn| j и ,-если y2cos-p34x2slrtjaj и сигнал П31 ( , если/ y2cospj|3 sInpj)H , если/х2-со8|)/х2-slnpj).. Следовательно, после п тактов второго преобразования на группе выходов 41 блока поразрядного кодирования 10 вырабатывается и начинается последний(п+Г)-и такт второго .преобразования, в котором блок управления 16 для генератора функций 5 вырабатывает сигналы П34 . Поэтому к концу преобразования на группе выходов 59 вычислительного блока 15. вырабатывается код F60 -r2-V2.54H(b2 + XacoSp2 В конце второго преобразования блок управления 16 генерирует И64 конца преобразования. Импульс И64 поступает на счетный вход триггера 67 и на выход для осуществления съема с преобразователя кодов р2 и г2.. В некото мй момент после окончания И 64 триггер 67 переключается в О На этом цикл второго преобразования заканчивается, а следующий цикл начинается с приходом очередного И23. Длительность цикла второго преобразования на периоде составляет + -)Т-СИ + Л(Г6Т) (19). Как отмечалось, второе преобразование может также проводиться на периоде Тцх/ т.е. одновременно с формированием раз вертки. Отличие в выполнении в.торого преобразования на периоде Т от выполнения его на периоде foj заключается в том,, что за время до окончания очередного те -/сущего цикла развертки Т , не , чем Т, с выхода 37 блока управ-, ления 16 снимается импульс с окончания некотороготакта второго вычисления. По И37 на преобразователь поступает сигнал и очередной Й22, который устанавливает триггер 65 в 1. Триггер 65 состоянием 1 ПРОИЗВОДИТ прерывание в выполнении второго преобразования и осуществляет в преобразователе первое преобразование по полным кодам т.е. по коду р) и. коду г (q+1) к моменту окончания q-ro цикла Т развертки. В момент окончания q-ro цикла Т,, развертки множительный блок 11 генерирует И26, по которому блок управления 16 переводит преобразова тель на формирование Cq+D-ro.цикл развертки, т.е. генерирует И32 и И36. В блоке управления 16 по каждо му Й32, если триггер 65 находится в 1., триггер 66 устанавливается в 1. Триггеры 66 и 67 СОСТОЯНИЯМИ 1 разрешают прохождение на счетный вход триггера 65 очередного импульса ИбЗ, который во времени как совпадать, так и не совпада с И26, После окончания импульса на счетном входе триггера 65, триггер 65 переключается в О и разрешает продолжение выполнения второго преобразования. В зависимости от соотношения меж ду Т и Т между прерываниями происх дит выполнение не менее трех тактов второго преобразования 17, после чего по соответствующему И37 производится очередное прерывание второго преобразования для выполнения, перехода по И26 к следующему циклу fy формирования развертки и . При применении предлагаемой спос реализуется преимущественно для Поэтому произведем для сравнение быстродейстзвия заявляемого преобразователя с известным получаем их протуи и ПХ VYIIH J прет (21) ,Т2прот /12 64 (22 -„ Следовательно, сравниваемые объекты имеют одинаковое быстродействи при форьшровании развертки 20, а пр преобразованиях по полным кодам коо динат заявляемый преобразователь им ет примерно в 64 раза более высокое быстродействие, чем известный. При реализации сравниваемых объектов дл , например на базе цифровых:, гликросхем серии 133, объем оборудования предлагаемого преобразователя примерно в 1,5 раза больше, чем объ ем оборудования известного. . Формула изобретения 1. Цифровой преобразователь-коорд нат, содержащий первый и второй датчики полярных координат, первый коммутатор, генератор СИНУСНО-косинусных функций, блок управления, первый и второй датчики прямоугольных коорди нат, первый и второй множительныеблоки, первый и второй регистры разверток, блок поразрядного кодирования и сумматор, причем выходы блока поразрядного кодирования соединены с первой - группой входов первого коммутатора, вторая группа входов которого соединена с выходами первого датчика пО лярнкх координат, выходы первого коммутатора соединены с группой входов генератора синусно-косинусных функций, первая и вторая группы выходов которого, соединены с первыми группами входов соответственно первого и второго множительных блоков, управляющий вход первого коммутатора является входом преобразователя, отличающийся тем, что, с целью повышения быстродействия, в него введены второй и третий коммутаторы и вычислительный блок, причем установочный, тактовый, первый и второй управляющий входы блока управления являются входами преобразователя, первый, второй, третий и четвертый входы блока управления соединены, соответственно с синхронизирующим выходом первого множительного блока, первым, вторым и третьим управляющими выходами блока поразрядного кодирования, пятый и шестой входы блока управления соединены с первым и вторым управляющими выходами вычислительного блока, первый и второй входы запуска блока управления, являются входами преобразователя, второй вход запуска блока управления соединен с установочным входом блока поразрядного кодирования, первый выход блока управления соединен с cyviMKрующим входом второго датчика полярных координат, управляющий вход кото-рого является входом преобразователя, второй выход блока управления соединен с управляющими входами второго и третьего коммутаторов, третий; выход блока управления соедиЕ ен с первым управляющим входом генератоо ра синусно-косинус ных функций и уЩгав;ляющими входами первого и второго множительных блоков, четвертыг выход .блока управления соединен со вторым управляющим входом генератора синуснокосинусных функций, пятый выход блока управления соединен с входами записи первого и второго регистров развертки, шестой, седьмой и восьмой выходы блока управления соединены , ь соответственно .с входом импульса конца кодирования, входом импульса уменьшения кода и входом импульса увеличения кода блока поразоядного кодирования, девятый и десятый выходы блока управления являются выходами преобразователя, первый и второй знаковые выходы генератора синусно-косинусных функций соединены со знаковыми входами соответственно первого и второго регистров развертки, суммирующие входы которых соединены с число- импульсными входами соответственно первого и второго множительных блоков, синхронизирукячий выход второго множительного блока является выходом преобразователя, выходы второго датчика полярных координат соединены с первыми группами входов второго и третьего коммутаторов, вторые группы

входов которых соединены с выходами первого и второго датчиков прямоугол ных координат соответственно,знаковы выход первого датчика прямоугольных координат соединен с первыми входами блока поразрядного кодирования и сумматора вторые входы которых соединены со знаковым выходом второго датчика прямоугольных координат и выходом сумматора соответственно, выходы второго и третьего коммутаторов соединены со вторыми группами входов первого и второго.множительных блоков соответственно, тактовые и установочные, входа которых объединены и являются тактовым и установочным входами преобразователя, выходы первого множительного блока соединены с входами первого регистра развертки и первой группой входов вычислительного блока, вторая группа входов которого соединена с выходами БТОрого множительного блока и.входами второго регистра развертки, выходы первого и второго регистров развертки, вычислительного блока и первого и второго множительных блоков являются выходами преобразовате™ ля.

2. Преобразователь по п, 1, о т л. ичающийся тем, что блок управления содержит два элемента 2И-ИЛИ, элемент ЗИ-ИЛИ, три триггера, сумматор по модулю два и десять элементов И, причем установочный вход блока управления соединен с первым входом первого элемента 2И-ИЛИ, второй вход которого соединен с. вьксодом первого триггера и первым входом первого элемента И, выход которого является первым выходом блока управления и соединен с первым входом элемента ЗИ-ИЛИ и первым и вторым входами второго элемента 2И-ИЛИ,третий и четвертый входы которого соединены с первым управлякицим входом блока управления и выходом второго триггера, первый вход которого соединен с выходом первого элемента 2И-ИЛИ, первым выходом блока управления и вторым входом элемента ЗИ-ИЛИ, третий и четвертый вход которого соединены со вторым управляющим входом блока управления, тактовый вход которого соединен со вторым входом первого элемента И и первым входом второго элемента И, второ вход которого соединен со входом третьего элемента И, первым входом четвертого элемента К, вторым выходом блока управления и выходом пятого элемента И, первый вход которого соединен с вторым входом второго триггера и инверсным выходом первого триггера, тактовый вход которого соединен с выходом второго элемента 2И-ИЛИ, пятый и шестой входы которого соединены с выходом третьего триггера и вторым входом пятого элемента И, первый вход запуска блока управления соединен с входом первого триггера и инверсным входом первого элемента И, первый вход блока управления соединен с третьим входом первого элемента 2И-ИЛИ, пятый вход элемента ЗИ-ИЛИ соединен с третьим выходом блока управления и выходом четвертого элемента И, второй вход которого соединен с третьим входом блока управления, шестой вход элемента ЗИ-ИЛИ соединен с шестым выходом блока управления, выходом шестого элемента И, первым входом седьмого элемента И, выход которого соединен с первыми входами восьмого и девятого элементов И, вторые входы которых соединены с i ;входом сумматора по модулю два, вы-, ходы восьмого и девятого элементов И являются соответственно седькым и воськым выходами блока управления, десятый выход которого соединен с тактовым входом третьего триггера и выходом десятого элемента И, первы вход которого соединен с инверсным входом шестого элемента И,.инверсным входом третьего элемента И.и четвертым входом блока управления, пятый вход которого соединен со вторым входом седьмого элемента И, вход шестого элемента И соединен с выходом второго элемента И и вторым входом десятого элемента И, выход третьего элемента И является четвертым выходом блока управления, выходэлемента ЗИ-ИЛИ является пятым выходом блока управления, второй вход запуска блока управления соединен с входом третьего триггера, второй и шестой входы блока управления соединены с входами сумматора по модулю два.3. Преобразователь по п. 1, отличающийся тем, что вычислительный блок содержит два сумматора, группу элементов НЕ, элемент НЕ.и элемент ИЛИ, причем первая группа входов вычислительного блока соединена с первыми группами входов первого и второго сумматоров, вторая группа входов вычислительного блока соединена со второй группой входов первого сумматора и через группу элементов НЕ со второй груйпой 1 входов второго сумматора,выходы которого подключены к входам элемента ИЛИ выход которого является первым выходом вычислительного блока, группой выходов которого являются выходы первого сумматора, вход переноса второго сумматора соединен с выходом элемента НЕ и первым входом знака первого сумматора, второй вход знака которого соединен со входом элемента НЕ и входом логического нуля вычислителного блока, выход знака второго сумматора является вторым выходом вычислительнохо блока.Источники информации, принятые во внимание при экспертизе

1. Задубовский И.И., Красноголовый Б.Н, Цифровой генератор радиаль нс гхруговой развертки. ИзвестияВУЗОВ, Радиоэлектроника т. 17, 2, 1974.

2. Авторское свидетельство СССР по заявке 2513089/24, кл. G 06 F 15/20, 01.80.77. (прототип) .55

58

S2

In

Шина логического О

л

55

85

fpЗнр

Зн.р

31 пр

HL

30

S5

IP

8Ь

Перенос