(54) ЦИФРОВОЙ ГЕНЕРАТОР БАЗИСНЫХ ФУНКЦИЙ

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой генератор базисных функций | 1979 |

|

SU857961A1 |

| Устройство для разложения цифровых сигналов по Уолшо-подобным базисам | 1983 |

|

SU1108461A1 |

| Устройство отображения информации на экране телевизионного индикатора | 1986 |

|

SU1425768A1 |

| УСТРОЙСТВО ДЛЯ КОДИРОВАНИЯ ВИДЕОСИГНАЛА | 1992 |

|

RU2042202C1 |

| Имитатор цифрового телевизионногоСигНАлА | 1978 |

|

SU815966A1 |

| Устройство для отображения векторных диаграмм на экране электронно-лучевой трубки | 1988 |

|

SU1541663A1 |

| Генератор систем действительных базисных функций Аристова | 1988 |

|

SU1566334A1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 2000 |

|

RU2170444C1 |

| Устройство для отображения информации на экране цветного видеоконтрольного блока | 1988 |

|

SU1529280A1 |

| Генератор последовательности чисел | 1983 |

|

SU1166089A1 |

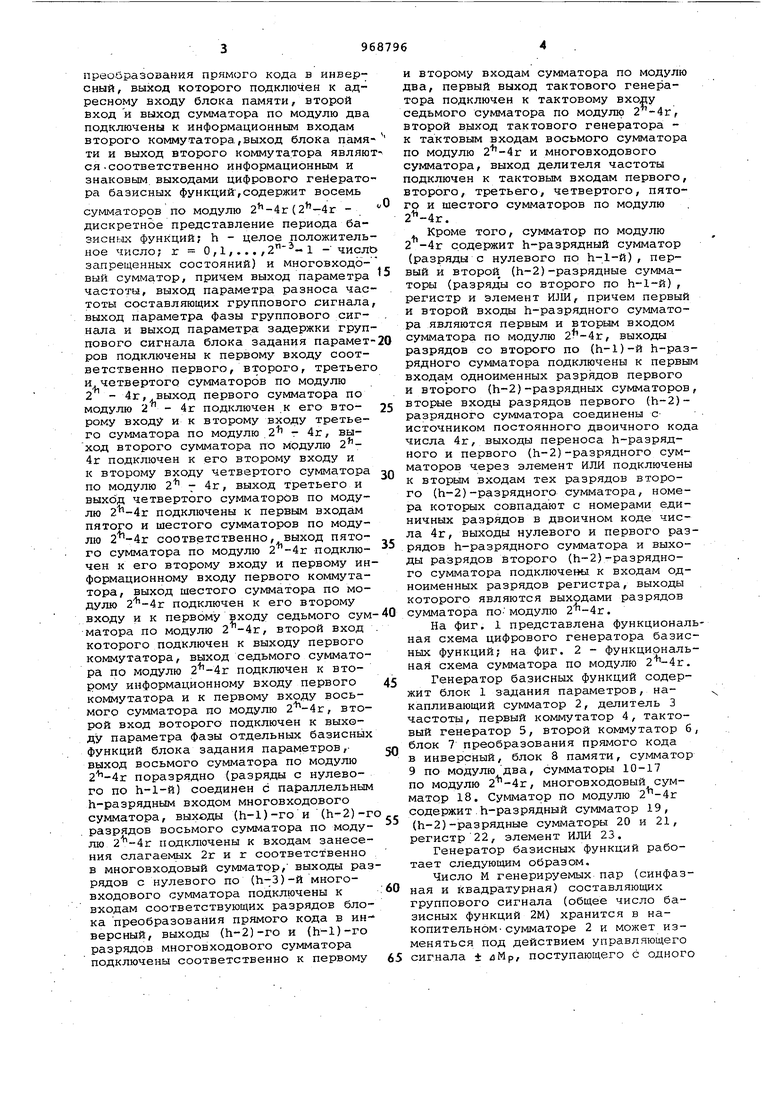

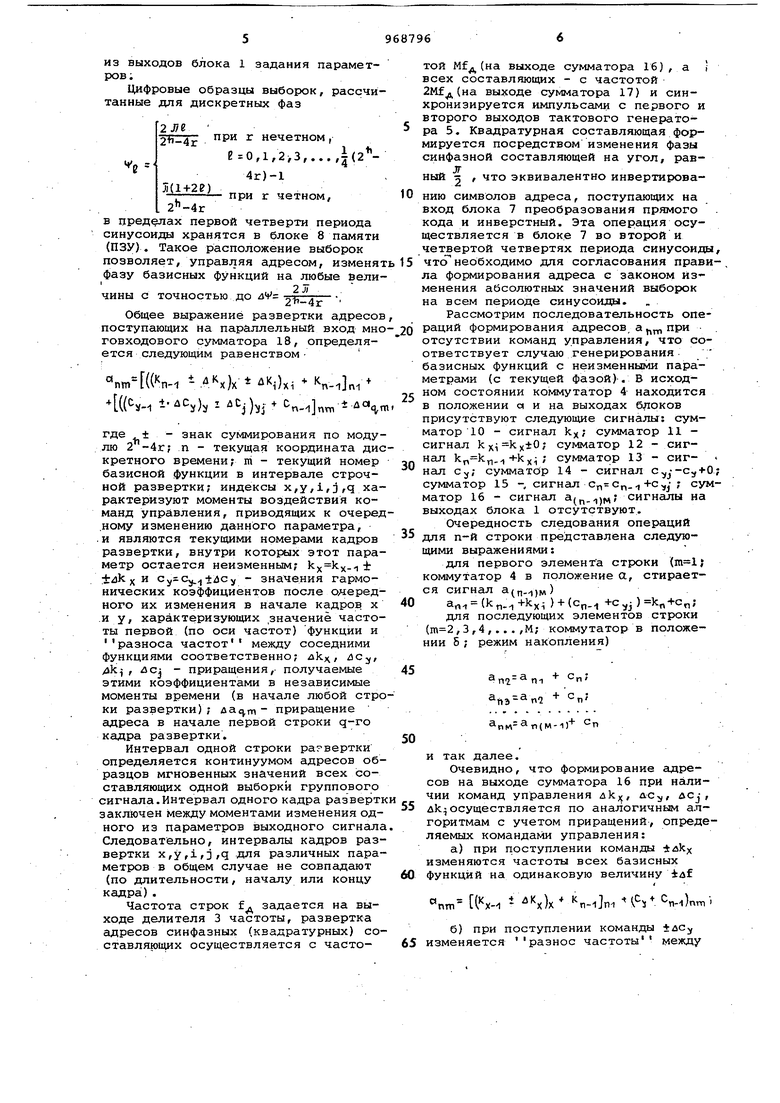

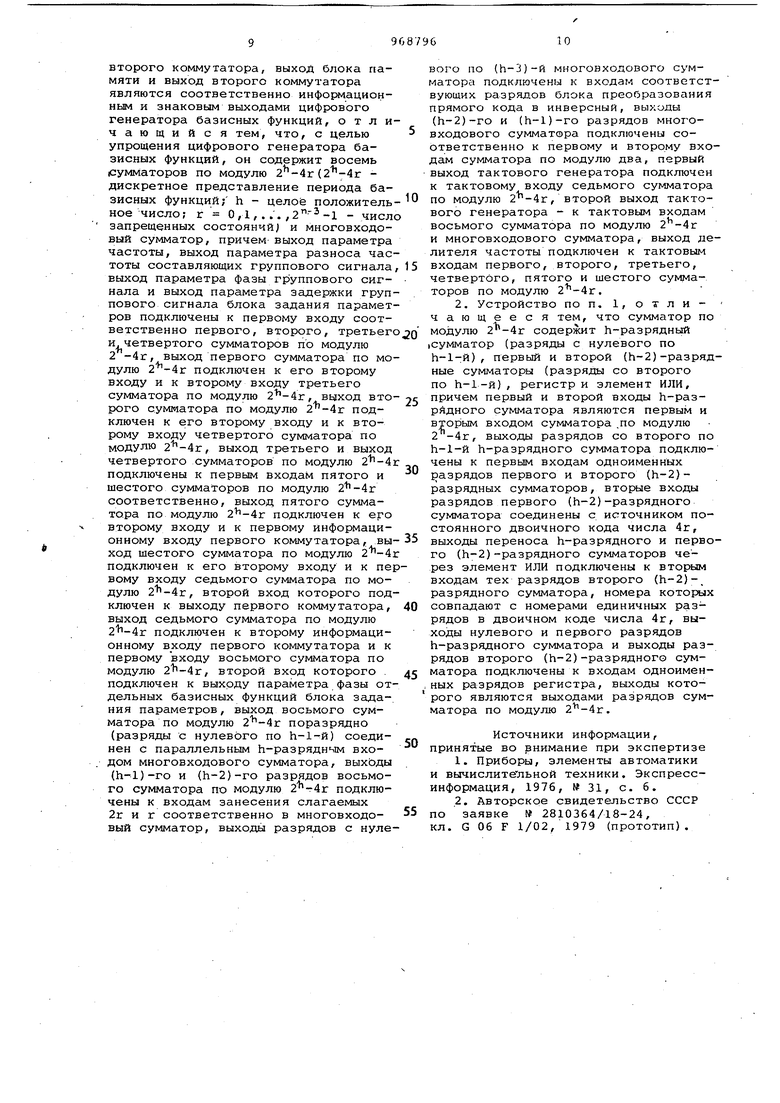

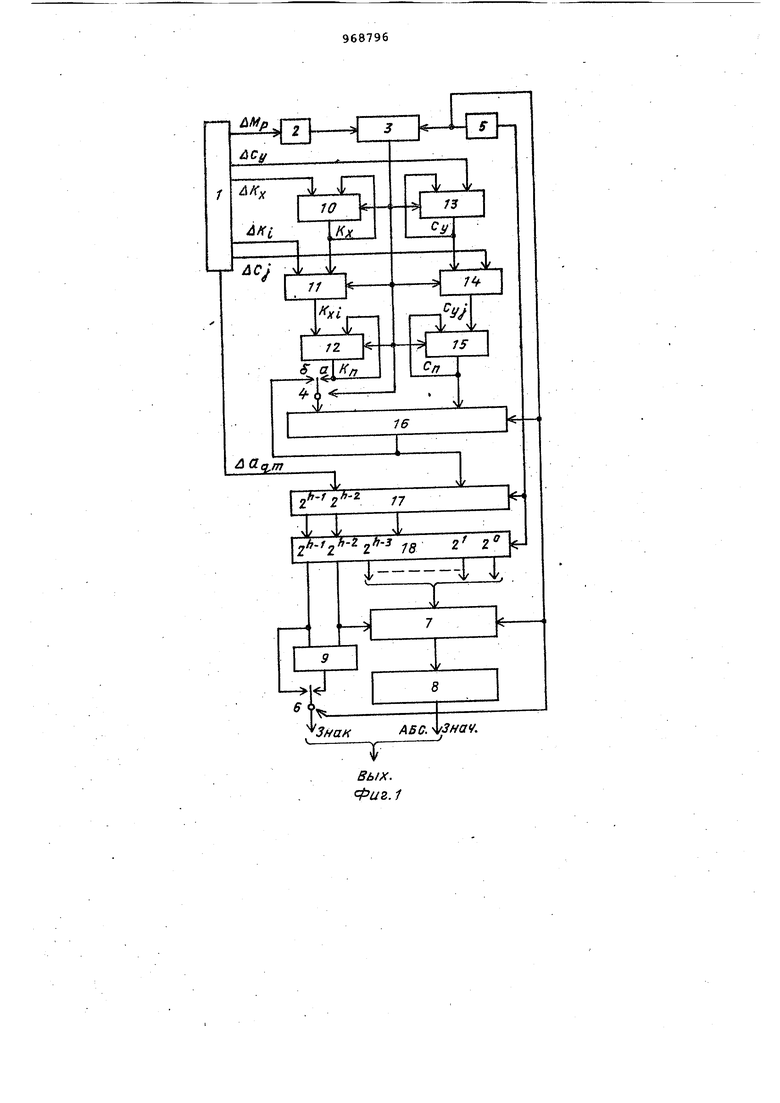

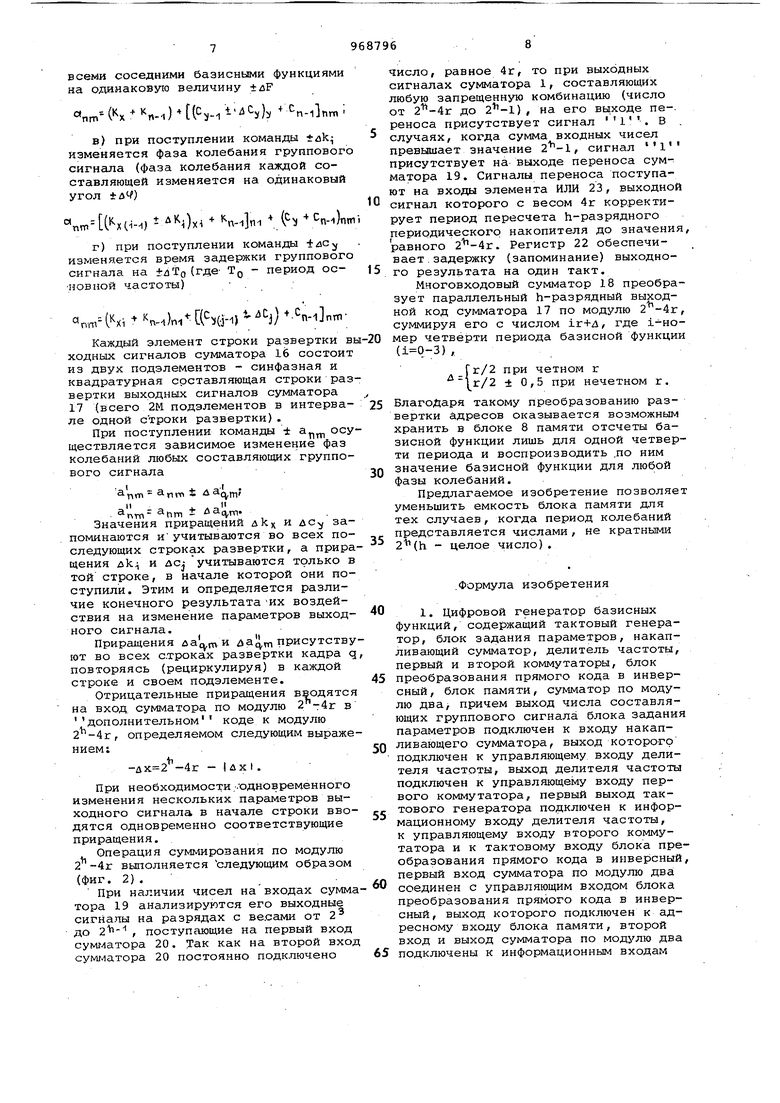

Изобретение относится к автоматике и вычислительной технике и может быть использовано в синтезаторах и анализаторах сложных сигналов различ ного назначения, в частности для формирования и обработки многочастот ных сигналов в многоканальных моделях или для формирования широкополосных сигналов с псевдослучайным за коном изменения его параметров. Известен цифровой генератор синусоидальнь1х колебаний, содержащий задающий генератор, счетчик, дешифратор и блок памяти. В этом генераторе блок памяти представлен постоянным: запоминающим устройством (ПЗУ) и пре назначен для хранения отсчетов синусоидального сигнала 1. Известен цифровой генератор базис ных функций, содержащий тактовый генератор, блок задания параметров, накапливающий сумматор/ делитель час тоты, блок преобразования прямого кода в инверсный, блок По1мяти, сумматор по модулю два и блок формирования адреса, состоящий из восьми су маторов по модулю 2 (h - целое положительное число)2J.. Недостаток известных генераторов состоит в том, что при генерировании базисных функций, с периодом , не Кра ным 2, необходимо хранить в блоке памяти отсчеты.базисной функций как минимум для половины ее периода и, таким образом, требуется блок памяти большой емкости. Целью изобретения является упрощение цифрового генератора базисных функций. Поставленная цель достигается тем, что цифровой генератор базисных функций, содержащий тактовый генератор, блок задания парметров, накапливеиощий. сумматор, делитель частоты, первый и второй коммутаторы, блок преобразованйя прямого кода в инверсный, блок памяти, сумматор по модулю два, причем выход числа составляющих группового сигнсша -блока задания параметров подключен к входу .накапливающего сумматора, выход которого подключен к, управляющему входу делителя частоты, выход делителя частоты подключен к управляющему входу первого коммутатора, первый выход тактово.го генератора подключен к информационному входу делителя частоты, к управляющему входу второго коммутатора и к тактовому входу блока преобразования прямого кода в инверсный, первый вход сумматора по модулю два соединен с управляющим входом блока прео-бразозания прямого кода в инверсный, выход которого подключен к адресному входу блока памяти, второй вход и выход сумматора по модулю два подключены к информационным входам второго коммутатора,выход блока памя ти и выход второго коммутатора являю ся .соответственно информационным и знаковым выходами цифрового гейерато ра базисных функций ,содержит восемь сумматоров по модулю ( дискретное представление периода базисньлх функций; h - целое положитель ное число; г О ,1,... , - числ запрещенных состояний) и многовходовый сумматор, причем выход параметра частоты, выход параметра разноса час тоты составляющих группового сигнала выход параметра фазы группового сигнала и выход параметра задержки груп пового сигнала блока задания парамет ров подключены к первому входу соответственно первого, второго, третьег и четвертого сумматоров по модулю 2 - 4г, выход первого сумматора по модулю 2 - 4г подключен ,к его второму входу и к второму входу третьего сумматора по модулю . 2 г 4г / выход второго сумматора по модулю подключен к его второму входу и к второму входу четвертого сумматора по модулю 2 - 4г, выход третьего и выход четвертого сумматоров по модулю подключены к первым входам пятого и шестого сумматоров по модулю соответственно, выход пятого сумматора по модулю 2 -4г подключен к его второму входу и первому ин формационному входу первого коммутатора, выход шестого сумматора по модулю подключен к его второму входу и к первому входу седьмого сум матора по модулю 2 -4г, второй вход которого подключен к выходу первого коммутатора, выход седьмого сумматора по модулю подключен к второму информационному входу первого коммутатора и к первому входу восьмого сумматора по модулю 2 -4г, второй вход воторого подключен к выходу параметра фазы отдельных базисных функций блока задания параметров,выход восьмого сумматора по модулю поразрядно (разряды с нулевого по h-1-й) соединен с параллельным h-разрядным входом многовходового сумматора, выходы (h-1)-го и (h-2)-г разрядов восьмого сумматора по модулю подключены к входам занесения слагаемых 2г и г соответственно в многовходовый сумматор, выходы раз рядов с нулевого по (Ь-З)-й многовходового сумматора подключены к входам соответствующих разрядов блока преобразования прямого кода в инверсный, выходы (h-2)-ro и (h-l)-ro разрядов многовходового сумматора подключены соответственно к первому и второму входам сумматора по модулю два, первый выход тактового генератора подключен к тактовому входу седьмого сумматора по модулю , второй выход тактового генератора к тактовым входам восьмого сумматора по модулю и многовходового сумматора, выход делителя частоты подключен к тактовым входам первого, второго, третьего, четвертого, пятого и шестого сумматоров по модулю . Кроме того, сумматор по модулю 2 -4г содержит h-разрядный сумматор (разряды с нулевого по h-.l-й) , первый и второй (h-2)-разрядные сумматоры (разряды со второго по h-1-й) , регистр и Элемент И}Ш, причем первый и второй входы h-разрядного сумматора являются первым и вторьам входом сумматора по модулю , выходы разрядов со второго по (Ь-1)-й h-разрядного сумматора подключены к первым входам одноименных разрядов первого и второго (h-2)-разрядных сумматоров, вторые входы разрядов первого (h-2)разрядного сумматора соединены систочником постоянного двоичного кода числа 4г, выходы переноса h-разрядного и первого (h-2)-разрядного сумматоров через элемент ИЛИ подключены к вторым входам тех разрядов второго (h-2)-разрядного сумматора, номера которых совпадают с номерами единичных разрядов в двоичном коде числа 4г, выходы нулевого и первого разрядов h-разрядного сумматора и выходы разрядов второго ()-разрядного сумматора подключены к входам одноименных разрядов регистра, выходы которого являются выходами разрядов сумматора по-модулю . На фиг, 1 представлена функциональная схема цифрового генератора базисных функций; на фиг. 2 - функциональная схема сумматора по модулю . Генератор базисных функций содержит блок 1 задания параметров, накапливающий сумматор 2, делитель 3 частоты, первый коммутатор 4, тактовый генератор 5, второй коммутатор б, блок 7 преобразования прямого кода в инверсный, блок 8 памяти, сумматор 9 по модулю два, сумматоры 10-17 по модулю , многовходовый сумматор 18, Сумматор по модулю содержит,h-разрядный сумматор 19, (h-2)-разрядные сумматоры 20 и 21, регистр 22, элемент ИЛИ 23, Генератор базисных функций работает следующим об ра 3 ом. Число М генерируемых пар (синфазная и квадратурная) составляющих группового сигнала (общее число базисных функций 2М) хранится в накопительном- сумматоре 2 и может изменяться под действием управляющего сигнала ± лМр, поступающего с одного из выходов блока 1 задания параметров;Цифровые образцы выборок, рассчитанные для дискретных фаз 2Лг . при г нечетном, ,1,,...,|()-1 ji(l+2g) при г четном. в пределах первой четверти периода синусоиды хранятся в блоке 8 памяти (ПЗУ). Такое расположение выборок позволяет, управляя адресом, изменя фазу базисных функций на любые вели чины с точностью до 211-4г Общее выражение развертки адресов поступающих на параллельный вход мно говходового сумматора 18, определяется следующим равенством«nm №n-l i ..S)x Ki)xi ViJaV + ((t,., 1.ДС,), I ЛС.). С„.,„.±.ас. где ± - знак суммирования по моду лю 2 -4г; п - текущая координата дис кретного времени; m - текущий номер базисной функции в интервале строчной развертки; индексы х,у,i,j,q характеризуют моменты воздействия команд управления, приводящих к очеред .ному изменению данного параметра, .и являются текущими номерами кадров развертки, внутри которых этот параметр остается неизменным; kj(kx. ± +,3k х и ,j.t4Cy - значения гармонических коэффициентов после очередного их изменения в начале кадров х .и у, характеризующих .значение частоты первой (по оси частот) функции и разноса частот между соседними функциями соответственно; o.Y., лс-у, xik , Cj - приращения, получаемые этими коэффициентами в независимые моменты времени (в начале любой стро ки развертки) ; приращение адреса в начале первой строки q-ro кадра развертки. Интервал одной строки рагвертки определяется континуумом адресов образцов мгновенных значений всех составляющих одной выборки группового сигнала.Интервал одного кадра разверт заключен между моментами изменения одного из параметров выходного сигнала Следовательно, интервалы кадров развертки x,y,i,j,q для различных параметров в общем случае не совпадают (по длительности, началу или концу кадра). Частота строк f задается на выходе делителя 3 частоты, развертка адресов синфазных (квадратурных) со ставляющих осуществляется с частотой (на выходе сумматора 16), а i всех составляющих - с частотой 2М(на выходе сумматора 17) и синхронизируется импульсами с первого и второго выходов тактового генератора 5. Квадратурная составляющая формируется посредством изменения фазы синфазной составляющей на угол, равный -х , что эквивалентно инвертированию символов адреса, поступающих на вход блока 7 преобразования прямого кода и инверстный. Эта операция осуществляется в блоке 7 во второй и четвертой четвертях периода синусоиды, что необходимо для согласования правила формирования адреса с законом изменения абсолютных значений выборок на всем периоде синусоиды. Рассмотрим последовательность операций формирования ащресов, а при отсутствии команд управления, что соответствует случаю генерирования базисных функций с неизменньми параметрами (с текущей фазой)-, В исходном состоянии коммутатор 4 находится в положении а и на выходах блоков присутствуют следующие сигналы: сумматор 10 - сигнал kx; сумматор 11 сигнал kxi kx±0; сумматор 12 - сигнал .-t-k ; сумматор 13 - сигНсш с,; сумматор 14 - сигнал .,+-0; сумматор 15 -, сигнсш ,+С.,У ; сумматор 16 - сигнал a. сигналы на выходах блока 1 отсутствуют. Очередность следования операций для п-й строки представлена следующими выражениями: для первого злемента строки ( коммутатор 4 в положение а, стирается сигнал а(п-1)м) , (kn.+kx ) + (Cn.i +c.,j) для последующих элементов строки (,3,4,...,М; коммутатор в положении 5; режим накопления) га П1 -а„1 + (М-1) Т и так далее. Очевидно, что формирование с1дресов на выходе сумматора 16 при наличии команд управления uk, дс,у, лсj , Ak осуществляется по аналогичным алгоритмам с учетом приращений, определяемых командами управления: а)при поступлении команды изменяются частоты всех базисных функций на одинаковую величину idf «пш (Vi )х n-.Jm MS Cn.i)nn.-. б)при поступлении команды ±лсу изменяется разнос частоты между всеми соседними базисными функциями на одинаковую величину ±лР «пт-- (Ч -i) (S-1 n-ilnn, ; в)при поступлении команды изменяется фаза колебания групповог сигнала (фаза колебания каждой составляющей изменяется на одинаковый угол ±лЮ пп. (() Мп-. г (S rCn-iW г)при поступлении команды -tuCy изменяется время задержки групповог сигнала на ±лТо (где- TQ - период основной частоты) ,.(К„ К„.,)„,(С,,(.,, t4C) С„.,„„. Каждый элемент строки развертки в ходных сигналов сумматора 16 состои из двух подэлементов - синфазная и квадратурная составляющая строки ра вертки выходных сигналов сумматора 17 (всего 2М подэлементов в интерва ле одной строки развертки). При поступлении команды ± а осу ществляется зависимое изменение фаз колебаний любых составляющих группо вого сигнала nn м -ап„ ± ла rvm Значения приращений дКх и дс за поминаются иучитываются во всех по следующих строках развертки, а прира щения ik и лс учитываются только в той строке, в начале которой они по ступили. Этим и определяется различие конечного результата их воздействия на изменение параметров выходного сигнала. Приращения и и а J присутству ют во всех строках развертки кадра q повторяясь (рециркулируя) в каждой строке и своем подэлементе. Отрицательные приращения вводятс на вход сумматора по модулю 2 -4г в дополнительном коде к модулю 2 -4г, определяемом следующим выраже нием; - |лх1. При необходимости ..одновременного изменения нескольких парс1метров выходного сигнала в начале строки вводятся одновременно соответствующие приращения. Операция суммирования по модулю 2 -4г выполняется следующим образом (фиг. 2) . При наличии чисел на входах сумма тора 19 анализируются его выходные сигналы на разрядах с весами от 2 до f поступающие на первый вход сумг атора 20. Так как на второй вход сум1/1атора 20 постоянно подключено число, равное 4г, то при выходных сигналах сумматора 1, составляющих любую запрещенную комбинацию (число от до ) , на его выходе па-. реноса присутствует сигнал случаях, когда сумма входных чисел сигнал превышает значение присутствует на выходе переноса сумматора 19, Сигналы переноса поступают на входы элемента ИЛИ 23, выходной сигнал которого с весом 4г кор.ректирует период пересчета h-разрядного периодического накопителя до значения, равного . Регистр 22 обеспечивает. задержку (запоминание) выходного результата на один такт. Многовходовый сумматор 18 преобразует параллельный h-разрядный выходной код сумматора 17 по модулю , суммируя его с числом ir+д, где i-номер четверти периода базисной функции () , Г г/2 при четном г г:/2 ± 0,5 при нечетном г. Благодаря такому преобразованию развертки адресов оказывается возможным хранить в блоке 8 памяти отсчеты базисной функции лишь для одной четверти периода и воспроизводить .по ним значение базисной функции для любой фазы колебаний. Предлагаемое изобретение позволяет уменьшить емкость блока памяти для тех случаев, когда период колебаний представляется числами, не кратными 2(h - целое число). .Формула изобретения 1. Цифровой генератор базисных функций, содержащий тактовый генератор, блок задания параметров, накапливающий сумматор, делитель частоты, первый и второй коммутаторы, блок преобразования прямого кода в инверсный, блок памяти, сумматор по модулю два, причем выход числа составляющих группового сигнала блока задания параметров подключен к входу накапливающего сумматора, выход которого подключен к управляющему входу делителя частоты, выход делителя частоты подключен к управляющему входу первого коммутатора, первый выход тактового генератора подключен к информационному входу делителя частоты, к управляющему входу второго коммутатора и к тактовому входу блока преобразования прямого кода в инверсный, первый вход сумматора по модулю два соединен с управляющим входом блока преобразования прямого кода в инверсный, выход которого подключен к адресному входу блока памяти, второй вход и выход сумматора по модулю два подключены к информационным входам второго коммутатора, выход блока памяти и выход второго коммутатора являются соответственно информационным и знаковым выходами цифрового генератора базисных функций, отли чающийся тем, что, с целью упрощения цифрового генератора базисных функций, он содержит восемь (Сумматоров по модулю ( дискретное представление периода базисных функций; h - целое положитель ное число; г О,1,..., - числ запрещенных состояний; и многовходовый сумматор, причем выход параметра частоты, выход параметра разноса частоты составляющих группового сигнала выход параметра фазы группового сигнала и выход параметра задержки группового сигнала блока задания параметров подключены к первому входу соответственно первого, второго, третьего и четвертого сумматоров по модулю 2 -4г, выход первого сумматора по мо дулю 2 -4г подключен к его второму входу и к второму входу третьего сумматора по модулю , вцход вто рого сумматора по модулю подключен к его второму входу и к второму входу четвертого сумматора по модулю , выход третьего и выход четвертого сумматоров по модулю подключены к первым входам пятого и шестого сумматоров по модулю соответственно, выход пятого сумматора по модулю подключен к его второму входу и к первому информационному входу первого коммутатора, вы ход шестого сумматора по модулю подключен к его второму входу и к пер вому входу седьмого сумматора по модулю , второй вход которого подключен к выходу первого коммутатора, выход седьмого сумматора по модулю 211-4г подключен к второму информационному входу первого коммутатора и к первому входу восьмого сумматора по модулю 2Ь-4г, второй вход которого . подключен к выходу параметра фазы отдельных базисных функций блока задания параметров, выход восьмого сумматора по модулю поразрядно (разряды с нулевого по h-1-й) соединен с параллельным Ь-разрядньм входом многовходового сумматора, выхЬды (h-l)-ro и (h-2)-ro разрядов восьмого сумматора по модулю подключены к входам занесения слагаемых 2г и г соответственно в многовходовый сумматор, выходы разрядов с нулевого по (Ь-З)-й многовходового сумматоре подключены к входам соответствующих разрядов блока преобразования прямого кода в инверсный, выходы (h-2)-ro и (h-l)-ro разрядов многовходового сумматора подключены соответственно к первому и второму входам сумматора по модулю два, первый выход тактового генератора подключен к тактовому входу седьмого сумматора по модулю , второй выход тактового генератора - к тактовым входам восьмого сумматора по модулю 2 -4г и многовходового сумматора, выход делителя частоты подключен к тактовым входам первого, второго, третьего, четвертого, пятого и шестого сумматоров по модулю . 2. Устройство по п. 1, отличающееся тем, что сумматор по модулю содержит h-разрядный (Сумматор (разряды с нулевого по h-1-й), первый и второй (h-2)-разрядные сумматоры (разряды со второго по h-1-й), регистр и элемент ИЛИ, причем первый и второй входы h-разрядного сумматора являются первым и вторым входом сумматора .по модулю 2 -4г, выходы разрядов со второго по h-1-й h-разрядного сумматора подключены к первым входам одноименных 15азрядов первого и второго (h-2)разрядных сумматоров, вторые входы разрядов первого (h-2)-разрядного сумматора соединены с источником постоянного двоичного кода числа 4г, выходы переноса h-разрядного и первого (h-2)-разрядного сумматоров через элемент ИЛИ подключены к вторым входам тех разрядов второго (h-2)- разрядного сумматора, номера которых совпадают с номерами единичных разрядов в двоичном коде числа 4г, выходы нулевого и первого разрядов h-разрядного сумматора и выходы разрядов второго (h-2)-разрядного сумматора подключены к входам одноименных разрядов регистра, выходы которого являются выходами разрядов сумматора по модулю . Источники информации, принятые во внимание при экспертизе 1.Приборы, элементы автоматики и вычислительной техники. Экспрессинформация, 1976, № 31, с. б. 2.Авторское свидетельство СССР по заявке 2810364/18-24, кл. G 06 F 1/02, 1979 (прототип).

ж

Знак

АБС.

г

Вь/х. Фиг.-/

Bx.l Bx.Z

Авторы

Даты

1982-10-23—Публикация

1980-10-29—Подача