(54) УСТРОЙСТВО ДЛЯ ОТОБРАЖЕНИЯ ОДНОКРАТНЫХ ПРОЦЕССОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для регистрации информации | 1980 |

|

SU953644A1 |

| Устройство для регистрации динамических процессов | 1988 |

|

SU1624437A1 |

| Устройство для отображения информации | 1979 |

|

SU888182A1 |

| Устройство для отображения радиолокационной информации на экране электронно-лучевой трубки | 1989 |

|

SU1691880A1 |

| Устройство для регистрации динамических процессов | 1989 |

|

SU1702358A1 |

| Устройство для регистрации аналоговых сигналов | 1980 |

|

SU911577A1 |

| Устройство для регистрации однократныхпРОцЕССОВ | 1978 |

|

SU842936A1 |

| ИНТЕГРИРУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1991 |

|

RU2012130C1 |

| Устройство отображения формы электрического сигнала | 1983 |

|

SU1151820A1 |

| Устройство для отображения однократных электрических сигналов | 1983 |

|

SU1141445A1 |

1

Изобретение относится к информационно-измерительной технике и может быть использовано для исс;гедования однократных электрических сигналов.

Известно устройство регистрации однократных сигналов, содержащее последовательно соединенные усилитель, аналого-цифровой преобразователь (АЦП), коммутатор, блок памяти и видеоконтрольный блок и блок управления 11.

Недостатком этого устройства является большая ек-ость памяти, необходимая для регистрации исследуемого сигнала с высокой точностью.

Наиболее близким к изобретению по технической сущности является устройство регистрации однократных сигналов, содержащее усилитель, АЦП, три блока памяти, блок вьаделения границ сообщения, коммутаторы, блок управления, видеоконтрольный блок, блок горизонтальной развертки и генератор тактовых импульсов. Это устройство позволяет автоматически выбирать длительность развертки, т.е. адаптироваться к длительности сигНс1ла 2 .

Недостатком устройства является большая погрешность регистрсщии за

счет потери высокочастотных составляющих между соседними отсчетами, взятыми через равные интервалы дискретизации .

Цель устройства - повыиение точности регистрации сигналов.

Указанная цель достигас- ся тем, что в устройство, содержащее усилитель, соединенный с блоком вьщелеtoния границ сообщения и аналого-цифровым преобразователем, подключенным к блоку управления и к генератору, первь1й блок памяти, подключенный к одному из входов блока отоб15ражения, к другому входу которого подключен первый счетчик, связанный с генератором, второй и третий блоки памяти и коммутатор, введены компаратор кодов, второй, третий и чет20вертый счетчики, схема сравнения, элемент ИЛИ и формирователь кода, причем вход компаратора кодов подключен к выходу аналого-цифрового преобразователя, а выходы подключены

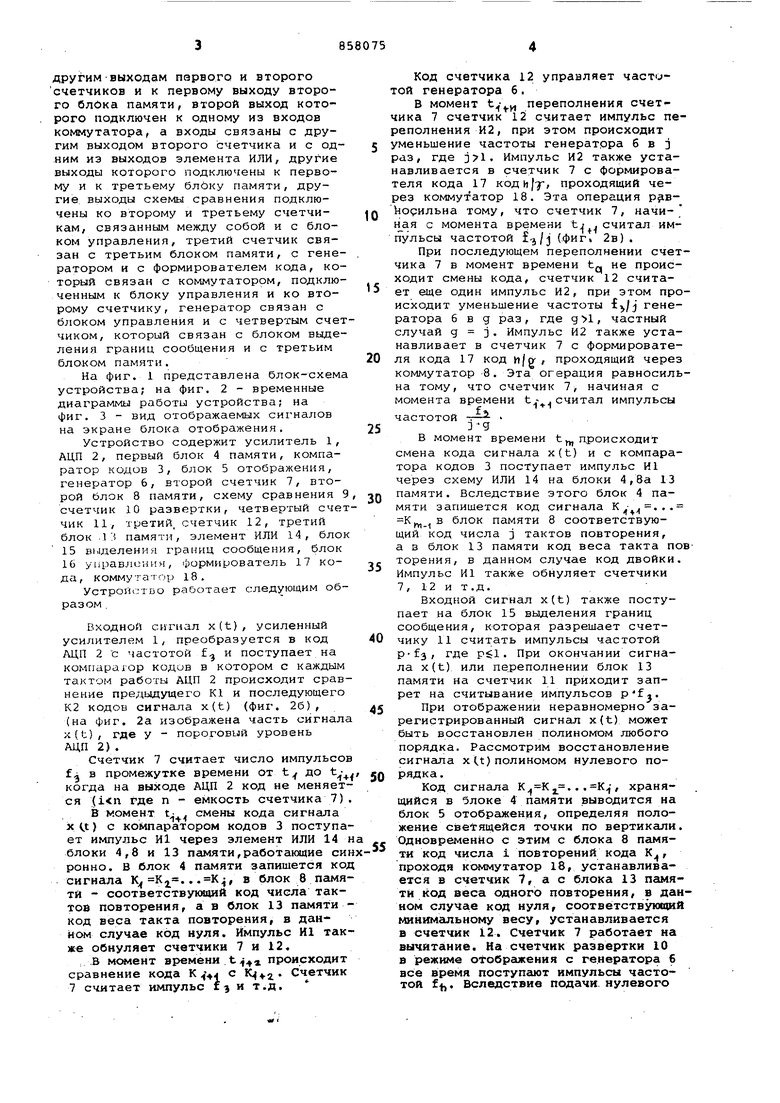

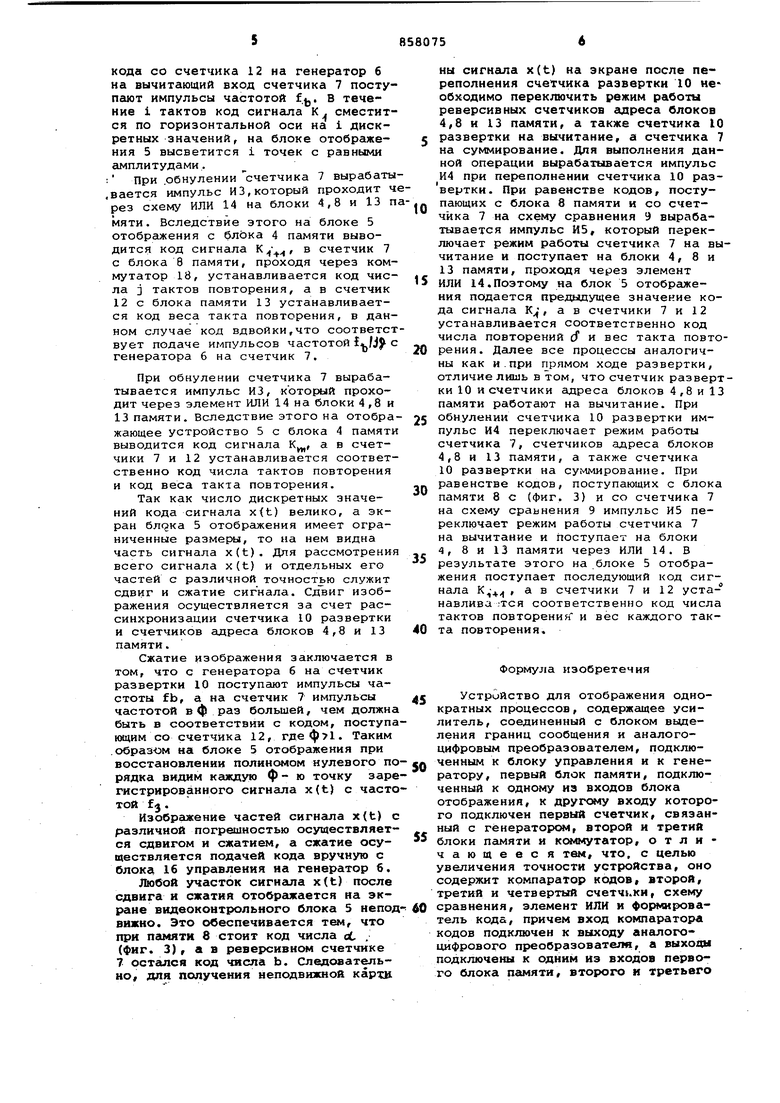

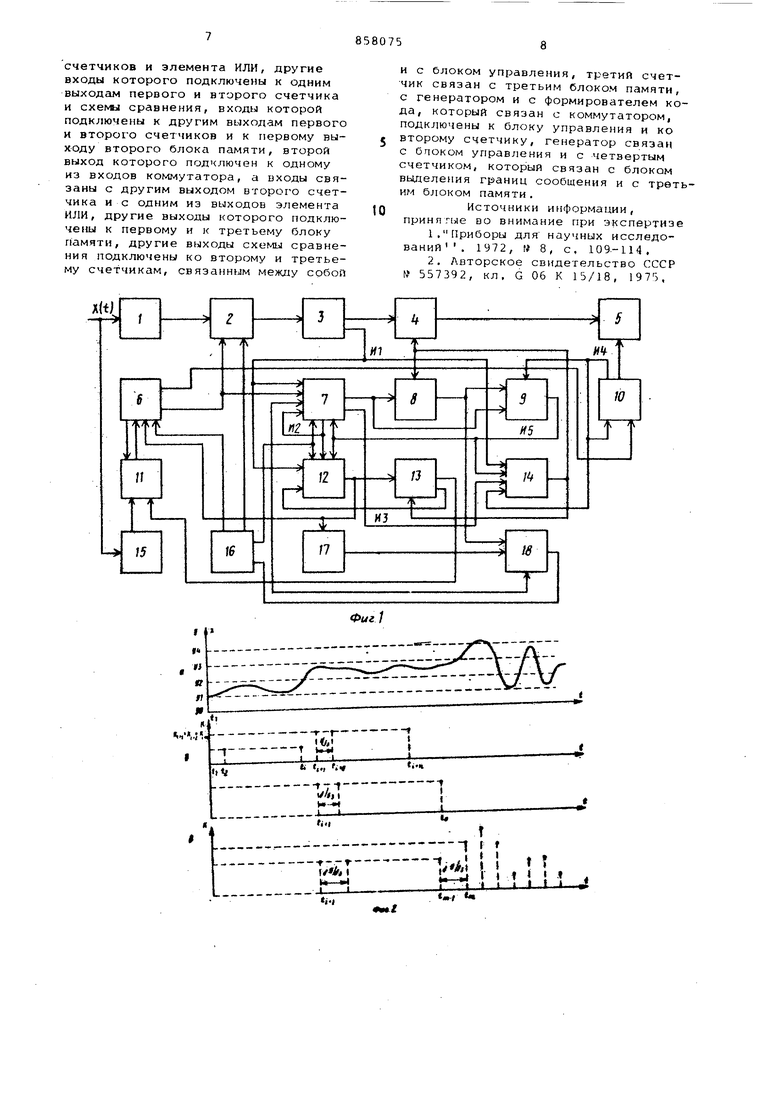

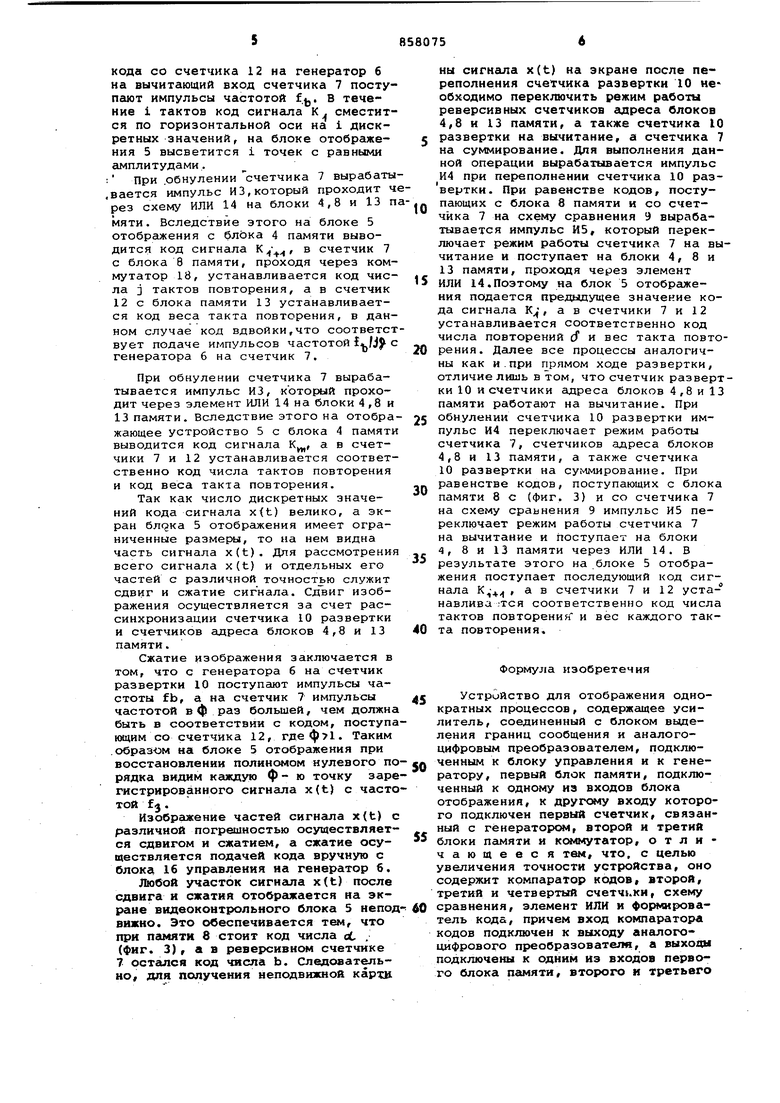

25 к одним из входов первого блока памяти, второго и третьего счетчиков и элемента ИЛИ, другие входы которого подключены к одним выходам первого и второго счетчика и схекы срав2Ю нения, входы которой подключены к другимВыходам парвого и второго счетчиков и к первому выходу второго блока памяти, второй выход которого подключен к одному из входов коммутатора, а входы связаны с другим выходом второго счетчика и с одним из выходов элемента ИЛИ, другие выходы которого подключены к первому и к третьему блоку памяти, другие выходы схемы сравнения подключены ко второму и третьему счетчикам, связанным между собой и с блоком управления, третий счетчик связан с третьим блоком памяти, с гене ратором и с формирователем кода, ко торый связан с коммутатором, подклю ченным к блоку управления и ко второму счетчику, генератор связан с блоком управления и с четвертым сче чиком, который связан с блоком выде ления границ сообщения и с третьим блоком памяти. На фиг. 1 представлена блок-схем устройства; на фиг. 2 - временные диаграммы работы устройства; на фиг. 3 - вид отображаемых сигналов на экране блока отображения, Устройство содержит усилитель 1, АЦП 2, первый блок 4 памяти, компаратор кодов 3, блок 5 отображения, генератор 6, второй счетчик 7, второй блок 8 памяти, схему сравнения счетчик 10 развертки, четвертый сче чик 11, третий, счетчик 12, третий блок .1 памяти, элемент ИЛИ 14, бло 15выделения границ сообщения, блок 16управленни, формирователь 17 кода, к омму т а т о i 18. Устро 1ство работает следующим об разом . Входной сигнал x(t), усиленный усилителем 1, преобразуется в код АЦП 2 с частотой f и поступает на компаратор кодов в котором с каждым тактом работы АЦП 2 происходит срав нение предыдущего К1 и последующего К2 кодов сигнала x(t) (фиг. 26), (на фиг, 2а изображена часть сигнал x.{t), где у - пороговый уровень АЦП 2) . Счетчик 7 считает число импульсо f в промежутке времени от t ДО t когда на выходе АЦП 2 код не меняет ся ( где п - емкость счетчика 7) IB момент t смены кода сигнала X (,t) с компаратором кодов 3 поступа ет импульс И1 через элемент ИЛИ 14 блоки 4,8 и 13 памяти,работакадие си ронно. В блок 4 naiMHTH запишется ко сигнала К Kj.. .К, в блок 8 памя ти - соответствукиций код числа такfos повторения, а в блок 13 пгиляти код веса такта повторения, в данном случае код иудя. Импульс И1 так же обиуляет счетчики 1 н 12. ,..В момент времени происходит сравнение кода К с Счетчик 7 считает импульс С и т.д. Код счетчика 12 управляет частоой генератора б. В момент переполнения счетика 7 счетчик 12 считает импульс пееполнения И2, при этом происходит меньшение частоты генератора б в j аз, где . Импульс И2 также устаавливается в счетчик 7 с формирователя кода 17 код h IT, проходящий через коммутатор 18. Эта операция pjiB орильна тому, что счетчик 7, начиная с момента времени t . считал импульсы частотой fj/3 (фиг. 2в) . При последующем переполнении счетчика 7 в момент времени tg не происходит смены кода, счетчик 12 считает еще один импульс И2, при этом происходит уменьшение частоты генератора 6 в g раз, где , частный случай g j. Импульс И2 также устанавливает в счетчик 7 с формирователя кода 17 код n/g , проходящий через коммутатор 8. Эта огерация равносильна тому, что счетчик 7, начиная с момента времени считал импульсы частотой -:- 3 g В момент времени t происходит смена кода сигнала x(t) и с компаратора кодов 3 поступает импульс И1 через схему ИЛИ 14 на блоки 4,8а 13 памяти. Вследствие этого блок 4 памяти запишется код сигнала ... блок памяти 8 соответствующий код числа 3 тактов повторения, а в блок 13 памяти код веса такта повторения, в данном случае код двойки. Импульс И1 также обнуляет счетчики 7 , 12 и т . д. Входной сигнал x(t) также поступает на блок 15 выделения границ сообщения, которая разрешает счетчику 11 считать импульсы частотой , где р$1. При окончании сигнала x(t) или переполнении блок 13 памяти на счетчик 11 приходит запрет на считывание импульсов pf.. При отображении неравномерно зарегистрированный сигнал x(t) может быть восстановлен полиномом любого порядка. Рассмотрим восстановление сигнала x(.t) полиномом нулевого порядка. Код сигнала j.. ., хранящийся в блоке 4 памяти выводится иа блок 5 отображения, определяя положение ев с я точки по вертикали. Одновременно с этим с блока 8 памяти код числа i повторений кода К,, проходя коммутатор 18, устанавливается в счетчик 7, а с блока 13 памяти код веса одного повторения, а данном случае код нуля, соответствующий минимальному весу, устанавливается в счетчик 12. Счетчик 7 работает на вычитание. На счетчик развертки 10 в режиме отобреикения с генератора 6 асе время поступают импульсы частотой f. Вследствие подачи нулевого кода со счетчика 12 на генератор б на вычитающий вход счетчика 7 поступают импульсы частотой f. В течение i тактов код сигнала К . сместится по горизонтальной оси на i дискретных значений, на блоке отобргикения 5 высветится i точек с равными амплитудами. : При обнулении счетчика 7 вырабаты .вается импульс ИЗ,который проходит ч рез схему ИЛИ 14 на блоки 4,8 и 13 п мяти. Вследствие этого на блоке 5 отображения с блока 4 памяти выводится код сигнала К в счетчик 7 с блока 8 памяти, проходя через коммутатор 18, устанавливается код чиспа j тактов повторения, а в счетчик 12с блока памяти 13 устанавливается код веса такта повторения, в данном случае код вдвойки,что соответст вует подаче импульсов частотой с генератора 6 на счетчик 7, При обнулении счетчика 7 вырабатывается импульс ИЗ, который проходит через элемент ИЛИ 14 на блоки 4 ,8 и 13памяти. Вследствие этого на отобра жающее устройство 5 с блока 4 памяти выводится код сигнала К, а в счетчики 7 и 12 устанавливается соответственно код числа тактов повторения и код веса такта повторения. Так как число дискретных значений кода сигнала ) велико, а экран бл(зка 5 отображения имеет ограниченные размеры, то на нем видна часть сигнала x(t). Для рассмотрени всего сигнала x(t) и отдельных его частей с различной точностью служит сдвиг и сжатие сигнала. Сдвиг изображения осуществляется за счет раесинхронизации счетчика 10 развертки и счетчиков адреса блоков 4,8 и 13 памяти. Сжатие изображения заключается в том, что с генератора б на счетчик развертки 10 поступгиот импульсы частоты fb, а на счетчик 7 импульсы частотой вф раз большей, чем должна быть в соответствии с кодом, поступа ющим со счетчика 12, гдеф71. Таким .образ-ом на блоке 5 отображения при восстановлении полиномом нулевого по рядка видим каждую ф- ю точку заре гистрированного сигнала x(t) с часто той f 3 . Изображение частей сигнгша x(t) с различной погрешностью осуществляется сдвигом и сжатием, а сжатие осуществляется подачей кода вручную с блокг1 16 управления на геиератор 6. Любой участок сигигша x(t) после сдвига и сжатия ото&ргикается иа экраие видеоконтрольного блока 5 иепод вижно. Это обеспечивается тем, что при памяти 8 стоит код числа сС . (фиг. 3), а в реверсивном счетчике 7 остался код числа Ь. Следовательно, для получения неподвижной карти ны сигнала x(t) на экране после переполнения счетчика развертки 10 необходимо переключить режим работы реверсивных счетчиков адреса блоков 4,8 и 13 памяти, а также счетчика LO развертки на вычитание, а счетчика 7 на суммирование. Для выполнения данной операции вырабатывается импульс И4 при переполнении счетчика 10 развертки. При равенстве кодов, поступающих с блока 8 памяти и со счетчика 7 на схему сравнения Э вырабатывается импульс И5, который переключает режим работы счетчика 7 на вычитание и поступает на блоки 4, 8 и 13 памяти, проходя через элемент ИЛИ 14.Поэтому на блок 5 отображения подается предвдцущее значение кода сигнала , а в счетчики 7 и 12 устанавливается соответственно код числа повторений cf и вес такта повторения. Далее все процессы аналогичны как и.при прямом ходе развертки, отличие лишь в том, что счетчик развертки 10 и счетчики адреса блоков 4 ,8 и 13 памяти работают на вычитание. При обнулении счетчика 10 развертки импульс И4 переключает режим работы счетчика 7, счетчиков адреса блоков 4,8 и 13 памяти, а также счетчика 10 развертки на суммирование. При равенстве кодов, поступающих с блока памяти 8 с (фиг. 3) и со счетчика 7 на схему сраьнения 9 импульс И5 переключает режим работы счетчика 7 на вычитание и Поступает на блоки -3, 8 и 13 памяти через ИЛИ 14. В результате этого на блоке 5 отображения поступает последующий код сигнала К144 а в счетчики 7 и 12 уста- навлива ;тся соответственно код числа тактов повторения и вес каждого такта повторения. Формула изобретения Устройство для отображения однократных процессов, содержащее усилитель, соединенный с блоком выделения границ сообщения и аналогоцифровым преобразователем, подключенным к блоку управления и к генератору, первый блок памяти, подключенный к одному из входов блока отображения, к другсму входу которого подключен первый счетчик, связанный с генератором, второй и третий блоки памяти и коммутатор, отличающееся тем, что, с целью увеличения точности устройства, оно содержит компаратор кодов, второй, третий и четвертый счетчики, схему сравнения, элемент ИЛИ и формирователь кода, причем вход компаратора кодов подключен к выходу аналоге- цифрового преобразователя, а выходы подключены к одИим из входов первого блока пгичяти, второго и третьего

счетчиков и элемента ИЛИ, другие входы которого подключены к одним выходам первого и второго счетчика и cxeivbj сравнения, входы которой подключены к другим выходам первого и второго счетчиков и к первому выходу второго блока памяти, второй выход которого подключен к одному из входов коммутатора, а входы связаны с другим выходом второго счетчика и с одним из вьлходов элемента ИЛИ, другие выходы которого подключены к первому и к третьему блоку памяти, другие выходы схемы сравнения подключены ко второму и третьему счетчикам, связанным между собой

и с блоком управления, третий счетчик связан с третьим блоком памяти, с генератором и с формирователем кода, который связан с коммутатором, подключены к блоку управления и ко второму счетчику, генератор связан с Споком управления и с четвертым счетчиком, который связан с блоком выделения границ сообщения и с третьим блоком памяти.

Источники информации, принягые во внимание при экспертизе

1,Приборы для научных исследований. 1972, W 8, с, 109--114.

2, Авторское свидетельство СССР № 557392, кл, G 06 К 15/18, 1975,

Отображающее устройство

tx

Ki

V

Авторы

Даты

1981-08-23—Публикация

1979-12-21—Подача