(5) УСТРОЙСТВО ДЛЯ РЕГИСТРАЦИИ ИНФОРМАЦИИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения мощности цилиндров двигателя внутреннего сгорания | 1990 |

|

SU1789898A1 |

| Тренажер радиотелеграфиста | 1983 |

|

SU1124369A1 |

| Устройство для контроля микропроцессорных блоков | 1988 |

|

SU1531099A1 |

| Устройство для автоматического измерения амплитудно-частотных характеристик | 1986 |

|

SU1379749A1 |

| Устройство для определения взаимной корреляционной функции | 1986 |

|

SU1361577A1 |

| Устройство для отображения однократных электрических сигналов | 1983 |

|

SU1141445A1 |

| Устройство для измерения угла закручивания вращающегося вала | 1991 |

|

SU1795312A1 |

| СПОСОБ ОПРЕДЕЛЕНИЯ ТЕХНИЧЕСКОГО СОСТОЯНИЯ ДВИГАТЕЛЕЙ ВНУТРЕННЕГО СГОРАНИЯ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2001 |

|

RU2208771C2 |

| СПОСОБ ФОРМИРОВАНИЯ СИГНАЛОВ МАГНИТОТЕРАПЕВТИЧЕСКОГО ВОЗДЕЙСТВИЯ И УСТРОЙСТВА ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1996 |

|

RU2090217C1 |

| Устройство для контроля работы оператора | 1990 |

|

SU1749904A1 |

1

Изобретение относится к информациioHHO-измерительной технике и может быть использовано для исследования однократных электрических процессов.

Известно устройство для регистрации однократных процессов, сЬдержащее последовательно соединенные усилитель, аналого-цифровой преобразователь (АЦП, -коммутатор, блок памяти и отображающее устройство, управляющие входы которых синхронизированы блоком управления ll.

Недостатком устройства является большая емкость памяти, необходимая для регистрации исследуемого процесса с большой точностью.

Наиболее близким к изобретению по технической сущности является устройство для регистрации однократных процессов , содержащее усилитель, АЦП, схему определения смены кода, три блока памяти, блок отображения, генератор управляемой частоты, схему

сравнения кодов, счетчик развертки, схему ИЛИ, четыре счетчика, схему выделения начала и конца сигналов, устройство управления, задатчик кода, коммутатор кода, связанные между собой определенным образом. Устройство позволяет сократить емкость памяти, необходимую для регистрации сигналов с высокой точностью. Это достигается записью кода сигнала, числа

10 повторений этого кода и веста такта повторений 2.

Однако эта точность регистрации понижается после того, как число повторений превышает максимальное зна15чение. Это связано с тем, что увеличивается вес такта повторений, т.е. увеличивается интервал дискретизации.

20

Целью изобретения является повышение точности устройства.

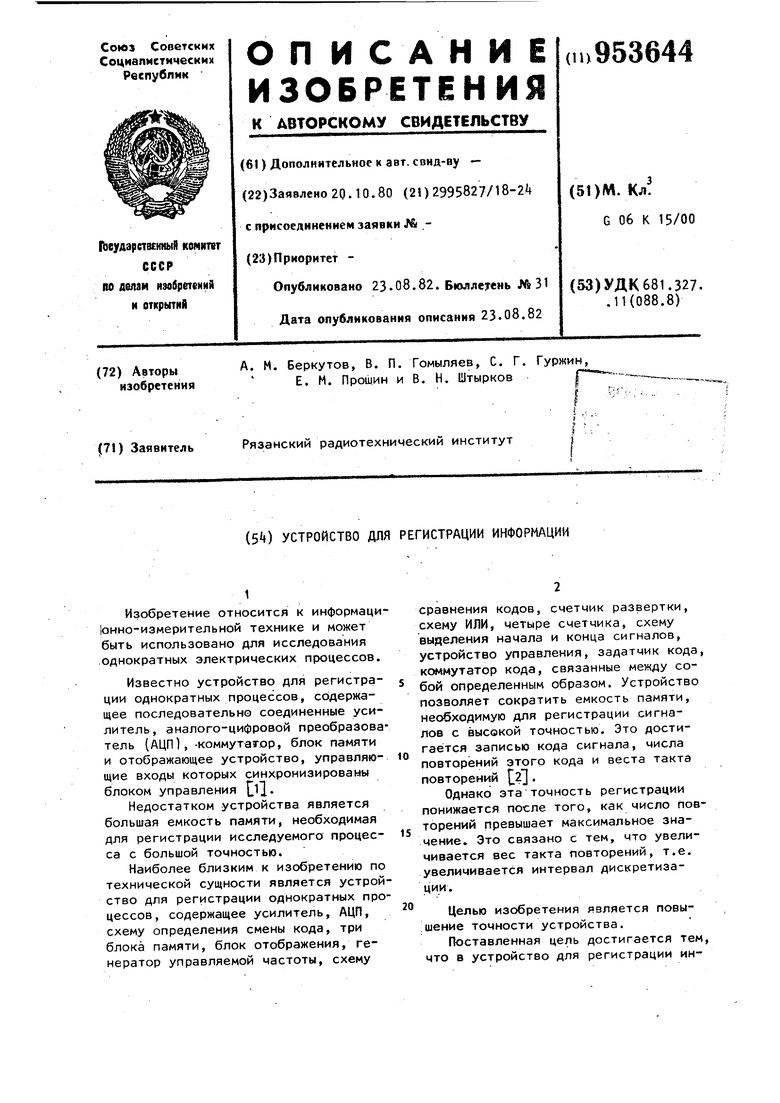

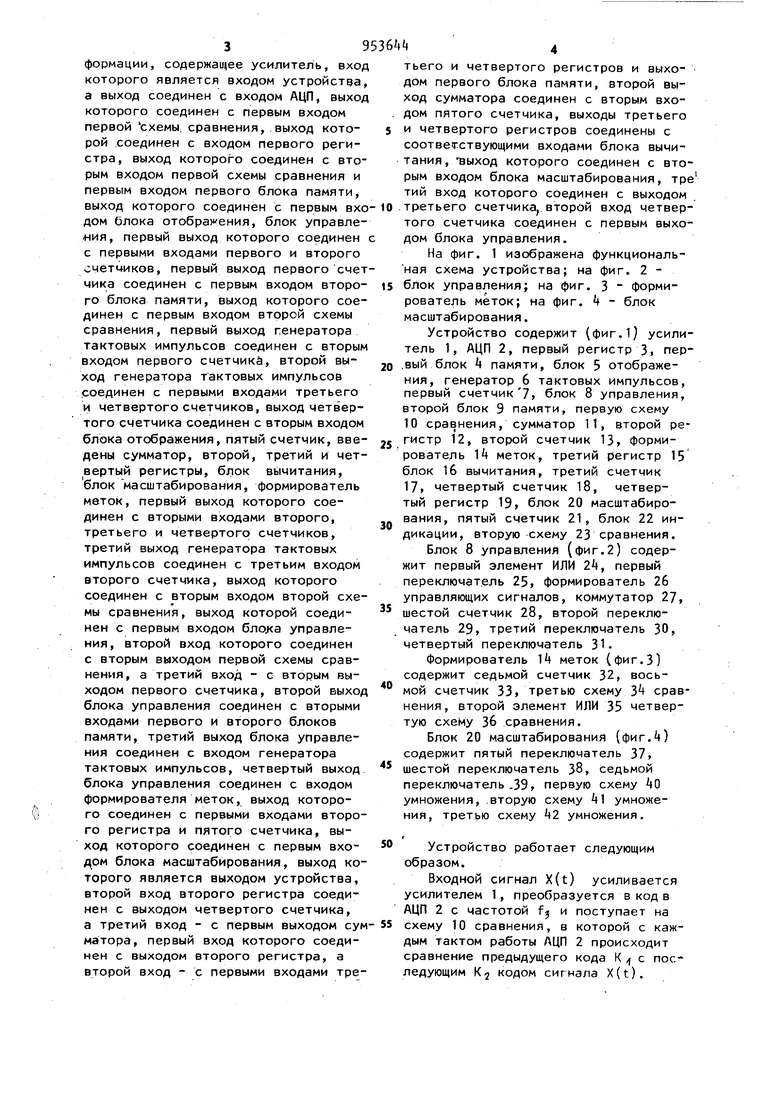

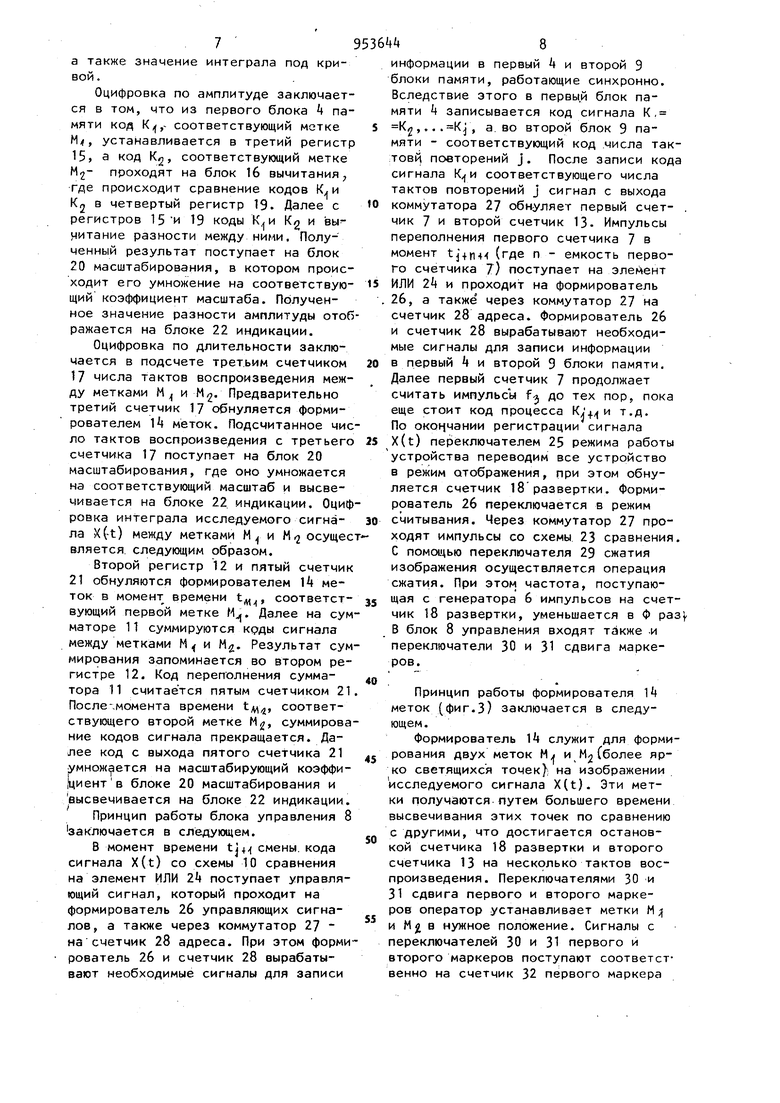

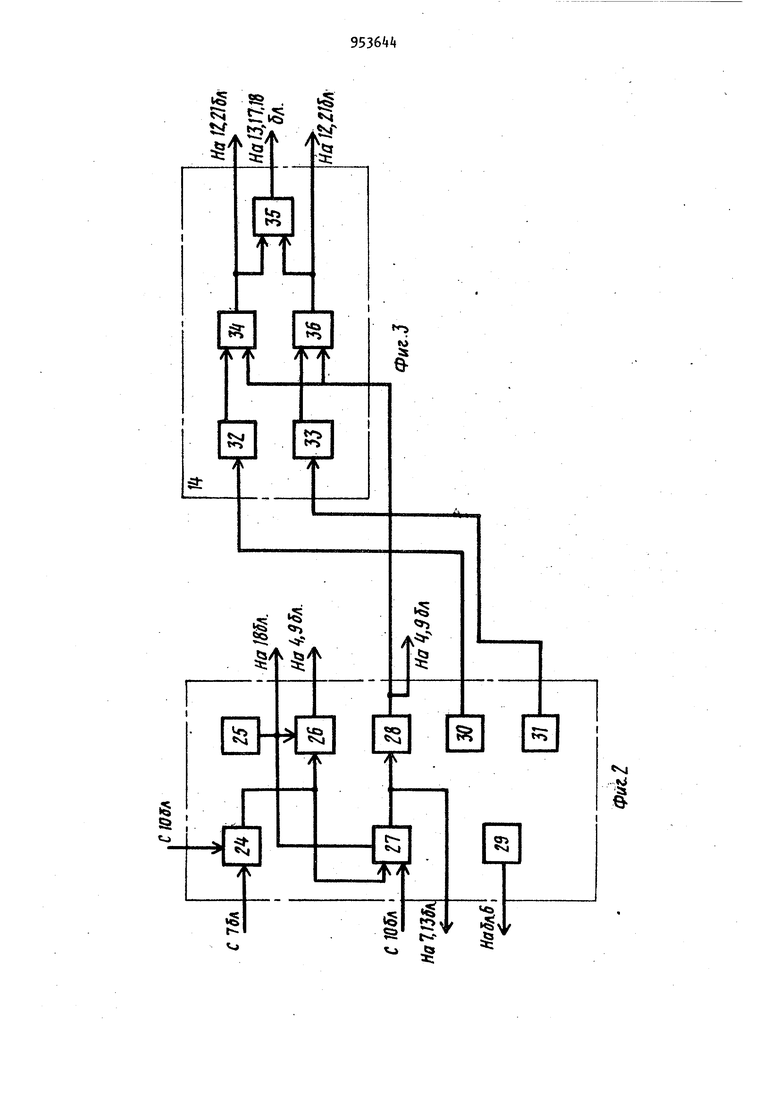

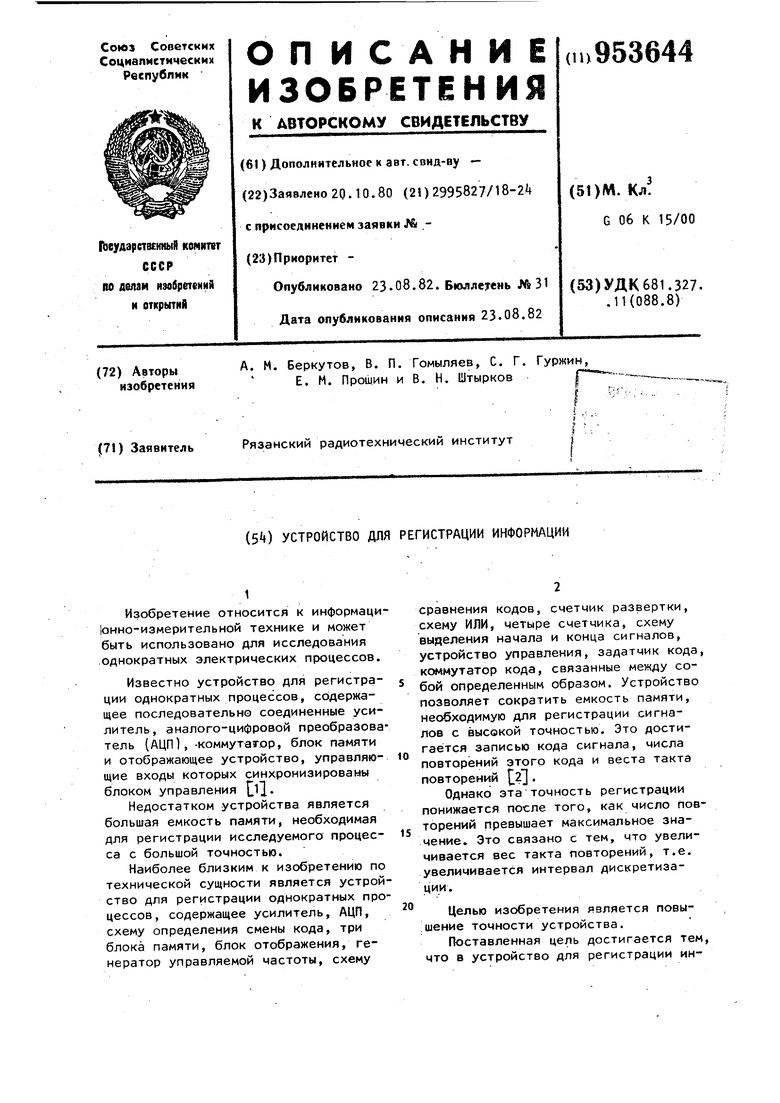

Поставленная цель достигается тем, что в устройство для регистрации ин395формации, содержащее усилитель, вход которого является входом устройства, а выход соединен с входом АЦП, выход которого соединен с первым входом первой схемы, сравнения, выход которой .соединен с входом первого регистра, выход которого соединен с вторым входом первой схемы сравнения и первым входом первого блока памяти. выход которого соединен с первым вхо дом блока отображения, блок управления, первый выход которого соединен с первыми входами первого и второго счетчиков, первый выход первого счет чика соединен с первым входом второго блока памяти, выход которого соединен с первым входом второй схемы сравнения, первый выход генератора тактовых импульсов соединен с вторым входом первого счетчика, второй выход генератора тактовых импульсов .соединен с первыми входами третьего и четвертого счетчиков, выход четвертого счетчика соединен с вторым входом блока отображения, пятый счетчик, введены сумматор, второй, третий и четвертый регистры, блок вйчитания, блок масштабирования, формирователь меток, первый выход которого соединен с вторыми входами второго, третьего и четвертого счетчиков, третий выход генератора тактовых импульсов соединен с третьим входом второго счетчика, выход которого соединен с вторым входом второй схемы сравнения, выход которой соединен с первым входом управления , второй вход которого соединен с вторым выходом первой схемы сравнения, а третий вход - с вторым выходом первого счетчика, второй выход блока управления соединен с вторыми входами первого и второго блоков памяти, третий выход блока управления соединен с входом генератора тактовых импульсов, четвертый выход блока управления соединен с входом формирователя меток, выход которого соединен с первыми входами второ го регистра и пятого счетчика, выход которого соединен с первым входом блока масштабирования, выход ко торого является выходом устройства, второй вход второго регистра соединен с выходом четвертого счетчика, а третий вход - с первым выходом су матора, первый вход которого соединен с выходом второго регистра, а второй вход - с первыми входами тре й тьего и четвертого регистров и выхо- дом первого блока памяти, второй выход сумматора соединен с вторым входом пятого счетчика, выходы третьего и четвертого регистров соединены с соответствующими входами блока вычитания, ВЫХОД которого соединен с вторым входом блока масштабирования, тре тий вход которого соединен с выходом третьего счетчика, второй вход четвертого счетчика соединен с первым выходом блока управления. На фиг. 1 изображена функциональная схема устройства; на фиг. 2 блок управления; на фиг. 3 - формирователь меток; на фиг. k - блок масштабирования. Устройство содержит (фиг.1} усилитель 1, АЦП 2, первый регистр 3i пер.вый блок h памяти, блок 5 отображения, генератор 6 тактовых импульсов, первый счетчик7, блок 8 управления, второй блок 9 памяти, первую схему 10 сравнения, сумматор 11, второй регистр 12, второй счетчик 13, формировате.ль Т меток, третий регистр 15 блок 16 вычитания, третий счетчик 17, четвертый счетчик 18, четвертый регистр 19, блок 20 масштабирования, пятый счетчик 21, блок 22 индикации, вторую схему 23 сравнения. Блок 8 управления (фиг.2) содержит первый элемент ИЛИ 2А, первый переключатель 25, формирователь 26 управляющих сигналов, коммутатор 27, шестой счетчик 28, второй переключатель 29, третий переключатель 30, четвертый переключатель 31. формирователь 1 меток (фиг.З) содержит седьмой счетчик 32, восьмой счетчик 33, третью схему З сравнения, второй элемент ИЛИ 35 четвертую схему Зб сравнения. Блок 20 масштабирования (фиг.) содержит пятый переключатель 37, шестой переключатель 38, седьмой переключатель ,39, первую схему 0 умножения, .вторую схему k умножения, третью схему k2 умножения. Устройство работает следующим образом. Входной сигнал X(t) усиливается усилителем 1, преобразуется в код в АЦП 2 с частотой fj и поступает на схему 10 сравнения, в которой с каждым тактом работы АЦП 2 происходит сравнение предыдущего кода К с пос ледующим К2 кодом сигнала X(t).

Счетчик 7 считает число импульсов f в промежутке времени от t до tj. , пока на входе ЛЦП2 код не меняется. В момент t Hсмены кода сигнала X(t) со схемы 10 сравнения на блок 8 управления поступает управляющий сигнал, под действием которого блок 8 управления вырабатывает сигналы, необходимые для записи информации в первый и второй 9 блоки памяти, работающие синхронно, следствие этого в первый блок k памяти записывается код сигнала i,...K,j, а во второй блок 9 памяти - соответствующий код числа тактов повторения j. После записи кода сигнала К и соответствующего числа повторений j блок 8 управления обнуляет счетчик 7.

В момент времени t;. происходит сравнение кодов Kj4 и К +2- Так как ( Kj+12, то счетчик 7 считает импульс f и т.д.

Импульс переполнения счетчика 7 в момент , (где п - емкость пер.вого счетчика 7 ) поступает на блок 8 управления, в котором вырабатываются необходимые сигналы для записи в первый и второй 9 блоки памяти. Далее первый счетчик 7 продолжает считать импульсы f до тех пор, пока еще стоит код процесса К.j. и т.д.

При отображении зарегистрированный сигнал X(t) может быть восстановлен полиномом любого порядка. Рассмотрим восстановление сигнала X(t) полиномом нулевого порядка.

Код сигнала К К,-, ,... ,К j, хранящийся в первом блоке k памяти, выводится на блок 5 отображения, определяя положение светящейся точки по вертикали. Одновременно со второго блока 9 памяти код числа j повторени кода Kj поступает на схему 23 сравIнения, где сравнивается со значением поступающим со второго счетчика 13 который считатет тактовые импульсы воспроизведения f , поступающие с генератора 6. Четвертый счетчик 18 (развертки) , определяю1 ий положение светящейся точки по горизонтали, смитает тактовые импульеы воспроизведения f, поступающие с генератора 6 тактовых импульсов. Поэтому в течение j тактов код сигнала Kj смещается по горизонтальной оси на j дискретных значений и на блоке 5 отобоажения высвечиваются j точек с равыми амплитудами ,...Кj. Когда

число j повторений кода К; значению второго счетчика 13, то схема 23 сравнения вырабатывает импульс, который поступает на блок 8 управления, вырабатывающий при этом необходимые сигналы для вывода зарегистрированной информации из первого. и второго 9 блоков памяти. Вследствие этого на блок 5 отображения с первого блока h памяти выводится код сигнала Kj4;(, а на схему 23 сравнения поступает соответствующий код чила повторений h кода сигнала KJ4-{ Таким образом, в следующие п тактов на блоке 5 отобрак ения высвечивается код сигнала Kj4i. Код последующих . зарегистрированных значений сигнала X(t) выводится аналогичным образом.

Так как число дискретных значений сигнала X(t) велико, а блок 5 отображения имеет ограниченные размеры, то на экране видна только част сигнала Х(). Для рассмотрения всего сигнала X(t) и отдельных его частей с различной точностью служит сдвиг и сжатие сигнала.

Сжатие изображения Заключается в том, что с генератора тактовых импульсов на второй счетчик 13 поступают импульсы с частотой f{j, а на счетчик 18 развертки - импульсы с частотой в Ф раз меньшей. Таким образом, на блоке 5 отображения при восстановлении полиномом нулевого по,рядка видим каждую Ф-ю точку зарегистрированного сигнала X(t) .с частотой f J.

Сдвиг изображения осуществляется за счет рассинхронизации счетчика 18 развертки и счетчиков адреса блоков 4 и 3 памяти. Чтобы не потерять достигнутой точности при записи служит оцифровка параметров сигналов между метками.

Формирователь 1 меток служит для формирбвания двух (более ярко светящихся точек) меток М и М на изображении исследуемого сигнала X(t). Эти метки получаются путем дольшего времени высвечивания этих точек по сравнению с другим Это достигается остановкой счетчика 18 развертки и второго счетчика 13 на несколько тактов воспроизведения. При помощи блока 8 управления оператором устанавливаются метки М;|И М в нужное положение. При этом на блоке 22 индикации высвечивается разность по амплитуде, по длительности между метками a также значение интеграла под кривой. Оцифровка по амплитуде заключается в том, что из первого блока k памяти код К,- соответствующий метке М, устанавливается в третий регистр 15, а код Kg, соответствующий метке проходят на блок 16 вычитания где происходит сравнение кодов К,и К2 в четвертый регистр 19. Далее с регистров 15И 19 коды К и Kg и вынитание разности между ними. Полученный результат поступает на блок 20масштабирования, в котором происходит его умножение на соответствующий коэффициент масштаба. Полученное значение разности амплитуды отоб ражается на блоке 22 индикации. Оцифровка по длительности заключается в подсчете третьим счетчиком 17 числа тактов воспроизведения между метками М и Предварительно третий счетчик 17 обнуляется формирователем Ц меток. Подсчитанное чис ло тактов воспроизведения с третьего счетчика 17 поступает на блок 20 масштабирования, где оно умножается на соответствующий масштаб и высвечивается на блоке 22. индикации. Оциф ровка интеграла исследуемого сигнала X(-t) между метками М| и М осущес вляется, следующим образом. Второй регистр 12 и пятый счетчик 21обнуляются формирователем 14 меток в момент времени t, соответствующий первой метке М.., Далее на сум маторе 11 суммируются крды сигнала между метками М и М. Результат сум мирования запоминается во втором регистре 12. Код переполнения сумматора 11 считается пятым счетчиком 21 После-.момента времени t, соответствующего второй метке М,, суммирова ние кодов сигнала прекращается. Далее код с выхода пятого c4et4HKa 21 умножается на масштабирующий коэффи|циентв блоке 20 масштабирования и высвечивается на блоке 22 индикации. Принцип работы блока управления 8 заключается в следующем. В момент времени tj4 смены, кода сигнала X(t) со схемы 10 сравнения на элемент ИЛИ 24 поступает управляющий сигнал, который проходит на формирователь 26 управляющих сигналов, а также через коммутатор 27 на счетчик 28 адреса. При этом форми рователь 2б и счетчик 28 вырабатывают необходимые сигналы для записи информации в первый 4 и второй 9 блоки памяти, работающие синхронно. Вследствие этого в первы.й блок памяти 4 записывается код сигнала К, Krt,,..Kj, а. во второй блок 9 памяти - соответствующий код .числа тактовй повторений j. После записи кода сигнала соответствующего числа тактов повторений j сигнал с выхода коммутатора 27 обнуляет первый счет- . чик 7 и второй счетчик 13. Импульсы переполнения первого счетчика 7 в момент tJ4.(i4( (где п - емкость первого счетчика 7} поступает на элемент ИЛИ 24 и проходит на формирователь 26, а также через коммутатор 27 на счетчик 28 адреса. Формирователь 26 и счетчик 28 вырабатывают необходимые сигналы для записи информации в первый 4 и второй 9 блоки памяти. Далее первый счетчик 7 продолжает считать импульсы f до тех пор, пока еще стоит код процесса т.д. По окончании регистрации сигнала X(t) переключателем 25 режима работы устройства переводим все устройство в режим отображения, при этом обнуляется счетчик 18 развертки. Формирователь 26 переключается в режим считывания. Через коммутатор 27 проходят импульсы со схемы 23 сравнения. С помощью переключателя 29 сжатия изображения осуществляется операция сжатия. При этом частота, поступающая с генератора 6 импульсов на счетчик 13 развертки, уменьшается в Ф раз В блок 8 управления входят также -и переключатели 30 и 31 сдвига маркеров. Принцип работы формирователя 14 меток (фиг.3) заключается в следующем. Формирователь 14 служит для формирования двух меток MJ и Mj(более ярко светящихся точек ): на изображении исследуемого сигнала X(t). Эти метки получаются путем большего времени высвечивания этих точек по сравнению с другими, что достигается остановкой счетчика 18 развертки и второго счетчика 13 на несколько тактов воспроизведения. Переключателями 30 и 31 сдвига первого и второго маркеров оператор устанавливает метки М и М в нужное положение. Сигналы с переключателей 30 и 31 первого и второго маркеров поступают соответственно на счетчик 32 первого маркера

и счетчик 33 второго маркера. 8 момент равенства кодов, поступающих со счетчика 33 маркера и счетчика 28 адресаУсигнал со схемы 3 или 36 сравнения проходит через элемент ИЛИ 35 и останавливает счетчик 18 развертки и второй 13 счетчик на несколько тактов, тем самым достигается более длительное время высвечивания меток М и Mjf по сравнению с другими точками исследуемого процесса X(t). Этот же сигнал с выхода схемы элемента ИЛИ 35 обнуляет третий счетчик 17- Импульс с выхода схемы 3 или 36 сравнения обнуляет первый регистр 12 и пятый счетчик 21.

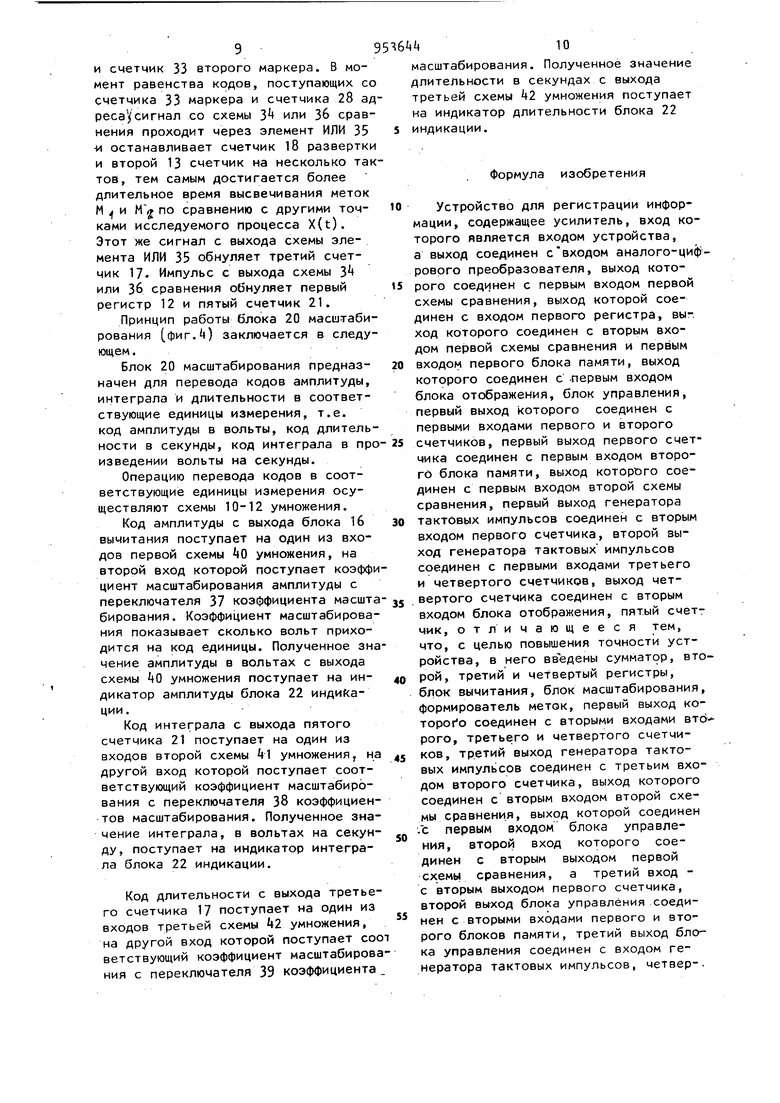

Принцип работы блока 20 масштабирования фиг.4) заключается в следующем.

Блок 20 масштабирования предназначен для перевода кодов амплитуды, интеграла и длительности в соответствующие единицы измерения, т.е. код амплитуды в вольты, код длительности в секунды, код интеграла в про изведении вольты на секунды.

Операцию перевода кодов в соответствующие единицы измерения осуществляют схемы 10-12 умножения.

Код амплитуды с выхода блока 16 вычитания поступает на один из входов первой схемы О умножения, на второй вход которой поступает коэффициент масштабирования амплитуды с переключателя 37 коэффициента масшта бирования. Коэффициент масштабирования показывает сколько вольт приходится на код единицы. Полученное значение амплитуды в вольтах с выхода схемы «О умножения поступает на индикатор амплитуды блока 22 индикации.

Код интеграла с выхода пятого счетчика 21 поступает на один из входов второй схемы 1 умножения, на другой вход которой поступает соответствующий коэффициент масштабирования с переключателя 33 коэффициентов масштабирования. Полученное значение интеграла, в вольтах на секунду, поступает на индикатор интеграла блока 22 индикации.

Код длительности с выхода третьего счетчика 17 поступает на один из входов третьей схемы умножения, на другой вход которой поступает соо ветствующий коэффициент масштабирования с переключателя 39 коэффициента.

масштабирования. Полученное значение длительности в секундах с выхода третьей схемы k2 умножения поступает на индикатор длительности блока 22 индикации.

Формула изобретения

Устройство для регистрации информации, содержащее усилитель, вход которого является входом устройства, а выход соединен свходом аналого-цифрового преобразователя, выход которого соединен с первым входом первой схемы сравнения, выход которой соединен с входом первого регистра, вы-, ход которого соединен с вторым входом первой схемы сравнения и первым входом первого блока памяти, выход которого соединен с .первым входом блока отображения, блок управления, первый выход которого соединен с первыми входами первого и второго счетчиков, первый выход первого счетчика соединен с первым входом второго блока памяти, выход которого соединен с первым входом второй схемы сравнения, первый выход генератора тактовых импульсов соединен с вторым входом первого счетчика, второй выход генератора тактовых импульсов соединен с первыми входами третьего и четвертого счетчиков, выход четвертого счетчика соединен с вторым входом блока отображения, пятый счетчик, отличающееся тем, что, с целью повышения точности устройства, в него введены сумматор, второй, третий и четвертый регистры, блок вычитания, блок масштабирования формирователь меток, первый выход коTopoto соединен с вторыми входами вто рого, третьего и четвертого счетчиков, третий выход генератора тактовых импульсов соединен с третьим входом второго счетчика, выход которого соединен с вторым входом второй схемы сравнения, выход которой соединен -С первым входом блока управления, второй вход которого соединен с вторым выходом первой схемь сравнения, а третий вход с вторым выходом первого счетчика, второй вы-ход блока управления соединен с вторыми входами первого и второго блоков памяти, третий выход блока управления соединен с входом генератора тактовых импульсов, четвер-.

тый выход блока управления соединен с входом формирователя меток, выход

iкоторого соединен с первыми входами второго регистра и пятого счетчика, выход кеторого соединен с первым вхог дом блока Масштабирования, выход которого является выходом устройства, второй вход второго регистра соединен с выходом четвертого счетчика, а третий вход - с первым выходом сумматора, первый вход которого соединен с выходом второго регистра, а второй вход - спервыми входами третьего и четвертого регистров и выходом пер.вого блока памяти,второй выход сумматора соединен с вторым BxojqoM пя,того счетчика, выходы третьего и четвертого регистров соединены с соотеетствующими входами блока вычитания, выход которого соединен с вторым входом блока масштабирования, третий вход которого соединен с выходом третьего счетчика, второй вход четвертого счетчика соединен с первым выходом блоке управления.

Источники информации, принятые во внимание при экспертизе

2,Авторское свидетельство СССР по заявке № 2859836/18-2,

кл. G Об К 15/00, 1980 (прототип).

С1ббл

CZ1Ь

ФигЛ

Авторы

Даты

1982-08-23—Публикация

1980-10-20—Подача