двух последних дополнительных групп являются разрядными входами устройства.

2. Устройство по п. 1, о т л ичающееся тем, что блок обработки многозначного ответа содержит триггеры, вторую группу элементов И, rpjrnny элементов И-ИЛИ, элементы И со второго по пятый, элемент ИЛИ и элемент НЕ, выход и вход которого соединены соответственно с первыми входами второго и третьего элеменtOB И, вторые входа которых объединены, причем прямые выходы триггеров подклк$чены к первым входам элементов ИЧ1ИЙ группы, вторые входы которых соединены с выходом первого элемента И, третьи входа элементов ИШШ группы, кроме первого, подключены к выходам элементов И второй групШ первые вхоДы которых соединены с йявеЬсяыми выходами одних из триггеров, выход второго элемента И под00638

ключей к третьему входу первого элемента И-ИЖ и. второму входу первого иэ элементов И второй группы, второй вход каждого последующего элемента И второй группы соединен с выходом предыдущего элемента И второй группы, выход элемента ИЛИ подключен к первому входу четвертого элемента И, второй вход которого соединен с одним из входов пятого элемента И и управляющими входгши триггеров, входы которых соединены со входами элемента ИЛИ и другими входами пятого элемента И и являются одними из входов блока, одними иэ выходов которого являются выходы элементов И-ИЛИ группы, вход элемента НЕ, второй вход второго элемента И и второй вход четвертого элемента И являются другими входами блока, другими выхо дами которого являются выходы четвертого и пятого элементов И соответственно.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1249592A1 |

| Ассоциативное запоминающее устройство с самоконтролем | 1980 |

|

SU858105A1 |

| СИСТЕМА ДЛЯ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ С ИСПРАВЛЕНИЕМ ОШИБОК | 1991 |

|

RU2007042C1 |

| Ассоциативное запоминающее устройство | 1975 |

|

SU555438A1 |

| Запоминающее устройство с самоконтролем | 1988 |

|

SU1522292A1 |

| САМОКОНТРОЛИРУЮЩЕЕСЯ УСТРОЙСТВО | 2004 |

|

RU2297028C2 |

| САМОКОРРЕКТИРУЮЩЕЕСЯ УСТРОЙСТВО | 2004 |

|

RU2297029C2 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1167659A1 |

| ОТКАЗОУСТОЙЧИВОЕ УСТРОЙСТВО | 2004 |

|

RU2297036C2 |

| САМОКОРРЕКТИРУЮЩЕЕСЯ УСТРОЙСТВО ХРАНЕНИЯ ИНФОРМАЦИИ | 2004 |

|

RU2297030C2 |

1. ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С (ЖОНТРШБН содержащее накопитель, упр ляюоще входы которого являются соответственно перв)ым входом обращения и йе|юьм входом записисчитывания усч йства, первый элемент И и основную группу из п триггер(Ю, выходы которых являются выходам а% еоциативмого считывания устройства, причем первые входал п триггеров основной группы, где т- разрядность адреса и , подключены к адресным входам накогостеля и являются основными адресньво входами устройства, от ли ч а ю щ е е с я тем, что./ с целью повыше ния надекности за счет повышения достоверности контроля и быстродействия устройства, в него введены сумматор по модулю два, одни из входов которого подключены соответствеЯ1Н к информационным выходам и к иифа|й«а ционшлм входам устройства,блоки сравнения, первая группа элементов И, блок обработки многозначного ответа . и (п-1) дополнительных групп из И триггеров, первые выходы которт соединены с первыми выходами соответствующих триггеров основной группы. Ефичем вторые выхода триггеров основной и дополнительных групп подключены к первым входам соответствующих блоков .сравнения, выходы которых подкдючешл к оДиин ИЗ входов блока обработки многозначного ответа, первый вход Кто триггера, где К 1, «.. (-1) К-й дополнительной группы, кроме последней, соединен с первым входом (т+1)-го триггера той же группы, первые входа1 триггеров дополнительных подколочены к первым входам Соответствующих триггеров основной грушил, выходы первого элемента И и элементов И первой группы I соединесш соответственно со вторыми входами триггеров основной и допол- . (Л нителывлс групп и одними из выходов с блока обработки многозначного ответа, другие входы и другие выходы § которого являются соответственно одт ними из управляющих входов и контрольных выходов устройства, первые входы первого элемента И и И первой группы объединены и являются э ДРУГ1Ш управЛя(Ш(им входом устройства, р вторые входы первого элемента И и р .одного из элементов И первой группы 9 30 являются дополнительными адресными входами устройства, вторые входы других элементов И первой группы подключены к адресным входам накопителя, вторые входы блоков сравнения соответственно объединены и являются входаш маскирбвания устройства, . вторым входом записи-считывания которого и другим контрольным выходом которого являются-другой вход и выход с: о атора по модулю два, первые входы (n-m) триггеров основной и

Изобретение относится к вычислительной технике.

Известно запоминающее устройство с самоконтролем, в котором используется информационная избыточность на группу слов ЗУ для обнаружения и диагностирования ошибок при считывании информации ЗУ tn

Недостатком этого устройства является низкая Достоверность контроля.

Наиболее близким к данному изобретению является запомина|(яцее устройство с самоконтролем, включающее в себй регистр, содержащий триггеры со счетным входом, элементы И, накопитель, блок начальной установки и разрядный коммутатор, причем первые входы всех разрядов регистра соединены ойной выборки, вторые входы регистра каждого разряда соединены с первыми адресными шинайи, выходные числовые В1ИНЫ, шины считывания и поиска, соединенные с выходами каждого разряда регистра, первые адресные щины соединены с входами накопителя, которое при одном цикле контрольного считывания информации проверяемого множества слов ЗУ диагностирует (указывает адерс) одиночную ошибку и обнаруживает некоторые типы многократных ошибок С 2 .

Недостатком этого устройства является то, что оно не позволяет различать одиночную ошибку от многократной ошибки нечетной кратности, а также производить диагностирование многократных ошибок без проведения дополнительных циклов контрольного считывания информации, что снижает достоверность контроля, т.е. снижает его надежность, особенно в случае ошибок типа сбоя, а также его быстродействие, и, кроме того, устройство ориентировано на контроль накопителя с заранее известной информацией (ПЗУ), что ограничивает область его применения.

Целью изобретения является повьпвение надежности за счет повышения достоверности контроля и быстродействия устройства за счет возможности диагностирования многократных ошибок (двойных и тройных) при одном цикле ,контрольного считывания информации.

Поставленная цель достигается тем, чТо в запоминающее устройство с самоконтролем, содержащее накопитель, управляющие входы которого являются соответственно первым входом обращения и первымВХОДОМ записи-считьшания устройства, первый элемент И и основную группу из п триггеров (где п - разрядность накопителя), первые выходы которых являются выходани ассоциативного считьшания устройства, причем первые входы m триггеров основной группы (где m - разрядность адреса и m и ) подключены к адресным входам накопителя и являются основньши адресньмй входами устройства, введены сумматор по модулю два, одни из входов которого подключены соответственно к информационным выходам и к. информационньш входам устройства, блоки сравнения, первая группа элементов И, блок обработки многозначного ответа и (h-1) дополнительных групп из п триггеров, первые выходы которых соединены с первыми выходами соответствующих триггеров основной группы, причем вторые выходы триггеров основной и дополнительных групп- подключены к первьм входам соответствующих блоков сравнения, вькоды которых подключены к одним из входов блока обработки MHoro3ita ittoro ответа, первый вход К-го триггера (где К 1,... , (rv-l) К-й дополнительной группы, кроме пос-з5

ладней, соединен с пераьж входом ( +1)-гО триггера той же 1руппы, первые входы триггеров дополнительных групп йодключешл к первым входам соответствующих триггеров основной группы, выходы первого элемента И и элементов И группы соединены соответственно со вторыми входами триггеров основной и дополнительных групп и одними из выходов блока обработки многозначного ответа, другие входы и другие выходы которого явля-ются соответственно одними из управляющих входов и контрольных выходов устройства, первые входы первого эле мента И и элементов И первой группы объединены и являются другим управляющим входом устройства, вторые входы первого элемента И и одного из элементов И первой группы являются дополнительными адресными входами устройства, вторые входы других эле.ментов И первой группы подключены

к адресным входам накопителя, вторые входы блоков сравнения соответственно объединены и являются входами |маскирования устройства, вторым входом записи-считывания которого и другим контрольным выходом которого являются другой вход и выход сумматора по модулю два, первые входы (n-nt) триггеров основной и двух последних дополнительных групп являются разрядными входами устройства.

Блок обработки многозначного ответа содержит триггеры, вторую группу элементов И, группу элементов ИИЛИ, элементы И со второго по пятый, элемент ИЛИ и элемент НЕ, выход и вход которого соединены соответственно с первьми входами второго и третьего элементов И, вторые входы которых объединены, причем прямые выходы триггеров подключены к первым входам элементов И-ИЛИ группы, вторые входы которых соединены с выходом первого элемента И, третьи входы элементов И-ИЛИ групгал, кроме первого, подключены к выходам элементов И второй группы, входы которых соединены с инверсными выходами одних из триггеров, выход второго элемента И подключен к третьему входу первого элемента И-ИЛИ и второму входу первого из элементов И второй группы, второй вход каждого последунлцего элемента И второй группы соединен с выгруппы, выход элемента ИЛИ подключен к первому входу четвертого элемента И второй вход которого соединен с одним из входов пятого элемента И и управляняцими входами триггеров, входы которых соединены со входами элемента ИЛИ и другими входами Пятого элемента И и являются одними из входов блока, одними из выходов которого являются выходы элементов И-ИИИ группы, вход элемента НЕ, второй вход второго элемента И и второй вход четвертого элемента И являются другими входами блока, другими выходами ксЖ рого являются выходы четвертого и пятого элементов И соответственно

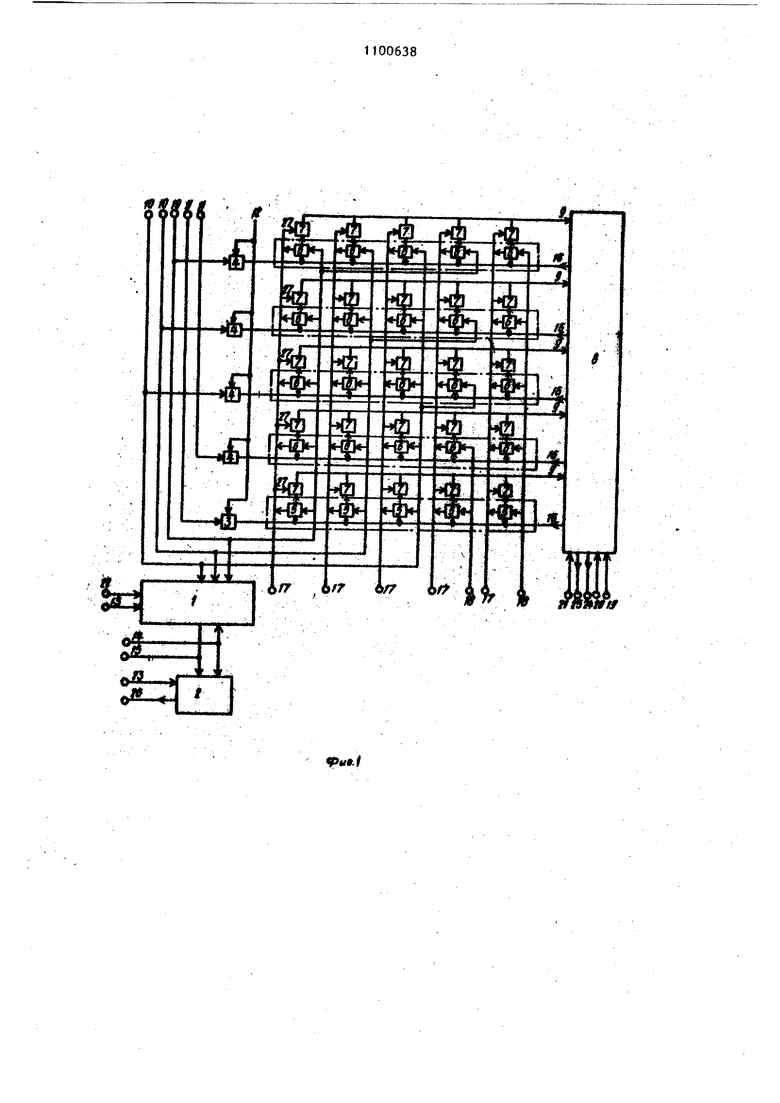

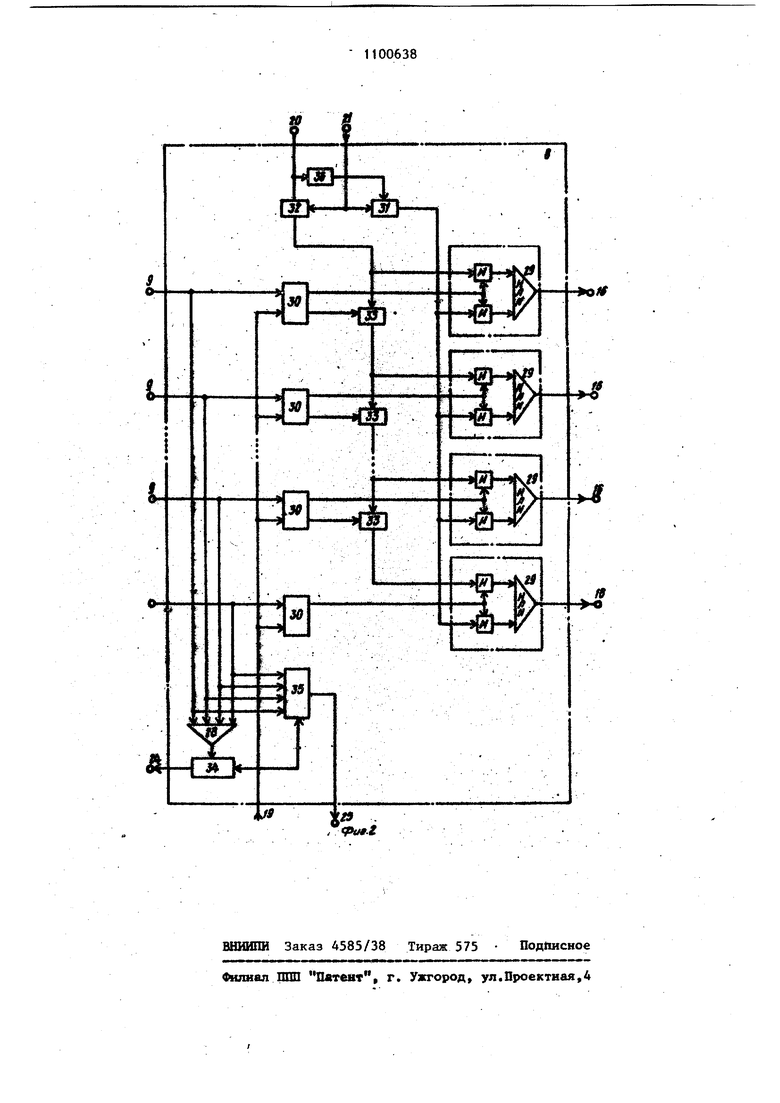

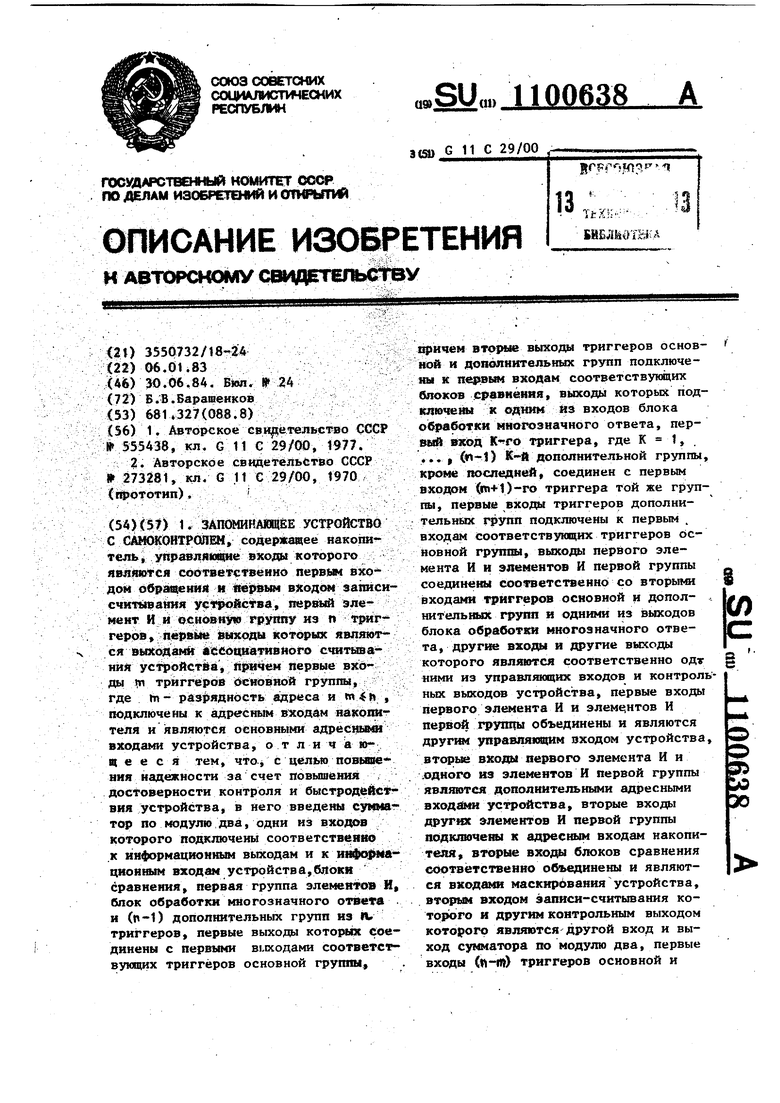

На фиг. 1 представлена функциональная схема предпоженного устройства на фиг. 2 - функциональная схема блока обработки многозначного ответа.

Предложенное устройство содержит (фиг. 1) накопитель 1, сумматор 2 по модулю два, Первый элемент ИЗ, перходом предадущего элемента-И второй вуто группу элементов И 4, основную группу триггеров 5, д(полнительные группы триггеров 6, блоки 7 сравнен и.блок 8 обработки многозначного от вета с одними из входов 9. На фиг. 1 обозначены основные 10 и дополнительные 11 адресные входы устройства, управляющий вход 12 уст ройства, предназначенный для подачи сигналов разрешения выборки группы триггеров, первый вход 13 обращения информационные входы 14 и выходы 15 устройства, одни из выходов 16 блока 8 обработки многозначного ответа выходы 17 ассоциативного считывания и разрядные входы 18 устройства, уп равляющие входы 19, 20, 21 устройст ва, предназначенные для ввода сигна лов признака поиска, признака запис считывания и ассоциативного обращения соответственно, первый22 и вто рой 23 входы записи-считывания, конт рольные выходы 24, 25, 26 и входы маскирования 27 устройства: Блок 8 обработки многозначного ответа содержит (фиг, 2) элемент ИЛИ группу элементов И-ИЛИ 29, триггеры 30, второй 31 и третий 32 элементы И, вторзта группу элементов И 33, четвертый 34 и пятый 35 элементы И и элемент НЕ 36. Устройство работает следующим образом. 2 производит сложение кодов на входах 14 и выходах 15 (фиг. 1). При нечетном количестве единиц в кодах чисел на вьпсоде 26 формиру|гтся сигнал 1, при четном - О. Предполагается, что при операции Чтение из накопителя 1 сумматор 2 производит сложение по модулю два только кодов чисел, считьюаемых на iвыходе 15, а при операции Запись кодов чисел на взсодах 14 и выходах 15. Считается, что при операции Запись по некоторому адресу предварительно считывается информация по этому адресу на выходы 15. Для контроля считьгеания информации из накопителя 1 используется проверка на четность с применениемкода Хемминга. Вектор полной проверки представляет собой поразрядную сумму по модулю два двоичных кодов адресов накопителя 1, с которых считывается нечетное количество единиц. Старший разряд полной проверки представляет собой, сумму по модулю два всей считываемой из накопителя 1 информации. Вектор полной проверки содержит (l-t-Eog N) разрядов (где т - количество разрядов кода адреса ЗУ и 2 N - количество адресов). Вектор частичной i-ой проверки представляет собой поразрядную сумму по модулю два кодов адресов накопителя 1 , имеющих единицу в 1-ом разряде кода адреса и нечетное количество единиц, считываемых по этому адресу (где 1 i tn) . Вектор частичной проверки содержит (1+во&2 разрядов. Базисным разрядом вектора частичной . i-й проверки называется ее i-й разряд. Значение старшего разряда частичной проверки равно значению базисного разряда и количество частичных сумм равно Jo N. Аппаратно векторы проверок образуются с помощью триггеров 5 и 6, реализующих операцию сложения по модулю два кодов адресов накопителя 1. Каждой i-й частичной проверке соответствует i-я из трупп триггеров 5 и 6. Полной проверке соответствуют (и-т) групп триггеров 5 и 6 (для рассматриваемого случая п ). Принадлежность кода адреса накопителя 1 i-й проверке определяется значением .i-ro разряда кода адреса. Для формирования проверочных сумм (выполнения поразрядного суммирования по модулю два и накопления результатов) соответствующие группы триггеров 5 и 6 выбираются по содержанию суммируемого кода адреса. Векторы полных и частичных проверок образуются группами триггеров 5 и 6 в процессе записи информации в накопитель 1. . Если информация при контрольном считывании соответствует записанной, значения проверок во всех триггерах 5 и 6 дополняются до нуля в процессе считывания и суммирования. В случае одиночной ошибки (измеения частности информации в одном дресе) при считывании из накопитея 1 значения векторов частичных проерок могут образовывать: во-первых, нулевой вектор - для ех проверок, в которые не включается код адреса ошибки,, т.е. код адреса содержит О в разрядах, соответствугацих базисным разрядам проверок,

во-вторых, ненулевой вектор, равный вектору общей проверки - для тех проверок, в которые включается код адреса ошибки, т.е. код адреса содержит 1 в разрядах, соответствующих базисным разрядам проверок:.

В соответствии с рассмотренными значениями частичные суммы образуют два множества: Sj, S.

В случае двойной ошибки (изменение четности информации в двух адресах при считывании из накопителя 1 значения частичных проверок в триггерах 5 и 6 могут образовывать:

во-первых, нулевой вектор - для тех проверок, в которые не входят адреса ошибок, т.е. эти адреса содержат О в разрядах, соответствующих базисным разрядам проверок;

во-вторых, ненулевой вектор, равный seKtopy общей проверки - для тех проверок которые включили каждьй из адресов ошибок, т.е. эти адреса содержат 1 в разрядах, соответствунхцих базисным разрядам проверок

в-третьих, хотя бы один ненулевой вектор, не равный зектору общей про верки.

В первых двух случаях базисные разряды частных проверок содержат О в последнем случае - 1.

Код адреса одной из двух ошибок определяется проверками содержащими 1 в базисном разряде. Код адреса второй ошибки находится как результат сложения векторов первой ошибки, и вектора общей проверки. В соответствии с рассмотренными значениями частичные суммы образуют три множества.

В случае тройной ошибки (изменение четности информации в трех адресах при считывании из накопителя 1) значения частичных проверок могут образовывать S, sf:

во-первых, нулевой вектор - для проверок, в которые не включены адг реса ошибок, т.е. эти адреса содержат О в разрядах, соответств ощис базисным разрядам проверок,

во-вторых, не нулевой вектор, неравный вектору общей проверки - для тех проверок, которые включают один из адресов ошибок и, следовательно, «определяют адрес одной ошибки.

в-третьих, не нулевой вектор, не равный вектору общей проверки - для тех проверок, в которых содержатся два из трех адресов ошибок, т.е. два адреса-ошибок содержат 1 в разрядах, соответствующих базисным разрядам проверок,

в-четвертых,.вектор, равный вектору общей проверки - для тех проверок которые включают каждый из трех адресов ошибки, т.е. эти адреса содержат 1 в разрядах, соответствующих базисным разрядам проверок. Вектор любой из трех ошибок не мбжет равняться сумме трех векторов ошибок, так как сумма двухоставшихся векторов не равна нулю вследствие того, что они различаются бы в одном разряде.

В соответствии с рассмотренными значениями частичные суммы образуют четыре множества: S, S, Sj, S.

В первом и третьем случаях базисные разряды частичных проверок содержат О.

Во втором и четвертом случаях базисные разряды частичных проверок содержат t.

В случае трехкратной ошибки хотя бы одно из множеств S или S не пусто.

Если множество S, пусто, то множество S в качестве своих элементов содержит все три вектора (адреса) ошибок, которые можно выделить вследствие их попарного неравенства

Если Sj не пусто, вектор одной из трех ошибок можнЬ найти сложением какого-либо из элементов множест ва Sj (значение которого представляет собой суммы пар векторов ошибок) с вектором общей проверки, содержащей сумму трек векторов ошибок

Ьычктая полученный вектор, одной из ошибок из тех проверок в которые он входил, можно получить новое содержание множества всех проверок, которое соответствует случаю двойной ошибки.

Процедура О1фвделения адресов двойных ошибок описьюалась выше.

Рассмотренные случаи определяют четыре попарно раэличт«ых и не пересекающихся мншсества векторов проверок.

Анализ принадлежности векторов частичных проверок, полученных в результате контрольного суммирования 9 к рассмотренным множествам, позволяет определить кратность ошибок (одиночная, двойная или тройная), а также адреса всех одиночных, двойных и тройных ошибок. Анализ выполняется с помощью операций поиска и поразряд ного сложения по модулю два, выполняемых в триггерах 5 и 6. Описываемое устройство работает в режимах начальной установки, рабо та, контроль. В режиме начальной установки в накопитель 1, в триггеры 5 и 6 записывается код О, для чего на входы 10подается последовательность ад ресов и производится запись кода О После этого реализуется операция поиск 1 - запись О по всем триг герам 5 и 6. В режиме Работа производится запись и считывание внешней информации на входах 14 и выходах в накопитель 1 . Если сумма по модулю два записываемой и считываемой информации по некоторому адресу равна единице на выходе 26 сумматора 2, то производится запись кода со входов 10 в те группы триггеров 5 и 6, которым соответствуют 1 в коде адреса. При этом элементы И 3, 4 открыты, на входы 11 поданы сигналы 1, а на входы 18 - код О, тем самым в (п-пО триггерах 5 и 6 накапливается значение вектора полной проверки. При равенстве записываемых в накопитель 1 и считываемых кодов сигнал на выходе 26 равен О. Запись в триггеры 5 и 6 не производится, сигналы на входах 11, 12 и 21 равны О. При операции Чтение из накопителя 1 запись в триггеры 5 и 6 не производится Предполагается, что накопитель 1 вьтолняет две операции: Считывание иСчитывание - запись. Над информац ей, содержащейся в триггерах 5 и 6 выполняются адресные операции (Считывание, Запись) и ассоциативные операции (Поиск-ответ, Поиск-считьшание, Поиск-запись). Вид операции определяется значением О или 1 сигнала признака Запись-чтение на входе 20, сигнала на входе 21, сигнала признака Поиск на входе 19, сигнала разрешения выборки на входе 12. При адресных операциях значения сигнала Поиск на входе 19 равно О при ассоциативных - 1. 3810 Адрес, по которому производится обращение к накопителю 1, подается | на входы 10, а коды чисел - на входы 14 и выходы 15 соответственно. Коды, хранящиеся в накопителе 1, считываются на выходы 15 при каждом обращении по входу 13. Выборка групп триггеров 5 и 6 Mof жет быть групповой или одиночной при операциях Запись или Поискзапись и одиночной - при операции Чтение, Поиск-считывание. При адресных операциях это обеспечивается соотвегтствугацим выбором кода адреса на входах 10, 11, который поступает на входы триггеров 5 и 6 через элементы И 3,4, открытые сигналом на входе 12. Код информации, записываемой в триггеры 5 и 6, пойтупает на входы 10 и 18 выбранной группы триггеров 5 и 6. Записываемая информация складывается по модулю два с хранимой в триггерах 5 и 6, в которых остается сумма. Запись в любом разряде может быть маскирована сигналов на входах 27 блоков 7, поступающим по выходу 17, используемому также и для вывода информации во внешнее устройство (ЭВМ) при операции Считывание. При операции Запись триггеры 5 и 6, которые связаны со входами 10, 18 базисных разрядов и входят в старшие разряды групп триггеров 5 и 6, информационно дублируют триггеры 5 и 6 базисных разрядов. При операции Поиск-ответ. код поиска подается на выходы 17. Сигналы совпадения при поиске образуются блоками 7, поступают на входы 9 и анализируются блоком 8. При наличии хотя бы одного совпадения кода в триггерах 5 или 6 и кода на выходах 17 блоком 8 выдается сигнал 1 на выход 24, а при отсутствии совпадения - О. При операции Поиск-запись, определяемой управляющими сигналами на входах 22, 23, блоком 8 одновременно активизируются для записи те из выходов 16, на которые проходят сигналы совпадения со входом 9 (фиг. 2)i выработанные блоками 7 в процессе поиска. При операции Поиск-чтение те выходы 16, на которые поступают через блок 8 сигналы совпадения с выходов блоков 7, возбуждаются для считьшания последовательно.

Считываемый из выбранной блоком 8 по выходу 16 группы триггеров 5 или 6 код передается на выход 17.

Рассмотрим работу блока 8 при ассоциативных операциях.

При операции Поиск-ответ на вход 19 (фиг. 2) подается сигнал 1 в результате чего элемент ИЛИ 28 фор мирует сигнал 1 на выходе 24 при наличии хотя бы одного сигнала совпадения на входах 9.

Сигнал 1 на выходе 25 формируется элементом И 35 при наличии совпадения на всех входах 9.

Состояние входов 9 запоминается в триггерах 30.

При операции Поиск-запись информация из триггеров 30 через элементы И-ИЛИ 29 передается на выходы 16, на входе элемента И 31 формируется сигнал 1 при наличии сигнала 1 на- входе 21 и сигнала О на входе 20, что обеспечивает групповую запись информации в триггеры 5 и 6 (фиг. 1) в соответствии с кодом информации, содержащейся в триггерах 30

При операции Поиск-считывание сигнал 1 на выходе элемента И 32, образующийся при сигналах 1 на входах 20 и 21, проходит до того из элементов И 33, который соответствует триггеру 30, находящемуся в состоянии 1, что обеспечивает сигнал 1 на выходах этого элемента И 33, соответствующего ему элемента И-Ш1И 29 и на соответствующем из выходов 16, что обеспечивает выбоку информации из соответствующей группы триггеров 5 или 6.

При адресных операциях сигнал О на входе 21 блокирует активизацию выходов 16 со стороны блока 8.

Рассмотрим работу устройства 6 ре жиме контроля.

Процедура контроля разделяется на два цикла:

контрольного считывания информаци из накопителя 1,

анализа результатов контрольного суммирования.

При контрольном считывании информации на входы 10 подается последовательность адресов накопителя 1, на входы 11 - код 1, на входы 18 ()-ro и (т+2)-го триггеров 5 и 6 коды О и 1 соответственно, на

вход 12 - код, равный- значению сигнала на выходе 26.

При сигнале 1 на выходе 26 производится запись в триггеры 5 и 6, выбранные кодом адресов на входах 10 и 11 при открытых сигналом на входе 12 элементах И 3 и 4.

Анализ результатов контрольного суммирования производится следующим образом.

В режиме Поиск-ответ производится поиск нулевого кода триггеров 5 и 6. При отсутствии ошибок состояние всех триггеров 5 и 6 - нулевое, и на выходах 24, 25 блоком 8 формируется сигнал 1.

При наличии хотя бы одного нулевого слова в группах триггеров, 5 и 6 на вькоде 25 формируется сигнал G.

V В этом случае в режиме Считывани сигналом на входах 11 выбирается (т+2) группа триггеров 5 и 6 и их содержимое анализируется внешним устройством (ЭВМ).

Нулевое состояние группы триггеров 5 или 6 соответствует наличию четного количества ошибок при контрольном считывании информации из накопителя 1, эти ошибки не могут быть диагностированы устройством в общем случае.

При ошибках кратностью до трех включительно состояние триггеров 5 и 6 - ненулевое.

В этом случае нулевое значение старшего разряда в группе триггеров 5 и 6 соответствует двойной ошибке.

Рассмотрим определение адресов двойной ошибки.

Производится поиск 1 в (т+1)-м разряде группы триггеров 5 или 6 при массированных остальных разрядах в режиме Поиск-считывание.

РезульФат поиска (сигналы на входах 9) анализируется блоком 8, который обеспечивает выборку (считьгоание информации из одной ,из групп триггеров 5 или 6, имеющей 1 на выходе 17 в старшем разряде.

Считанный код является адресом одной из ошибок.

Для определения адреса второй ошибки производят вычитание (поразрядное сложение по модулю два) считанного кода с информацией в (т+2)-и группе триггеров 5 или 6, которая

является суммой векторов адресов двух ошибок.

Вычитание производится записью считанного кода в (ni-f2)-ro группу

триггеров 5,6, выбранную сигналом 1 5 на (т+2)-м входе 11 в режиме Запись при открытых элементах И 3,4 сигналом 1 на входе 12. Результат вычитания является адресом второй ошибки и считывается на выходы 17 Ю

Если из (гтн-2)-й группы триггеров 5, 6 считался код, старший разряд которого равен 1, то количество ошибок нечетно (одна или три) и диагностирование производится следующим об- fs разом.

В (т+1)-х триггерах 5 и 6 содержатся единицы в тех группах № триггеров 5,6, которые содержат код О и код вектора полной проверки в 20 (т+2)-х триггерах 5 и 6. Для1 диагностирования производится поиск 0 запись 1 в (т+2)-х триггерах 5 и 6 ГРЗТ1П, причем Поиск 6 производится во всех группах тригге|) . 25 и .6 (без маскирования) а запись 1 только в (tri+O-x триггерах групп.

Затем производится поиск кода, считанного из всех триггеров 6 (т+2)-й группы, кроме (п+1)-го триг- зо гера 6, который маскируется, и запись 1 в зависимости от результата поиска в (гч+2)-е триггеры 5 и 6 тех групп, которые содержат код равный коду (|П+2)-й групгал триггеров 5,

Бели в результате рассмотренных операций (пн-1)-е тригге1ял 5 и 6 всех групп содержат единицы ошибка является одиночнойу ее адрес хранится в {п1+2)-й группе. Информация в , о (w+1)-x триггерах 5 и 6 определяется операцией Поиск О,

Если в (m+t)-x триггерах 5 и 6 не содержится нули, то блок 8 вырабатывает сигнал О на выходе 24, 45 при наличии которого производится считывание кода адреса одиночной ошибки на выходы 17 из (пи-2)-й группы триггеров 5,6. В противоположном случае на выходе 24 вырабатывается ,. сигнал t, что соответствует трехкратной ошибке.

Диагностирование трехкратной ошибки производится следующим образом.

Производится поиск групп тригге- 55 ров 5 и 6, содержащих сумму адресов двух ошибок. Достаточным признаком таких групп триггеров 5, 6 является

нулевое значение (.ц-т)-х триггеров 5 и 6 (так как все содержащие нули группы триггеров 5 и 6 отмечены 1 в (п+1)-х. триггеров 5 и 6 в результате прёдьщущих операций).

Поиск этих регистров производится как операция Поиск О в (h-m)-x триггерах 5 и 6 при маскированных остальных триггерах 5 и 6.

Если блок 8 вырабатьгоает сигнал О на выходе 24, то векторы--кодов адресов ошибок ортогональны и могут быть определены поиском групп триггеров 5 и 6, содержащих адрес одной ошибки, и считыванием элементов множества.

Признаком таких групп триггеров 5 и 6 является значение 1 в п-х триггерах 5 и 6 при значении О в (tn+1)-x триггерах 5 и 6. Множество групп триггеров 5 и 6, содержащих сумму трех ошибок и значение 1 в -п-м триггере 5 (или 6), отмечено 1 в (m+1)-iii триггере 5 (или 6) в результате предыдущих операций.

Поиск зтих групп триггеров 5 и 6 осуществляется как операция Поиск 1 в п-х и Поиск О в (п+1)-х триггерах 5 и 6 при маскированных остальных триггерах 5 и 6 и последующее считывание с выборкой от блока 8, что обеспечивает считывание кода адреса первой ошибки на выходы 17.

Получение адресов вторсй и третьей ошибок обеспечивается режимом Поиск-3 апнсь t. Поиск произ водите я на соответствие с кодом адреса первой ошибки.

Запись производится в (пн-1)-е тригге|ял 5 и 6 при маскировании остальных триггеров 5 и 6. t-

Получение адреса второй и третьей

ошибок для образованного распределения информации в триггерах 5 и 6 производится аналогично рассмотренным операциям сс1итывания адреса первой ошибки..

Если после получения адреса второ ошибки поиск группы триггеров 5 или 6 с кодом адреса третьей ошибки дает результат О на выходе 24, код адреса третьей ошибки нулевой, так как этот адрес не может входить в частичные проверки и его информация контролируется ц-ми триггерами 5, 6 (), ()-х групп.

Если блок 8 при поиске регистров с кодами множества Sj вырабатывает 15 сигнал 1 на выходе 24, то адрес первой ошибки можно найти вычитанием (сложением по модулю два) элемен тов множества S с суммой трех оши бок (элементами множества S ), которая хранится в (m+l) и (in+2)-x группах триггеров 5,6. Для этого используются режимы Поиск-считывание элементов множества S и запись его в (т+2)-ю группу триггеров 5,6. Поиск производится на соответствие с кодом, содержащим О в (ш+О (tn-i-2)-M разрядах при маскировании остальных разрядов. Считанный блоком 8 код записывается в регистр (гт-2)-ю группу триггеров 5, 6 и образует код адреса первой ошибки как результат суммиро вания. Для определения адресов второй и третьей ошибок предварительно получают распределение информации в триггерах 5 и 6, соответствующее наличию двух ошибок (второй и третьей) в считанной из накопителя 1 информации. .ч Для этого код адреса первой ошиб ки, находящийся в()-й группе 38 триггеров 5,6, вычитают из тех проверок, в которых он присутствовал. Эта процедура обеспечивается режимом Запись в триггеры 5 и 6 при подаче на входы 10 кода адреса первой ошибки, сигналов 1 на входы 11 и 12, при этом (п(И-1)-е триггеры 5 и 6 всех групп устанавливаются в состояние, О в режиме Поиск 1 завись О при маскированных остальных триггерах 5 и б. Обработка нового распределения информации производится по приведенному алгоритму диагностирования двойной ошибки. Таким образом, предлагаемое устройство дает возможность диагностировать одиночные, двойные и тройные ошибки за один цикл контроля, T.ej локализовать многократные сбои,- что повышает достоверность контроля и быстродействие устройства. Технико-экономическое преимущество предложенного устройства заключается в его более высокой надежности, достигаемой повышением достоверности контроля и быстродействия устройства по сравнению с прототипом.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Ассоциативное запоминающее устройство | 1975 |

|

SU555438A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 0 |

|

SU273281A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1984-06-30—Публикация

1983-01-06—Подача