Изобретение относится к запоминающим устройствам. Известно запоминающее устройство для определения достоверности и контроля в процессе функционирования хранящейся информации, в котором используется метод схемного и информационнотчэ дублирования запоминающей матрицы устройства l . Структурно это решается с помощью связей выходов индикаторов и шин считывания запоминающих матриц с элементами сравнения, что позволяет осуществлять пословную обработку информации (сравне ние считываемых слов и результатов поиска в двух ассоциативных матрицах между собой). Это приводит к значительной информационной и схемной избыточности этого устройства. Из известных устройств наиболее близким техническим решением к изобретению является ассоциативное запоминающее устройство, содержащее блок управления, подключенный к блоку сравнения, элемент И и утфавляющие шины J. Недостатком этого устройства является большая информационная и схемная избыточность ассоциативной памяти, состоящая в необходимости использования второй (дублирующей) матрицы ассоциативной памяти. Целью изобретения является упрощение устройства. Достигается это тем, что устройство содержит сумматоры по модулю два, коммутатор и дополнительный блок сравнения, входы первого и второго сумматоров по модулю два подключены к соответствующим выходам блока памяти, выход первого сумматора по модулю два соединен с входом коммутатора, выходы которого подключены к одним входам дополнительного блока сравнения, другие входы которого соединены с выходами третьего сумматора по модулю два, выходы второго сумматора по модулю два и блока сравнения подключены соответственно к входам элемента И и третьего сумматора по модулю два; входы блока сравнения подключены к управляющим шинам и одному из выходов блока управления, другие выходы которого соединены с

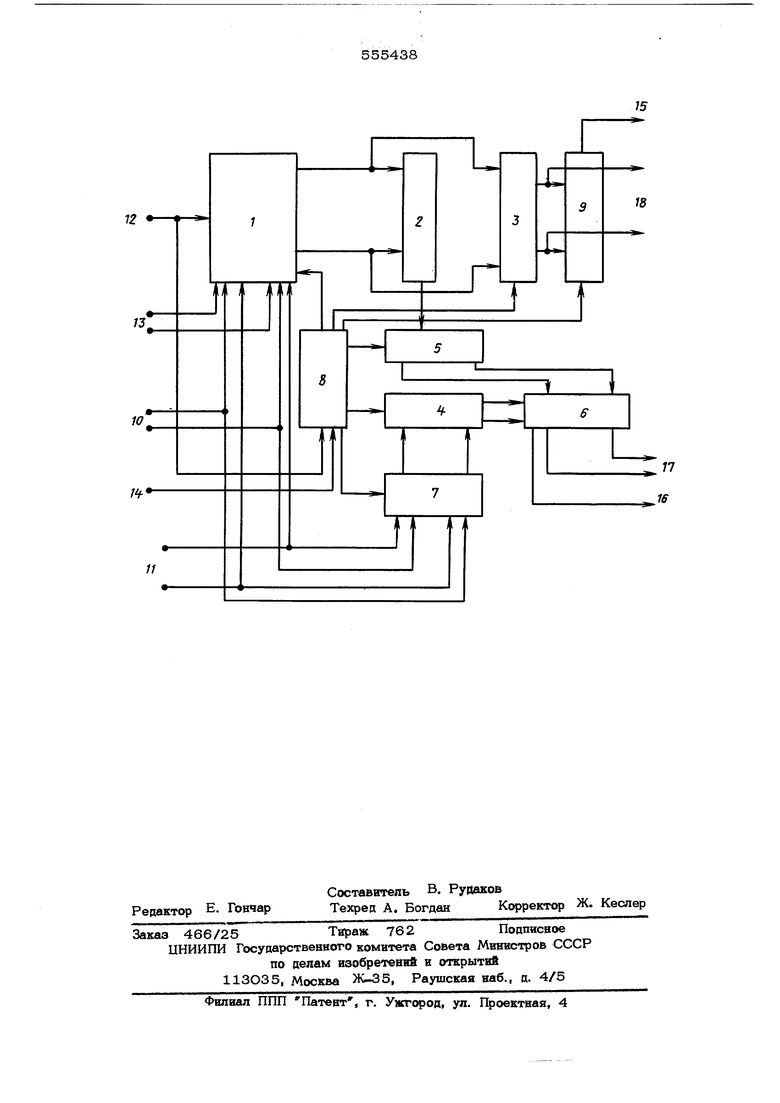

входами второго и третьего сумматоров по модулю два, элемента И и коммутатора. На чертеже дана блок-схема устройства Ассоциативное запоминающее устройство содержит блок памяти 1, первый, второй

и третий сумматоры 2, 3, 4 по модулю два коммутатор 5, дополнительный блок сравнения 6, блок сравнения 7, блок управления 8, элемент И 9, управляющие шины 10-14 выходные шины 15-18.

Входы первого 2 и второго 3 сумматоро по модулю два подключены к соответствующим выходам блока памяти 1, выход первого сумматора 2 по модулю два соединен с входом коммутатора 5, выходы которого

подключены к одним входам дополнительного блока сравнения 6, другие входы которого соединены с выходами третьего сумматора 4 по модулю два, выходы второго сумматора 3 по модулю два и блока сравнения 7 подключены соответственно к входам элемента И - 9 и третьего сумматора 4 по модулю два, входы блока сравнения 7 подключены к управляющим шинам 10 и 11 и одному из выходов блока управления 8, другие выходы которого соединены с входами второго 3 и третьего 4 сумматоров по модулю два элемента И 9 и коммутатора 5.

Устройство работает в двух режимах. Первый режим - определение контрольной суммы информации, записываемой в устройство, и второй - определение контрольной суммы информации, хранящейся в устройства.

Перед началом работы устройства в составе ЭВМ сигналами от блока управления 8 производится запись О во все ячейки блока памяти 1, а также сброс в состояние О сумматоров 3 и 4 по модулю два. При заполнении блока памяти 1 информацией производится обращение к устройству с поиском нулевого слова (признак поиск и код числа О на уп- равляющих шинах 12 и Ю соответственно), которое считывается на управляющую шину 11с некоторого адреса блока памяти 1 с последующей записью кода числа от ЭВМ по этому адресу.

Этот процесс записи сопровождается определением контрольной суммы информации, записываемой в устройство. Происходит это следующим образом. Коды чисел от ЭВМ, записываемые в блок памяти 1, поразрядно сравниваются с помощью блока сравнения 7 с содержанием тех ячеек блока памяти 1, в которые производят запись,

В процессе сравнения на выходах соответствующих разрядов блока сравнения 7

появляются сигналы 1 ( случае несовпадения) и О ( в случае совпадения), поступающие на соответствующие входы сумматора 4 по модулю два, где происходит их сложение с предыдущим значением результата суммы и запоминание в сумматоре 4 по модулю два.

В результате начального заполнения информацией блока памяти 1 в сумматоре 4 по модулю два накапливается поразрядная cyiviMa по модулю два всех слоев, записываемых в блок памяти 1, так как начальйое содержание блока памяти составляли нулевые слова.

В дальнейшем при записи (признак Запись - на управляющей шине 12) кодов чисел от ЭВМ в ячейки с произвольным содержанием меняются на противоположные значения те разряды контрольной суммы, хранящейся в сумматоре 4 по модулю два, которые не совпадают у считываемого и записываемого кодов чисел. При этом предполагается, что операции записи всегда предшествуют считыванию с некоторого адрса блока памяти, в который должна производиться запись. При начальном заполнении устройства считывание может не производится, так как начальное содержащие блока памяти 1- нулевое. При считывании информации сигналами от блока управления 8 производится запрет передачи информации от блока сравнения 7 в сумматор 4 по модулю два.

Для контроля хранящейся в блоке памяти 1 информации блок управления 8 по сигналу Контроль, поступающему от ЭВМ по управляющей шине 14, запрещает поступление информации в сумматор 4 по модулю два от блока сравнения 7. Одновременно с сигналом Контроль от ЭВМ поступают сигналы Поиск по управляющей шине -по управляющей шине 1О, последовательно по каждому из разрядов устройства, причем все остальные разряды маскируются кодом маски по управляющей шине 13. Тем самым на выходах индикаторов совпадения блока памяти 1 последовательно фиксируется информация, хранящаяся во всех ячейках разряда, по которому производится поиск i ,

Сумматор 2 по модулю два образует значение вертикальной суммы по модулю два информационного содержания разряда всех слоев блока памяти 1, которая с помощью коммутатора 5 сравнивается с соответствуклдим значением разряда контрольной суммы, хранящейся в сумматоре 4 по модулю два с помощью дополнительного блока сравнения 6.

При окончании цикла поиска по все разрядам дополнительным блоком сравнения 6 при несовпадении контрольной суммы, записанной и хранящейся в устройстве информации на шине 16, вырабатывается сигнал Ошибка и код результата сравнения на шине 17, Параллельно с образованием вертикальной суммы, в процессе поразрядного ассоциативного поиска происходит образование горизонтальной суммы по мо- дулю два информационного содержания каждого слова.

Это происходит следующим образом.

По сигналу Контроль блока управления 8 информация с выхода каждого индикатора совпадения блока памяти 1 поступает на соответствующие входы сумматора 3 по модулю два, который производит суммирование иввформации по модулю два с запоминанием результата.

Предполагается, что один разряд блока памяти является контрольным и дополняет до 1 сумму по модулю два информационных разрядов. Затем производится опрос состояния сумматора 3 по модулю два. В том случае, если на всех выходах сумматоров 3 оказывается сигнал 1, элемент И 9 образует сигнал отсутствия ошибки. В противном случае, при нечетном количестве ошибок в каком-либо слове на шинах 18 и 15 образуется сигнал О, сигнал ошибки и код результата суммирования- на шинах 18 с указанием адреса ошибки памяти 1.

Рассмотренные циклы контроля можно периодически использовать в качестве теста проверки хранения информации устройства, либо после каждой операции запись для проверки правильности занесения информации в устройство.

Таким образом, проверки на четность вертикальные и горизонтальные - образуют

систему ортогональных проверок на четность, с помощью которых могут быть указаны как адрес, так и разряд ошибки.

Формула Изобретения

Ассоциативное запоминающее устройство, содержащее блок управления, подключенный к блоку памяти и блоку сравнения, элемент И и управляющие шины, отличающееся тем, что, с целью упрощения устройства, оно содержит сумматоры по модулю два, коммутатор и дополнительный блок сравнения, входы первого и второго сумматоров по модулю два подключены к соответствующим выходам блока памяти, выход первого сумматора по модулю два соединен с входом коммутатора, выходы которого подключены к одним входам дополнительного блока сравнения, другие входы которого соединены с выходами третьего сумматора по модулю два, выходы второго сумматора по модулю два и блока сравнения подключены соответственно к входам элемента И и третьего сумматора по модулю два, входы блока сравнения подключены к управляющим шинам и одному из выходов блока управления, другие выходы которого соединены с входами второго и третьего сумматоров по модулю два, элемента И и коммутатора.

Источники информации, принятые во внимание при экспертизе:

1.Патент Великобритании № 1265013 М. кл. Gil С 15/00, 1972 г.

2.Патент Великобритании № 1265014 М. кл. О- 11 С 15/ОО, 1972 (проготип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Ассоциативное запоминающее устройство с самоконтролем | 1980 |

|

SU858105A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1100638A1 |

| Запоминающее устройство с само-КОНТРОлЕМ | 1979 |

|

SU836682A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1094071A1 |

| Вычислительная система | 1989 |

|

SU1777148A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1185400A1 |

| Устройство для фиксации трассы выполнения программы | 1983 |

|

SU1136170A1 |

| Оперативное запоминающее устройство с блокировкой неисправных ячеек памяти | 1981 |

|

SU1014033A1 |

| Устройство для сжатия данных при обмене между электронными вычислительными машинами | 1983 |

|

SU1118996A1 |

| Устройство для отладки специализированных микроЭВМ | 1990 |

|

SU1741135A1 |

Авторы

Даты

1977-04-25—Публикация

1975-09-01—Подача