1

Изобретение относится к автоматике и вычислительной технике и может быть использовано при реализации узлов измерительных систем,, следящих цифровых систем и устройств автоматики .

Известно устройство для сравнения двоичных чисел, содержащее элементы И-НЕ, НЕ 1.

Наиболее близким к предлагаемому являеуся устройство для сравнения двоичных чисел, содержащее п последовательно соединенных ячеек сравнения, каждая из которых состоит из элементов И-НЕ, первые входы первого и второго элементов И-НЕ каждой i-ой ячейки (,...,n) соединены с шиной i-ro разряда первого числа, а первый вход третьего элемента И-НЕ и второй вход второго элемента И-НЕ каисдой i-ой ячейки подключены к шине i-ro разряда второго числа, и в каждой i-ой ячейке выход второго элемента И-НЕ соединен со вторыми входами первого и третьего элементов И-НЕ 2.

Недостатком известных устройств является сложность,

Цель изобретения - упрощение устройства.

Поставленная цель достигается тем, что в устройстве для сравнения двоичных чисел, содержащем элементы И-НЕ, НЕ JK-триггеры, п ячеек сравнения, каждая из которых состоит из элементов И-НЕ, элемента НЕ, причем входная шина каждого i-го разряда первого из сравниваемых чисел соединена с первыми входами первого и втоtoрого элементов И-НЕ i-ой ячейки сравнения, где f 1,2,...,п, входная шина каждого i-ro разряда второго из сравниваемых чисел подключена ко второму входу первого элемента И-НЕ и к

15 первому входу третьего элемента И-НЕ i-ой ячейки сравнения, выход первого элемента И-НЕ каждой ячейки сравнения соединен со вторьл1вс входами второго и третьего элементов И-НЕ, выходы которых подключены ко входам четвертого

20 элемента И-НЕ той же ячейки сравнения, выход четвертого элемента И-НЕ каждой J-ой ячейки сравнения, где J 1,2, .,., п-1, соединен со входом элемента НЕ (+1)-ой ячейки сравнения, вы25ход элемента НЕ каждой ячейки подк.гшчен к третьему входу четвертого элемента И-НЕ той же ячейки сравнения, выход четвертого элемента И-НЕ п-ой

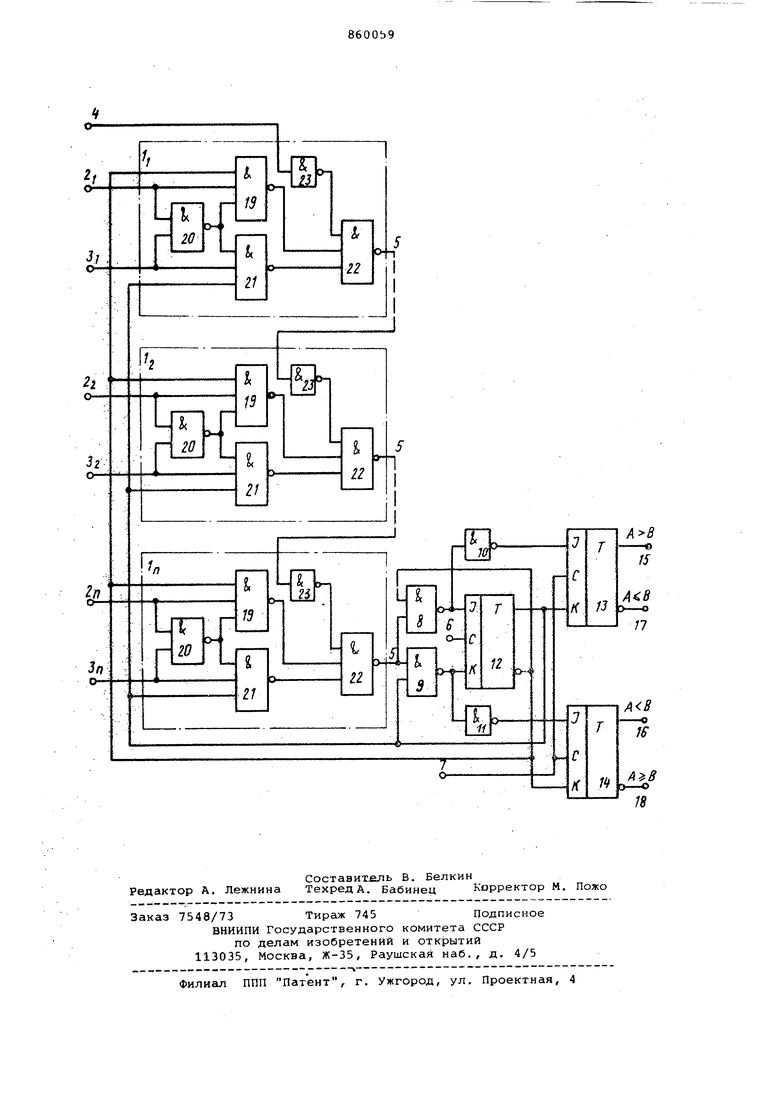

30 ячейки сравнения соединен с nepatom входами первого и второго элементов Н-НЕ, выход первого элемента И-НЕ п ключей ко входу J первого JK-тригге и через первый элемент НЕ ко входу второго К триггера, выход второго элемента И-НЕ соединен со входом К первогО К триггера и через второй элемент НЕ со входом J третьего JKтриггера, прямой выход первого JKтриггера, подключен ко входу К второго JK-триггера и к третьим входам третьихэлементов И-НЕ всех ячеек сравнения и ко второму.входу второго элементаИ-НЕ, инверсный выход первого JK-триггера соединен со вторым входом первого элемента И-НЕ, со вхо дом К третьего JK-триггера и с третьими входами вторых элементов И-НЕ всех ячеек сравнения. На чертеже приведена функциональ ная схема предлагаемого устройства. Устройство содержит ячейки 1, 1 ..., ly, сравнения входные шины 2, 2,, ...-, 2( разрядов первого числа, входные шины 3 ..., Зу, разрядов второго числа, шину 4 управления выходы 5 ячеек сравнения, шины 6 и тактовых импульсов, элементы И-НЕ 8 и 9, элементы НЕ 10 и 11, JK-тригге ры 12-14, выходные шины 15-18. Ячейка 1 сравнения включает элементы И-НЕ 19-22 и элемент НЕ 23. Устройство работает следующим образом. На шину 4 подают низкий уровень напряжения (логический нуль). Сравне ние исел производят параллельным кодом. Каждая ячейка сравнения реализует функцию, описываемую выражением .{АВ)--а-Ъ-ХСАВ)ч-1In x(AB)+Ua +BjxlABU -(.а:;4Ъ,)хСАЬ)И.АВ), где а- - t-ый разряд первого числа А; Ь - 1-ый разряд второго чисХ(АВ)- функция, реализуемая триг гером 12. На выходе ячейки 1 сравнения ly в зависимости от значения функции х(АВ реализуется функция F() или F( Значения функций F() или ) совместно со значением функции х(АВ управляют работой JK-триггеров 13 или 14.. При равенстве чисел независимо от состояния JK-триггера 12 на выходе ячейки ly,сравнения установится состояние логического нуля, которое одновременно установит состояние логической единицы на выходах элементов И-НЕ 8 и 9, вследствие чего JK-триггер 12 меняет свое состояние на противоположное по каждому поступлению тактового импульса по шине б, а оба JK-триггера 13 и 14 по поступлению тактового импульса по шине 7 устанавливаются в нулевое состояние. При неравенстве сравниваемых чисел результат сравнения старших разрядов является преобладающим по отношению ко всем результатам сравнения последующих младших разрядов. Если после установки JK-триггера 12 в нулевое состояние на выходе ячейки 1 сравнения установится состояние логической единицы, состояние логического нуля установится на гвыходе первого элемента И-НЕ 8, что запретит срабатывание JK-триггера 12 до изменения результата сравнения и установит J К-триггер 13 по поступлению тактового импульса по шине 7 в единичное состояние «{на выходной шине 15 установится состояние логической единицы). Аналогично, если , то после установки J К-триггера 12 в единичное состояние на- выходе ячейки 1. сравнения установится состояние логической единицы, состояние логического нуля установится на выходе элемента И-НЕ 9, что запретит срабатывание JK-триггера 12 до изменения результата сравнения и установит JК-триггер 14 по поступлению тактового импульс 7 в единичное состояние (на выходной шине 16 установится состояние логической единицы). На выходные шины 17 и 18 выводятся результаты сравнения А$В и соответственно. Установление состояния логической единицы.одновременно на шинах 5 и 17 говорит о равенстве сравниваемых чисел. Возможна реализация устройства с применением мультиплексоров . При реализации предлагаемого устройства на интегральных микросхемах сокращаются на 6% (с применением глультиплексоров на 34%) количество корпусов микросхем и на 11% их число входов/выходов ( с применением мультиплексоров На 35%) по сравнению с известным, что повышает его надежностные характеристики. Формула изобретения Устройство для сравнения двоичных чисел, содержащее элементы И-НЕ, НЕ, JK-триггеры, п ячеек сравнения, каждая из которых состоит из элементов И;;;; НЕ, элемента НЕ, причем входная шина каждого i-го разряда первого из сравниваемых чисел соединена с первыми входами первого и второго элементов И-НЕ 1-ой ячейки сравнения, где ,2,.,.,n, входная шина каяедого i-го разряда второго из сравниваемых чисел подключена ко второму входу первого элемента И-НЕ и к первому входу третьего элемента И-НЕ i-ой

ячейки сравнения, выход первого элемента И-НЕ каждой ячейки сравнения соединен со вторыми входами второго и третьего элементов И-НЕ, выходы которых подключены ко входам четвертого элемента И-НЕ, той же ячейки сравнения выход четвертого элемента И-НЕ каждоЛ j-ой ячейки сравнения, где ,..., г-1, соединен со входом элемента НЕ (J-tl)-oй ячейки сравнения, выход элемента НЕ каящой ячейки подключен к третьему входу четвертого элемента И-НЕ той же ячейки сравнения, отличающееся тем, что, с целью упрощения устройства, в нем выход четвертого элемента И-НЕ п-ой ячейки сравнения соединен с первыми входами первого и второго элементов И-НЕ, выход первого элемента И-НЕ подключен ко входу J первого. J К-триггера и че- рез первый элемент НЕ ко входу J второго J К-триггера, выход второго елвмента И-НЕ соединен со входом К первого JK-триггера, и через второй элемент НЕ со входом J третьего JK-триггера, прямой выход первого JK-триггера, подключен ко входу К второго JK-триггера и к третьим входам третьих элементов И-НЕ всех ячеек сравнения и ко второму входу второго элемента И-НЕ,инверсный выход первого JK-триггера соединен со вторым входом первого элемента И-НЕ, со входом К третьего J К-триггера и с третьими входами вторых элементов И-НЕ всех ячеек сравнения.

Источники информации, принятые во внимание при экспертизе - 1. Авторское свидетельство СССР 628486, кл. G 06 F 7/02, 1976.

2. Авторское свидетельство СССР №631914, кл. G 06 F 7/02, 1976 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сравнения -разрядных чисел | 1976 |

|

SU641443A1 |

| Программируемое запоминающее устройство | 1985 |

|

SU1282219A1 |

| Логическая ячейка для ассоциативного запоминающего устройства | 1981 |

|

SU980162A1 |

| Многофункциональное вычислительное устройство | 1985 |

|

SU1293727A1 |

| Устройство для сравнения чисел | 1979 |

|

SU824192A1 |

| МНОГОРАЗРЯДНЫЙ УПРАВЛЯЕМЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ | 1996 |

|

RU2119248C1 |

| Вероятностный коррелометор | 1980 |

|

SU892449A1 |

| АССОЦИАТИВНЫЙ ПРОЦЕССОР | 1988 |

|

SU1521118A1 |

| Преобразователь кода в период повторения импульсов | 1978 |

|

SU744976A1 |

| УСТРОЙСТВО ДЛЯ ВЫРАВНИВАНИЯ ПОРЯДКОВ m ДВОИЧНЫХ ЧИСЕЛ | 2012 |

|

RU2503991C1 |

Авторы

Даты

1981-08-30—Публикация

1979-06-08—Подача