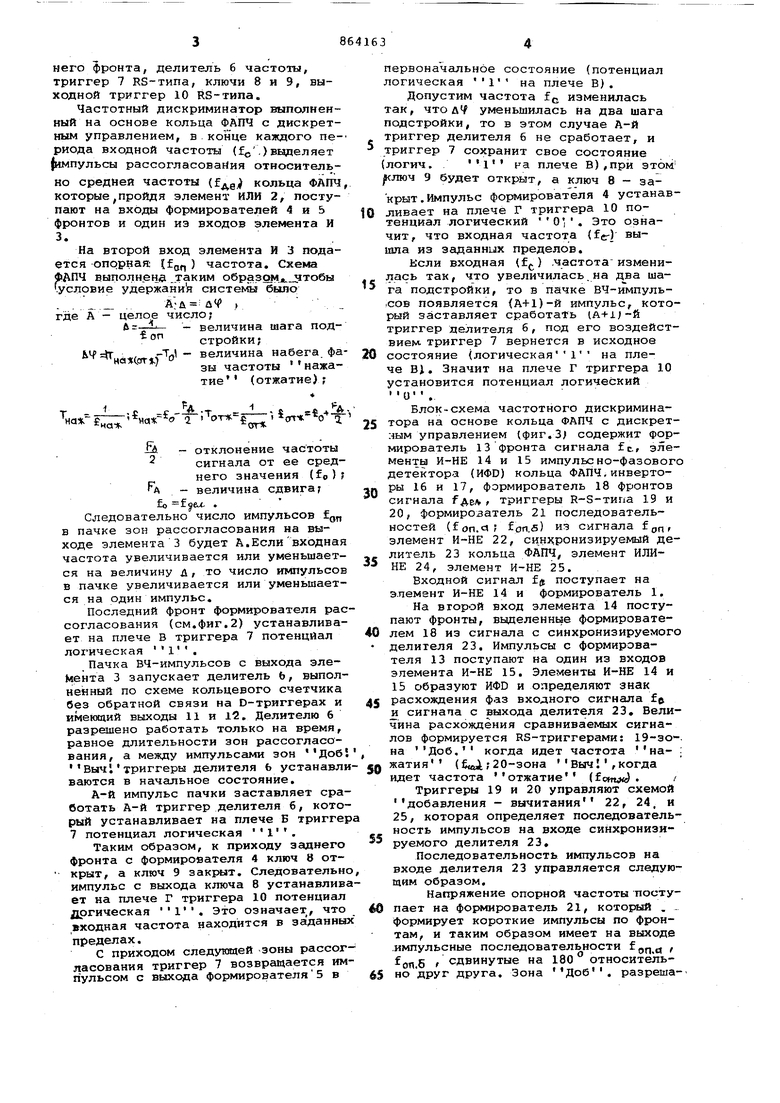

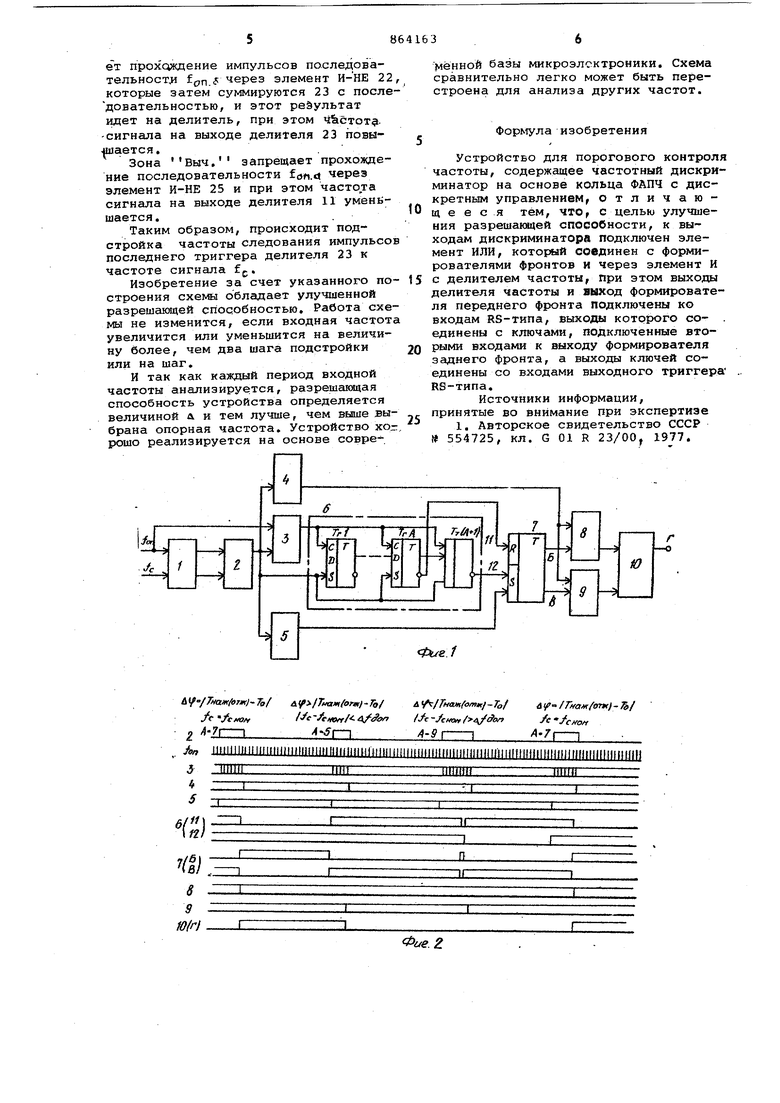

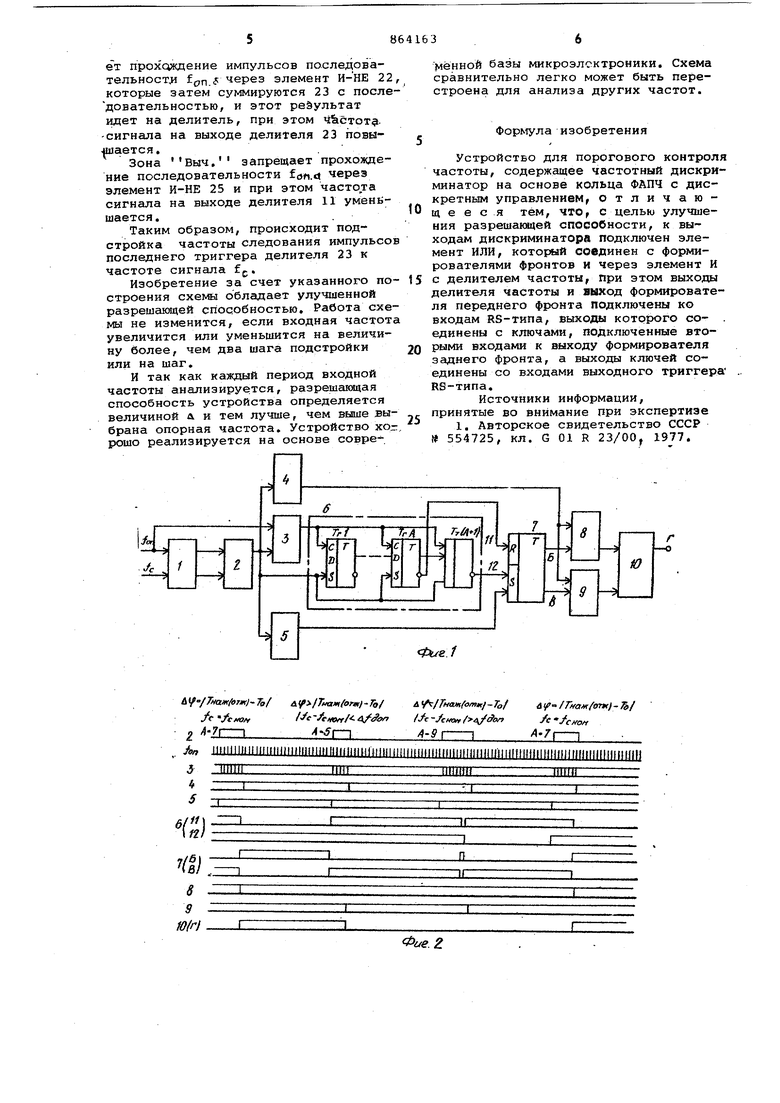

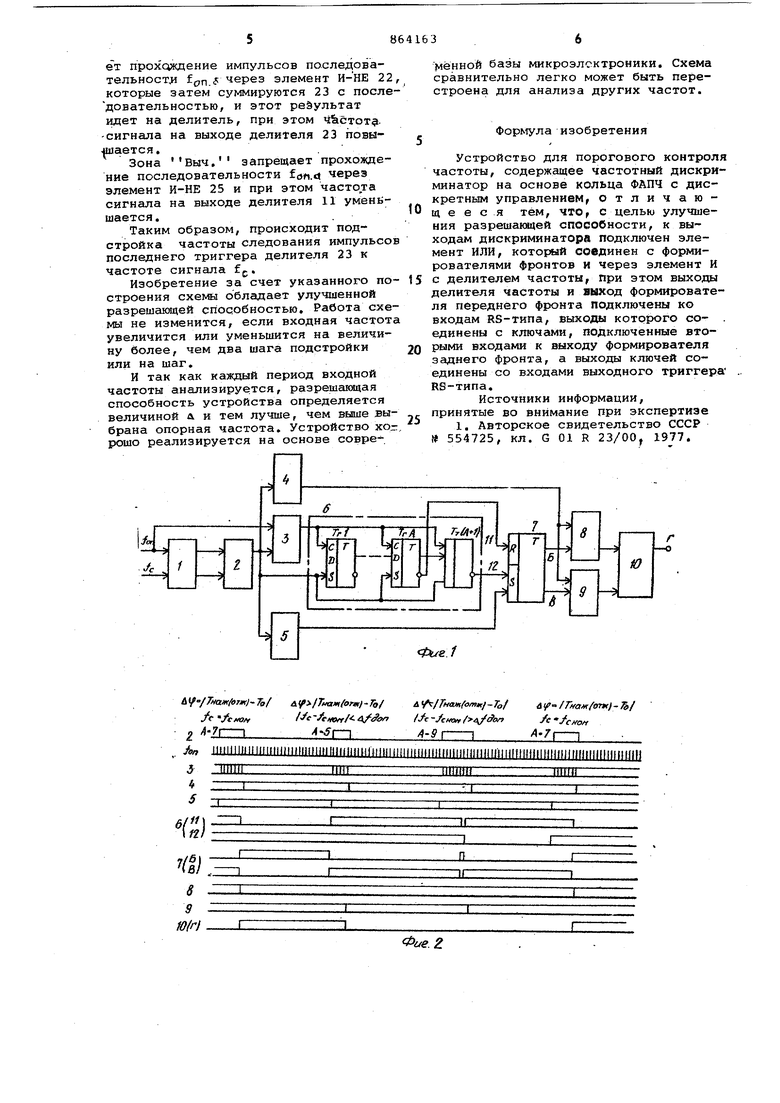

Изобретение относится к измерител ной технике, и может быть использован в различных системах контроля средст связи, в частности, для контроля пра вильности установки частот возбудителя. Известно устройство для контролячастоты, содержащее частотный детектор, двухполярный источник питания, усилитель постоянного тока, к выходу которого через резисто л подключены базы двух транзисторов разного типа (Проводимости с индикаторами в колек торных цепях, причем вход усилителя постоянного тока через одни резисторы подключен к двум разнопояяриым вы ходам частотного .детектора, а ,з другие резисторы подключен к коллекторам транзисторов {. . однако,в ряде случаеа, например при контроле -частот возбудителя сигналов частотной телеграфии с малыми сдвигами, .разретиающар. способность известного устройства недостаточна, а при необходимости контроля еще и широкого диапазона частот устройство усложняется. Цель изобретения - улучшение раз:решающей способности. Поставленная цель достигается, тем, что в устройстве,содержащем частотный дискриминатор, выполненный на ос.нове кольца ФАПЧ с дискретным управлением, к выходам дискриминатора подключен элемент ИЛИ, который соединен с формирователями фронтов и через элемент И с делителем частоты, выходы делителя частоты и выход формирователя переднего фронта при этом подключены ко входам триггера RS-типа . выходы которого соединены с ключами, подключенные входами к формирователю заднего фронта, а выходы ключей соединены со входами выходного триггера RS-типа. На фиг.1 представлена блок-схема устройства для порогового контроля частоты,- на|.фиг,2 - эпюры напряжений в различных точках схемы, прясняюцие работу устройства; на фиг.З- блоксхема частотного дискриминатора на основе кольца ФАПЧ с дискретным управлением. Устройство для порогового контроля частоты содержит частотный дискриминатор 1 на основе кольца фАПЧ с дискретным управлением, элемент ИЛИ 2, элемент ИЛИ 3, формирователь 4 заднего фронта, формирователь 5 переднего фронта, делитель 6 частоты, триггер 7 RS-типа, ключи 8 и 9, выходной триггер 10 RS-типа. Частотный дискриминатор выполненный на основе кольца ФАПЧ с дискретным управлением, в конце каждого периода входной частоты (.выделяет пульсы рассогласования относительно средней частоты (дд кольца ФАПЧ которые,пройдя элемент ИЛИ 2, поступают на входы формирователей 4 и 5 фронтов и один из входов элемента И На второй вход элемента И 3 подается опорная; fg ) частота. Схема ФАПЧ выполнена „таким образом г.чтобы условие удержаний системы было . . - . ) где А - целое число; - величина шага стройки; fcif Ha«faTitf величина набега, фа нажазы частоты (отжатие) ,« на crr-«,V-СД - отклонение частоты сигнала от ее среднего значения (fo)f РА - величина сдвига; fo f jej- . Следовательно число импульсов fgn в пачке зон рассогласования на выходе элемента 3 будет А.Есливходная частота увеличивается или уменьшается на величину д, то число импульсов в пачке увеличивается или уменьшается на один импульс. Последний фронт формирователя рас согласования (см,фиг,2) устанавливает на плече В триггера 7 потенциал логическая . Пачка ВЧ-импульсов с выхода элемента 3 запускает делитель Ь, выполненный по схеме кольцевого счетчика без обратной связи на D-триггерах и имеккций выходы 11 и 12. Делителю 6 разрешено работать только на время, равное длительности зон рассогласования, а между импульсами зон Доб Выч. триггеры делителя Ь устанавл ваются в начальное состояние, А-й импульс пачки заставляет сра ботать А-й триггер делителя 6, кото рый устанавливает на плече Б тригге 7 потенциал логическая . Таким образом, к приходу заднего фронта с формирователя 4 ключ 8 открыт, а ключ 9 закрыт. Следовательн импульс с выхода ключа 8 устанавлив ет на плече Г триггера 10 потенциал логическая 1, Это означает,, что входная частота находится в заданны пределах. С приходом следунлдей зоны рассог ласования триггер 7 возвращается им пульсом с выхода формирователя 5 в первоначальное состояние (потенциал логическая ч- на плече В), Допустим частота f, изменилась так, что д уменьшилась на два шага подстройки, то в этом случае А-й триггер делителя 6 не сработает, и триггер 7 сохранит свое состояние логич. ««ц ра плече В) ,при этом люч 9 будет открыт, а ключ 8 - закрыт. Импульс формирователя 4 устанавливает на плече Г триггера 10 потенциал логический О Это означит, что входная частота (fcr) вышла из заданных пределов, Ксли входная (f,) .частота изменилась так, что увеличилась.на два щага подстройки, то в пачке ВЧ-импуль.сов появляется А+1)-й импульс, который заставляет сработать (А-и;-й триггер делителя б, под его воздействием, триггер 7 вернется в исходное состояние (логическая на плече Hi, Значит на плече Г триггера 10 установится потенциал логический О, Блок-схема частотного дискриминатора на основе кольца ФАПЧ с дискретным управлением (фиг,3) содержит формирователь 13 фронта сигнала ft, элементы И-НЕ 14 и 15 импульсно-фазового детектора (МФО) кольца ФАПЧ,инверторы 16 и 17, формирователь 18 фронтов сигнала f де/v t триггеры R-S-типа 19 и 20, формирователь 21 последовательностей (fon.a; foas) из сигнала fon элемент И-НЕ 22, синхронизируемый делитель 23 кольца ФАПЧ, элемент ИЛИНЕ 24, элемент И-НЕ 25. Входной сигнал fj поступает на э.пемент И-НЕ 14 и формирователь 1. На второй вход элемента 14 поступают фронты, выделенные формирователем 18 из сигнала с синхронизируемого делителя 23, Импульсы с формирователя 13 поступают на один из входов элемента И-НЕ 15, Элементы И-НЕ 14 и 15 образуют ИФП и определяют знак расхождения фаз входного сигнала f и сигнапа с выхода делителя 23, Величина расхождения сравниваемых сигналов формируется RS-триггерами; 19-зо-. Доб. когда идет частота нажатия (aji;20-30Ha ВычI,когда идет частота отжатие (fcwjij / Триггеры 19 и 20 управляют схемой добавления - вычитания 22, 24. и 25, которая определяет последовательность импульсов на входе синхронизируемого делителя 23, Последовательность импульсов на входе делителя 23 управляется следующим образом. Напряжение опорной частоты поступает на формирователь 21, который , . формирует короткие импульсы по фронтам, и таким образом имеет на выходе .импульсные последовательности .e t оп.б /сдвинутые на 180 относительно друг друга. Зона Доб, разрешает прохождение импульсов по.следовательностл fpn.f через элемент И-НЕ 22, которые затем суммируются 23 с последовательностью, и этот результат идет на делитель, при этом чб1стотэ.

-сигнала на выходе делителя 23 позылшается.

Зона Выч. запрещает прохождение последовательности fefi.«t через элемент И-НЕ 25 и при этом частота сигнала на выходе делителя 11 уменьшается.

Таким образом, происходит подстройка частоты следования импульсов последнего триггера делителя 23 к частоте сигнала f.

Изобретение за счет указанного построения схема обладает улучшенной разрешающей способностью. Работа схемы не изменится, если входная частота увеличится или уменьшится на величину более, чем два шага подстройки или на шаг.

И так как каждый период входной частоты анализируется, разрешающая способность устройства определяется величиной А и тем лучше, чем №ше выбрана опорная частота. Устройство хог

jlJOLna - -,--- - -

. . .. / OinO

рошо реализируется на основе совреira j m ги |1 Г Г

менной базы микроэлектроники. Схема сравнительно легко может быть перестроена для анализа других частот.

Формула изобретения

Устройство для порогового контроля частоты, содержащее частотный дискриминатор на основе кольца ФАПЧ с дискретным управлением, отличающееся тем, что, с целый улучшения разрешакядей способности, к выходам дискриминатора подключен элемент ИЛИ, которой соединен с формирователями фронтов и через элемент И с делителем частоты, при этом выходы делителя частоты и выход формирователя переднего фронта подключены ко входам RS-типа, выходы которого соединены с ключами, подключенные вторыми входами к выходу формирователя заднего фронта, а выходы ключей соединены со входами выходного триггера RS-типа.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР I 554725, кл. G 01 R 23/00, 1977. ЧТ |

& //Тна/я/Ьг с1 То/ & f /Ttni n/or il7it/& 1Тнаж(от,1-То{A(f /Гна/х/огк)ffffMOftIfffcuofr/ u/ on l(-fcmHf A fofifcfcHoH

ue.Z

Авторы

Даты

1981-09-15—Публикация

1979-11-11—Подача