У/7р0б/7(#ме

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство компенсации сдвига частот | 1985 |

|

SU1316097A2 |

| Цифровой управляемый генератор | 1986 |

|

SU1401553A1 |

| УСТРОЙСТВО АВТОПОДСТРОЙКИ ФАЗЫ СИГНАЛОВ | 1991 |

|

RU2027301C1 |

| Устройство синхронизации в одночастотных многоканальных адресных системах с временным разделением каналов | 1989 |

|

SU1811018A1 |

| Двухступенчатый регенератор | 1983 |

|

SU1197117A1 |

| Устройство для измерения преобладаний двоичных сигналов | 1985 |

|

SU1246396A1 |

| Устройство цифровой фазовой автоподстройки частоты | 1982 |

|

SU1125748A1 |

| Устройство для программного управления положением вала электродвигателя | 1980 |

|

SU907512A1 |

| Устройство тактовой синхронизации | 1980 |

|

SU906016A1 |

| Двухступенчатый регенератор | 1978 |

|

SU726668A1 |

Изобретение относится к импульсной технике и может быть использовано для повышения точности подстройки цифрового управляемого генератора. Цель изобретения достигается за счет введения в устройство первого фильтра 11 нижних частот, второго блока 7 добавления-вычитания импульсов, делителя 8 частоты, фазового дискриминатора 9 и фильтра 10 нижних частот, а также первого 12 и второго 13 формирователей опорного сигнала и новых функциональных связей. Кроме того, устройство содержит опорный генератор 1, первые блок 2 добавления-исключения импульсов, делитель 3 частоты, фазовый дискриминатор 4, а также первый 6 и второй 11 управляемые генераторы. Повышение точности подстройки достигается за счет последовательного включения двух делителей частоты с дробными коэффициентами деления, образованными кольцами ФАП 4, и выбором коэффициентов делений в первом и втором делителях частоты соответственно равными -1 и +1, что позволяет в п раз по сравнению с устройством-прототипом повысить точность подстройки. 3 ил. (Л с

-:№

ГТ -Г/ТЫЖЦ

t w ww-eiLiiinaiiii iJ1 I

,.3 ф

fa/Mi

Ш«Д

XI

ь

00

го

XI

Фиг 1

Изобретение относится к импульсной технике и может быть использовано в цифровых устройствах синхронизации и синтезаторах частот.

Цель изобретения - повышение точности подстройки фазы цифрового управляемого генератора.

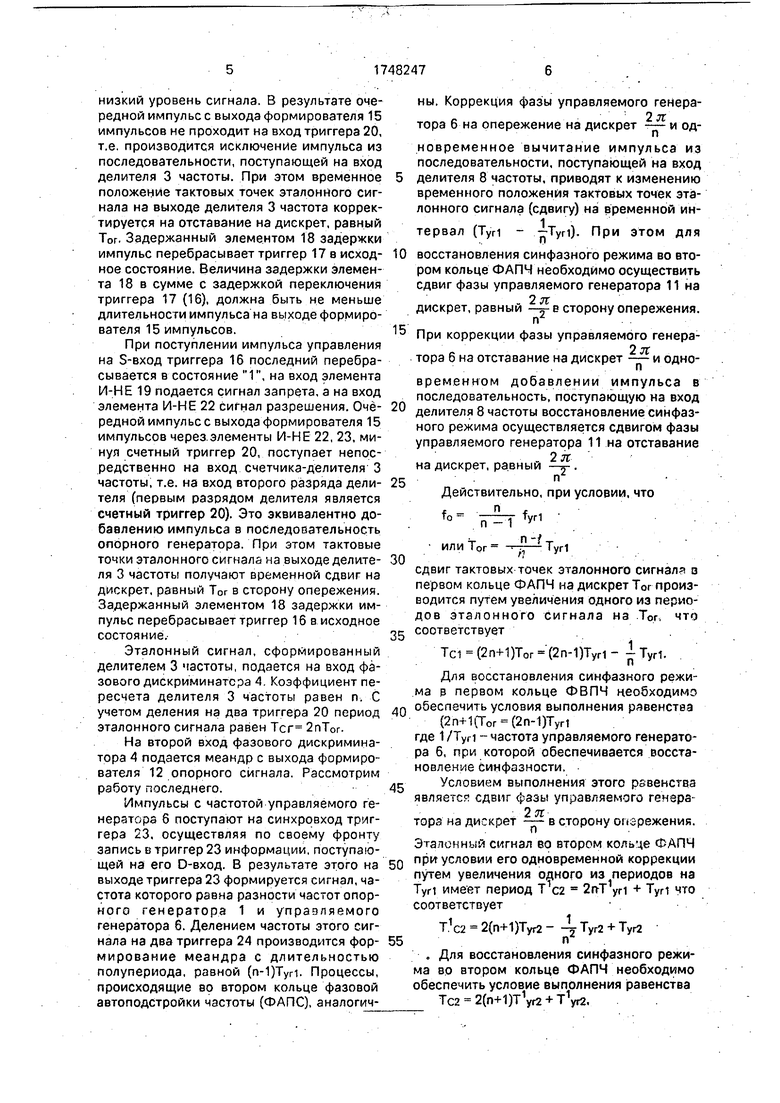

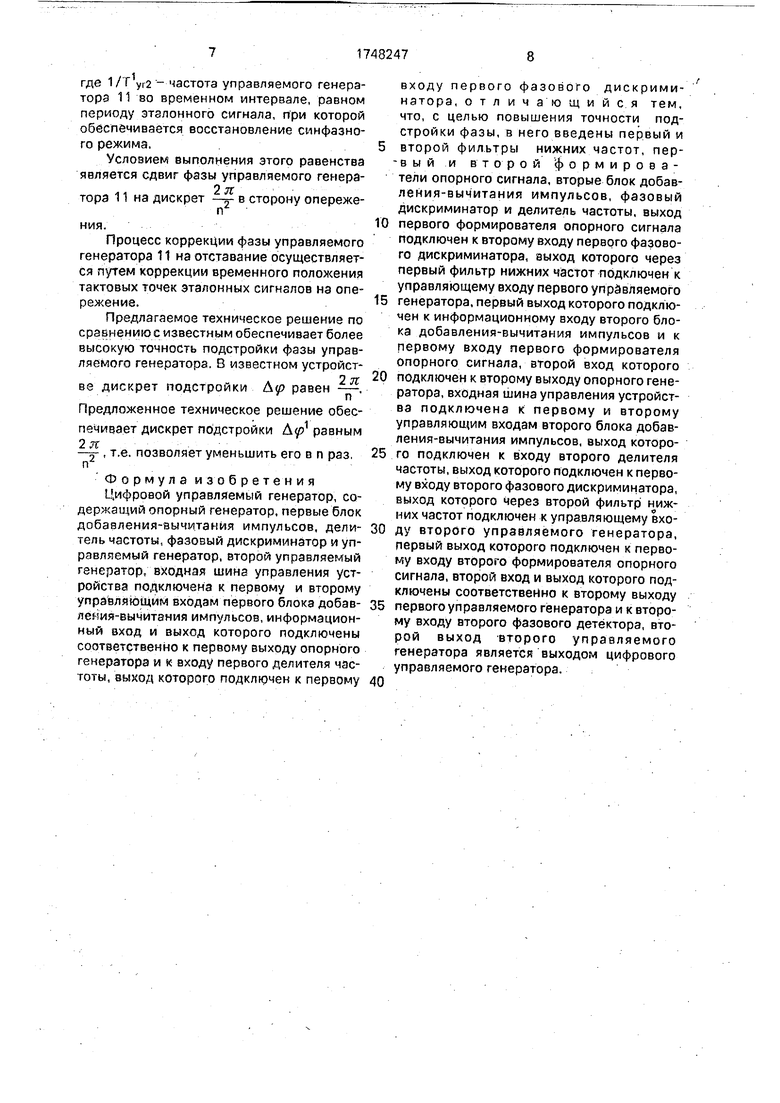

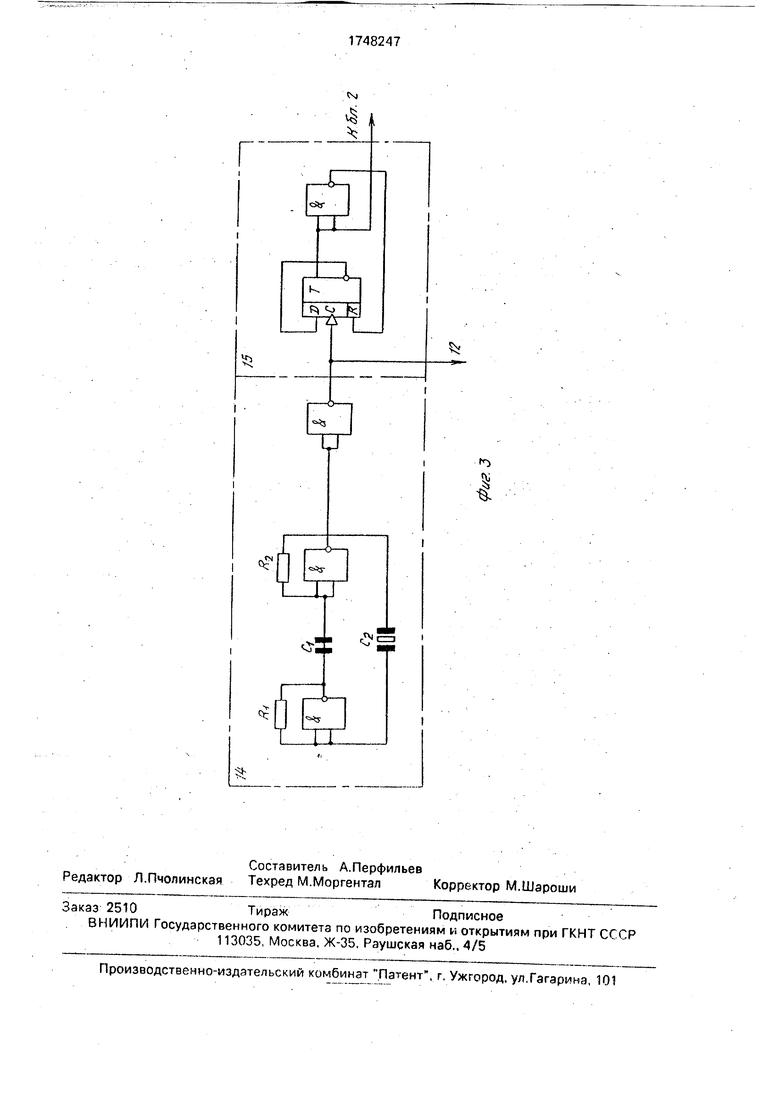

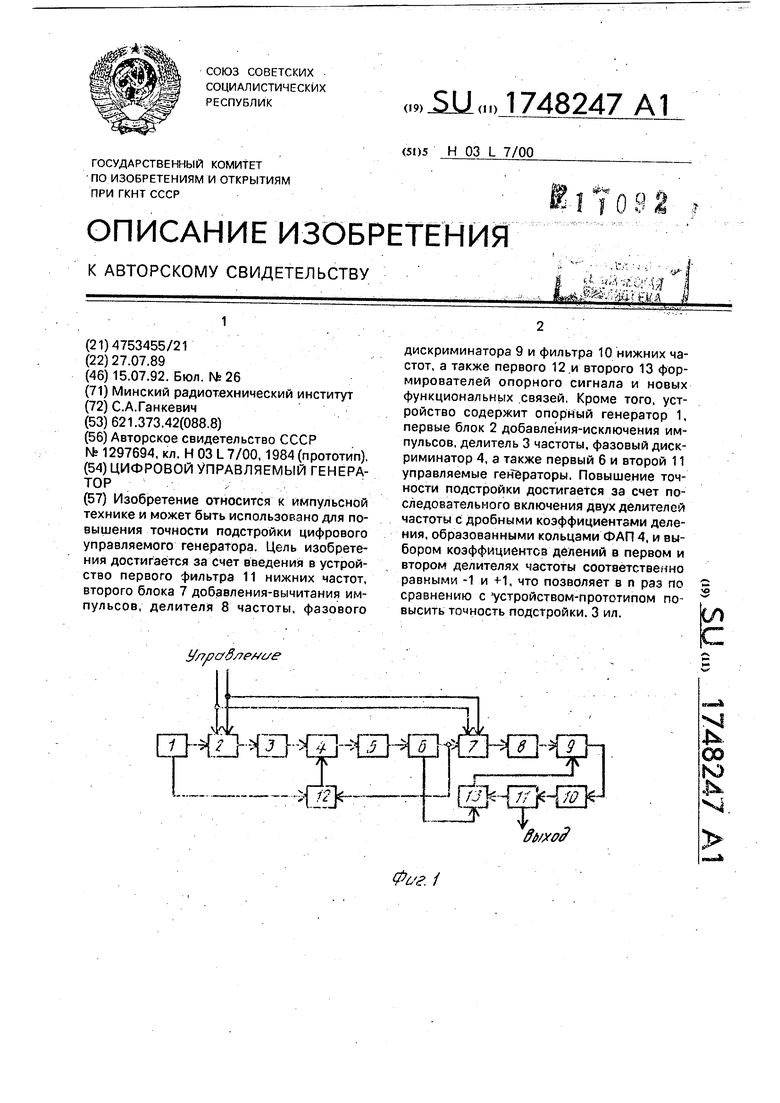

На фиг. 1 приведена функциональная схема цифрового управляемого генератора; на фиг. 2 - функциональная схема блока добавления - вычисления импульсов и формирователя опорного сигнала; на фиг. 3 - схема опорного генератора.

Цифровой управляемый генератор содержит опорный генератор 1, первый блок

2добавления-вычитания импульсов, первый делитель 3 частоты, первый фазовый дискриминатор 4, первый фильтр 5 нижних частот, первый управляемый генератор 6, второй блок 7 добавления-вычитания импульсов, второй делитель 8 частоты, второй цифровой дискриминатор 9, второй.фильтр 10 нижних частот, второй управляемый генератор 11, первый 12 и второй 13 формирователи опорного сигнала.

Первый выход опорного генератора 1 подключен к информационному входу первого блока 2 добавления-вычитания импульсов, выход которого через первый делитель

3частоты подключен к первому входу первого фазового дискриминатора 4, выход которого через первый фильтр 5 нижних частот подключен к управляющему входу первого управляемого генератора 6, первый выход которого подключен к информационному входу второго блока 7 добавления-вычитания импульсов и к первому входу первого формирователя 12 опорного сигнала, выход и второй вход которого подключе- ны соответственно ко второму входу первого фазового дискриминатора 4 и ко второму выходу опорного генератора 1. Выход второго блока 7 добавления-вычитания импульсов подключен через второй делитель 8 частоты к первому входу второго фазового дискриминатора 9. второй вход которого подключен к выходу второго формирователя 13 опорного сигнала. Выход второго фазового дискриминатора 9 подключен через второй фильтр 10 нижних частот к управляющему входу второго управляемого генератора 11, первый выход которого подключен к первому входу второго формирователя 13 опорного сигнала, второй вход которого подключен ко второму выходу первого управляемого генератора 6. Первые и вторые управляющие входы первого 2 и второго 7 блоков добавления-вычитания импульсов попарно объединены и образуют входную шину управления устройства, выходом которого является второй выход второго управляемого генератора 11. Каждый из блоков 2 и 7 добавления-вычитания импульсов содержит задающий генератор 14, формирователь 15, образующие генератор 1, первый 16 и второй 17 RS-триг- геры, элемент 18 задержки, первый элемент И-НЕ 19, счетный триггер 20, второй 21, третий 22 и четвертый 23 элементы И-НЕ.

0 S-входы первого 16 и второго 17 RS-тригге- ров являются соответственно первым и вторым управляющими входами блока 2 (7) добавления-вычитания импульсов, информационный вход которого подключен к первым входам второго 21 и третьего 22

5 элементов И-НЕ и через элемент 18 задержки к входам первого 16 и второго 17 RS- триггеров, инверсные выходы которых подключены соответственно ко второму и третьему входам первого элемента И-НЕ 19, выход которого подключен ко входу счетно0 го триггера 20, выход которого подключен ко второму входу второго элемента И-НЕ 21. Прямой выход первого RS-триггера 16 и инверсный выход второго RS-триггера 17 подключены соответственно ко второму входу

5 третьего элемента И-НЕ 22 и к третьему входу второго элемента И-НЕ 21, выходы которых подключены соответственно к первому и второму входам четвертого элемента И-НЕ 23 выход которого является выходом

0 блока 2 (7) добавления-вычитания импульсов.

Каждый из формирователей 12 и 13 опорного сигнала (фиг. 2) содержит D-триг- гер 23 и счетный триггер 24. Первым и вто5 рым входами формирователя 12 (13) опорного сигнала являются соответственно синхровход и D-вход D-триггера 23, выход которого подключен ко входу счетного триггера 24, выход которого является выходом

0 формирователя 12 (13) опорного сигнала.

Опорный генератор 1 (фиг. 3) содержит последовательно включенные задающий генератор 14 и формирователь 15 импульсов, выходы которых являются соответственно

5 вторым и первым выходами опорного генератора 1.

Цифровой управляемый генератор работает следующим образом,

Управление фазой производится с по0 мощью импульсов, поступающих на S-входы триггеров 16, 17, блока 2 добавления-вычитания импульсов, и входь1 соответствующих триггеров блока 7 добавления-вычитания импульсов. При поступле5 нии импульса управления на S-вход триггера 17, последний перебрасывается в состояние 1 и с его инверсного выхода на входы элементов И-НЕ 19 и 21 подается

низкий уровень сигнала. В результате очередной импульс с выхода формирователя 15 импульсов не проходит на вход триггера 20, т.е производится исключение импульса из последовательности, поступающей на вход делителя 3 частоты. При этом временное положение тактовых точек эталонного сигнала на выходе делителя 3 частота корректируется на отставание на дискрет, равный Тог. Задержанный элементом 18 задержки импульс перебрасывает триггер 17 в исходное состояние. Величина задержки элемента 18 в сумме с задержкой переключения триггера 17 (16), должна быть не меньше длительности импульса на выходе формирователя 15 импульсов.

При поступлении импульса управления на S-вход триггера 16 последний перебрасывается в состояние 1, на вход элемента И-НЕ 19 подается сигнал запрета, а на вход элемента И-НЕ 22 сигнал разрешения. Очередной импульс с выхода формирователя 15 импульсов через элементы И-НЕ 22, 23, минуя счетный триггер 20, поступает непосредственно на вход счетчика-делителя 3 частоты, т.е. на вход второго разряда делителя (первым разрядом делителя является счетный триггер 20). Это эквивалентно добавлению импульса в последовательность опорного генератора. При этом тактовые точки эталонного сигнала на выходе делителя 3 частоты получают временной сдвиг на дискрет, равный Т0г в сторону опережения. Задержанный элементом 18 задержки импульс перебрасывает триггер 16 в исходное состояние.

Эталонный сигнал, сформированный делителем 3 частоты, подается на вход фазового дискриминатора 4 Коэффициент пересчета делителя 3 частоты равен п. С учетом деления на два триггера 20 период эталонного сигнала равен Тсг 2пТ0г.

На второй вход фазового дискриминатора 4 подается меандр с выхода формирователя 12 опорного сигнала. Рассмотрим работу последнего.

Импульсы с частотой управляемого генератора 6 поступают на синхровход триггера 23, осуществляя по своему фронту запись в триггер 23 информации, поступающей на его D-вход. В результате этого на выходе триггера 23 формируется сигнал, частота которого равна разности частот опорного генератора 1 и управляемого генератора 6. Делением частоты этого сигнала на два триггера 24 производится формирование меандра с длительностью полупериода, равной (n-1)Tyri. Процессы, происходящие во втором кольце фазовой автоподстройки частоты (ФАПС), аналогичны. Коррекция фазы управляемого генератора 6 на опережение на дискрет - и одновременное вычитание импульса из последовательности, поступающей на вход делителя 8 частоты, приводят к изменению временного положения тактовых точек эталонного сигнала (сдвигу) на временной интервал (ТУг1 - -Туп). При этом для

восстановления синфазного режима во втором кольце ФАПЧ необходимо осуществить сдвиг фазы управляемого генератора 11 на

дискрет, равный -Ґв сторону опережения, гг

При коррекции фазы управляемого генера2 л тора 6 на отставание на дискрет - и одновременном добавлении импульса в последовательность, поступающую на вход делителя 8 частоты восстановление синфазного режима осуществляется сдвигом фазы управляемого генератора 11 на отставание

. 2л на дискрет, равный -я-.

п Действительно, при условии, что

П

ПЛ

-г Vi

1

0

5

0

5

0

5

или Тог n-f

п

Туг1

сдвиг тактовых точек эталонного сигнал з первом кольце ФАПЧ на дискрет TQI производится путем увеличения одного из перио- дов эталонного сигнала на Т0г что соответствует

ТС1 (2п+1)Тог (2п-1)ТУг1 - 1 ТУг1.

Для восстановления синфазного режима в первом кольце ФВПЧ необходимо обеспечить условия выполнения равенства

(2п-ИСГог-(2п-1)ТУг1

где 1 /ТУг1 - частота управляемого генератора 6, при которой обеспечивается восстановление синфазности.

Условием выполнения этого равенства являете 1 сдвиг фазы управляемого гечзра

торз ча дискрет -- в сторону опережения.

Эталонный сигнал во втором коль-де ФАПЧ при условии его одновременной коррекции путем увеличения одного из периодов на ТУг1 имеет период Т1с2 2ггТ yri + Tyri что соответствует

Т с2

2(п+1)Туг2 - Л Туг2 + Туг2

п

. Для восстановления синфазного режима во втором кольце ФАПЧ необходимо обеспечить условие выполнения равенства

ТС2 2(п+1)Т1уг2 + Т1уг2.

где 1/Г yi2 частота управляемого генератора 11 во временном интервале, равном периоду эталонного сигнала, при которой обеспечивается восстановление синфазного режима.

Условием выполнения этого равенства является сдвиг фазы управляемого генератора 11 на дискрет -в- в сторону опереже- п

ния.

Процесс коррекции фазы управляемого генератора 11 на отставание осуществляется путем коррекции временного положения тактовых точек эталонных сигналов на опережение.

Предлагаемое техническое решение по сравнению с известным обеспечивает более высокую точность подстройки фазы управляемого генератора. В известном устройстве дискрет подстройки Д# равен -. Предложенное техническое решение обеспечивает дискрет подстройки равным

2 ч

-т}-, т.е. позволяет уменьшить его в п раз,

гг

Формула изобретения Цифровой управляемый генератор, содержащий опорный генератор, первые блок добавления-вычитания импульсов, делитель частоты, фазовый дискриминатор и управляемый генератор, второй управляемый генератор, входная шина управления устройства подключена к первому и второму управляющим входам первого блока добавления-вычитания импульсоа, информационный вход и выход которого подключены соответственно к первому выходу опорного генератора и к входу первого делителя частоты, выход которого подключен к первому

входу первого фазового дискриминатора, отличающийся тем, что, с целью повышения точности подстройки фазы, в него введены первый и

второй фильтры нижних частот, пер- -вый и второй формирова- тели опорного сигнала, вторые блок добавления-вычитания импульсов, фазовый дискриминатор и делитель частоты, выход

первого формирователя опорного сигнала подключен к второму входу первого фазового дискриминатора, выход которого через первый фильтр нижних частот подключен к управляющему входу первого управляемого

генератора, первый выход которого подключен к информационному входу второго блока добавления-вычитания импульсов и к первому входу первого формирователя опорного сигнала, второй вход которого

подключен к второму выходу опорного генератора, входная шина управления устройства подключена к первому и второму управляющим входам второго блока добавления-вычитания импульсов, выход которого подключен к входу второго делителя частоты, выход которого подключен к первому входу второго фазового дискриминатора, выход которого через второй фильтр нижних частот подключен к управляющему входу второго управляемого генератора, первый выход которого подключен к первому входу второго формирователя опорного сигнала, второй вход и выход которого подключены соответственно к второму выходу

первого управляемого генератора и к второму входу второго фазового детектора, второй выход второго упрааляемого генератора является выходом цифрового управляемого генератора.

Управление

N5

Јfr28W.l

Г

ч

ъ

I

| Авторское свидетельство СССР № 1297694, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-07-15—Публикация

1989-07-27—Подача