113

Изобретение относится к электросвязи и может использоваться в системах передачи дискретной информации по радиоканалам для осуществления тактовой синхронизации,

Цель изобретения - повышение помехоустойчивости путем снижения воздействия случайных фазовых сдвигов в радиоканале.

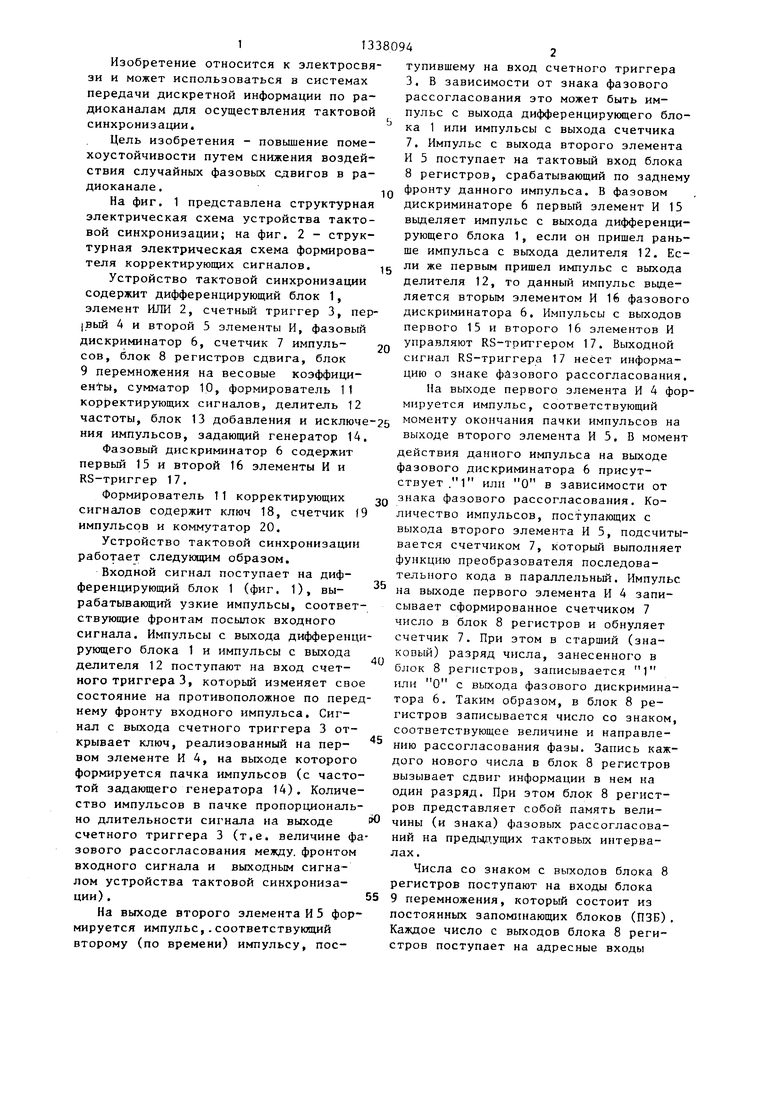

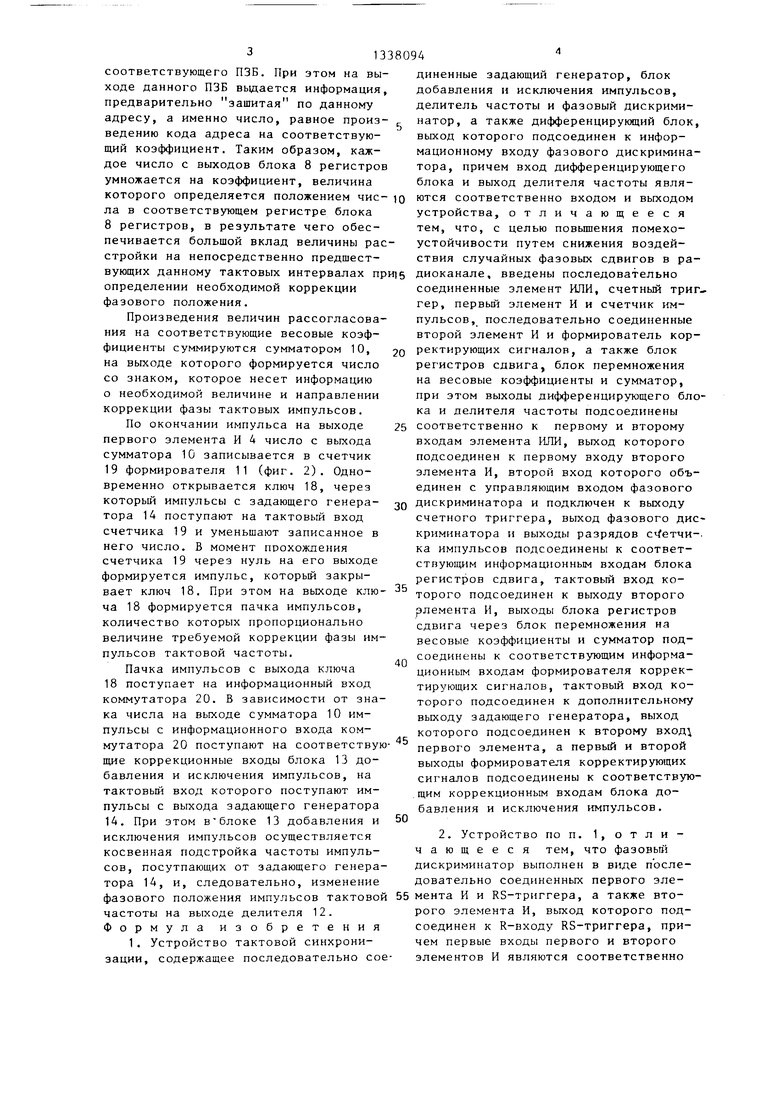

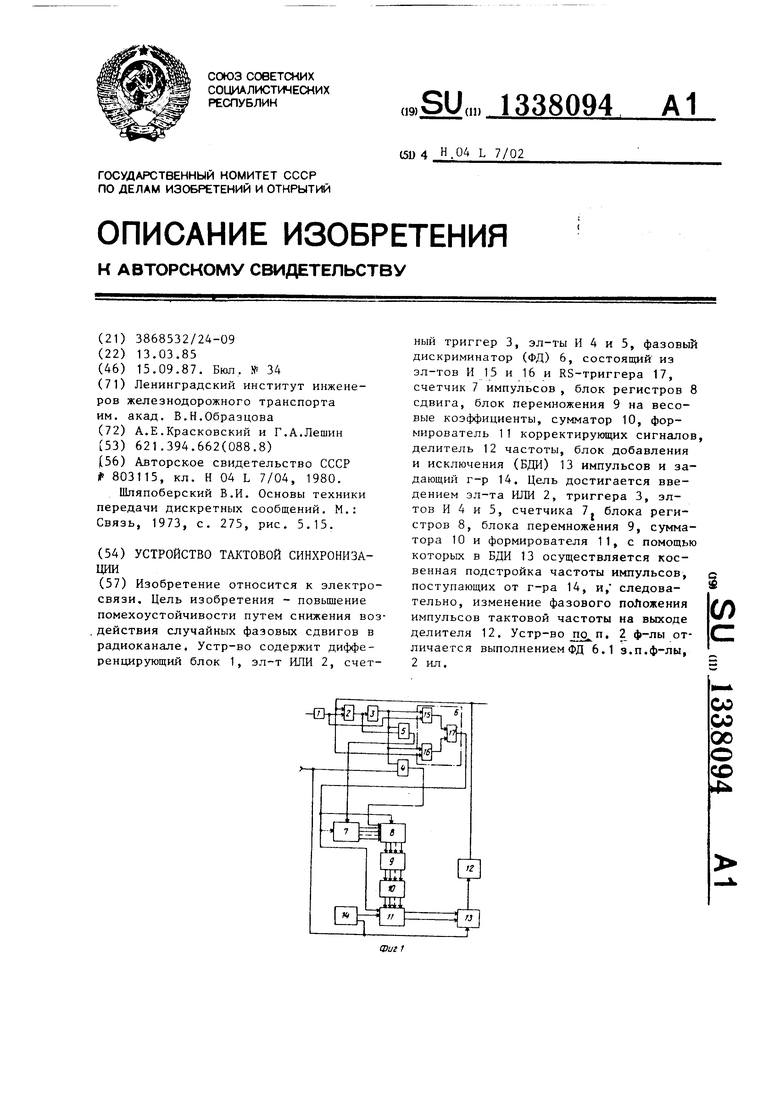

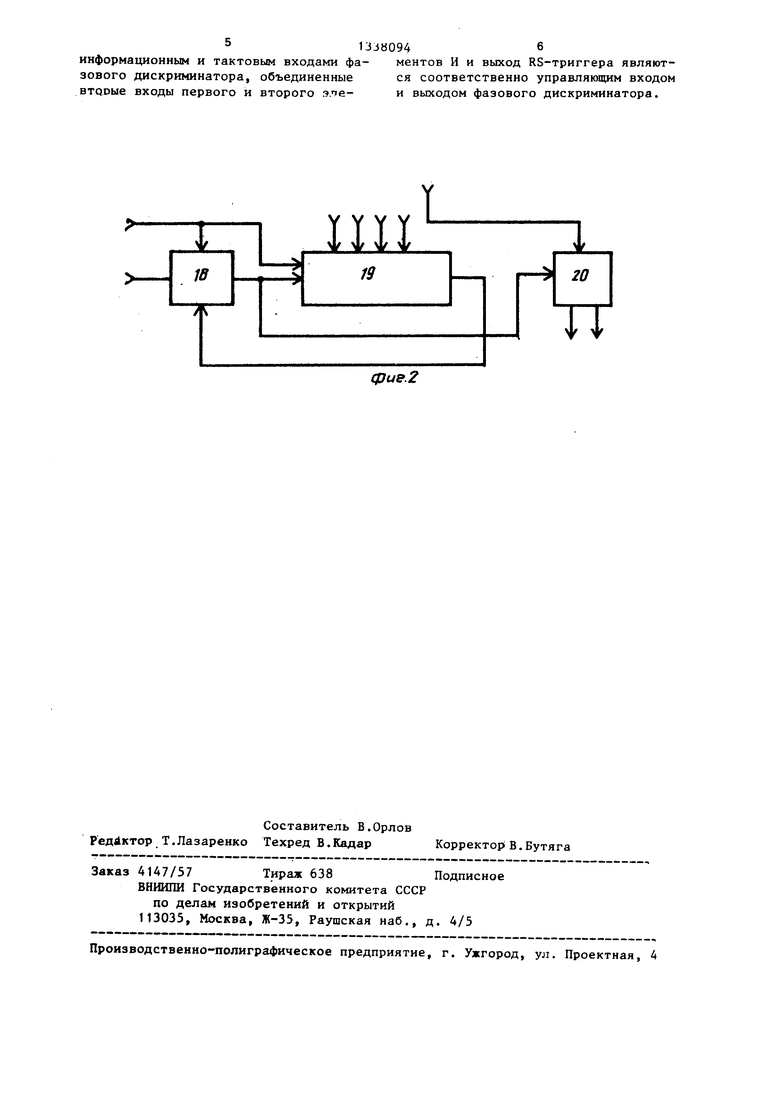

На фиг. 1 представлена структурная электрическая схема устройства тактовой синхронизации; на фиг. 2 - структурная электрическая схема формирователя корректирующих сигналов.

Устройство тактовой синхронизации содержит дифференцирующий блок 1, элемент ИЛИ 2, счетный триггер 3, пер |вый 4 и второй 5 элементы И, фазовый дискриминатор 6, счетчик 7 импуль- сов, блок 8 регистров сдвига, блок 9 перемножения на весовые коэффициенты, сумматор 10, формирователь 11 корректирующих сигналов, делитель 12 частоты, блок 13 добавления и исключе ния импульсов, задающий генератор 14.

Фазовый дискриминатор 6 содержит первый 15 и второй 16 элементы И и RS-триггер 17.

Формирователь 11 корректирующих

сигналов содержит ключ 18, счетчик 19

импульсов и коммутатор 20.

Устройство тактовой синхронизации работает следующим образом.

Входной сигнал поступает на дифференцирующий блок 1 (фиг. 1), вырабатывающий узкие импульсы, соответствующие фронтам посылок входного сигнала. Импульсы с выхода дифференцирующего блока 1 и импульсы с выхода делителя 12 поступают на вход счетного триггера 3, который изменяет свое состояние на противоположное по переднему фронту входного импульса. Сигнал с выхода счетного триггера 3 открывает ключ, реализованный на первом элементе И 4, на выходе которого формируется пачка импульсов (с частотой задающего генератора 14). Количество импульсов в пачке пропорционально длительности сигнала на выходе счетного триггера 3 (т,е, величине фазового рассогласования между, фронтом входного сигнала и выходным сигналом устройства тактовой синхронизации) ,

На выходе второго элемента И 5 формируется импульс,.соответствующий второму (по времени) импульсу, пос

Q

g

0 5

5

0

0

тупившему на вход счетного триггера 3. В зависимости от знака фазового рассогласования это может быть импульс с выхода дифференцирующего блока 1 или импульсы с выхода счетчика 7. Импульс с выхода второго элемента И 5 поступает на тактовый вход блока 8 регистров, срабатывающий по заднему фронту данного импульса. В фазовом дискриминаторе 6 первый элемент И 15 выделяет импульс с выхода дифференцирующего блока 1, если он пришел раньше импульса с выхода делителя 12. Если же первым пришел импульс с выхода делителя 12, то данный импульс выделяется вторым элементом И 16 фазового дискриминатора 6, Импульсы с выходов первого 15 и второго 16 элементов И управляют RS-тритгером 17. Выходной сигнал RS-триггера 17 несет информацию о знаке фазового рассогласования.

На выходе первого элемента И 4 формируется импульс, соответствующий моменту окончания пачки импульсов на выходе второго элемента И 5. В момент

действия данного импульса на выходе фазового дискриминатора 6 присутствует .1 или О в зависимости от знака фазового рассогласования. Количество импульсов, поступающих с выхода второго элемента И 5, подсчитывается счетчиком 7, который выполняет функцию преобразователя последовательного кода в параллельный. Импульс на выходе первого элемента И 4 записывает сформированное счетчиком 7 число в блок 8 регистров и обнуляет счетчик 7. При этом в старший (знаковый) разряд числа, занесенного в блок 8 регистров, записывается 1 или О с выхода фазового дискриминатора 6. Таким образом, в блок 8 регистров записывается число со знаком, соответствующее величине и направлению рассогласования фазы. Запись каждого нового числа в блок 8 регистров вызывает сдвиг информации в нем на один разряд. При этом блок 8 регистров представляет собой память величины (и знака) фазовых рассогласований на предыдущих тактовых интервалах .

Числа со знаком с выходов блока 8 регистров поступают на входы блока 9 перемножения, который состоит из постоянных запоминающих блоков (ИЗБ). Каждое число с выходов блока 8 регистров поступает на адресные входы

313

соответствующего ПЗБ. При этом на выходе данного ПЗБ выдается информация, предварительно зашитая по данному адресу, а именно число, равное произведению кода адреса на соответствующий коэффициент. Таким образом, каждое число с выходов блока 8 регистров умножается на коэффициент, величина которого определяется положением чис- ла в соответствующем регистре блока 8 регистров, в результате чего обеспечивается большой вклад величины расстройки на непосредственно предшест

вующих данному тактовых интервалах при|5 диоканале, введены последовательно

30

определении необходимой коррекции фазового положения.

Произведения величин рассогласования на соответствующие весовые коэффициенты суммируются сумматором 10, 20 на выходе которого формируется число со знаком, которое несет информацию о необходимой величине и направлении коррекции фазы тактовых импульсов.

По окончании импульса на выходе 25 первого элемента И 4 число с выхода сумматора 10 записывается в счетчик 19 формирователя 11 (фиг. 2). Одновременно открывается ключ 18, через который импульсы с задающего генератора 14 поступают на тактовый вход счетчика 19 и уменьшают записанное в него число. В момент прохождения счетчика 19 через нуль на его выходе формируется импульс, который закрывает ключ 18. При этом на выходе клю- 35 ча 18 формируется пачка импульсов, количество которых пропорционально величине требуемой коррекции фазы импульсов тактовой частоты.

Пачка импульсов с выхода ключа 18 поступает на информационный вход коммутатора 20. В зависимости от знака числа на выходе сумматора 10 импульсы с информационного входа коммутатора 20 поступают на соответствую щие коррекционные входы блока 13 добавления и исключения импульсов, на тактовый вход которого поступают импульсы с выхода задающего генератора 14. При этом в блоке 13 добавления и исключения импульсов осуществляется косвенная подстройка частоты импульсов, посутпающих от задающего генератора 14, и, следовательно, изменение фазового положения импульсов тактовой 55 мента И и RS-триггера, а также вто40

,. 45

50

соединенные элемент ИЛИ, счетный три гер, первый элемент И и счетчик Ю4- пульсов, последовательно соединенные второй элемент И и формирователь кор ректирующих сигналов, а также блок регистров сдвига, блок перемножения на весовые коэффициенты и сумматор, при этом выходы дифференцирующего бл ка и делителя частоты подсоединены соответственно к первому и второму входам элемента ИЛИ, выход которого подсоединен к первому входу второго элемента И, второй вход которого объ единен с управляющим входом фазового дискриминатора и подключен к выходу счетного триггера, выход фазового ди криминатора и выходы разрядов ка импульсов подсоединены к соответствующим информационным входам блока регистров сдвига, тактовый вход которого подсоединен к выходу второго рлемента И, выходы блока регистров сдвига через блок перемножения на весовые коэффициенты и сумматор подсоединены к соответствующим информационным входам формирователя корректирующих сигналов, тактовый вход которого подсоединен к дополнительноьгу выходу задающего генератора, выход которого подсоединен к второму вход первого элемента, а первый и второй выходы формирователя корректирующих сигналов подсоединены к соответствую щим коррекционным входам блока добавления и исключения импульсов.

2. Устройство по п. 1, о т л и - чающееся тем, что фазовьш дискриминатор выполнен в В1аде последовательно соединенных первого элечастоты на выходе делителя 12. Формула изобретения

1. Устройство тактовой синхронизации, содержащее последовательно соединенные задающий генератор, блок добавления и исключения импульсов, делитель частоты и фазовый дискриминатор, а также дифференцирующий блок, выход которого подсоединен к информационному входу фазового дискриминатора, причем вход дифференцирующего блока и выход делителя частоты являются соответственно входом и выходом устройства, отличающееся тем, что, с целью повьппения помехоустойчивости путем снижения воздействия случайных фазовых сдвигов в ра30

0

25 35

55 мента И и RS-триггера, а также вто40

45

50

соединенные элемент ИЛИ, счетный триг гер, первый элемент И и счетчик Ю4- пульсов, последовательно соединенные второй элемент И и формирователь корректирующих сигналов, а также блок регистров сдвига, блок перемножения на весовые коэффициенты и сумматор, при этом выходы дифференцирующего блока и делителя частоты подсоединены соответственно к первому и второму входам элемента ИЛИ, выход которого подсоединен к первому входу второго элемента И, второй вход которого объединен с управляющим входом фазового дискриминатора и подключен к выходу счетного триггера, выход фазового дискриминатора и выходы разрядов сг етчи-. ка импульсов подсоединены к соответствующим информационным входам блока регистров сдвига, тактовый вход которого подсоединен к выходу второго рлемента И, выходы блока регистров сдвига через блок перемножения на весовые коэффициенты и сумматор подсоединены к соответствующим информационным входам формирователя корректирующих сигналов, тактовый вход которого подсоединен к дополнительноьгу выходу задающего генератора, выход которого подсоединен к второму вход первого элемента, а первый и второй выходы формирователя корректирующих сигналов подсоединены к соответствующим коррекционным входам блока добавления и исключения импульсов.

2. Устройство по п. 1, о т л и - чающееся тем, что фазовьш дискриминатор выполнен в В1аде последовательно соединенных первого элерого элемента И, выход которого подсоединен к R-входу RS-триггера, причем первые входы первого и второго элементов И являются соответственно

513380946

информационным и тактовым входами фа- ментов И и выход RS-триггера являют- зового дискриминатора, объединенные ся соответственно управляющим входом втооые входы первого и второго эле- и выходом фазового дискриминатора.

Ф 4 Ф Ф

1В

19

20

фие.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство синхронизации | 1988 |

|

SU1644398A1 |

| Устройство фазовой автоподстройки тактовой частоты | 1989 |

|

SU1721834A1 |

| Устройство синхронизации в одночастотных многоканальных адресных системах с временным разделением каналов | 1989 |

|

SU1811018A1 |

| Помехоустойчивый цифровой фазометр | 1979 |

|

SU1002979A1 |

| Цифровой фазовый дискриминатор | 1985 |

|

SU1288624A1 |

| Цифровой одноканальный инфранизкочастотный фазометр | 1987 |

|

SU1472831A1 |

| АДАПТИВНЫЙ ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 2000 |

|

RU2166773C1 |

| Устройство синхронизации равнодоступной многоадресной системы радиосвязи | 1987 |

|

SU1478363A1 |

| Цифровой частотный дискриминатор | 1982 |

|

SU1131036A1 |

| ЧАСТОТНО-ФАЗОВОЕ РЕЛЕ | 2016 |

|

RU2641096C2 |

Изобретение относится к электросвязи. Цель изобретения - повышение помехоустойчивости путем снижения воз- , действия случайных фазовых сдвигов в радиоканале. Устр-во содержит дифференцирующий блок 1, эл-т ИЛИ 2, счетный триггер 3, эл-ты И 4 и 5, фазовый дискриминатор (ФД) 6, состоящий из эл-тов И 15 и 16 и RS-триггера 17, счетчик 7 импульсов , блок регистров 8 сдвига, блок перемножения 9 на весовые коэффициенты, сумматор 10, формирователь 11 корректирующих сигналов, делитель 12 частоты, блок добавления и исключения (БДИ) 13 импульсов и задающий г-р 14. Цель достигается введением эл-та ИЛИ 2, триггера 3, эл- тов И 4 и 5, счетчика 7. блока регистров 8, блока перемножения 9, сумматора 10 и формирователя 11, с помощью которых в БДИ 13 осуществляется косвенная подстройка частоты импульсов, поступающих от г-ра 14, и, следовательно, изменение фазового положения импульсов тактовой частоты на выходе делителя 12, Устр-во . 2 ф-лы отличается выполнением ФД 6,1 з.п.ф-лы, 2 ил. (Л со QO 00 о (Х 4

Авторы

Даты

1987-09-15—Публикация

1985-03-13—Подача