(54) ЛОГИЧЕСКОЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования сетевого графика | 1976 |

|

SU656067A1 |

| Логическое устройство | 1977 |

|

SU729588A1 |

| ВСЕСОНЭЗНАН | 1973 |

|

SU368602A1 |

| Устройство для решения комбинаторно-логических задач при проектировании печатных плат | 1982 |

|

SU1059579A1 |

| Устройство для многоточечной сигнализации | 1990 |

|

SU1795496A1 |

| УСТРОЙСТВО ДЛЯ ЗАПИСИ И ОТОБРАЖЕНИЯ ИНФОРМАЦИИ | 1992 |

|

RU2101781C1 |

| Ассоциативное запоминающее устройство | 1983 |

|

SU1169023A1 |

| Однородная вычислительная среда | 1973 |

|

SU443382A1 |

| Устройство для диагностики и прогнозирования отказов | 1989 |

|

SU1629898A1 |

| ВЕРОЯТНОСТНЫЙ АВТОМАТ | 2001 |

|

RU2195697C1 |

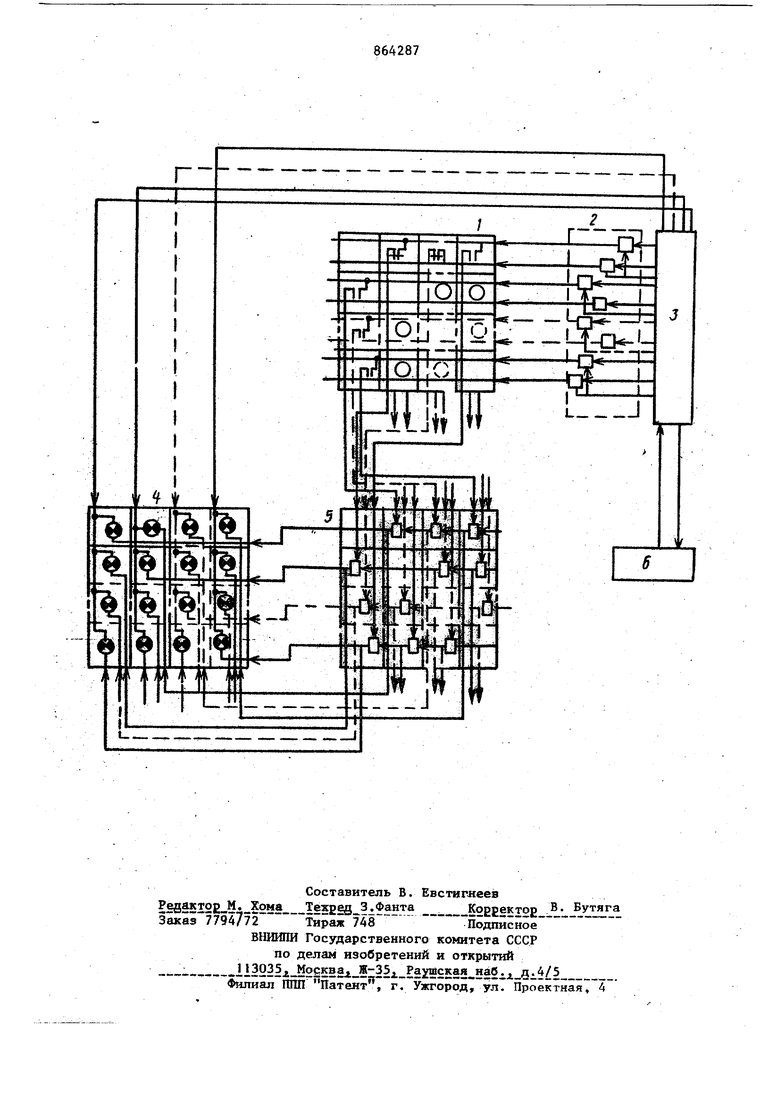

Изобретение относится к командноинформахщонным системам и средствам отображения информации и может быть использовано в качестве основного ко манд но информационно го технического средства на больших технологических комплексах. Известно логическое устройство, с держащее блок управления с подключен ными к нему блоками анализа, элемент ми И блока1 ш логики П . Однако такое устройство имеет недостаточные логические возможиости и надежность работы. Наиболее близким к предлагаемому является логическое устройство, содержащее блок управления, квадратную матрицу с элементами памяти в ее ячейках, с одной пустой диагональю, входами строк через элементы И соеди ненную с блоком управления, который соединен двусторонними связтт с объ ектом управления С 21. Однако это устройство не позволяет получить повышение надеяшости логического устройства, не позволяет упростить его конструкцию, процесс управления и контроля за операциями, технологического процесса сложен и не исключает возни|снове1гая ошибок в процессе управления и контроля. Цель изобретения - повышение надежности работы устройства и исключения ошибок оператора в процессе управления и контроля. Поставленная цель достигается тем, что в устройство, содержащее блок уп равления, первую и вторую группы элементов И, матрицу памяти с элементами памятн в ее ячейках, кроме ячеек в одной из ее диагоналей, входы каж дои строки матрицы памяти через элементы И первой и второй групп подключены к блоку управления, объект управления, соединенный двусторонними связями с блоком управления, введены матрица индикации и матрица анализа 3 связей с логическш-1и элементами ЗАПРЕТ в ее ячейках, элементы ЗАПРЕТ каждой строки матрицы анализа связей соединены последовательно, входы строк матрицы элементов ЗАПРЕТ анали за связей соединены с выходами соответствующих элементов И первой и вто рой групп, выходы строк матрицы анализа связей соединены со входами диа гональных элементов матрицы индикации, входы столбцов матрицы анализа связей соединены с выходами соответствующих элементов памяти соответствующих строк матрицы памяти, выходы элементов ЗАПРЕТ матрицы анализа свя зей соединены с первыми входами соот ветствующих элементов матрицы индика ции, вторые входы которых соединены по столбцам, входы столбцов подключе ны к соответствующим управляющим выходам блока управления. На чертеже изображена блок-схема предлагаемого устройства. Устройство содержит квадратную матрицу i с элементами памяти в ее ячейках, группы элементов И 2, блок управления 3, матрицу индикации 4, матрицу элементов ЗАПРЕТ 5, объект управления 6. Логическое устройство работает следующим образом. Каждой строке и каждому столбцу матриц 1, 4 и 5 соответствует один элемент детерминированного процесса При этом перечень элементов, соответствующий строкам сверху вниз, оди наков с перечнем элементов, соответствующим столбцам слева направо. В общем случае, если процесс состоит из м элементов, необходимо и иметь квадратную матрицу с М строкам и АЛ столбцами. В элемент памяти известным способом вносится информация отображающая логическую связь двух рассматриваемых элементов процесса, находящихся на пересечении одной ст ки и одного столбца матрицы 1. Такж вносится информация в элементы памя ти о наличиии ограничений на одновр .менность вьшолнения элементов процесса. Элементы ЗАПРЕТ квадратной матри цы 5 по строкам включены последовательно, а по столбцам подключены па раллельно к выходам столбцов матрицы 1 и ко входам столбцов матрицы 4 Диа гональны1е индикаторы матрицы индикации 4 подключены по строкам к выходам строк матрицы элементов SAnPET 5, а по столбцам к выходам блока управления 3. Остальные индиаторы матрицы 4 по столбцам подклюены к выходам столбцов матрицы 5, а по строкам - к выходам строк матицы 5. При подаче сигналов с блока управения, информация через элементы И 2 заносится в элементы памяти матриы 1 и затем переносится в ячейки соответствующих строк матрицы 5. При отсутствии связи между элементами процесса сигнал с блока управения 3 через элементы ЗАПРЕТ матри19)1 5 с выходов ее строк подается на инндйкаторы матрицы 4. При наличии связи между элементаи процесса соответствующие элементы ЗАПРЕТ строк матрицы 5 закрываются и производится отключение питания индикаторов матрицы 4 сигналами с выходов столбцов матрицы 5. Одновременно. . Отключается соответствукщий диагональный индикатор матрицы 4. Таким образом, в каждой строке матрицы 4.. при отсутствии логической связи между элемeнтa и включены все индикаторы, что сигнализирует о разрешении вьтолнения данной операции. При наличии логической связи между выполняемыми элементами отключен один диагональный индикатор и один или несколько других индикаторов матрицы 4, что сигнализирует о невозможности выполнения данной операции, так как до ее начала должны быть выполнены операции, соответствукицие отключенным индикаторам. После выполнения некоторой операции процесса снимается сигнал с п-х строк матриц- 1 и 5. Сигналы снимаются путем запирания элементов И 2 с блока управления 3. При этом выключаются все индикаторы п-й строки матрицы 4. Одновременно с этим при наличии логической связи между выполненньгм элементом и.всеми остальными включаются индикаторы в строках матрицы 4, соответствующих- тем элементам процесса, с которыми связан выполненный элемент. Таким образом, по мере выполнения элементов процесса в строках матрицы 4 набирается готовность на выполнение тех элементов процесса, которые логически связаны с уже выполненными. В случае, когда сигнал со входов элементов И 2 блоком управления снимается, необходимо в элементах памяти, горизонтального ряда матрицы 1 перезаписать зависимые, логические связ на независимь1е, Если зависш-юсть меж ду элементами процесса представляет собой ограничение на одновременноЬть и элемент, от которого зависит это ограничение, не может быть выполнен по каким-либо причинам, путем подачи запрещающего сигнала с блока управления 3 на элементы И 2, соответству щие этому элементу процесса, разреша ется выполнение зависимого элемента. Определение тех элементов, которы необходимо вьшолнить до начала испол нения какого-либо определенного элемента процесса, производится до состоянию индикаторов в строках матрицы 4. Отключенные индикаторы в строках матриць 4 сиг-нализируют о зависимости выбранного элемента процесса от остальных. Информацию об оставшихся невьшол(ненных элементах процесса вьщают индикаторы, включенные в соответствующих строках матрицы 4. Если хотя бы один индикатор соответствующей строки матрицы 4 находится во включенном состоянии, а соответствующий ему диагональный индикатор отключен, то это сигнализирует о том, что данный элемент процесса еще не выполнен. Если число элементов процесса из цикла в цикл изменяется, например уменьшается, то достаточно в элементах памяти горизонтальных и вертикальных рядов матрицы 1, соответству щих этим элементам, перезаписать зависимые связи на независимые или закрыть элементы И 2 этих рядов. При увеличении числа элементов процесса в элементы памяти, .соответствующих горизонтальных и вертикальных рядов матрицы 1, достаточно внести функ циональные зависимости между всеми имеющимися и.вновь введенными элемен тами и добавить в матрицы 1 4, 5 столько строк и столбцов, сколько вновь введено элементов процесса. Процесс управления при этом перестра ивается автоматически. Таким образом, введенные в состав устройства матрицы элементов ЗАПРЕТ И матрицы индикации ссоответствующими связями сводит к минимуму возмсгжность ошибки оператора, что приводит к повьш1ению надежности работы устройства в целом.Формула изобретения Логическое устройство, содержащее блок управления, первую и вторую jpynпы элементов И, матрицу памяти с элемеЕ1тами памяти в ее- ячейках, кроме ячеек в одной из ее, диагоналей, входы каждой строки матрицы памяти через элементы И первой и второй групп подключены к блоку управления, объект управления, соединенный двусторонними связями с блоком управления, отличающееся тем, что, с целью повьш1ения надежности работы и ис- . ключения ошибок оператора в процессе управления и контроля, оно содержит матрицу индикации и матрицу анализа связей с логическими элементами ЗА-. . ПРЕТ в ее ячейках, элементы ЗАПРЕТ каждой строки матрицы анализа связей соединены последовательно, входы строк матрицы элементов ЗАПРЕТ анализа связей Соединены с выходами соответ ствующих элементов И первой и второй групп, выходы строк матрицы анализа связей соединены со входами диагональных элементов матрицы индикации, входы столбцов матрицы анализа связей соединены с выходами соответствующих элементов памяти соответствующих строк матрицы памяти, выходы элементов ЗАПРЕТ матрицы анализа соединены с первыми входами соответствующих элементов матрицы индикации, вторые входы которых соединены по столбцам, входы столбцов подключены к соответствующим управляющим выходам блока управления. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 458828, кл/ G 06 F 9/18, 1975. 2.Авторское свидетельство СССР № 368602, кл. G 06 F 9/00, 1973 (прототип.

Авторы

Даты

1981-09-15—Публикация

1976-07-14—Подача