(54) ЛОГИЧЕСКОЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Архитектура параллельной вычислительной системы | 2016 |

|

RU2644535C2 |

| Устройство для сопряжения многопроцессорной вычислительной системы | 1983 |

|

SU1160423A1 |

| Устройство для редактирования информации | 1981 |

|

SU980099A1 |

| Устройство для сдвига информации | 1978 |

|

SU798820A1 |

| Буферное запоминающее устройство | 1990 |

|

SU1833918A1 |

| СПОСОБ ПЕРЕДАЧИ ДИСКРЕТНОГО СООБЩЕНИЯ И СИСТЕМА ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2001 |

|

RU2179365C1 |

| АССОЦИАТИВНАЯ ЗАПОМИНАЮЩАЯ МАТРИЦА | 1996 |

|

RU2107955C1 |

| Устройство для сопряжения цифровой вычислительной машины с устройством ввода изображений | 1983 |

|

SU1176339A1 |

| Ортогональная многопроцессорная система | 1990 |

|

SU1839261A1 |

| Логическое устройство | 1976 |

|

SU864287A1 |

Изобретение относится к вычислительной технике и может быть использовано в качестве управляющего устройства в информационно-управляющих системах.

Известны логические устройства, 5 содержащие вычислительные машины, входные и выходные регистры, блоки цифроаналогового преобразования, селекторы каналов и дешифраторы, выполняющие функции анализа состояния про-О цёсса и формирования последовательностей команд управления технологического процесса 1.

Недостаток известных устройств состоит в большом объеме оборудования. 15

Наиболее близким к предлагаемому техническому решению является логическое устройство, содержащее блок па,мяти в виде матрицы элементов памяти, блок управления, соединенный первой 20 группой входов с группой выходов блока дешифрации связей, а второй группой входов - с группой выходов блока дешифрации состояния, управляющий вход которого и управляющий вход,блока де-25 шифрации связей подключены к соответствукяцим управляющим выходам блока управления, и две группы элементов И, входы которых соединены с соответствующими выходами блока управления, вы- 30

ходы к-тых элементов И первой и второй групп подключены соответственно к первым и вторым входам элементов памяти к-той строки матрицы 2,

Целью изобретения является уменьшение объема оборудования.

Поставленная цель достигается тем, что блок памяти выполнен в виде треугольной матрицы элементов памяти, причем третьи и четвертые входы элементов памяти к-ой строки матрицы сог единены соответственно с первыми и вторыми входами элементов памяти к-ой строки и к-ми входами из первой и второй групп входов блока дешифрации связей, к-ый вход из третьей группы входов которого соединен с к-ым входом из первой группы входов блока дешифрации состояния и первыми выходами элементов памяти к-ой строки к-го столбца матрицы, к-ый вход из второй группы входов блока дешифрации состояния подключен ко вторым выходсш элементов памяти к-го столбца матрицы (,К);

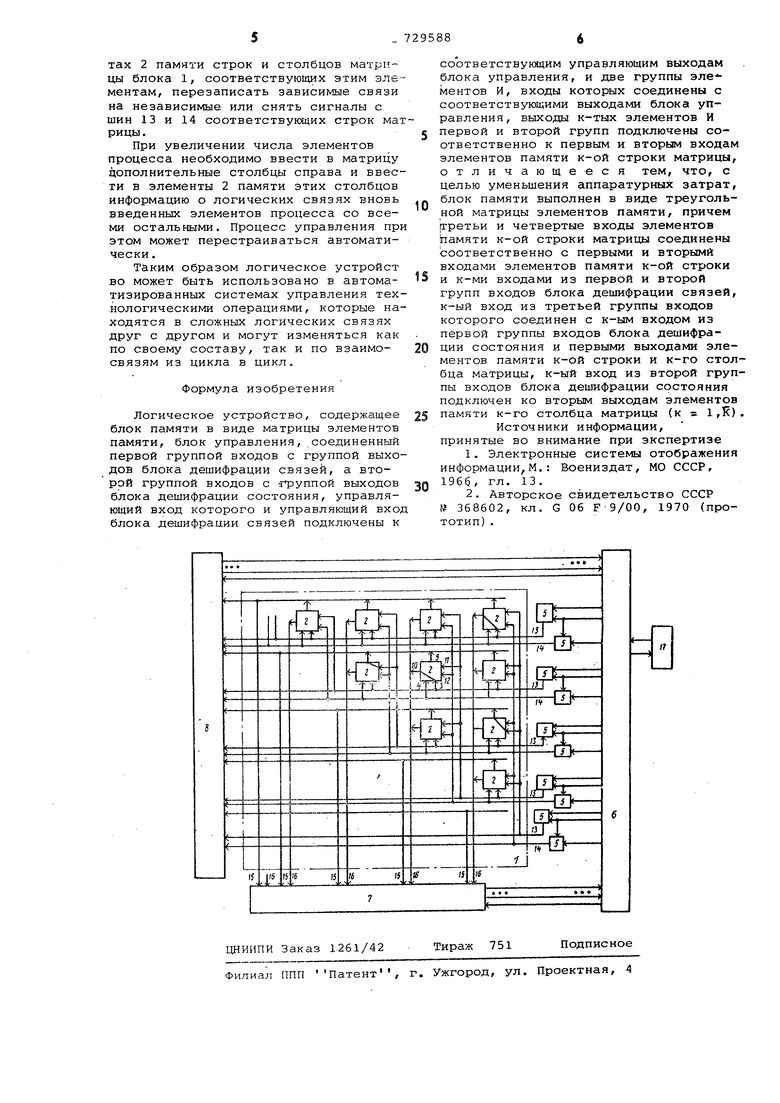

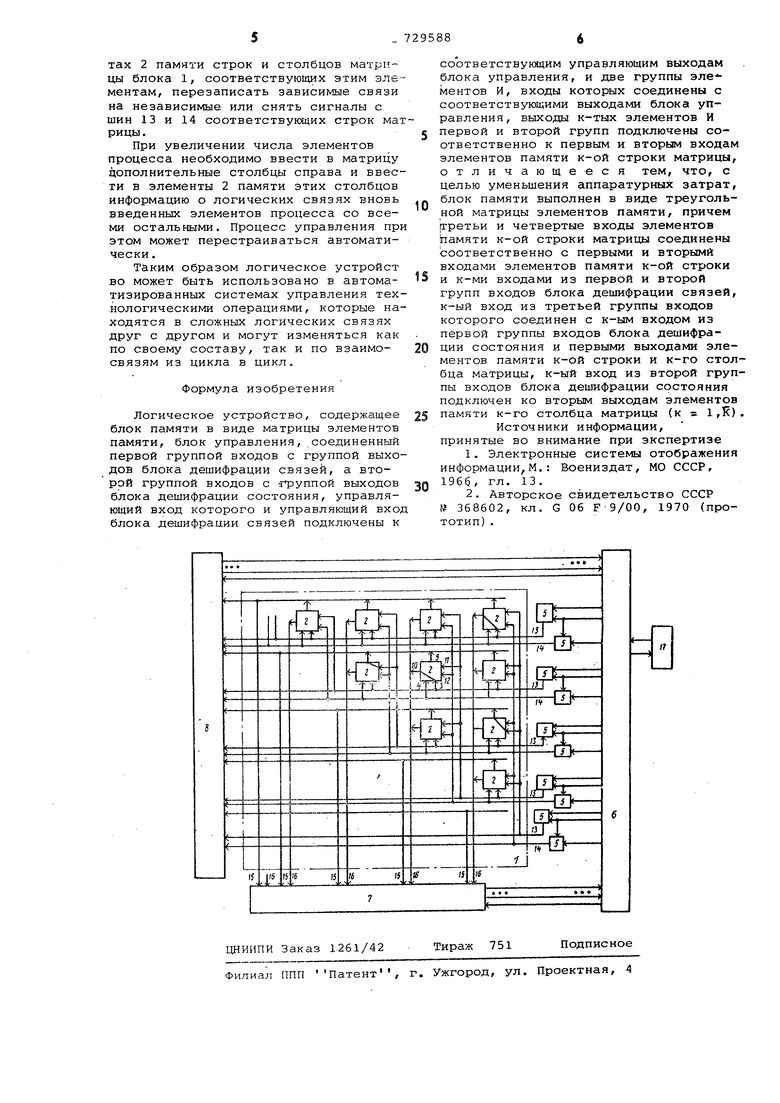

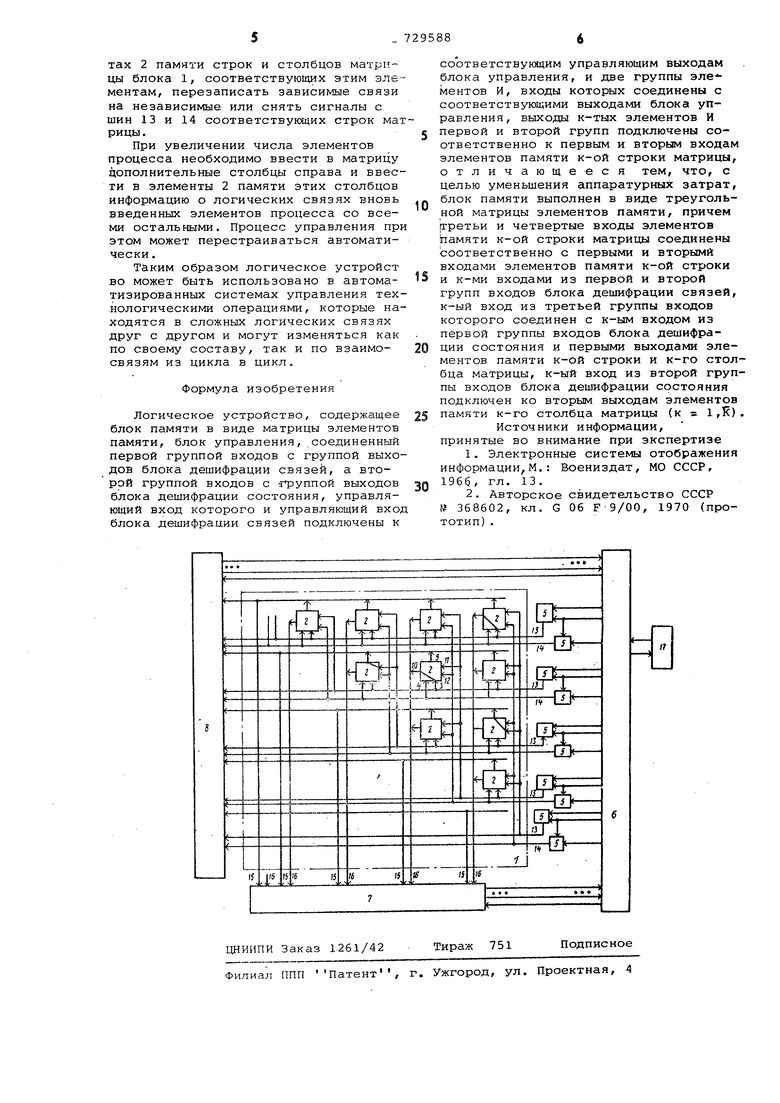

На чертеже показана блок-схема логического устройства.

Схема устройства содержит блок 1 памяти из образующих матрицу элементов 2 памяти, первый 3 и второй .4 входы элементов памяти 2, элементы И 5, блок 6 управле-/ния, блок 7 дешифрации состояния, блок 8 дешифрации связей, первый 9 и второй 10 выходы элементов памяти 2, третий 11 и четвертый 12 входы элементов Памяти 2, шины 13 выбора операций, шины 14 ограничений на одновременность, шины 15 запрета, шины 16 анализа связей и объект 17 управления. Предположим, что каждый элемент 2 памяти выполнен в виде контакта, соединяющего один из входов элемента с одним из выходов. Предположим также, что имеется пять команд (этому примеру соответствует блок-схема на чертеже), обозначенные через А1, А2 A3, А4 и А5, и что регшизация управления состоит в выдаче этих команд, например в последовательности А1, А5 A3, А2, А4. Пусть объект управления при невозможности выполнить команду А5 (например, из-за отказов оборудов ния, выполняющего эту команду) допус кает выполнение команды A3. В других же случаях замена команд недопустима Построим квадратную матрицу переходов размеров 5x5, причем будем считать, что номеру команды соответствует одноименные столбец и строка Возьмем, для примера, команду A3 и запишем в третий столбец и пятую строку (номер предшествующей команды) единицу, а в остальные клетки столбца занесем нули. Аналогичным образом для каждой команды заполним матрицу. Для рассматриваемого примера матрица выглядит следующим образом:X О 00 1 О 1 ХОО 000 X О . 00 10Х Конструкция блока 1 памяти выпол . нена так, что матрица элементов 2 с ответствует части матрицы переходов лежащей выше главной диагонали. Для работы устройства необходимо чтобы каждый элемент 2 матрицы был скоммутирован по следующим правилам: а)если в данной клетке матрицы, расположенной выше главной диагонали, клетке, симметричной ей отн сительно главной диагонали, то стои единица связи между входами и выходами соответствующего элемента 2 от сутствуют. Например, элемент 2 верх ней строки и левого столбца блока 1 соответствующий первой строке и вто рому столбцу матрицы переходов (в блоке 1 отсутствуют элементы 2 для главной диагонали) должен обеспечивать во всех случаях разрыв между входами и выходами; б)если в данной клетке матрицы, расположенной выше главной диагонаи, стоит единица, то элемент 2 долен коммутировать вход 3, подключенный к шине выбора операций на выход 10, подключенный к шине анализа связи;в)если в клетке матрицы, располоенной ниже главной диагонали, стоит единица, то элемен 2 должен коммутировать вход 11, подключенный к шине выбора операций, на выход 9, подключенный к шине запрета; г)если в Заданной программе допускается замена одной команды, выполнение которой в данный момент не представляется возможным, другой, то в соответствующем этой предшествующей команде элементе 2 рабочим входом должны быть не входы 3 или 11, а входы 4 или 12, подключенные к шине ограничения на одновременность. Устройство работает следующим образом. При подаче сигналов от блока 6 управления на щины 13 и 14 информация с элементов 2 вьвдается через шины 15 и 16 в блок 7 дешифрации состояния элементов . Блок 7 сигнализирует в блок 6 о Столбце, на шинах 15 и 16 которого присутствует нулевой сигнал. Номер этого столбца однозначно соответствует номеру команды, которую необходимо выполнить. Блок 6 выдает эту команду в объект 17 и ждет уведомления о выполнении этой команды. Получив уведомление, блок 6 вновь возбуждает шины 13 и 14, блокируя при этом с помощью соЬтветствующих элементов И 5 шины 13 и 14 строки, номер которой равен номеру выполненной команды. Таким путемпроисходит последовательное чтение номеров, команд, которые необходимо выдавать в объект 7. Если вместо уведомления об исполнении команды блок 6 получает от объекта сигнал о невозможности ее выполнить, то блок 6 снова возбуждает шины 13 и 14, блокируя при этом указанные шины строк элементов 2 исполненных команд и шину 14 строки, соответствующей номеру невыполненной команды. При этом, если команды связаны не жестко, будет выполняться следующая команда. Блок 8 во время работы устройства определяет те элементы процесса, которые уже выполнены, а также те элементы процесса, которые еще не выполнены, так как сигналы с блока 6 с выходов столбцов матрицы по шинам 13 и 14 поступают в блок 8. Кроме того, блок 8 выдает в блок б информацию о том, от каких элементов процесса зависит любой выбранный элемент процесса, так как данная информация поступает с элементов 2 памяти через шины запрета 15 в блок 8. Если число элементов процесса из цикла в цикл изменяется, например уменьшается, то достаточно в элемен

Авторы

Даты

1980-04-25—Публикация

1977-11-09—Подача