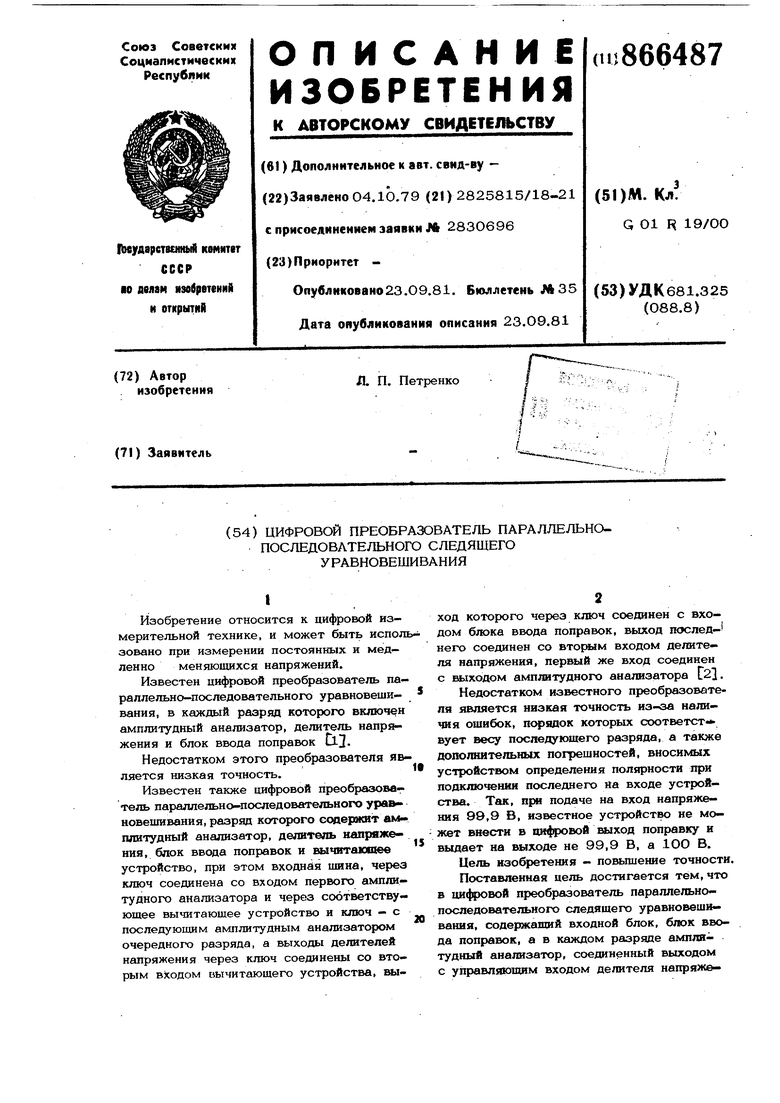

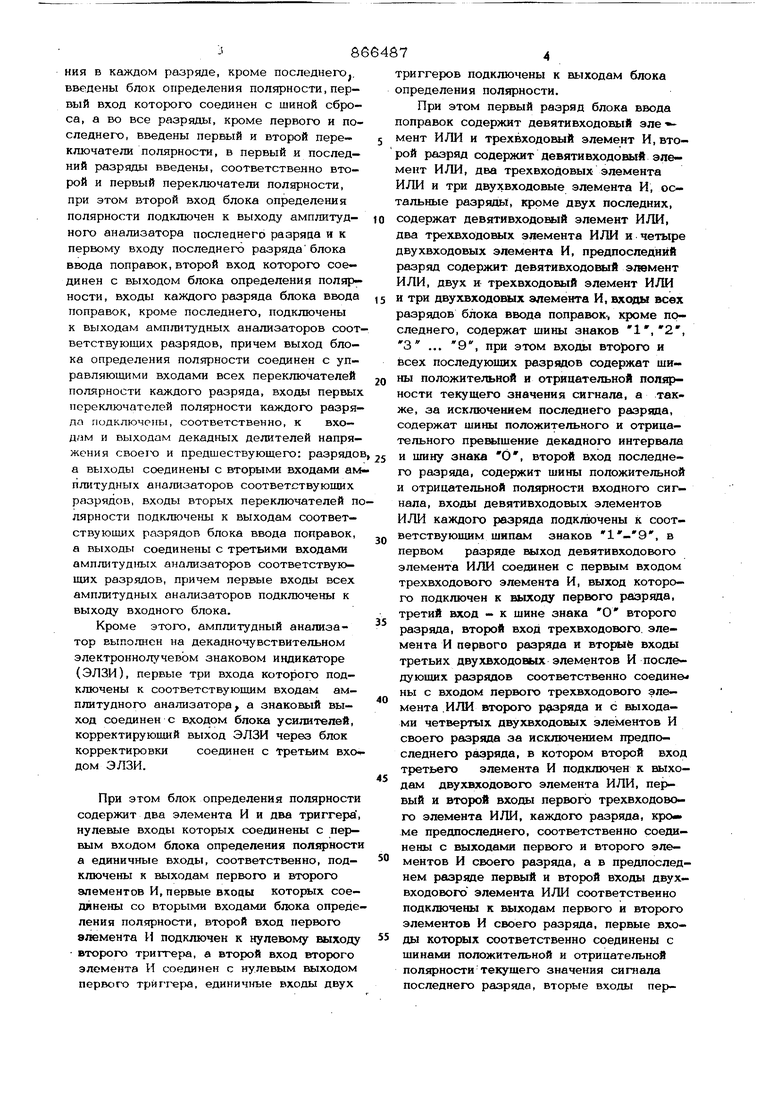

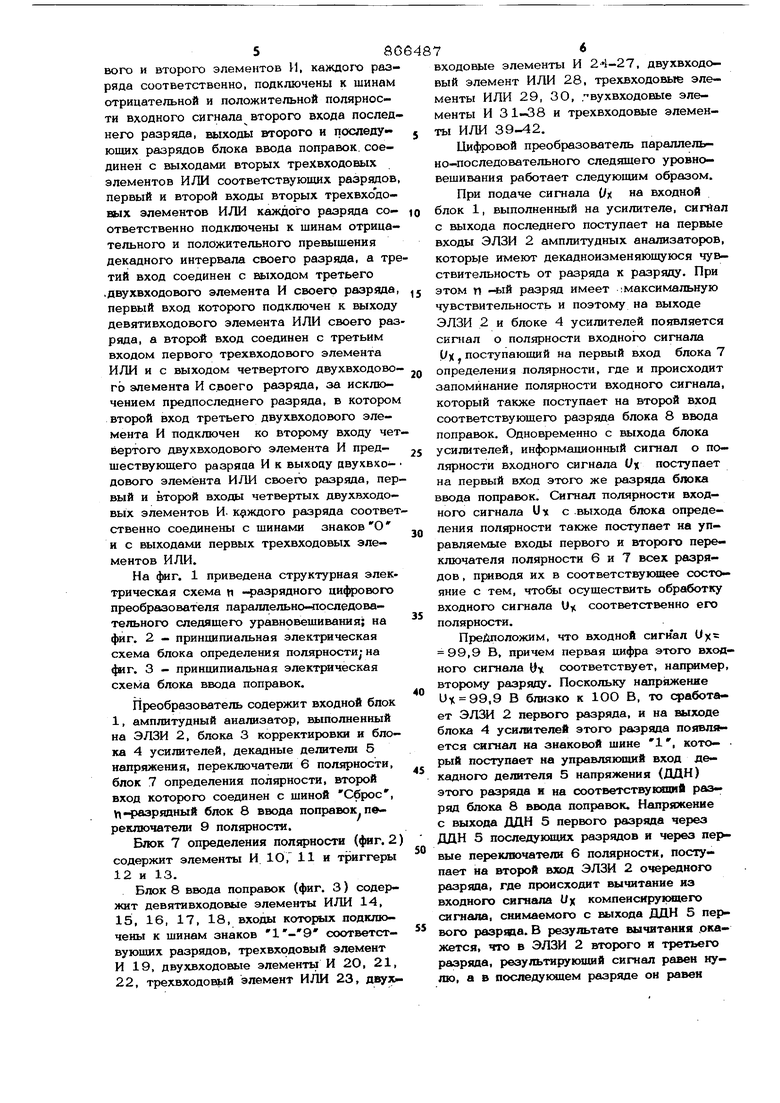

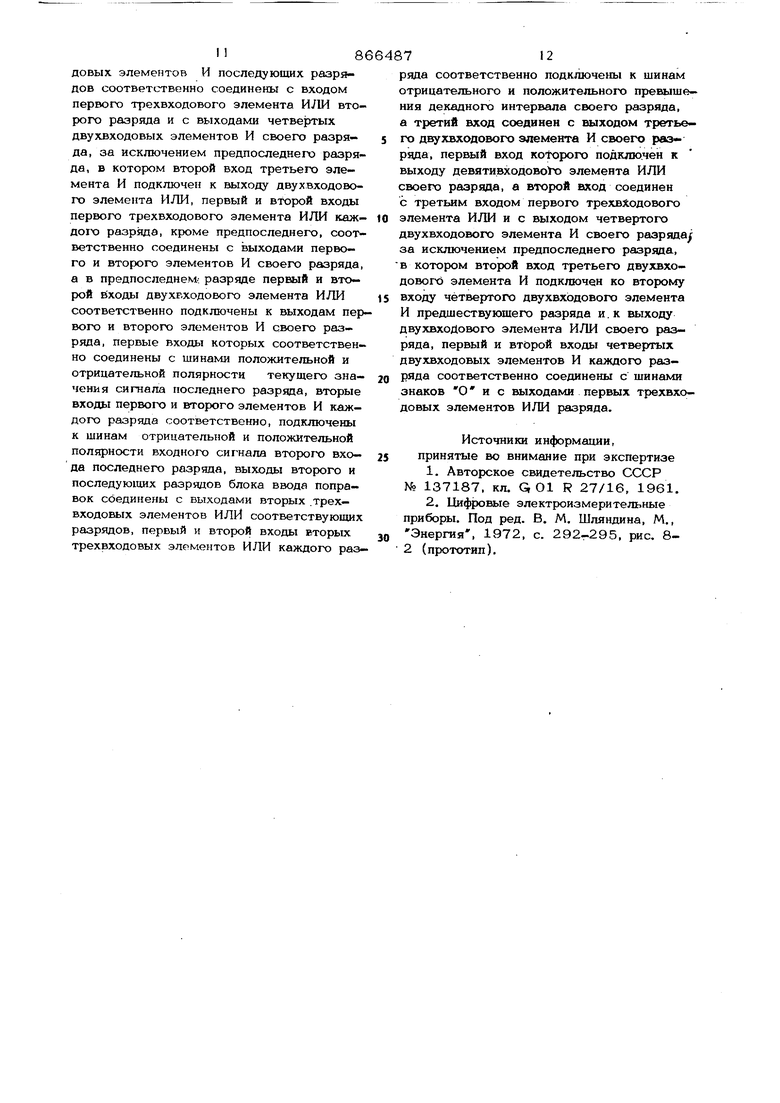

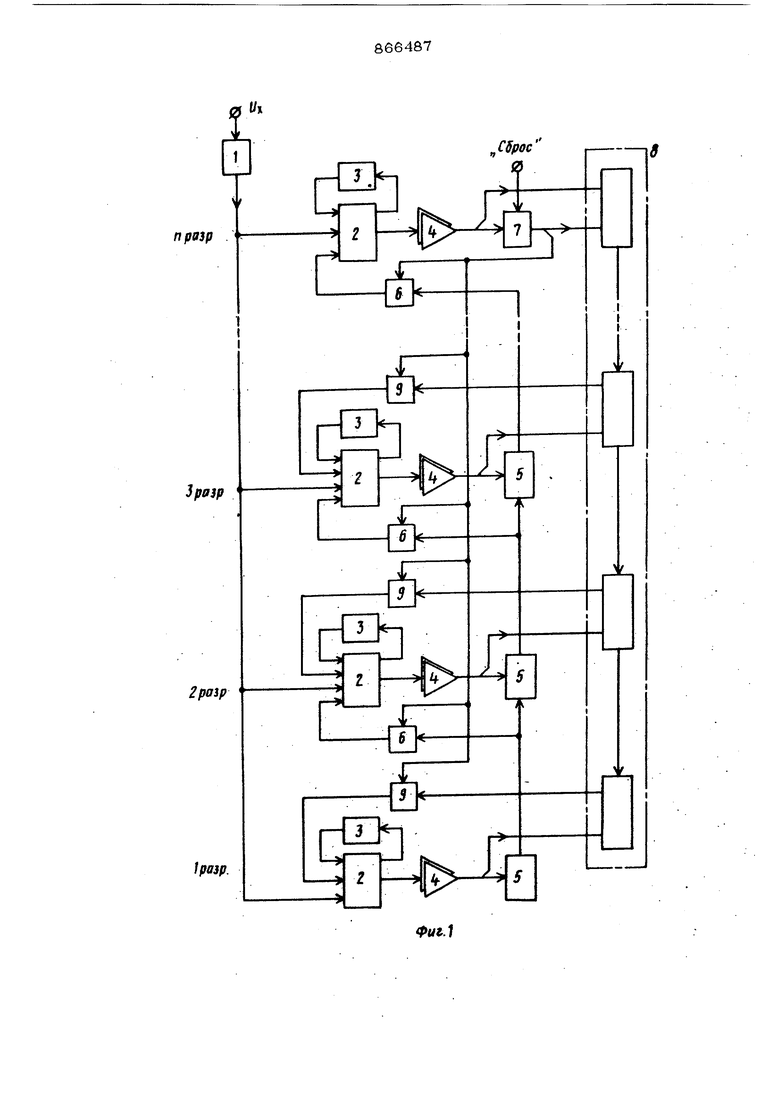

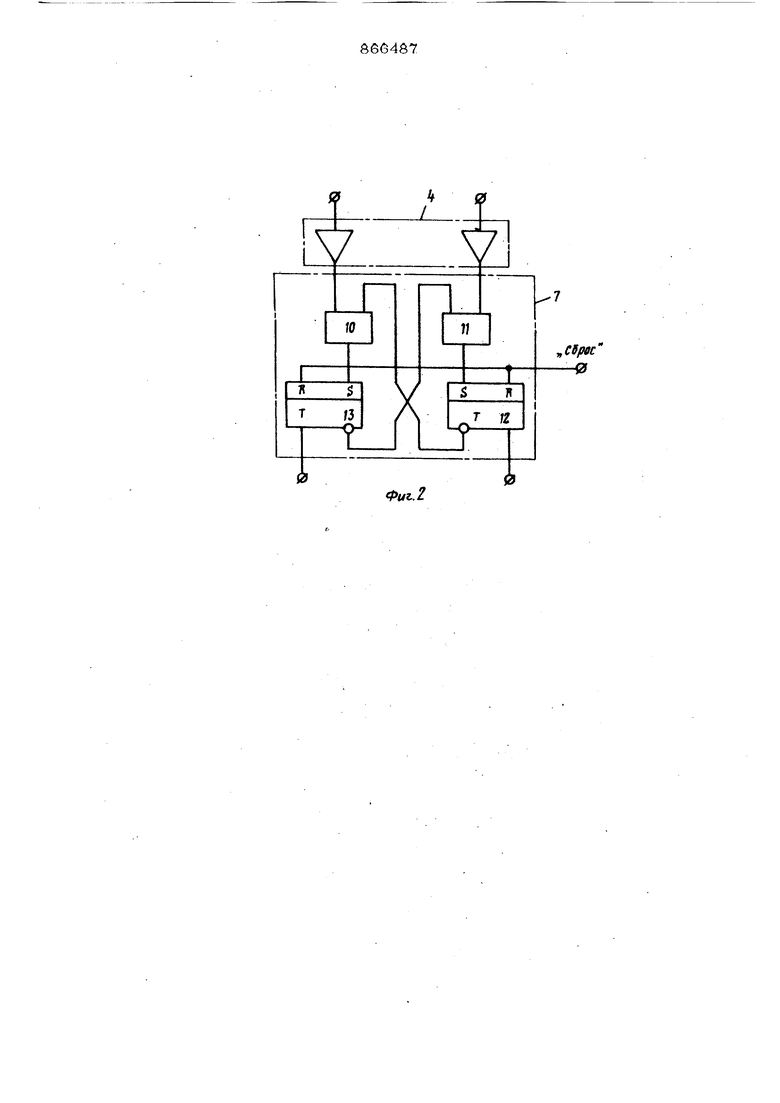

(54) ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНОПОСЛЕДОВАТЕЛЬНОГО СЛЕДЯЩЕГО УРАВНОВЕШИВАНИЯ Изобретение относится к цифровой измерительной технике, и может быть испол зовано при измерении постоянных и медленно меняющихся напряжений. Известен цифровой преобразователь параллельно-последовательного уравновешивания, в каждый разряд которого включен амплитудный анализатор, делитель напряжения и блок ввода поправок Ll. Недостатком этого преобразователя яв ляется низкая точность. Известен также цифровой преобразователь параллельно-последовательного уравновешивания, разряд которого содержит ам шштудный анализатор, делитель напряжения, блок ввода поправок и вычитакхоее устройство, при этом входная шииа, через ключ соединена со входом первого амплитудного анализатора и через соответствующее вычитающее устройство и ключ - с последующим амплитудным анализатором очередного разряда, а выходы делителей напряжения через ключ соединены со вторым входом вычитающего устройства, шлход которого через ключ соедииен с входом блока ввода поправок, выход последнего соединен со вторым входом делителя напряжения, первый же вход соединен с ш 1ходом амплитудного анализатора L21, Недостатком известного преобразователя является низкая точность из-за наличия ошибок, которых соответст-fc вует весу последукмцего разряда, а также лопогештельных погрешностей, вносимых устройством определения полярности при подключении последнего на входе устройства. Так, при подаче на вход напряжения 99,9 В, известное устройство не может внести в цн фовой выход поправку и выдает на выходе не 99,9 В, а 1ОО В. Цель изобретения - повьпцение точности. Поставленная цель достигается тем, что в преобразователь параллельнопоследовательного следящего уравновешивания, содержащий входной блок, блок ввода поправок, а в каждом разряде амплитудный анализатор, соединенный выходом с управляющим входом делителя напряжения в каждом разряде, кроме последнего,, введены блок определения полярности,первый вход которого соединен с шиной сброса, а во все разряды, кроме первого и последнего, введены первый и второй переключатели полярности, в первый и последний разряды введены, соответственно второй и первый переключатели полярности, при этом второй вход блока определения полярности подключен к выходу амплитудного анализатора последнего разряда и к первому входу последнего разряда блока ввода поправок, второй вход которого соединен с выходом блока определения полярности, входы каждого разряда блока ввода поправок, кроме последнего, подключены к выходам амплитудных анализаторов соот ветствующих разрядов, причем выход блока определения пол5фности соединен с управляющими входами всех переключателей полярности каждого разряда, входа первых переключателей полярности каждого разряда подключены, соответственно, к входам и выходам декадных делителей напряжения своетю и предществующего: разрядо а выходы соединены с вторыми входами ам плитудных анахшзаторов соответствующих разрядов, входы вторых переключателей п лярности подключены к выходам соответствующих разрядов блока ввода поправок, а выходы соединены с третьими входами амплитудных анализаторов соответствующих разрядов, причем первые входы всех амплитудных анализаторов подключены к выходу входного блока. Кроме этого, амплитудный анализатор выполнен на декадночувствительном электроннолучевом знаковом индикаторе (ЭЛЗИ), первые три входа которого подключены к соответствующим входам амплитудного анализатора, а знаковый выход соединен с входом блока усилителей, корректирующий выход ЭЛЗИ через блок корректировки соединен с третьим входом ЭЛЗИ. При этом блок определения полярности содержит два элемента И и два триггера нулевые входы которых соединены с первым входом блока определения полярност а единичные входы, соответственно, под- ключены к выходам первого и второго элементов И, первые входы которых соединены со вторыми входами блока опреде ления полярности, второй вход первого элемента И подключен к нулевому выходу второго триггера, а второй вход второго элемента И соединен с нулевым выходом первс1го триппера, единиЧ1тые входы двух триггеров подключены к выходам блока определения полярности. При этом первый разряд блока ввода поправок содержит девяти входовый эле мент ИЛИ и трехвходовый элемент И, второй разряд содержит девятивходовый элемент ИЛИ, два трехвходовых элемента ИЛИ и три двухвходовьге элемента И, остальные разрядь, кроме двух последних, содержат девятивходовый элемент ИЛИ, два трехвходовых элемента ИЛИ и четыре двухвходовых элемента И, предпоследний разряд содержит девятивходовый элемент ИЛИ, двух и трехвходовый элемент ИЛИ и три двухвходогаых элемента И, входы всех разрядов блока ввода поправок-, кроме последнего, содержат шины знаков ,2, 3 ... Э, при этом входы второго и всех последующих разрядов содержат щины положительной и отрицательной полярности текущего значения сигнала, а также, за исключением последнего разряда, содержат щины положительного и отрицательного премз1щение декадного интервала и щииу знаке О, второй вход последнего разряда, содержит щины положительной и отрицательной пол5фности входного сигнала, входы девятивходовых элементов ИЛИ каждого разряда подключены к соответствующим шипам знаков i-Q, в первом разряде выход девятивходового элемента ИЛИ соединен с первым входом трехвходового элемента И, выход которого подключен к вь«оду первого разряда, третий вход - к шине знака О второго разряда, второй вход трехвходового. элемента И первого разряда и вторые входы третьих двухвходовых элементов И последующих разрядов соответственно соедиие ны с входом первого трехвходового элемента .ИЛИ второго р4 зряда и с выходами четвертых двухвходовых элементов И своего разряда за исключением предпоследнего разряда, в котором второй вход третьего элемента И подключен к выходам двухвходового элемента ИЛИ, первый и второй входы первого трехвходового элемента ИЛИ, каждого разряда, кро- ме предпоследнего, соответственно соединены с выходами первого и второго элементов И своего разряда, а в предпоследнем разряде первый и второй входы двухвходового элемента ИЛИ соответствеино подключены к выходам первого и второго элементов И своегхэ разряда, первые вхо- ДЬ1 которых соответственно соединены с шинами положительной и отрицательной поЛ5фности текущего значения сигнала последнего разряда, вторые входы первого и второго элементов И, каждогх) раз ряда соответственно, подключены к шинам отрицательной и положительной полярности входного сигнала второго входа послед него разряда, выходы второго и последующих разрядов блока ввода поправок.соединен с выходами вторых трехвходовых элементов ИЛИ соответствующих разрядов первый и второй входы вторых трехвходовых элементов ИЛИ каждого разрода соответственно подключены к шинам отрица тельного и положительного превышения декадного интервала своего разряда, а тр тий вход соединен с выходом третьего .двухвходового элемента И своего разряда первый вход которого подключен к выходу девятивходового элемента ИЛИ своего раз ряда, а второй вход соединен с третьим входом первого трехвходового элемента ИЛИ и с выходом четвертого двухвходово го элемента И своего разряда, за исключением предпоследнего разряда, в котором второй вход третьего двухвходового элемента И подключен ко второму входу чет вертого двухвходового элемента И предшествующего разряаа И к выходу двухвходового элемента ИЛИ своего разряда, пер вый и вторюй входы четвертых двухвходо- вых элементов И- к жаого разряда соответ ственно соединены с шинами знаков О к с выходами первых трехвходовых элементов ИЛИ. На фиг. 1 приведена структурная электрическая схема } -разрядного цифрового преобразователя параллельно-лоследовательного следящего уравновешивания; на фиг. 2 - принципиальная электрическая схема блока определения полярности - на «}мг. 3 - принципиальная электрическая схема блока ввода поправок. Преобразователь содержит входной блок 1, амплитудный анализатор, выполненный на ЭЛЗИ 2, блока 3 корректировки и блока 4 усилителей, декадные делители 5 напряжения, переключатели 6 пол5фности, блок 7 определения полярности, второй вход которого соединен с шиной Сброс, t -разрядный блок S ввода поправок переключатели 9 полярности. Блок 7 определения полярности ((Jmr. 2) содержит элементы И Ю, 11 и триггеры 12 и 13. Блок 8 ввода поправок (фиг. 3) содержит девятивходовые элементы ИЛИ 14, 15, 16, 17, 18, входы которых подключены к шинам знаков 1-9 соответствуюших разрядов, трехвходовый элемент И 19, двухвходовые элементы И 2О, 21, 22, трехвходовь1й элемент ИЛИ 23, двухвходовые элементы И 24-27, двухвходовый элемент ИЛИ 28, трехвходовые элементы ИЛИ 29, 30, .вухвходовые элементы И 31-38 и трехвходовые элементы ИЛИ 39-42. Цифровой преобразователь параллельно-последовательного следящего уровновешивания работает следующим образом. При подаче сигнала (Ух на входной блок 1, выполненный на усилителе, сигнал с выхода последнего поступает на первые входы ЭЛЗИ 2 амплитудных анализаторов, которые имеют декадноизменяющуюся чувствительность от разряда к разряду. При этом п разряд имеет максимальную чувствительность и поэтому на выходе ЭЛЗИ 2 и блоке 4 усилителей появляется сигнал о полярности входного сигнала 1/Х , поступающий на первый вход блока 7 определения полярности, где и происходит запоминание полярности входного сигнала, который также поступает на второй вход соответствующего разряда блока 8 ввода поправок. Одновременно с выхода блока усилителей, информационный сигнал о по- Л5фности входного сигнала Ux поступает на первый вход этого же разряда блока ввода поправок. Сигнал полярности входного сигнала Uit с .выхода блока определения полярности также поступает на управляемые входы первого и второго переключателя полярности 6 и 7 всех разрядов , приводя их в соответствующее состояние с тем, ЧТО&1 осуществить обработку входного сигнала Ufc соответственно его полярности. Прейположим, что входной сигнал 0 99,9 В, причем первая цифра этого вхоа- ного сигнала Уу соответствует, , второму разряду. Поскольку напряжение и- 99,9 В бдазко к 1ОО В, то сработает ЭЛЗИ 2 первого разряда, и на выходе блока 4 усидштелей этого разряда появляется сигнал на знаковой шине 1, который поступает на управлякшшй вход декадного делителя 5 напряжения (ДДН) этого разряда и на соответствующий разряд блока 8 ввода поправок. Напряжение с выхода ИДИ 5 первого разряда через ДДН 5 последукмцих разрядов и через первые переключатели 6 полярности, поступает на второй вход ЭЛЗИ 2 очередного разряда, где происходит вычитание из входного сигнала Ux компенсирующего сигнала, снимаемого с выхода ДДН 5 первого разряда. В результате вычитания .окажется, что в ЭЛЗИ 2 второго и третьего разряда, результирующий сигнал равен ную, а в последующем разряде он равен единице, но с противоположным знаком (99,9-100 -0,1). Это приводит к тому, гго на первом входе последнего разряда блока 8 ввода поправок сигнал по$голяет- ся на шине с противоположным информационным значением полярности результирующего сигнала, что приводит к подаче сигнала исправления ошибки на все пре- дыдущие разряды, начиная с первого сработавшего, в результате чего в первом разряде, ЭЛЗИ 2 зафиксирует знак О и удерживает его сигналом с выхода блока 3 корректировки, также как и в последу- юших разрядах. Информация во втором разрвще зафиксируется и удерживается блоком 3 коррек тировки и соответствует знаку 9, так же как и в последуюших разрядах. При этом, как только откорректируется информация предпоследнего разряда, на выходе последовательно соединенных ДДН 5 синтезируется сигнал, равный 99,0 В. В результате вычитания, в последнем разряде результат имеет тот же знак, что и знак входного сигнала, следовательно, на первом входе последнего разряда блока ввода поправок появится сигнал на одноименной по полярности шине, по сравнению с первым его входом, что приводит к отключению блока 8 ввода поправок,. При отключении входного сигнала L/x от входного блока и подаче импульса на вход Сброс, выходная информация в циф ровом преобразователе сбрасывается. Работа блока определения полярности (фиг. 2) заключается в следующем. При подаче сигнала с выхода блока 4 усилителей на вход эпемента И Ю и, учитывая, что триггеры в исходном положении находятся в нулевом состоянии, срабатывает триггер 13, и на его единич ном выходе появится сигнал и тогда, когДа на первом входе элемента И 11 появится сигнал противоположной полярности Блок определения полярности находится в таком состоянии до тех пор, пока на шину Сброс не подадут сигнал, после чего он вновь готов к работе. Работа блока ввода поправок (фиг. 3) заключается в следующем. Предположим, что на вход цифрового преобразователя подан сигнал 99,99 В и он, с учетом погрешности, зафиксирует информацию 100 В. В этом .случае, на входе первого разряда блока ввода поправок появится сигнал, который по знаковой шине 1 через девятивходовый элемент ИЛИ 14 поступает на третий вход трехвх дового элемента И 19. На первом входе 86 64678 этого же элемента И 19 также есть сипнал, поскольку он подключен к знаковой шине, О входа второго разряда. На входе третьего и четвертого разряда, сигнал 5 появится на знаковых шинах,О, что приводит к появлению сигнала на вторых входах элементов И 24, 25. На входе пятого разряда, информационный сигнал появится на знаковой шине , поскольку - . 10О,00 В + 99,99 В -OO.Ol В. Остаток -ОО,О1 показывает номер знаковой шины, а знак говорит о том, что полярность текущего значения действующего сигнала в данном разряде прогавоположна полярности входного сигнала. Такое распределение полярностей приводит к тому, что на двух входах шестого разряда, сигнал появится на противоположных по фазе шинах, положительной и отрицательной. Это приведет к срабатыванию первого двухвходового элемента И 33 и сигнал с его выхода через первый трехвходошлй элемент ИЛИ ЗО, четвертый двухвходо- вой элементы И 25, первый трехвходовый элемент ИЛИ 29, четвертый д хвходовый элемент И 24 и первый трехвходовой элемент ИЛИ 23 поступает на второй вход трехвходового элемента И 19 и на его выход, следовательно, на вьгходе первого разряда появляется сигнал корректировки, который вводит поправку на одну значающую единицу в першлй разряд цифрового преобразователя. В результате, на входе первого разряда И на выходе элемента И 19 сигнал исчезает. Поданный сигнал Ux 99,99 В преаьпиает декадный интервал второго разрада на 9,99 В, что щмвояут к тому, что на входе второго разряде появляется сигнал в по знаковой шине превьпиения декадного интервала +Х он поступает через второй трехвходовый элемент ИЛИ 39 на Ooixoa второго разряда, при этом И1ф рмация в прео)азоввтеле данного разряаа измен11 ется на единцпу, т.е. фиксируется знак 9. Аналогичным образом по щнне превышения декадного интервала +Х, через второй трехвходовый элемент ИЛИ 4О, сигнал поступает на выход третьего разряда, так же как и в четвертом разряде. В результате последовательных операций в трех разрядах цифровой преобразователь аарегастрирует инфорк ацию 99,9 В. Разяость входного сигнала,- синтезированного в цифровом преобразователе, в пятом разряде сигнала появится на знаковой шине 9, что приведет к появлению сигнала на однофазных шинах всех входов разрядов, и ввод поправок прекратится. Использование предлагаемого изобрете ния позволяет повысить точность цифровых преобразователей параллельно-лоследовательного следящего уравновешивания. Формула изобретения 1.Цифровой преобразователь параллель но-последователЬного следящего уравновешивания, содержащий входной блок, блок ввода поправок, а в каждом разряде амплитудный анализатор, соединенный выходом с управляющим входом делителя напряжения в каждом разряде, кроме послед него, отличающийся тем, чч-о с целью повьпиения точности, введены блок определения полярности, первый вход которого соединен с шиной сброса, а во все разряды, кроме первого и последнего введены первый и второй переключатели полярности, в первый и последний разряды введены, соответственно, второй н пер вый переключатели полярности, при этом второй вход блока определения полярности подключен к выходу амплитудного анализатора последнего разряда и к перво му входу последнего разряда блока ввода поправок, второй вход которого соединен с выходом блока определения пол5фности, входы каждого разряда блока ввода поправок, кроме последнего, по рслючены к выходам амплитудных анализаторов соответствующих разрядов, причем выход блока определения полярности соединен с управляющими входами всех переключателей полярности каждого разряда, входы первых переключателей полярности каждого разряда подключены соответственно к входам и выходам декадных делителей напряжения своего и предшествующего разрядов, а вы ходы соединены с вторыми входами амплитудных анализаторов соответствукшшх раз рядов, входы вторых переключателей полярности подключены к выходам соответствукжсих разрядов блока ввода поправок, а выхоаы соеаинены с третьими входами амплитудных анализаторов соответствующих разрядов, прячем первые входы всех ампштудных анализаторов подключены к .выходу входного блока. 2.Прео юзователь по п. 1, о т л в чающийся тем, что амплитудный анализатор выполнен на декадночувствнтельном электроннолучевом знаковом ин;дикаторе, первые три входа которого подключены к соответствукидим входам амйлитудного анализатора, а знаковый выход соединён с входом блока усилителей,корректирующий выход электроннолучевого знакового индикатора через блок корректировки соединен с третьим входом эле1&троннолучевого знакового индикатора. 3.Преобразователь по п. 1, о т л и чающийся тем, что блок определения полярности содержит два элемента И и два триггера, нулевые входы которых соединены с первым входом блока определения полярности, а единичные входы, соответственно, подключены к выходам первого и второго элементов И, первые входы которых соединены со вторыми входами блока определения полярности, второй вход первого элемента И подключен к нулевому выходу триггера, а второй вход второго элемента И соединен с нулевым выходом первого триггера, единичные входы двух триггеров подключены к выход 1М блока определения полярности. 4.Преобразователь по п. 1, о т л и чающийся тем, что первый разр5Зд блока ввода поправок содержит девятивходовый элемент ИЛИ и трехвходовый элемент И, второй разр5щ содержит девяти- входовый элемент ИЛИ, два трехвходовых элемента ИЛИ и три двухвходовых элемента И, остальные разряды, кроме двух последних, содержат девятивходовый элемент ИЛИ, два трехвходовых элемента ИЛИ и четыре двухвходовых элемента И, предпоследний разряд содержит девятивходовый элемент ИЛИ, двух и трехвходовые элементы ИЛИ и три двухвходок.1х элемента И, входы всех разрядов блока ввода поправок, кроме последнего, содержат шины знаков , 2, 3 ... 9, при этом входам второго и всех последу няцих разрядов содержат шины положительной и отрицательней пол$фности текущего значения сигнала, а так же, за исключением последнего разряда, содержат шины положительного и отрицательного превьпиения декадного интервала и шину знака 0,второй вход последнего разряда содержит шины положительной и отрицательной пол$фностн входного сигнала, входы девятивходоетлх элементов ИЛИ каждого разряда подключены к соответствующим шинам знаков -9, в первом разряде выход девятивходового элемента ИЛИ соединен с первым входом трехвходового эле мента И, выход которого подключен к выходу разряда, третий вход - к ши не знака О второго разряда, второй вход трехвходового элемента И первого разр51да н входы третьих двухвходовых элементов И последующих разрядов соответственно соединены с входом первого трехвходового элемента ИЛИ второго разряда и с выходами четвертых двухвходовых элементов И своего разряда, за исключением предпоследнего разряда, в котором второй вход третьего элемента И подключен к выходу двухвходового элемента ИЛИ, первый и второй входы первого трехвходового элемента ИЛИ кажДО1Х1 разряда, кроме предпоследнего, соответственно соединены с выходами первого и второго элементов И своего разряда, а в предпоследнем разряде первый и второй бходы двухвходового элемента ИЛИ соответственно подключены к выходам первого и второго элементов И своего разряда, первые входы которых соответственно соединены с шинами положительной и отрицательной полярности текущего зна- чения сигнала последнего разряда, вторые входь первого и второго элементов И каждого разряда соответственно, подключены к шинам отрицательной и положительной пол1фности входного сигнала второго вхо- да последнего разряда, выходы второго и последующих разрядов блока ввода поправок соединены с выходами вторых .трех- входовых элементов ИЛИ соответствующих разр$щов, первый и второй входы кторых трехвходовых элементов ИЛИ каждого разряда соответственно подключены к щинам отрицательного и положительного превышения декадного интервала своего разряда, а третий вход соединен с выходом третьего двухвходового элемента И своего разряда, первый вход Kotoporo подклю.чен к выходу девятивходово1ро элемента ИЛИ своего разряда, а второй вход соединен с третьим входом первого трехвходового элемента ИЛИ и с выходом четвертого двухвходового элемента И своего разряда за исключением предпоследнего разряда, В котором второй вход третьего двухвходового элемента И подключен ко второму входу четвертого двухвходового элемента И предшествующего разряда и. к выходу двухвходового элемента ИЛИ своего разряда, первый и второй входы четвертых двухвходовых элементов И каждого разряда соответственно соединены с шинами знаков О и с выходами первых трехвходовых элементов ИЛИ разряда.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР

№ 137187, кл. Q О1 R 27/16, 1961.

2.Цифровые электроизмерительные приборы. Под ред. В. М. Шляндина, М., Энергия, 1972, с. 292-295, рис. 82 (прототип).

е

Фл.1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство ввода поправок в аналого-цифровой параллельно-последовательный следяной преобразователь | 1980 |

|

SU1010721A1 |

| Параллельно-последовательный цифровой вольтметр | 1979 |

|

SU879766A1 |

| "Цифровой следящий амплитудный анализатор | 1979 |

|

SU851273A1 |

| Устройство ввода поправок в хранительВРЕМЕНи | 1979 |

|

SU824118A1 |

| Матричное множительное устройство | 1980 |

|

SU942003A1 |

| ПОЛНЫЙ ОДНОРАЗРЯДНЫЙ СУММАТОР ПО МОДУЛЮ | 2011 |

|

RU2484519C1 |

| Аналого-цифровой параллельно-последовательный преобразователь | 1981 |

|

SU1023650A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1984 |

|

SU1282326A1 |

| ЦИФРОВОЙ ЧАСТОТОМЕР | 1996 |

|

RU2097774C1 |

| Цифровой амплитудный анализатор | 1980 |

|

SU1007038A1 |

Авторы

Даты

1981-09-23—Публикация

1979-10-04—Подача