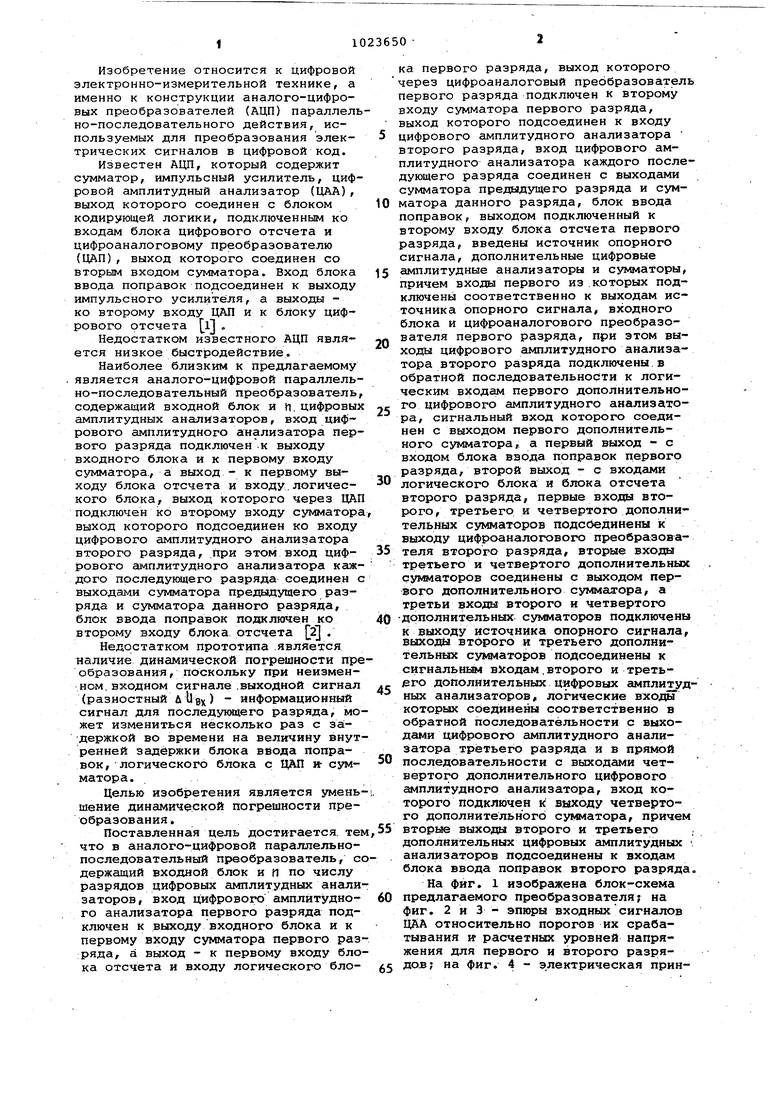

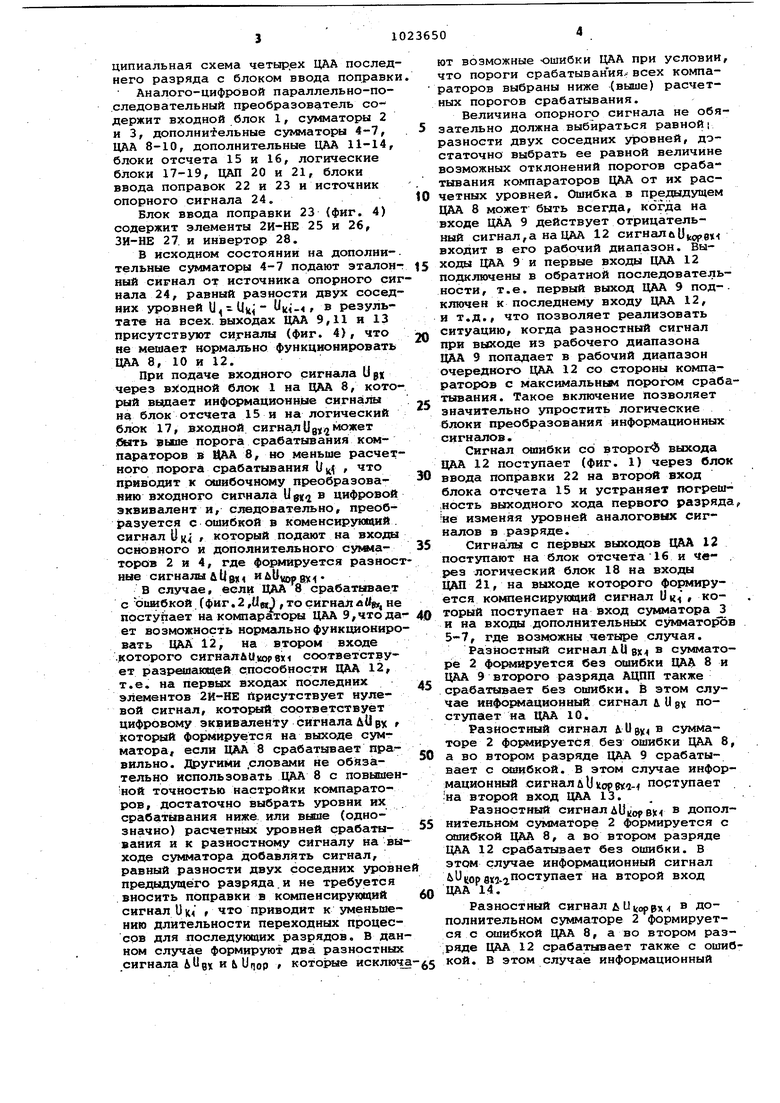

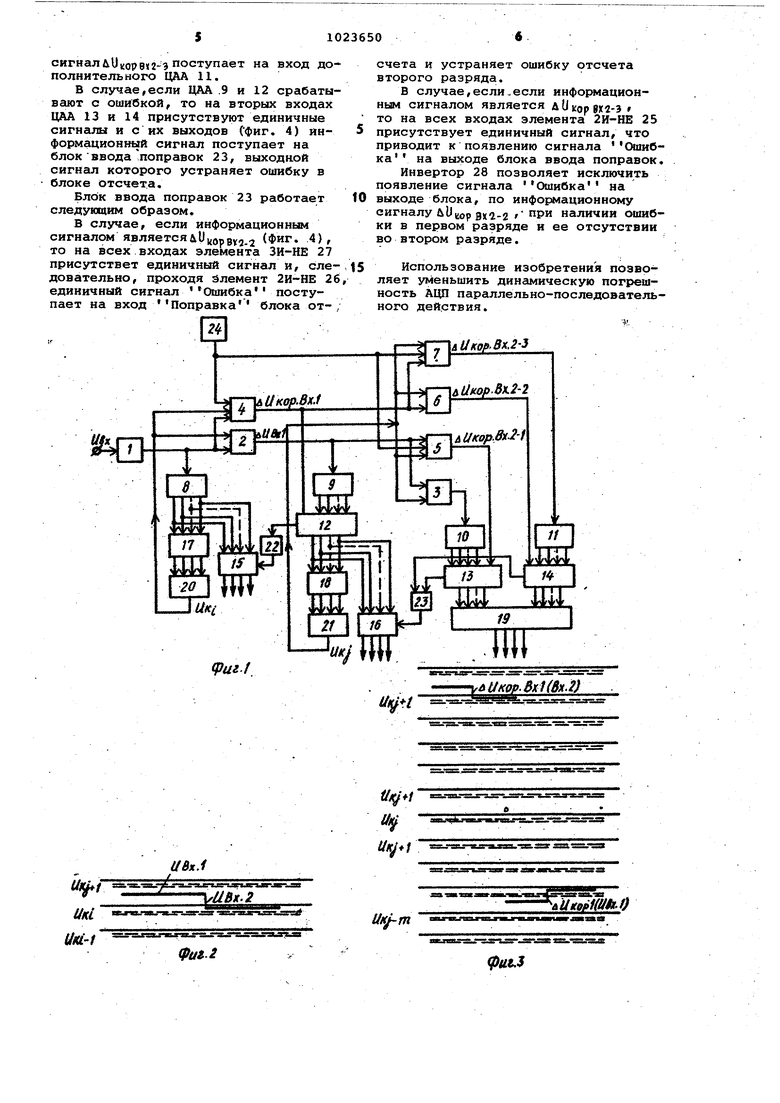

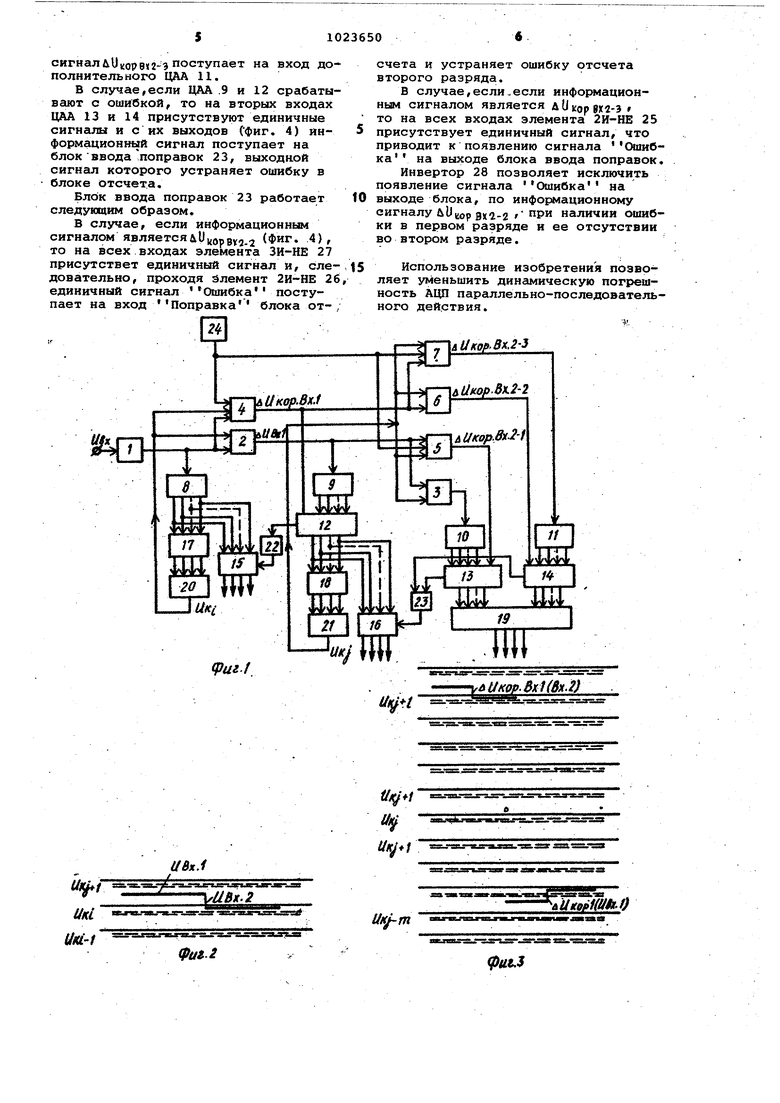

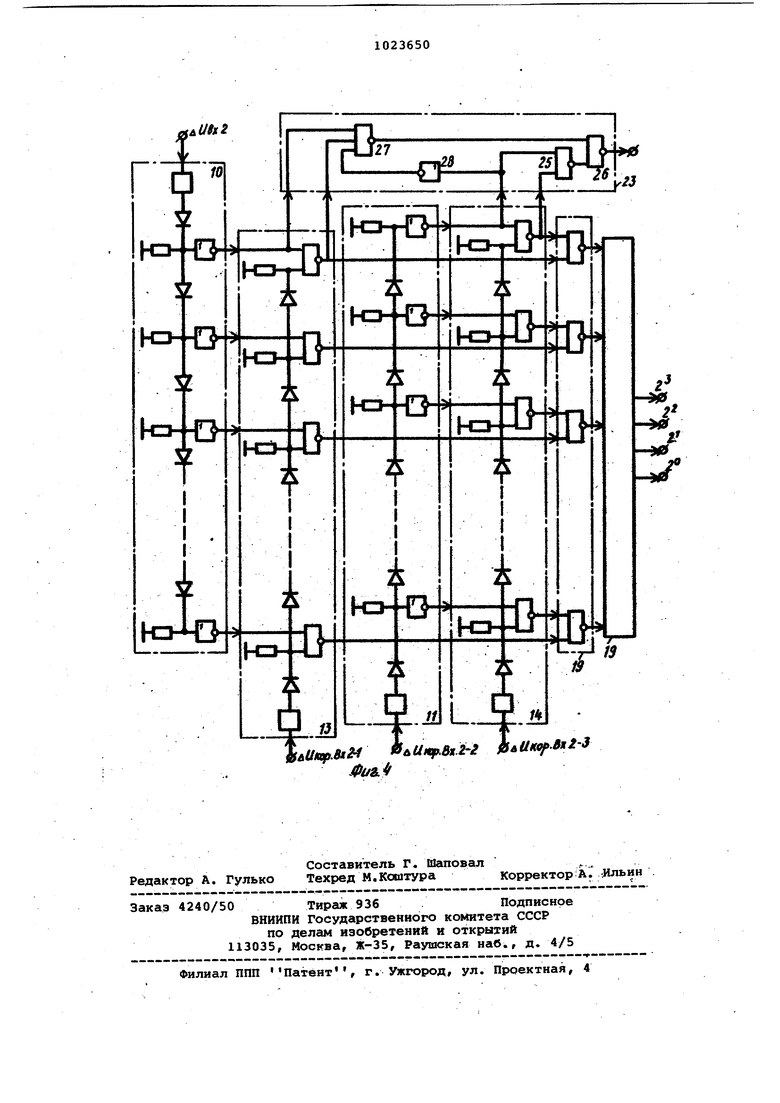

Изобретение относится к цифровой электронно-измерительной технике, а именно к конструкции аналого-цифровых преобразователей (АЦП) параллель но-последовательного действия, используемых для преобразования электрических сигналов в цифровой код. Известен АЦП, который содержит сумматор, импульсный усилитель, цифровой амплитудный анализатор (ЦАА), выход которого соединен с блоком кодирующей логики, подключенным ко входам блока цифрового отсчета и цифроаналоговому преобразователю (ЦАП), выход которого соединен со BTOpEiiM входом сумматора. Вход блока ввода поправок подсоединен к выходу импульсного усилителя, а выходы ко второму входу ЦДЛ и к блоку цифрового отсчета ij . Недостатком известного АЦП является низкое быстродействие. Наиболее близким к предлагаемому является аналого-цифровой параллельно-последовательный преобразователь содержащий входной блок и я. цифровых амплитудных анализаторов, вход цифрового амплитудного анализатора первого разряда подключен -к выходу входного блока и к первому входу сумматора., а выход - к первому выходу блока отсчета и входу.логического блока, выход которого через ЦАП подключен ко второму входу сумматора выход которого подсоединен ко входу цифрового амплитудного анализатора второго разряда, Лри этом вход цифрового амплитудного анализатора каждого последующего разряда соединен с выходами сумматора предыдущего разряда и сумматора данного разряда, блок ввода поправок подклкгчен ко второму входу блока, отсчета 2 . Недостатком прототипа .является наличие динамической погрешности пре образования , поскольку при неизменном, входном сигнале .выходной сигнал (разностный л Ugjj) - информационный сигнал для последующего разряда, мо жет измениться несколько раз с задержкой во времени на величину внут ренней задержки блока ввода поправок, логического блока с ЦАП и- сумматора. Целью изобретения является умень шение динамической погрешности преобразования . Поставленная цель достигается, те что в аналого-цифровой параллельнопоследовательный преобразователь, с держащий входной блок и и по числу разрядов цифровых амплитудных анали заторов, вход цифрового амплитудного анализатора первого разряда подключен к выходу входного блока и к первому входу сумматора первого раз ряда, а выход - к первому входу бло ка отсчета и входу логического блока первого разряда, выход которого через цифроаналоговый преобразователь первого разряда подключен к второму входу сумматора первого разряда, выход которого подсоединен к входу цифрового с1мплитудного анализатора второго разряда, вход цифрового амплитудного анализатора каждого последующего разряда соединен с выходами сумматора предалдущего разряда и сумматора данного разряда, блок ввода поправок, выходом подключенный к второму входу блока отсчета первого разряда, введены источник опорного сигнала, дополнительные цифровые амплитудные анализаторы и сумматоры, причем входы первого из.которых подключены соответственно к выходам источника опорного сигнала, входного блока и цифроаналогового преобразователя первого разряда, при этом выходы цифрового a шлитyднoгo анализатора второго разряда подключены в обратной последовательности к логическим входам первого дополнительного цифрового амплитудного анализатора, сигнальный вход которого соединен с выходом первого дополнительного сумматора,; а первый выход - с входом блока ваода поправок первого разряда, второй выход - с входами логического блока н блока отсчета второго разряда, первые входы второго, третьего и четвертого дополнительных сумматоров подсбединены к выходу цифроаналогового преобразователя второго разряда, вторые входы третьего и четвертого дополнительных сумматоров соединены с выходом первого дополнительного суммая-ора, а третьи входы второго и четвертого дополнительных сумматоров подключены к выходу источника опорного сигнала, выходы второго и третьего дополнительных сумматоров подсоединены к сигнальным входам.второго и третьего дополнительных цифровых амплитудных анализаторов, логические входа которьах соединены соответственно в обратной последовательности с выходами цифрового амплитудного анализатора тр этьего разряда и в прямой последовательности с выходами четвертого дополнительного цифрового амплитудного анализатора, вход которого подключен к выходу четвертого дополнительного сумматора, причем вторые выходе второго и третьего дополнительных цифровых амплитудных анализаторов подсоединены к входам блока ввода поправок второго разряда. На фиг. 1 изображена блок-схема предлагаемого преобразователя; на фиг. 2 и 3 - эпюры входныхсигналов ЦАА относительно порогов их срабатывания и расчетных уровней напряжения для первого и второго разрядо.в; на фиг. 4 - электрическая принципиальная схема четыр.ех ЦАА послед него разряда с блоком ввода поправк Аналого-цифровой параллельно-последовательный преобразователь содержит входной блок 1, сумматоры 2 и 3, дополнительные сумма-юра 4-7, ЦАА 8-10, дополнительные ЦАА 11-14, блоки отсчета 15 и 16, логические блоки 17-19, ЦАП 20 и 21, блоки ввода поправок 22 и 23 и источник опорного сигнала 24. Блок ввода поправки 23 (фиг. 4) содержит элементы 2И-НЕ 25 и 26, ЗИ-НЕ 27. и инвертор 28. В исходном состоянии на дополнительные сумматоры 4-7 подают эталон ный сигнал от источника опорного си нала 24/ равный разности двух сосед них уровней в результате на всех, выходах ЦАА 9,11 и 13 присутствуют сигналы (фиг. 4), что не мешает нормально функционировать ЦАА 8, 10 и 12. При подача входного сигнала U рх через входной блок 1 на ЦАА 8, кото рый выдает инфсч мационные сигналы на блок отсчета 15 и на логический блок 17, входной сигнал и может быть вьше порога срабатывания ксянпараторов в ЦАА 8, но меньше расчет ного порога срабатывания U f , что приводит к ошибочному преобразованию входного сигнала UgK. в цифровой эквивалент и, следовательно, преобразуется с ошибкой в коменсирукиднй . сигнал и , который подают на входы основного и дополнительного суиматоров 2 и 4, где формируется разнос ные сигналы &L(gy . В случае, если ЦАА 8 срабатывает с -опшвкой (фиг. 2,0(1, , то сигнал лй не поступает на компараторы ЦАА 9, что да ет возможность нормально функциониро вать ЦАА 12, на втором входе .которого сигнал&и 1ор8Х1 соответствует разрешающей способности ЦАА 12, т.е. на первых входах последних элементов 2Й-НЕ присутствует нулевой сигнал, который соответствует цифровому эквиваленту сигнала &ii рк г который формируется на выходе сумматора, если ЦАА 8 срабатывает правильно. Другими .словами не обязательно использовать ЦАА 8 с повышен ной точностью настройки компараторов, достаточно выбрать уровни их срабатывания ниже, или вшае (однозначно) расчетных уровней срабатывания и к разностному сигналу на вы ходе сумматора добавлять сигнал, равный разности двух соседних уровн предыдущего разряда.и не требуется вносить поправки в компенсирующий сигнал и К4 f что приводит к уменьшению длительности переходных процессов для последующих разрядов. В дан ном случае формируют два разностных сигнала iUgn и bUijop которые исключ ют возможные ошибки ЦАА при условии, что пороги срабатывания, всех компараторов выбраны ниже (выше) расчетных порогов срабатывания. Величина опорного сигнала не обязательно должна выбираться равной разности двух соседних у ровней, достаточно выбрать ее равной величине возможных отклонений порогов срабатывания компараторов ЦАА от их расчетных уровней. Ошибка в предадущем ЦАА 8 может быть всегда, когда на входе ЦАА 9 действует отрицательный сигнал,а на ЦАА 12 сигналйи рд,., входит в его рабочий диапазон. Выходы ЦАА 9 и первые входы ЦАА 12 подключены в обратной последовательности, т.е. первый выход ЦАА 9 под-ключен к последнему входу ЦАА 12, и т.д., что позволяет реализовать ситуацию/ когда разностный сигнал при выходе из рабочего диапазона ЦАА 9 попадает в рабочий диапазон очередного ЦАА 12 со стороны компараторов с максимальньм порогом срабатывания. Такое включение позволяет значительно упростить логические блоки преобразования информационных сигналов. Сигнал ошибки со второг 2 выхода ЦАА 12 поступает (фиг. 1) через блок ввода поправки 22 на второй вход блока отсчета 15 и устраняет погреш,ность выходного хода первого разряда, :не изменяя уровней аналоговых сигналов в разряде. Сигналы с первых выходов ЦАА 12 поступают на блок отсчета 16 и Чв- , рез логический блок 18 на входы ЦАП 21, на выходе которого формируется коьшеисирукхций сигнал II KI / который поступает на вход сумматора 3 и на входы дополнительных cs aTopbB 5-7, где возможны четыре случая. Разностный сигнёш лЦ в( в сумматоре 2 формируется без ошибки ЦАА 8 и ЦАА 9 второго разряда АЦПП также срабатывает без ошибки. В этом случае информбщиоиный сигнал i Ugy поступает на ЦАА 10. Разностный сигнал &Ugy4 сумматоре 2 фОЕвлируется без ошибки ЦАА 8, а во втором разряде ЦАА 9 срабатывает с снаибкой. В этом случае информационный сигнал д и itop . поступает на второй вход ЦАА 13. Разностный сигнал лиliopBXi дополнительном сумматоре 2 формируется с сшшбкой ЦАА 8, а во втором разряде ЦАА 12 срабатывает без ошибки. В этом случае информационный сигнал и иорв«мпоступает на второй вход ЦАА 14. Разностный сигнал U Ufcoppx в дополнительном сумматоре 2 формируется с (маибкой ЦАА 8, а во втором разряде ЦАА 12 срабатывает также с ошибкой. В этом случае информационный

сигналби| орв«2-3 поступает на вход дополнительного ЦАА 11.

В случае,если ЦАА .9 и 12 срабатывают с ошибкой, то на вторых входах ЦАА 13 и 14 присутствуют единичные сигналы и с их выходов Сфиг. 4) информационный сигнал поступает на блоквводапоправок 23, выходной сигнал которого устраняет ошибку в блоке Отсчета,

БлЪк ввода поправок 23 работает следующим образом,

В случае, если информационным

сигналом являетсяiUпорBV9 2 (Фиг, 4), то на всех входах элемента ЗИ-НЕ 27 присутствет единичный сигнал и, еледовательно, проходя элемент 2И-НЕ 26 единичный сигнал Ошибка поступает на вход Поправка блока от-; икор.Вк,1 ш4 lii лГ 12 I ПП Ж Й1Т1Ж asLfc ШГ t8 ш --&

счета и устраняет ошибку отсчета второго разряда.

В случае,еели,если информационным сигналом является AUKopgx2-3 i то на всех входах элемента 2И-НЕ 25 присутствует единичный сигнал, что приводит к появлению сигнала Ошибка на выходе блока ввода поправок,

Инвертор 28 позволяет исключить появление сигнала Ошибка на выходе блока, по информационно) сигналу Л и top вх 1-2 Ри наличии ошибки в первом разряде и ее отсутствии во втором разряде.

Использование изобретения позволяет уменьшить динамическую погрешность АЩ1 параллельно-последовательного действия. ликорВх.2 АуЧ/ -: -3

| название | год | авторы | номер документа |

|---|---|---|---|

| Параллельно-последовательный аналого-цифровой преобразователь | 1984 |

|

SU1282326A1 |

| Устройство ввода поправок в аналого-цифровой параллельно-последовательный следяной преобразователь | 1980 |

|

SU1010721A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1981 |

|

SU1039025A1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1181144A1 |

| Биполярный цифровой амплитудный анализатор | 1983 |

|

SU1208605A1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1202055A1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1193808A1 |

| Цифровой анализатор спектра | 1981 |

|

SU974374A1 |

| Преобразователь угла поворота вала в код | 1977 |

|

SU734775A1 |

| Цифровой фильтр | 1988 |

|

SU1566471A1 |

АНАЛЮГО-ЦИФРОВОЙ ПАРАЛЛЕЛЬ;НО-ПОСЛЕЛОВАТЕЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ, содержащий входной блок и п по числу разрядов цифровых амплитудиых анализаторов, вход цифрового амплитудного анализатора первого разряда подключен к выходу входного блока и к первому входу сумматора первого разряда, а выход - к первому входу блока отсчета первого разряда и вхо-. ду логического блока первого разряда, выход которого через цифроаналоговый преобразователь первого разряда подключен к второму входу сумматора первого разряда, выход которого подсоединен к входу цифрового амплитудного анализатора второго разряда, вход цифрового амплитудного анализатора каждого последующего разряда соединен с выходами сумматора предудущего разряда и сумматора данного разряда, блок ввода поправок, выходом подключенный к второму входу блока отсчета первого разряда, о т л ичающийся тем, что, с целью уменьшения динамической погр иности преобразования,в него введены источник onojpHoro сигнала, дополнительные цифровые амплитудные анализатосш и сумматоры, входы первого из которых, подключены соответственно к выходам источника опорного сигнала, входного блока и цифроанаяогового преобразователя первого разряда, при зтсял выхода цифрового амплнтудиого анализатора второго разряда подключены J обратной последовательности к логическим входам первохх) дополнительного цифрового акошитуяного анализатора, сигнальный вход которого соединен с выходом первого дополнительного сумматора, первый выход - с входом блока ввода поправок первого разряда, второй выход - с входами логического блока и блока отсчета второго разряда, первые входы второго, третьего и четвертого дополнительных суктаторов подсоединены к выходу цифроаналоговогр преобразователя второго разряда, вгорае входы третьего и четвертого дополнительных сумматоров соединены с выкодом перiBOro дополнительного сумматора, третьи входы второго и четвертого дополнительных суммат( подключены к выходу источника опорного сигнала, выходы второго и третьего дополнителышос сумматоров подсоединены к сигнальным входам второго и третьего IND дополнительных цифровых амплитудных со сь анализаторов, логические входы котоPlix соединены соответственно в обрат Нрй последоаатёльирсти с йифел рового амплитудного анализахор а третьего разряда и в прякю последо-вательностн с выходами че:Гвертого дополнительного цифрового амплитудного анализатора, вход которого под:Ключен к выходу четвертого дополнительного сумматора, прнчем вторые вы|ходы второго и третьего дополнитель:ных цифровых амплитудных анализато;ров подсоединены к входам блока ввода поправок второго разряда.

авж.1

i.s-a.Sajstjsrtanjsnja-jt

.2

(ри1.2

AUMfKUIx O

UK/-т

tf&J

AUttp. AUMf,en:i- Ф1/&

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| ЦИФРОВОЙ ВОЛЬТМЕТР ПАРАЛЛЕЛЬНО-ПОСЛЕДОВАТЕЛЬНОГО УРАВНОВЕШИВАНИЯ | 0 |

|

SU266937A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Цифровые электроизмерительные (приборы | |||

| Под ред | |||

| В.М | |||

| Шдяндина | |||

| М., Энергия, 1972, с | |||

| ПРИСПОСОБЛЕНИЕ ДЛЯ УСТРАНЕНИЯ СКОЛЬЖЕНИЯ КОЛЕС АВТОМОБИЛЕЙ | 1920 |

|

SU292A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1983-06-15—Публикация

1981-04-01—Подача