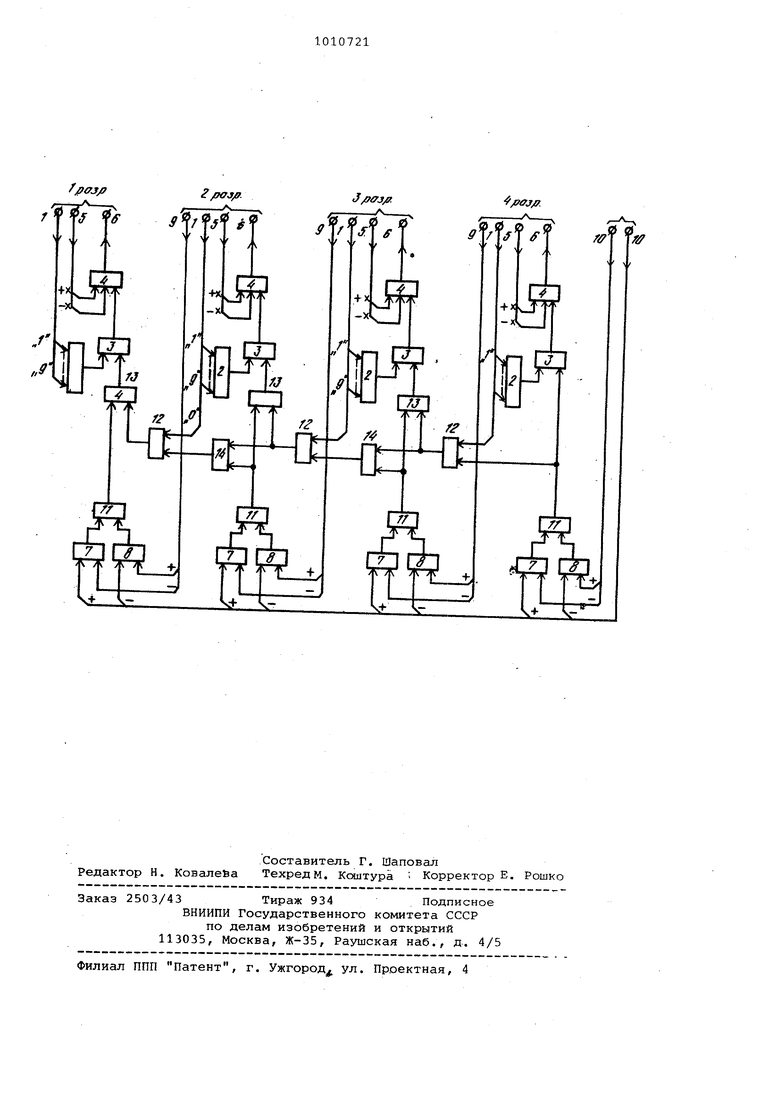

Изобретение относится к цифровой измерительной и вычислительной технике, а именно к конструкции устройства ввода поправок в аналогоцифровые преобразователи (АЦП),используемые при измерении напряжений Известен АЦП с устройством ввода поправок, разряды которого содержат цифровой амплитудный анализатор ДАД) делитель напряжения, блок ввода поправок и вычитающее устройство i Недостатком указанного преобразо вателя является Низкая точность. Известен также аналого-цифровой параллельно-последовательный следящий преобразователь, в котором устройство ввода поправок содержит п первых элементов ИЛИ, соответствующ М разрядам преобразователя, входы которых подключены к соответствующи входным числовым шинам, первые элементы И, первый вход каждого из которых подключен к выходу соответств ющего первого элемента ИЛИ, а выход каждого элемента И, кроме первого, разряда подключен к первому входу соответствующего второго элемента ИЛИ, второй и третий входы которого подсоединены к шинам положительного и отрицательного превышения декадно го интервала, а выход подключен к соответствующей выходной шине, втор и третьи элементы И, входы которых в каждом разряде, кроме первого, подключены соответственно к первым шинам полярности последующих разрядов, вторые входы - к второй шине знакового разряда, а выходы в каждо разряде, кроме первого, подключены к входам третьегоэлемента ИЛИ, чет вертые элементы И в каждом разряде, кроме первого, подключены к шинам знака О последующих разрядов Сз. Недостатком известного устройства ввода поправок является ограни-. ченность рабочего диапазона, так как при определении поправки в ДАЛ преобразователя, величина которой больше или равна интервалу разрешающей способности ЦАА очередного разряда, устройство ввода поправок не может внести поправку в соответ|Ствующие разряды преобразователя. Цель изобретения - расширение ра бочего диапазона ввода поправок. Поставленная цель достигается тем, что в устройство ввода поправок в аналого- цифровой параллельнопоследовательный следящий преобразователь, содержащее п первых элементов ИЛИ, соответствующих п разря дам преобразователя, входы которых подключены к соответствующим входным числовым шинам, первые элементы И, первый вход каждого из которых подключен к выходу соответствующего первого элемента ИЛИ, а выход каждого элемента И, кроме первого разряда, подключен к первому входу соответствующего второго элемента ИЛИ, второй и третий входы которого подсоединены к шинам положительного и отрицательного превышения декадного интервала, а выход подключен к соответствующей выходной шине, вторые и третьи элементы И, первые входы которых в каждом разряде, кроме первого, подключены соответственно к первым шинам полярности последующих разрядов, вторые входы - к второй шине знакового разряда, а выходы в каждом разряде, кроме первого, подключены к входу соответствующего третьего элемента ИЛИ, четвертые элементы И в каждом разряде, кроме последнего и знакового, первые входы которых в разрядах, кроме первого, подключены к шинам знака О последующих разрядов, во все разряды, кроме последнего и знакового, введены четвертые элементы ИЛИ, в . разряды, кроме .перво.го, последнего и.знакового, - пятые элементы ИЛИ, а в первый разряд - второй и третий элементы И, выходы которых подключены к входу третьего элемента ИЛИ, выход которого соединен с первым входом четвертого элемента ИЛИ, первые, входы - к шинам полярности второго разряда, а вторые входы - к второй шине знакового разряда, причем первый вход четвертого элемента ИЛИ в каждом разряде соединен с выходом третьего элемента ИЛИ 6, а второй вход - к выходу четвертого элемента И, первый вход которого в первом разряде подключен к шине знака О второго разряда, а второй вход в каждом разряде - с выходом пятого элемента ИЛИ последующего разряда, первый вход которого в каждом разряде подключен к первому входу четвертого элемента ИЛИ, второй вход к второму входу четвертого элемента ИЛИ, первый и второй входы второго элемента ИЛИ в первом разряде подключены к шинам положительного и отрицательного превышения декадного интервала, выход - к выходной шине, а третий вход соединен с выходом первого элемента И, второй вход которого в каждом разряде, кроме последнего и знакового, подключен к выходу четвертого элемента ИЛИ, На чертеже изображена блок-схема предлагаемого устройства. Устройство содержит входные клеммы 1, соответствующие знакам О и от 1 до 9 во всех разрядах, кроме последнего, подключенные к входам первых элементов ИЛИ 2, первые элементы И 3, первые входы которых подключены к выходам первых элементов ИЛИ 2, а выходы во всех разрядах, кроме последнего, подключены к первым входам вторых элементов ИЛИ 4, второй и третий входы элемента ИЛИ 4 подсоединены к клеммам 5 поло жительного (+х ) и отрицательного 1,-х) превышения декадного интервала а выход подключен к выходной клемме 6 своего разряда, входы вторых и третьих элементов 7 и 8 подключены соответственно к клеммам 9 отрицательной и положительной полярности входного сигнала последующих разрядов, а их вторые входы подключены к клеммам 10 положительной и отрицательной полярности дополнительного входа последнего разряда. Выходы второго и третьего элементов И 7 и 8 прдключены к входам третьего элемента ИЛИ 11, первые входы четвертых элементов И 12 подключены к . клеммам 1 знака О последующих разрядов, во все разряды, кроме двух последних, введены четвертые -элементы ИЛИ 13, а в- разряды, кроме первого и двух последних - пятые элементы ИЛИ 14.

Вторые входы первых элементов И 3 подключены к выходам четвертых элементов И 13, первые входыкоторых соединены с выходами третьих элементов ИЛИ 11, а вторые - подключены к выходам четвертых : элементов И 12, Вторые входы четвертых элементов И 12 соединены с выходами пятых элементов ИЛИ 14 последующих разрядов, первые входы которых, подключены к первым входам четвертьах элементов ИЛИ 13. Вторые входы пятых элементов ИЛИ 14 соединены с вторыми входами четвертых элементов ИЛИ 1

Устройство работает следующим образом. .

Предположим, что на вход АЦП подан входной сигнал Ugv 24,0 В, а он -зафиксировал выходной код, который соответствует 23,7.

В этом случае с учетом принципа работы параллельно-последовательного преобразователя, если входной сигнал равен 24,0 В и первый разряд зафиксировал знак 2, то на очередной разряд обработки АЦП поступают два сигнала - это входной +24,0 В и компенсирующий - 20,0 В, в результате этого формируется разностный сигнал (24,0 - 20,0 4,0 в).

Предположим, что во втором разряде обработки вместо знака М.Г АЦП зафиксировал знак 3(23,7 В)и на очередной третий разряд обработки АЦП поступает двасигнала - входной +24,0 В и компенсирующий - 23,0 В, в результате разностный сигнал будет равен 24,0 - 23,0 1,0 В.

0

Если учесть диапазон этого разряда, то величина 1,0 В для него будет выходить за его пределы, что приводит к зашкаливанию в ЦАА, вследствие чего сигнал появится на шинах +х, а коррекрируквдий сигнал через

5 элемент ИЛИ 4 третьего разряда пос тупает на один из входов ЦАА соответствующего разряда обработки АЦП, в котором на выходе установится близким к разностному сигналу 1,0 В

0 знак 9., В результате информационный сигнал корректировки погретяности с выхода +х третьего разряда исчезает..

5

На четвертый разряд АЦП поступают сигналы - входной +24,0 В и компенсирукйций - 23,9 9,разностый сигнал будет равен 0,1 В (24,0 - 23,9 О,1В) и т.д. В конечном счете

0 с помощью предлагаемого устройства АЦП зафиксирует выходной под эквивалентный сигналу в 23,999 ... В, т.е. с минимальной погрешностью.

В случае, если пороги срабатыва5ния ЦАА дрейфуют,-то устройство ввода поправок также может исправлять , результат преобразования АЦП. Например , дрейф порогов срабатывания ЦАА соседних разрядов происходит в одном направлении + и +, - и - .в

0 случае, когда при входном сигнале 30,0 В будет зафиксирован в первом разряде знак 4. В результате разностный сигнал в АЦП очередного раз;ряда будет равен -16,0 В (30,0 5- 40,0 т10,0), что приводит к ПО-явлению сигнала на двух входах элемента И 7 и через элементы ИЛИ 11 и . 13, И 3 и ИЛИ 13 корректирующий сигнал поступает на дополнительный

0 вход ЦАА первого разряда.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой преобразователь параллельно-последовательного следящего уравновешивания | 1979 |

|

SU866487A1 |

| Аналого-цифровой параллельно-последовательный преобразователь | 1981 |

|

SU1023650A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1984 |

|

SU1282326A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1981 |

|

SU1039025A1 |

| Параллельно-последовательный цифровой вольтметр | 1979 |

|

SU879766A1 |

| Способ аналого-цифрового преобразования и устройство для его осуществления | 1979 |

|

SU964981A1 |

| Матричное множительное устройство | 1980 |

|

SU942003A1 |

| Аналого-цифровой преобразователь знакопеременных сигналов | 1987 |

|

SU1483641A1 |

| Преобразователь код-напряжение | 1984 |

|

SU1197084A1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1181144A1 |

УСТРОЙСТВО ВВОДА ПОПРАВОК В АНАЛОГО-ЦИФРОВОЙ ПАРАЛЛЕЛЬНО-ПОСЛЕДОВАТЕЛЬНЫЙ СЛЕДЯЩИЙ ПРЕОБРАЗОВА,ТЕЛЬ, содержащее п первых элементов ИЛИ, соответствующих п разрядам преобразователя, BxotoJ которых подключены к соответствующим входным числовым шинам, первые элементы И, первый вход каждого --из которых подключен к выходу соответствующего первого элемента ИЛИ, а выход каждого элемента И, кроме первого разряда, : подключен к первому входу соответствующего второго элемента ИЛИ, второй и третий входы которого подсоединены к шинам .положительного и отрицательного превышения декадного интервала, а выход подключен к соответствующей выходной шине, вторые и третьи элементы И, первые входы которых в каждом разряде, кроме первого , подключены соответственно к первым шинам полярности последую- щих разрядов, вторые входы - к второй шине знакового разряда, а выходы в каждом разряде, кроме первого, подключены к входу соответствующего третьего элемента ИЛИ, четвертые элементы Ив каждом разряде, кроме последнего и знакового, первые входы -Х ГЛ .- -;t- „ 5 Л 7j : г ;::-,а у .,1 J - l;,.- .г; f г i. S: 1 t ufeiJ;fb3J:;;4i которых в разрядах, кроме первого, подключены к шинам знака О последующих разрядов, отличаю,г щ е е с я тем, что, с целью расширения рабочего диапазона вводимых поправок, во все разряды, кроме последнего и знакового, введены четвертые элементы ИЛИ, а разряды, кроме первого, последнего и знакового J - пятые элементы ИЛИ,-а в первый разряд - второй и третий элементы И, выходы которых подключены к входу третьего элемента ИЛИ, выход которого соединен с первым входом четвертого элемента ИЛИ, первые входы - к шинам полярности второго разряда, а вторые входы - к второй шине знакового разряда, причем перСО вый вход четвертого элег Лента ИЛИ в каждом разряде соединен с выходом третьего элемента ИЛИ, а второй вход к выходу четвертого элемента И, первый вход которого в первом разряде подключен к шине знака О второго разряда, а второй вход в каждом разряде - к выходу пятого элемента ИЛИ последующего разряда,, первый вход которого в каждом разряде подключен к первому входу четвертого элемента ИЛИ , второй - к второму входу 1С четвертого элемента ИЛИ, первый и второй входы второго элемента ИЛИ в первом разряде подключены к шинам положительного и отрицательного превышения декадного интервала, выходы - к выходной шине, а третий вход соединен с выходом первого элемента И, второй вход которого в каждом разряде, кроме последнего и знакового, подключен к выходу четвертого элемента ИЛИ.

Авторы

Даты

1983-04-07—Публикация

1980-10-20—Подача