(5) МАТРИЧНОЕ МНОЖИТЕЛЬНОЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения матричного типа | 1980 |

|

SU935948A1 |

| Устройство для умножения с накоплением | 1982 |

|

SU1108087A1 |

| Устройство для умножения | 1989 |

|

SU1689946A1 |

| Последовательное множительное устройство | 1985 |

|

SU1307455A1 |

| Устройство для умножения чисел | 1990 |

|

SU1714595A1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ | 1991 |

|

RU2021633C1 |

| Устройство для умножения | 1979 |

|

SU911514A1 |

| Устройство для деления | 1990 |

|

SU1746378A1 |

| Устройство для умножения | 1981 |

|

SU1018115A1 |

| Устройство для умножения чисел | 1988 |

|

SU1575173A1 |

Изобретение относится к вычислительной технике и может применяться в различных цифровых комплексах, например, для цифровой фильтрации. Известно матричное устройство для умножения и сложения, содержащее два регистра сомножителей и матрицу полусумматоров с вентилями на входе. Разрядные выходы регистров сомножителей подключены к вентилям попарно таким образом, что каждый разряд пер вого сомножителя на одном из вентиле подключен 6 паре с каждым разрядом второго сомножителя. Выходные сигналы вентилей складываются на полусумматорах, образующих матричную структуру, суммирующую все выходные сигна лы вентилей в соответствии с их весами, определяемыми номерами разрядов сомножителей, сигналы которых поданы на входы соответствующих вентилей. На выходе матрицы при этом формируется сигнал произведения 1. Недостатком известного устройства является невозможность умножения чисел с произвольным знаком, представленных, например, в дополнительном коде, так как в структуре устройства отсутствуют какие-либо средства для умножения отрицательных чисел, что сужает область его применения. Кроме того, устройство отличается высокой сложностью, обусловленной построением матрицы на полусумматорах, требуемое количество которых велико и равно удвоенному произведению количества разрядов в первом сомножителе на количество разрядов во втором сомножителе . Наиболее близким по техническому решению к предлагаемому является устройство, содержащее вычислительные блоки, объединенные в К линеек (К -; N - разрядность первого сомножителя; п - количество подразрядов, на

которые разбивается первый сомножитель; М - разрядность второго сомножителя; ), каждый из которых включает в себя п т-разрядные умно кители и многоразрядный сумматор, причем П информационных входов каждого умножителя соединены соответственно с разрядными входными шинами первого сомножителя устройства, m информационных входов каждого умножителя соединены соответственно с разрядными входными шинами второго сомножителя устройства, информационные входы умножителей являются соответствующими информационными входами вычислительных блоков, выходы умножителей каждого вычислительного блока соответственно соединены с первыми входами многоразрядного сумматора, выходы которого являются соответствующими выходами вычислительных блоков, выходы переноса многоразрядного сумматора являются выходами переноса соответствующего вычислительного блока входы переноса многоразрядного сумма- 5 тора являются входами переноса соответствующего вычислительного блока, вторые входы многоразрядного сумматора являются входами частичного результата вычислительных блоков t Недостатком известного устройства является невозможность умножать на нем числа с произвольным знаком в дополнительном коде, так как в струк туре устройства отсутствуют элeмeнты обрабатывающие сомножители с произвольным знаком, что ограничивает область его применения. Цель изобретения - расширение области применения путем обеспечения умножителя чисел с произвольным знэ ком в дополнительном коде. Поставленная цель достигается тем что в устройство введены сумматор по правок, группа из N двухвходовых эле ментов И-НЕ, группа из М двухвходовых элементов И-НЕ, сумматор переносов и блок формирования знака произведения, причем выход блока формирования знака произведения является знаковым выходом устройства, первые входы элементов И-ИЕ группы из М дву входовых элементов И-НЕ соединены с соответствующими разрядными входными шинами второго сомножителя, а вторые входы объединены и подключены к шине знака первого сомножителя устройства первые входы элементов И-НЕ группы из N двухвходовых элементов И-НЕ сое

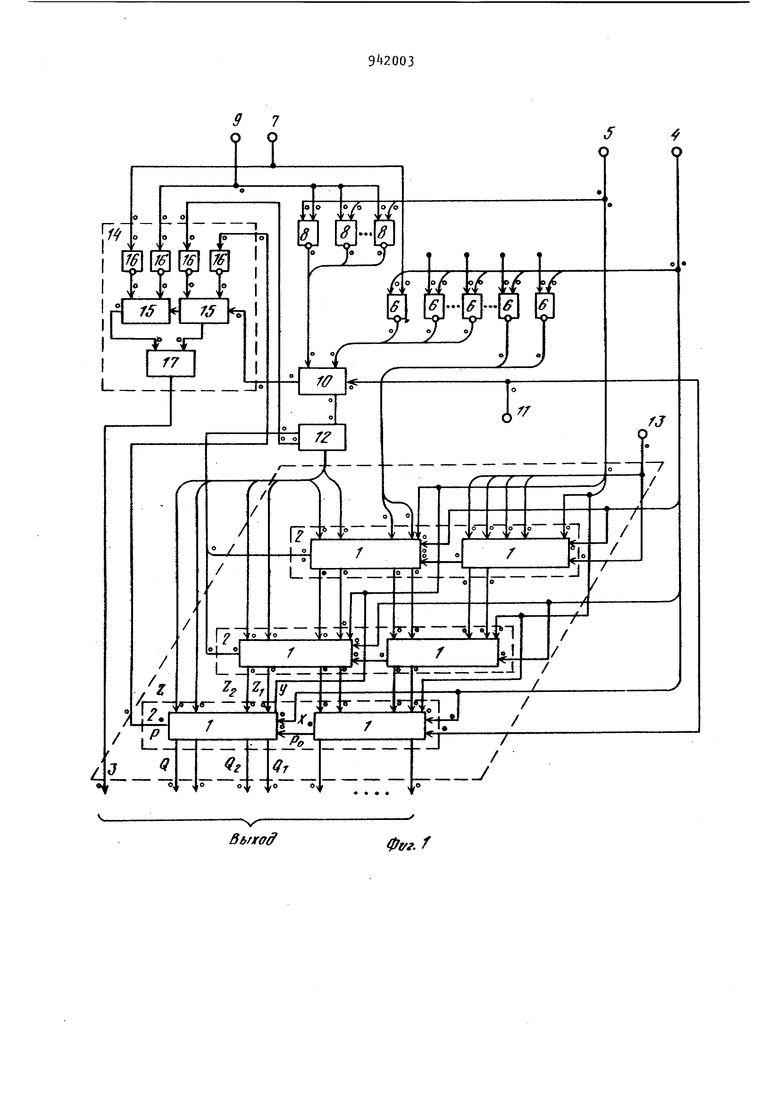

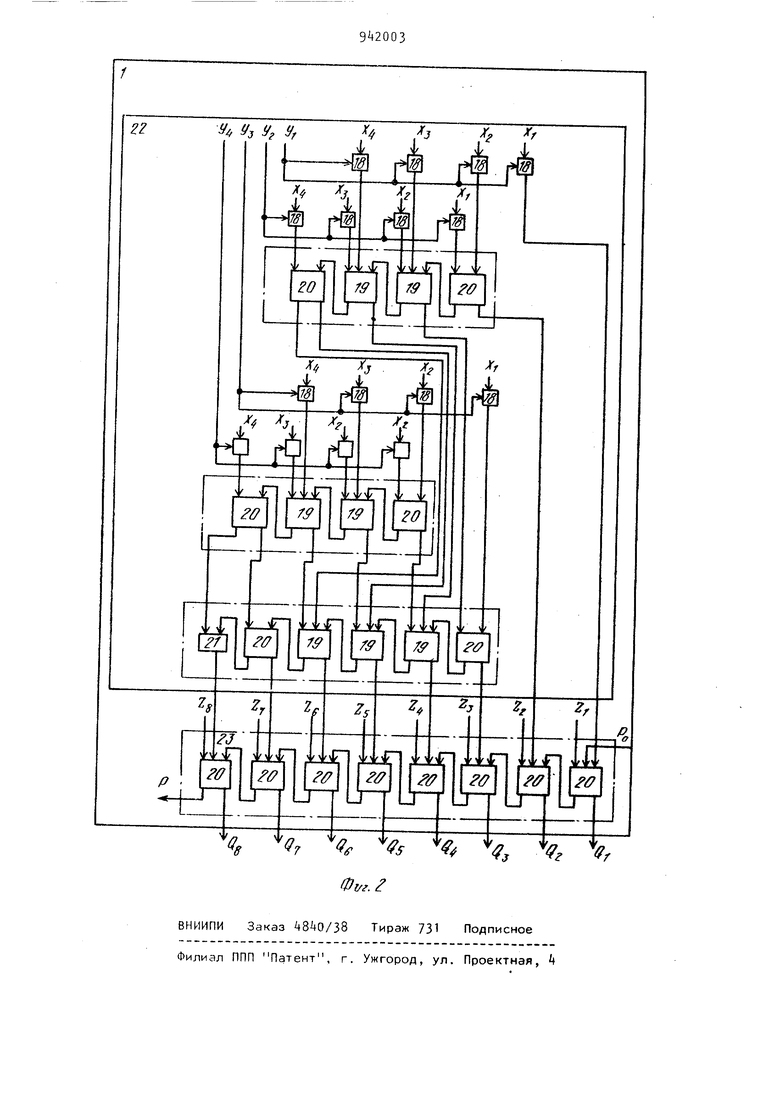

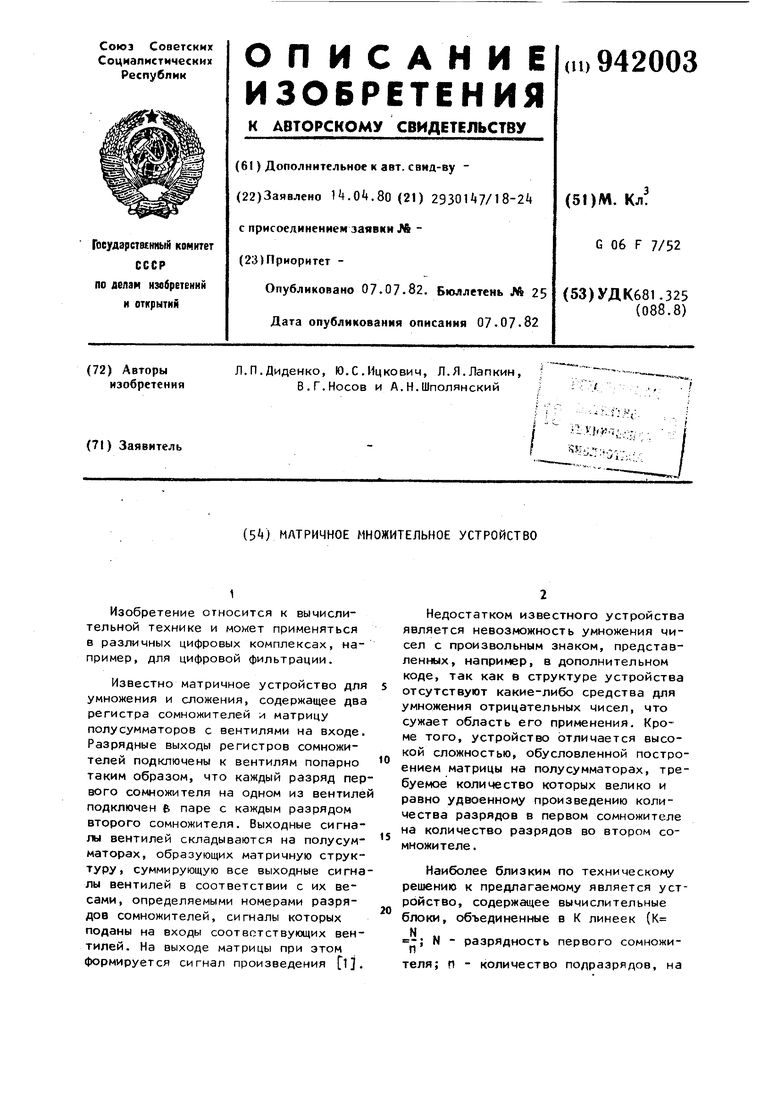

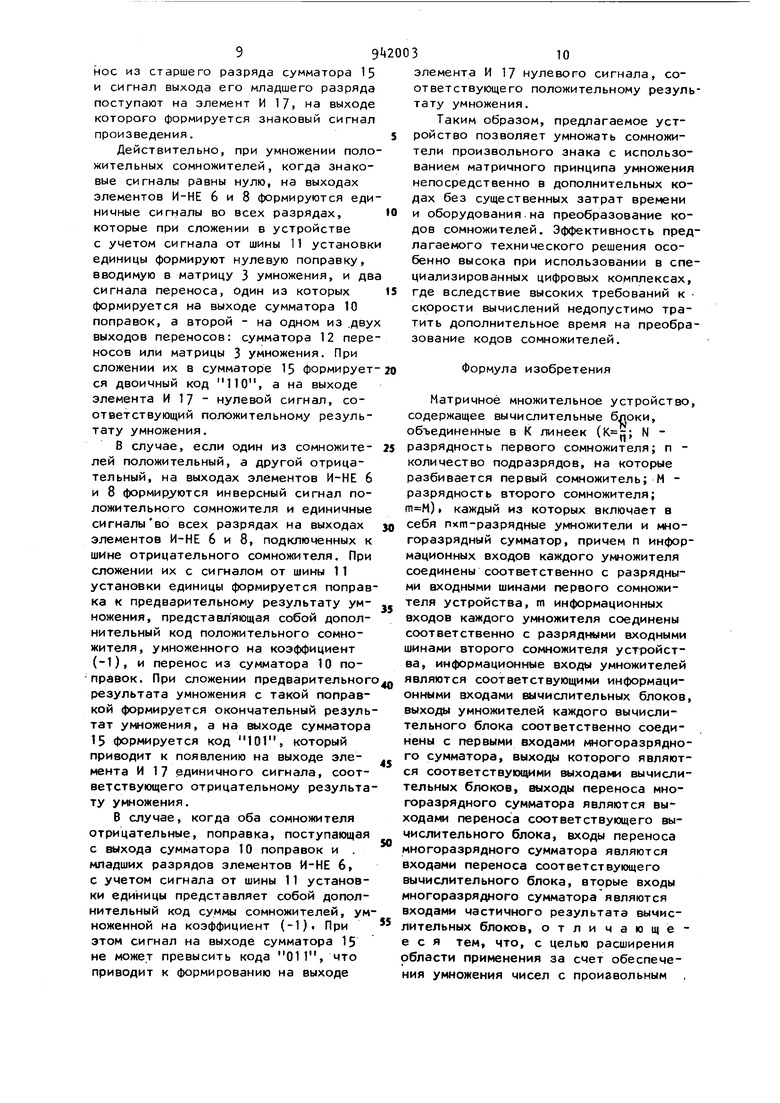

динены с соответствующими разрядными входными шинами первого сомножителя, а вторые входы объединены и подключены к шине знака второго сомножителя, входы первой группы сумматора поправок соединены соответственно с выходами М элементов И-НЕ группы иЗ М двухвходовых элементов И-НЕ, входы второй группы сумматора поправок соединены соответственно с выходами М элементов И-НЕ группы из N двухвходовых элементов И-НЕ, выходы суммы сумматора поправок соответственно соединены с входами сумматора переносов, выход переноса из старшего разряда которого соединен с первым входом блока формирования знака произведения, второй вход которого соединен с выходом переноса из старшего разряда сумматора поправок, а третий вход - с выходом переноса старшего вычислительного блока последней линейки, выходы переноса старших вычислительных блоков остальных линеек объединены и подключены к зходу переноса сумматора переносов, выход переноса младшего вычислительного блока каждой линейки соединен с входом переноса старшего вычислительного блока этой же линейки, входы переноса сумматора поправок и младшего вычислительного блока последней линейки объединены и подключены к шине установки единицы устройства, вход переноса и входы частичного результата младшего вычислительного блока объединены и подключены к шине округления устройства, выходы M-N элементов И-НЕ группы из двухвходовых элементов И-НЕ соответственно соединены с младшими входами частичного результата старшего вычислительного блока первой линейки, N старших входов частичного результата старших вычислительных блоков каждой линейки соединены с соответствующими выходами сумматора переносов, половина младших входов частичного результата младших вычислительных блоков каждой последующей линейки соответственно соединены с половиной старших выходов младших вычислительных блоков каждой предыдущей линейки, половина младших выходов старших вычислительных блоков каждой предыдущей линейки соответственно соединены с половиной старших входов частичного результата младших вычислительных блоков каждой последующей линейки, половина старших выходов старшего вычислительного блока каждой предыдущей линейки соответственно соединены с половиной младших входов частичного результата старшего вычислительного блока каждой последующей линейки, выходы вычислитель ных блоков последней линейки являются выходами устройства, четвертый вход блока формирования знака произведения соединен с шиной знака перво го сомножителя, пятый вход блока фор мирования знака произведения соединен с шиной знака второго сомножителя. В устройстве блок формирования знака произведения содержит четыре элемента НЕ, двухразрядный сумматор, элемент И, причем входы первого, вто рого, третьего и четвертого элементов НЕ соответственно соединены с третьим, первым, четвертым и пятым входами блока формирования знака про изведения, выходы элементов НЕ соеди нены соответственно с информационными входами двухразрядного сумматора, вход переноса младшего разряда которого соединен с вторым входом блока формирования знака произведения, выход переноса сумматора младшего разряда соединен с входом переноса сумматора старшего разряда, выход пере1носа которого соединен с первым входом элемента И, второй выход которого соединен с выходом суммы сумматора младшего разряда, а выход является выходом блока формирования знака произведения. На фиг.1 представлена структурная схема матричного множительного устро ства; на фиг.2 - вычислительный блок устройства. Устройство содержит вычислительны блоки 1, объединенные в линейки 2, образующие матрицу 3 умножения, шину первого сомножителя, шину 5 второго сомножителя, группу из N двухвходовых элементов И-НЕ 6, шину 7 знака второго сомножителя, группу из М двухвходовых элементов И-НЕ 8, шину 9знака первого сомножителя, суммато 10поправок, шину 11 установки едини цы, сумматор 12 переносов, шину 13 округления, блок 1 формирования зна ка произведения, который содержит двухразрядный сумматор 15, элементы НЕ 16, элемент И 17. Вычислительный блок Т состоит из элементов И 18, одноразрядных сумматоров 19 на три входа, одноразрядных сумматоров 20 на два входа и элемен93 та ИЛИ 21, которые образуют гтт-разрядный умножитель 22, выходы умножителя соединены соответственно с первыми входами сумматоров 20, образующих многоразрядный сумматор 23. В устройстве п информационных входов каждого вычислительного блока 1 соединены соответственно с разрядными входными шинами k первого сомножителя устройства, гп информационных входов - с шинами 5 второго сомножителя устройства, информационные входы умножителей 22 являются соответствующими информационными входами вычислительных блоков 1, выходы умножителей 22 каждого вычислительного блока 1 соответственно соединены с первыми входами многоразрядного сумматора 23, выходы которого являются соответствующими выходами вычислительных блоков 1, выходы переноса многоразрядного сумматора 23 являются выходами переноса соответствующего вычислительного блока 1, входы переноса многоразрядного сумматора 23 - входами переноса соответствующего вычислительного блока 1, вторые входы многоразрядного сумматора 23 являются входами частичного результата вычислительных блоков 1. Выход блока 14 формирования знака произведения является знаковым выходом устройства, первые входы группы из М двухвходовых элементов И-НЕ 8 соединены с соответствующими разрядными входными шинами 5 второго сомножителя , а вторые входы объединены и подключены к шине 9 знака первого сомножителя устройства, первые входы группы из N двухвходовых элементов И-НЕ 6 соединены с соответствующими разрядными входными шинами k первого сомножителя, а вторые входы объединены и подключены к шине 7 знака второго сомножителя. Входы первой группы сумматора 10 поправок соединены соответственно с выходами М элементов И-НЕ 8, входы второй группы - с выходами N элементов И-НЕ 6, выходы суммы сумматора 10 поправок соответственно соединены со входами сумматора 12 переносов, выход переноса из старшего разряда которого соединен с первым входом блока It формирования знака произведения, второй вход которого соединен с выходом переноса из старшего разряда сумматора 10 поправок, а третий вход - с вы 4одом переноса старшего вычислительного блока 1 последней линейки. Выходы переноса старших вычислительных блоков 1 остальных линеек объединены и подключены к выходу переноса сумматора 12 переносов, выход переноса младшего вычислительного блокд/1 каждой линейки соединен с входом переноса старшего вычислитель ного блока 1 этой же линейки, входы переноса сумматора 10 поправок и младшего вычислительного блока 1 пос ледней линейки объединены и подключены к шине 11 установки единицы устройства. Выход переноса и входы частичного результата младшего вычис лительного блока 1 объединены и подключены к шине 13 округления устройства, выходы M-N элементов 6 И-НЕ соответственно соединены с младшими входами частичного результата старшего вычислительного блока 1 первой линейки, N старших входов частичного результата старших вычислительных блоков 1 каждой линейки соединены с соответствующими выходами сумматора 12 переносов. Половина младших входов частичного результата младших вычислительных блоков 1 каждой последующей линейки соответственно соединены с половиной старших выходов младших вычислительных блоков 1 каждой предыдущей линейки, половина младших выходов стар ших вычислительных блоков 1 каждой предыдущей линейки соответственно соединены с половиной старших входов частичного результата младших вычислительных блоков 1 каждой последующей линейки, половина старших выходов старшего вычислительного блока 1 каждой предыдущей линейки соответственно соединены с половиной младших входов частичного результата старшег вычислительного блока 1 каждой после дующей линейки. Выходы вычислительны блоков 1 последней линейки являются выходами устройства, четвертый вход блока формирования знака произведения соединен с шиной 9 знака первого сомножителя, пятый вход блока }Ц формирования знака произведения соединен с шиной 7 знака второго сомножителя . В блоке k формирования знака произведения входы первого, второго, третьего и четвертого элементов НЕ 1 соответственно соединены с третьим, первым, четвертым и пятым входами блока формирования знака произве-, дения, выходы элементов НЕ 16 соединены соответственно с информационными входами двухразрядного сумматора 15. вход переноса младшего разряда которого соединен с вторым входом блока 1 формирования знака произведения, выход переноса сумматора 15 младшего разряда соединен с входом переноса сумматора 15 старшего разряда, выход переноса которого соединен с первым входом элемента И 17, второй выход которого соединен с выходом суммы сумматора 15 младшего разряда, а выход является выходом блока Т формирования знака произведения. Устройство работает следующим образом. Разряды сомножителей в дополнительном коде поступают на шины k и S, а их знаковые разряды - соответственг но на шины 9 и 7.- Сигналы с шин k и 5 поступают на первые и вторые входы соответствующих вычислительных блоков 1, в результате чего на числовых выходах устройства формируется предварительный результат умножения. Одновременно разряды сомножителей и их знаков поступают на элементы И-НЕ 6 и 8 и далее на входы сумматора 10 поправок и на соответствующие M-N входов частичного результата вычислительных блоков 1. С выхода сумматора 10 поправок сигнал поступает на сумматор 12, где складывается с переносами из матрицы 3 умножения, и поступает на N старших входов частичного результата матрицы 3 умножения. При этом на выходе матрицы 3 умножения с учетом единичных сигналов, поступающих от шины 11 установки единицы на входы переносов в младшие разряды сумматора 10 поправок и последней линейки 2, формируется сигнал окончательного результата умножения, а при подаче сигнала от шины 1 3 округления формируется сигнал округленного результата умножения. Одноременно сигналы переносов из суммаоров 10 и 12 и матрицы 3 умножения оступают на блок 1Ц формирования нака произведения, где перенос суматора 10 поправок складывается в ладшем разряде сумматора 15 с инвериями переносов сумматора 12 переносов и матрицы 3 умножения и далее в таршем разряде сумматора 15 с инверсиями знаков сомножителей, а перенос из старшего разряда сумматора 15 и сигнал выхода его младшего разряда поступают на элемент И 17 на выходе которого формируется знаковый сигнал произведения. Действительно, при умножении поло жительных сомножителей, когда знаковые сигналы равны нулю, на выходах элементов И-НЕ 6 и 8 формируются еди ничные сигналы во всех разрядах, которые при сложении в устройстве с учетом сигнала от шины 11 установк единицы формируют нулевую поправку, вводимую в матрицу 3 умножения, и дв сигнала переноса, один из которых формируется на выходе сумматора 10 поправок, а второй - на одном из .дву выходов переносов: сумматора 12 пере носов или матрицы 3 умножения. При сложении их в сумматоре 15 формирует ся двоичный код 110, а на выходе элемента И 17 - нулевой сигнал, соответствующий положительному результату умножения. В случае, если один из сомножителей положительный, а другой отрицательный, на выходах элементов И-НЕ 6 и 8 формируются инверсный сигнал положительного сомножителя и единичные сигналыво всех разрядах на выходах элементов И-НЕ 6 и 8, подключенных к шине отрицательного сомножителя. При сложении их с сигналом от шины 11 установки единицы формируется поправ ка к предварительному результату умножения, представляющая собой дополнительный код положительного сомножителя, умноженного на коэффициент (-1), и перенос из сумматора 10 поправок. При сложении предварительног результата умножения с такой поправ кой формируется окончательный резуль тат уьчножения, а на выходе сумматора 15 формируется код 101, который приводит к появлению на выходе элемента И 17 единичного сигнала, соответствующего отрицательному результа ту умножения. В случае, когда оба сомножителя отрицательные, поправка, поступающая с выхода сумматора 10 поправок и . младших разрядов элементов И-НЕ 6, с учетом сигнала от шины 11 установки единицы представляет собой дополнительный код суммы сомножителей, ум ноженной на коэффициент (-1). При этом сигнал на выходе сумматора 15 не может превысить кода 011, что приводит к формированию на выходе элемента И 17 нулевого сигнала, соответствующего положительному результату умножения. Таким образом, предлагаемое устройство позволяет умножать сомножители произвольного знака с использованием матричного принципа умножения непосредственно в дополнительных кодах без существенных затрат времени и оборудования на преобразование кодов сомножителей. Эффективность предлагаемого технического решения особенно высока при использовании в специализированных цифровых комплексах, где вследствие высоких требований к скорости вычислений недопустимо тратить дополнительное время на преобразование кодов сомножителей. Формула изобретения Матричное множительное устройство, содержащее вычислительные блоки, объединенные в К линеек ( N разрядность первого сомножителя; п количество подразрядов, на которые разбивается первый сомножитель; М разрядность второго сомножителя; ) каждый из которых включает в себя nxm-разрядные умножители и многоразрядный сумматор, причем п информационных входов каждого умножителя соединены соответственно с разрядными входными шинами первого сомножителя устройства, m информационных входов каждого умножителя соединены соответственно с разрядными входными шинами второго сомножителя устройства, ин(| ормационные входы умножителей являются соответствующими информационными входами вычислительных блоков, выходы умножителей каждого вычислительного блока соответственно соединены с первыми входами многоразрядного сумматора, выходы которого являются соответствующими выхода1 1 вычислительных блоков, выходы переноса многоразрядного сумматора являются выходами переноса соответствующего вычислительного блока, входы переноса многоразрядного сумматора являются входами переноса соответствующего вычислительного блока, вторые входы многоразрядного сумматора являются входами частичного результата вычислительных блоков, отличающееся тем, что, с целью расширения области применения за счет обеспечения умножения чисел с произвольным знаком в дополнительном коде, в него введены сумматор поправок, группа из N двухвходовых элементов И-НЕ, группа из М двухвходовых элементов И-НЕ,сумматор переносов и блок формирования знака произведения, причем выход блока формирования знака произведения является знаковым выходом устройства первые входы элементов И-НЕ группы из М двухвходовых элементов И-НЕ соединены с соответствующими разрядными входными шинами второго сомножителя, а вторые входы объединены и подключены к шине знака первого сомножителя устройства, первые входы элементов И-НЕ группы из N двухвходовых элементов И-НЕ соединены с соответствующими разрядными входными шинами первого сомножителя, а вторые входы объединены и подключены к шине знака второго сомножителя, входы первой группы сумматора поправок соединены соответственно с выходами М элементов И-НЕ группы из М двухвходовых элементов И-НЕ, входы второй группы сумматора поправок соединены соответственно с выходами М элементов И-НЕ. группы из N двухвходовых элементов И-НЕ, выходы суммы сумматора поправок соответственно соединены с входами сумматора переносов, выход переноса из старшего разряда которого соединен с первым входом блока формирования знака произведения, второй вход которого соединен с выходом переноса из стар шего разряда сумматора поправок, а третий вход - с выходом переноса старшего вычислительного блока последней линейки, выходы переноса стар ших вычислительных блоков остальных линеек объединены и подключены к входу переноса сумматора переносов,выход переноса младшего вычислительного блока каждой линейки соединен с входом переноса старшего вычислитель него блока этой же линейки, входы переноса сумматора поправок и младшего вычислительного блока последней линейки объединены и подключены к шине установки единицы устройства, вход переноса и входы частичного ре зультата младшего вычислительного блока объединены и подключены к шине округления устройства, выходы M-N элементов M-fiE группы из N двухвходовых элементов И-НЕ соответственно соединены с младшими входами частичного результата старшего вычислительного блока первой линейки, N. старших ВХОДОВ частичного результата старших вычислительных блоков каждой линейки соединены с соответствующими выходами сумматора переносов, половина младших входов частичного результата младших вычислительных блоков каждой последующей линейки соответственно соединены с половиной старших выходов младших вычислительных блоков предыдущей линейки, половина младших выходов старших вычислительных блоков каждой предыдущей линейки соответственно соединены с половиной старших входов частичного результата младших вычислительных блоков каждой последующей линейки, половина старших выходов старшего вычислительного блока каждой предыдущей линейки соответственно соединены с половиной младших входов частичного результата старшего вычислительного блока каждой последующей линейки, выходы вычислительных блоков последней линейки являются выходами устройства, четвертый вход блока формирования знака произведения соединен с шиной знака первого сомножителя, пятый вход блока формирования знака произведения соединен с шиной знака второго сомножителя. 2. Устройство по п.1, о т л и чающееся тем, что блок формирования знака произведения содержит четыре элемента НЕ, двухразрядный сумматор, элемент И, причем входы первого, второго, третьего и четвертого элементов НЕ соответственно соединены с третьим, первым,четвертым и пятым входами блока формирования знака произведения, выходы элементов НЕ соединены соответственно с информационными входами двухразрядного сумматора, вход переноса младшего разряда которого соединен с вторым входом блока формирования знака произведения, выход переноса сумматора младшего разряда соединен с входом переноса сумматора старшего разряда, выход переноса которого соединен с первым входом элемента И, второй выход которого соединен с выходом суммы сумматора младшего разряда, а выход является выходом блока формирования знака произведения. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР N 169881, кл. G Об F 7/39, 1961. 2,Авторское свидетельство СССР №б0055,кл. G 06 F 7/52,1975(прототип).

9 7

v

Bbfroff

J о

0Vf. /

Авторы

Даты

1982-07-07—Публикация

1980-04-14—Подача