(54) МИКРОПРОГРАММНЫЙ ПРОЦЕССОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор с совмещением операций | 1982 |

|

SU1138805A1 |

| Устройство для формирования адресов процессора быстрого преобразования фурье | 1987 |

|

SU1499373A1 |

| Микропроцессорное вычислительное устройство | 1982 |

|

SU1269145A1 |

| Вычислительное устройство с совмещением операций | 1989 |

|

SU1716528A1 |

| Микропрограммируемый векторный процессор | 1987 |

|

SU1594557A1 |

| Процессор с микропрограммным управлением | 1975 |

|

SU525956A1 |

| Устройство для распределения подканалов | 1981 |

|

SU1003065A1 |

| Процессор | 1984 |

|

SU1247884A1 |

| Устройство для предварительной обработки операндов переменной длины | 1984 |

|

SU1269147A1 |

| Устройство для формирования адресов процессора быстрого преобразования Фурье | 1989 |

|

SU1691853A1 |

1

Изобретение относится к.вычислительной технике и может быть использовано в цифровой вычислительной машине.

Известен микропрограммный процессор, содержащий арифметические блоки с регистрами операндов и результата, память микропрограмм с регистрами адреса и микрокоманды и дешифратором микроопераций, регистр состояния Ш. Недостатком известного процессора является невозможность обработки информационных слов произвольной (но в пределах разрядности арифметики) длины за один рабочий такт процессора . Обработка таких слов в известном процессоре выполняется в течение нескольких рабочих тактов, малыми порциями за такт побайтно, потетрадно или побитно (команды типа память-память, в ЕС ЭВМ, некоторые ситуации арифметики с плавающей точкой, команды с маскированием операций в отдельных байтах, адресная арифметика, процедуры обработки прерываний и т.д.), что приводит к снижению быстродействия известного процессора.

Наиболее близким к предлагаемому является микропрограммный процессор.

содержащий N идентичных арифметических блоков, регистры результата первого и второго операндов, узел маскирования, память микропрограмм с регистрами адреса и микрокоманды, дешифратор микроопераций и регистр состояния Г2 .

В известном процессоре для цели обработки информации нефиксированной

10 длины использован принцип маскирования: конкретная величина обрабатываемого информационного слова задается специальными масками, которые управляют работой узла маскирова15ния на выходе арифметических блоков. Кроме того, что узел маскирования сам по себе вносит дополнительное увеличение времени срабатывания арифметики (как дополнительная сту20пень) , известный процессор имеет низкие функциональные возможности, непозволяющие выполнять ряд часто используемых операций по обработке данных и адресов за один рабочий такт. Например, операция базирования адреса (сложение 24-разрядной базы адреса с 12-разрядным смещением) требует двух рабочих тактов - выделение смещения из 32-разрядного слова 30 или 16-разрядного полуслова путем

маскирования (первый такт) и сложение базы со смещением (второй такт). По указанным причинам быстродействие известного процессора является Е1изким.,

Цель изобретения - повьпление быстродействия процессора.

Поставленная цель достигаетсй тем, что в микропрограммный процессор, содержащий группу из N арифметических блоков, регистр результата, регистры первого и второго операндов память микропрограмм, регистр адреса, регистр состояния, регистр микрокоманды, дешифратор микроопераций, причем выходы арифметических блоков соединены о соответствующими входами регистра результата, выходы которого соединены с соответствующими входами регистров первого и второго операндов, выходы регистра первого операнда соединены с первыми информационными входами соответствующих арифметических блоков, вторые информационные входы которых соединены с соответствующими выходами регистра второго операнда, выход памяти микропрограмм подключен ко входам регистра микрокоманд, адресный выход которого соединен со входом регистра адреса, выход которого подключен ко входу памяти микропрограмм, управляющий выход регистра микрокоманд соединен со входом дешифратора микроопераций, первый выход которого подключен ко входу регистра состояний, введены шифратор, формирователь кодов и группа из N селекторов, причем выход каждого селектора подключен к управляющему входу соответствующего арифметического блока, выход регистра состояния соединен с первым входом формирователя кодов и первым входом дешифратора, выходы которого соединены с управляющими входами соответствующих селекторов, первые информационные входы которых подключены к выходу операций регистра микрокоманд, а вторые информационные входы - к соответствующим входам формирователя кодов, второй вход которого соединен со вторым выходом дешифратора и вторым входом шифратора.

Причем, формирователь кодов содержит два элемента И, три элемента ИЛИ, элемент НЕ, генератор логического Ауля и три мультиплексора, причем первый вход формирователя кодов соединен со вторыми входами элементов И, второй вход формирователя кодов соединен с первыми входами элементов И, с четырьмя входами первого элемента ИЛИ, с тремя входами второго элемента ИЛИ, третьим и четвертым входг1ми третьего элемента ИЛИ, первый и второй входы которого соединены с выходами первого и второго элементов И соответственно, выходы

элементов ИЛИ соединены с управляющими входами трех мультиплексоров, выходы которых соединены с выходами формирователя кодов, выход генератора логического нуля соединен с информационными входами мультиплексоров и входом элемента НЕ, выход которого соединен с информационными входами

мультиплексоров.

Введение дополнительных узлов позволяет в предлагаемом процессоре выполнять одновременно различные опе,рации над различными группами разрядов входной информации арифметических блоков, тогда как в известном процессоре может выполняться только одна операция.

Возможность выполнения различных операций в разных арифметических блоках.или в разных группах арифмети ческих блоков приводит к возможности совмещения в одном рабочем такте предлагаемого процессора совокупност разных действий, которые выполняются в известном процессоре за несколько рабочих тактов. Кроме этого, в предлагаемом процессоре увеличено быстродействие цепочки регистры первого и второго операндов - арифметические блоки - регистр результата за счет устранения задержки,вводимой в известном процессоре узлом маскирова-. НИН.

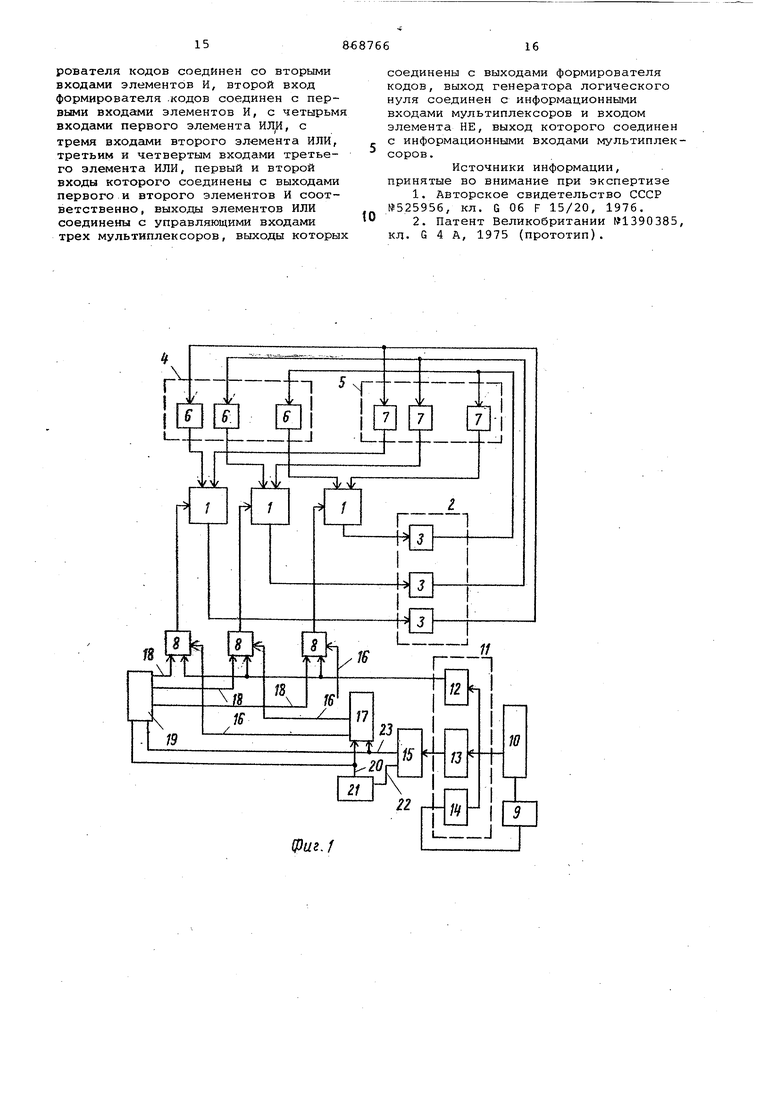

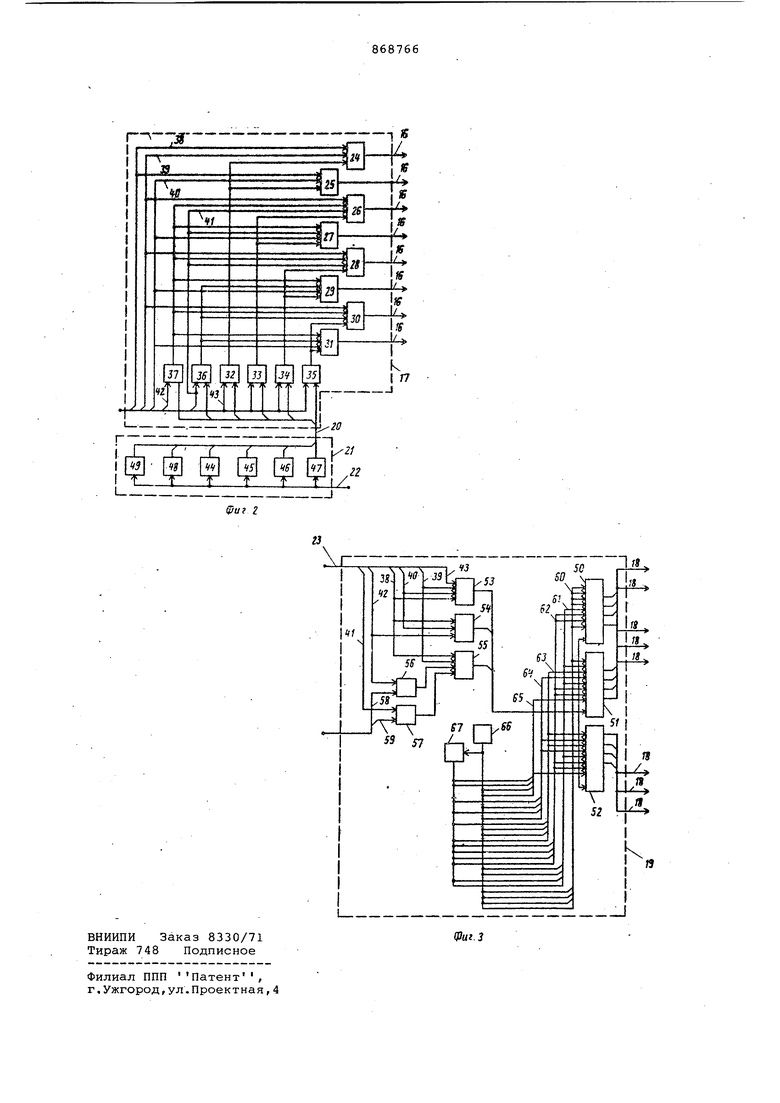

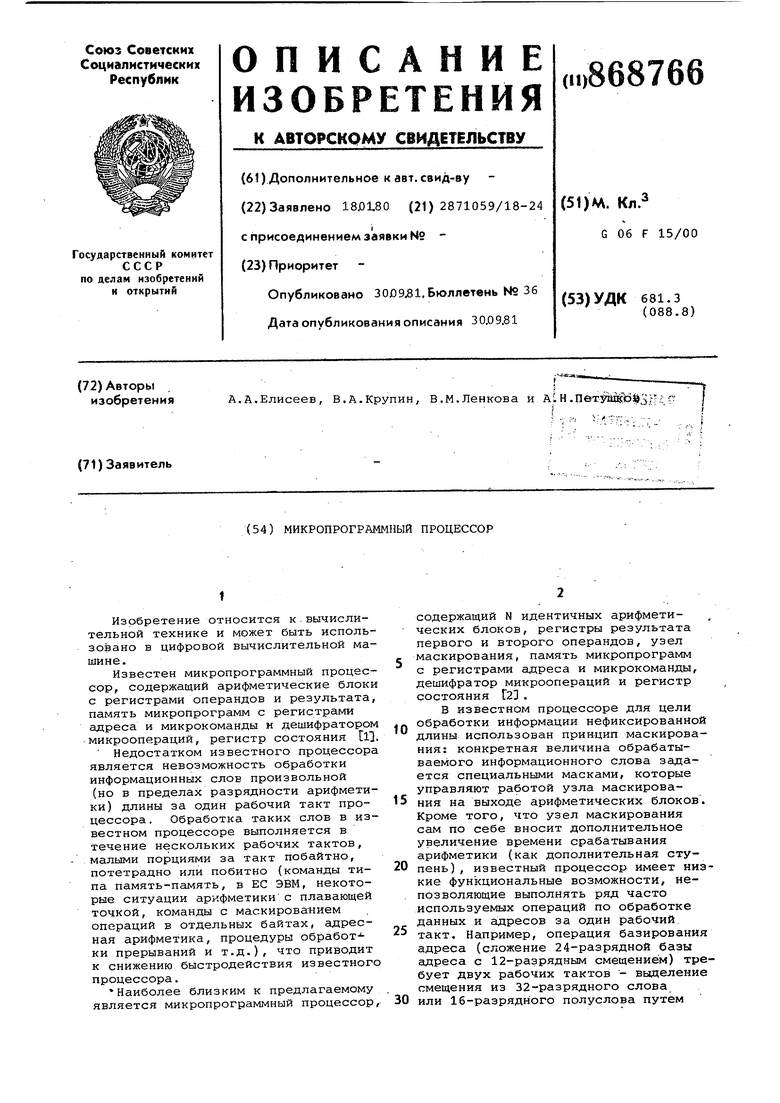

На фиг. 1 изображена блок-схема микропрограммного процессора; на фиг. 2 - схема шифратора и регистра состояний; на фиг. 3 - схема формирователя кодов.

Микропрограммный процессор содержит арифметические блоки 1, регистр 2 результата, разрядные группы 3 регистра 2 результата, регистры 4 и 5 первого и второго операндов, разрядные группы б регистра 4 первого операнда, разрядные группы 7 регистра 5 вторЬго операнда, селекторы 8, регистр 9 адреса, память 10 микропрограмм, регистр 11 микрокоманды, операционная группа 12 разрядов .регистра 11 микрокоманды, управляющая группа 13 разрядов регистра 11 микрокоманды, адресная группа 14 разрядов регистра 11 микрокоманды, дешифратор 15 микроопераций, выходы 16 шифратора 17, выходы 18 формирователя 19 кодов, выход 20 регистра 21 состояний, первый выход 22 дешифратора 15 микроопераций, второй выход 23 дешифратора 15 микроопераций, элементы ИЛИ 24-31, элементы И 32-37 линии 38-43 микроопераций НОРМАЛИЗАЦИЯ, ПЕРЕСЫЛКА ЗОН, ПЕРЕСЫЛКА ЦИФР, БАЗИРОВАНИЕ, ИНДЕКСИРОВАНИЕ и ОПЕРА ЦИЯ ПО МАСКЕ соответственно, триггеры 44-47 масок соответственно нулевого, первого, второго и третьего байтов и триггеры 48 и 49 соответственно нулевой базы и нулевого индексов, мультиплексоры 50-52, элементы ИЛИ 53-55, элементы И 56 и 57 линии 58 и 59 состояния соответственно ИНДЕКС НУЛЕВОЙ И БАЗА НУЛЕВАЯ шины 60-65 -кодов 0000, ООН, 1111, 1001, 1010 и 1100, генератор 66 логического нуля, элемент НЕ 67. Выход первого, второго, ... и Nарифметических блоков 1 в регистре 2 результата соответственно соедине ны со входами первой, второй,... и N-й разрядных групп 3, выходы которых в регистрах 4 и 5 первого и вто рого операндов соответственно соеди нены со входами первых, вторых,... и N-X разрядных групп 6 и 7. К первому и второму входам арифметически блоков 1 подключены выходы соответствующих разрядных групп 6 и 7 реги стров 4 и 5 первого и второго операндов соответственно. К управляющи входам арифметических блоков 1 подключены выходы соответствующих селекторов 8. Выход регистра 9 адреса соединен со входом памяти 10 микропрограмм, выход которой в регистре 11 микроко манды соединен со входами операцион ной, управляющей и адресной группы 12, 13 и 14 разрядов. К первым инфо мационным входам селекторов 8 подключен выход операционной группы 12 разрядов ко входу дешифратора 15 микроопераций - выход управляющей группы 13 разрядов и ко входу регис ра 9 адреса - выход адресной группы 14 разрядов регистра 11 микрокоманд Первый, второй,... и N-й выходы 16 шифратора 17 соединены с управляющи ми входами первого, второго,... и N-ro селекторов 8 соответственно. Первый, второй,... и N-й выходы 18 формирователя 19 кодов соединены со вторыми информационными входами первого, второго,... и N-ro селектор 8 соответственно. Выход 20 регистра 21 состояний соединен с первыми входами шифратора 17 и формирователя 19 кодов. Первый и второй выходы 22 и 23 дешифратора 15 микроопераций со единены, соответственно со входом регистра 21 состояний и со вторыми входами шифратора 17 и формирователя 19 кодов. В шифраторе 17 выходы элементов ИЛИ 24-31 подключены к соответствующим выходам 16 шифратора 17 Выходы элементов И 32-35 соединены с первыми входами элементов ИЛИ 24 и 25, 26 и 27, 28 и 29, .30 и 31 соответственно. Выход элемента И 37 соединен со вторыми входами элементо ИЛИ 26-31, выход элемента И 36 соеди нен с третьими входами элементов ИЛИ 29-31. Второй выход 23 дешифратора 15 микроопераций состоит из шес ти сигнальных линий 38-43 микроопераций. Линия 38 микрооперации НОРМАЛИЗАЦИЯ в шифраторе 17 соединена со вторыми входами элементов ИЛИ 24 и 25, линия 39 микрооперации ПЕРЕСЫЛКА зон соединена с третьими входами элементов ИЛИ 24, 26 и 28 и с четвертым входом элемента ИЛИ 30. Линия 40микрооперации ПЕРЕСЫЛКА ЦИФР соединена с третьими входами элементов ИЛИ 25 и 27 и с четвертыми входами элементов ИЛИ 29 и 31, линия 42 микрооперации ИНДЕКСИРОВАНИЕ соединена с первым входом элемента И 37, линия 41микрооперации БАЗИРОВАНИЕ соединена с первым входом элемента И 36 и с четвертыми входами элементов ИЛИ 26-28, линия 43 микрооперации ОПЕРАЦИЯ ПО МАСКЕ соединена с первыми входами элементов И 32-35. Регистр 21 состояний содержит триггеры 44-47 масок соответственно нулевого, первого, второго и третьего байтов, а также триггеры 48 и 29 нулевой базы и нулевого индекса соответствен-г но,.с входами триггеров 44-49 в регистре 21 состояний соединен первый выход 22 дешифратора-15 микроопераций, выходы триггеров 44-49 соединены с выходом 20 регистра 21 состояний и в шифраторе 17 соответственно соединены со вторыми входами элементов И 32-37. В формирователе 19 кодов кодовый- выход мультиплексора 50 соединен с первым и вторым, мультиплексора 51 - с третьим, четвертым и пятым мультиплексора 52 - с шестым, седьмым и восьмым выходами 18 формирователя 19 кодов. Выходы элементов И ИЛИ 53-5Ь соединены с управляющими входами мультиплексоров 50-52. Первый, второй, третий и четвертый входы элемента ИЛИ 53 соединены с линиями 38, 39, 40 и 43 микроопераций НОРМАЛИЗАЦИЯ, ПЕРЕСЫЛКА ЗОН, ПЕРЕСЫЛКА ЦИФР и ОПЕРАЦИЯ ПО МАСКЕ соответственно. Первый, второй и третий входы элемента ИЛИ 54 соединены с ли:ниями 38, 40 и 42 микроопераций НОР МАЛИЗАЦИЯ, ПЕРЕСЫЛКА ЦИФР И ИНДЕКСИРОВАНИЕ соответственно. Перйый и второй входы элемента ИЛИ 55 соединены с выходами элементов И 56 и 57 соответственно, третий и четвертый входы - с линиями 38 и 39 микроопераций НОРМАЛИЗАЦИЯ и ПЕРЕСЫЛКА- ЗОН соответственно. С первыми входами элементов И 56 и 57 соединены соответственно линии 42 и 41 микроопераций ИНДЕКСИРОВАНИЕ И БАЗИРОВАНИЕ. ВЫХОД 20 регистра 21 состояний в формирователе 19 кодов соединен со вторыми входами элементов И 56 и- 57 линиями 58 и 59 состояний ИНДЕКС НУЛЕВОЙ и БАЗА НУЛЕВАЯ соответственно. Первый четвертый и восьмой кодовые вводы мультиплексора 50 и первый кодовый вход мультиплексора 51 соединены с шиной 60 кода 0000. Второй кодовый вход мультиплексора 51 и пятые кодовые в-ходы мультиплексоров 50-52 соединены с шиной 61 кода ООН. Шестой и седьмой кодовые входы мультиплексоров 50-52 .соединены с шиной

62 кода 1111. Первый кодовый вход мультиплексора 52 и третьи кодовые входы мультиплексоров 51 и 52 соединены с шиной 63 кода 1001. Второй кодовый вход мультиплексора 52 и четвертые кодовые входы мультиплексоров 51 и 52 соединены с шиной 64 кода 1010, Восьмые кодовые входы мультиплексоров 51 и 52 соединены с шиной 65 кода 1100. Каждая из шин 60-65 включает четыре разрядных линии. С выходом генератора 66 логического нуля соединены все разрядные линии шины 60 кода 0000, первая и вторая разрядные линии шины 61 кода ООН, вторая и третья разряднылинии шины 63 кода 1001, вторая и четвертая разрядные линии шины 64 кода 1010, третья и четвертая разряные линии шины 65 .кода 1100 и вход элемента НЕ 67, с выходом которого соединены третья и четвёртаяг разрядные линии шины 61 кода ООН, все разрядные линии шины 62 кода 1111, первая и четвертая разрядные линии шины 63 кода 1001, первая и третья разрядные линии шины 64 кода 1010, первая и вторая разрядные линии шины 65 кода 1100.

В описываемом варианте процессор .содержит восемь четырехразрядных арифметических блоков 1, каждый из регистров 2, 4 и 5 результата, первого и второго операндов включает по восемь четырехразрядных групп 3, 6 и 7, а шифратор 17 и формировател 19 кодов имеют по восемь выходов 16 и 18.

Процессор работает следующим образом.

В каждом рабочем такте из памяти 10 микропрограмм в регистр 11 микрокоманды по адресу, сформированному в регистре 8 адреса, считывается микрокоманда, управляющая выполнением совокупности действий данного рабочего такта. Адрес очередной микрокоманды в микропрограммной последовательности определяется адресной группой 14 {разрядов регистра 11 микрокоманды.По содержимому управляю.щей группы 13 разрядов дешифратор 15 микроопераций вырабатывает набор управляющих сигналов данного рабочего такта. Операционная группа 12 разрядов определяет операцию, выполняег 1ую в данном рабочем такте арифметическими блоками 1. При этом на вхорда арифметических блоков 1 подаютсвн ..первый и второй операнды из регистров 4 и 5 первого и второго операндов, а результат операции с выходов арифметических блоков 1 заносится в регистр 2 результата. При обработке данных фиксированной длины .исходные 32-разрядные операнды занимают полный объем регистров 4 и 5 первого и второго операндов так что каждая разрядная группа 6 и 7

этих регистров содержит четыре разряда (тетраду) исходных данных, а в регистр 2 результата заносится 32разрядный результат обработки так, что в каждую разрядную группу 3 помещается тетрада -результата. На все выходах 16 шифратора 17 вырабатывается сигнал, по которому через селеторы 8 на управляющие входы всех арифметических блоков 1 передается содержимое операционной группы 12 разрядов регистра 11 микроманды. При обработке операндов фиксированной длины все арифметические блоки

Iвыполняют одну и ту же операцию, заданную операционной группой 12 разрядов. Процессор выполняет такую обработку в том случае, если управляющая группа 13 разрядов регистра

IIмикрокоманды не задает ни один из режимов специальной обработки. В описываемом варианте процессора режимы специальной обработки могут быть заданы однЪй из следующих микроопераций: БАЗИРОВАНИЕ, ИНДЕКСИРОВАНИЕ, ПЕРЕСЫЛКА ЗОН, ПЕРЕСЫЛКА ЦИФ

(НОРМАЛИЗАЦИЯ, ОПЕРАЦИЯ ПО МАСКЕ.

Если управляющая группа 13 разрядов регистра 11 микрокоманды указывает одну из перечисленных микроопераций, на втором выходе 23 дешифратра 15 микроопераций возбуждается соответствующая линия 38-43 микрооперации, по которой шифратор 17 и формирователь 18 кодов настраивается на выполнение специальной операции. На выходах 16 шифратора 17 вырабатывается набор сигн.алов, управляющих работой селекторов 8. Если на управляющий вход какого-либо селекчгора 8 с, соответствующего выхода 16 шифратра 17 подан уровень логического нуля, на управляющий вход соответствующего арифметического блока 1 передается код с выхода операционной группы 12 разрядов регистра 11 микркоманды. При логической единице на управляющем входе селектора 8 на управляющий вход соответствующего арифметического блока 1 передается код с соответствующего выхода 18 формирователя 19 кодов, в зависимости от выполняемой специальной операции на выходах 16 шифратора 17 формируется та или иная совокупность

-управляющих сигналов, а на выходах 18 формирователя 19 кодов - совокупность кодов, каждый из которых в данном рабочем такте может быть использован для управления соответствующим арифметическим блоком 1. Список функций, выполняемых любым арифметическим блоком 1, соответствующие этим функциям управляющие коды и применяемые в тексте обозначения функций следующие:

код 0000, сложение в данном арифметическом блоке 1 содержимого соответствующей разрядной группы 6 регистра 4 первого операнда с перен сом из предыдущего арифметического блока 1, обозначение функции - ПЕРЕДАЧА А; код 0011, на выходе данного ариф метического блока 1- формируется нулевая информация, обозначение - выработка нулей; код 1001, сложение и данном ариф метическом блоке 1 содержимого соот ветствующих разрядных групп 6 и 7 регистров 4 и 5 первого и второго операндов, обозначение - СЛОЖЕНИЕ; код 1010, пересылка через данный арифметический блок 1 содержимого соответствующей разрядной группы 7 регистра 5 второго операнда, обозна чение - ПЕРЕДАЧА В; код 1100, сложение в данном ариф метическом блоке удвоенного содержи мого соответствующей разрядной груп пы 6 регистра 4 первого операнда С переносом из предыдущего арифметиче кого блока- 1, обозначение - СДВИГ ВЛЕВО; код 1111, вычитание в данном ари метическом блоке 1 единицы из содер жимого соответствующей разрядной группы 6 регистра 4 первого операнд обозначение - А МИНУС 1. Для любой из перечисленных функц результат обработки с выхода данног арифметического блока 1 заносится в соответствующую разрядную группу 3 регистра 2 результата. Адресная арифметика. Процесс вычисления адресов в ЕС ЭВМ сводится, в основном, к двум операциям: БАЗИРОВАНИЕ И ИНДЕКСИРОВАНИЕ . В предлагаемом микропрограммном процессоре каждая из указанных операций выполняется за.один рабочи такт. При базировании в шесть младших разрядных групп 6 регистра 4 первого операнда помещается 24-разрядная база адреса (две старших раз рядные группы 6 содержат произвольную информацию) и в три младших разрядных группы 7 регистра.5 второго операнда помещается 12-разрядное сме щение, информация в старших разряд.ных группах 7 также произвольна. Микрокоманда, управляющая рабочим тактом базирования, содержит в опера ционной группе 12 разрядов регистра 11 микрокоманды код функции СЛОЖЕНИЕ, а в управляющей группе 13 разрядов - код микрооперации ВАЗИРОВАНИЕ, в результате чего на втором выходе 23 дешифратора 15 микроопераций возбуждается линия 41 микрооперации БАЗИРОВАНИЕ. Если в регистре 21 состояний триггер 48 нулевой базы-установлен в нуль (это говорит о необходимости полноразрядного базирования), в шифраторе 17 на элементе И 36 отсутствуют совпадения и по. возбужденной линии 41 микрооперации БАЗИРОВАНИЕ срабатывают элементы ИЛИ 26-28, что вызывает появление сигналов на соответствующих выходах 16 шифратора 17. .В результате возбуждаются только третий-пятый выходы 16 шифратора 17, и первый, второй, шестой, седьмой и восьмой выходы 16 остаются невозбужденными. В формирователе 19 кодов не срабатывает ни один из элементов ИЛИ 53-55, так как возбуждена только линия 41 микрооперации БАЗИРОВАНИЕ, а элемент И 57 заперт запрещающим потенциалом на линии 59 состояния БАЗА НУЛЕВАЯ. На управляющие входы мультиплексоров 50-52 подается нулевой код, в результате чего через мультиплексоры 50-52 передается код, соответствующий коммутации их первых кодовых входов. В частности, через мультиплексор 51 на третий-пятый выходы 18 формирователя 19 кодов выдается код 0000, соответствующий функции ПЕРЕДАЧА А. . На управляющие входы первого, второго, шестого, седьмого и восьмого арифметических блоков 1 (фиг.1) через соответствующие селекторы 8 поступает ко.д функции СЛОЖЕНИЕ из операционной группы 12 разрядов, а на управляющие входы третьего-пятого арифметических блоков 1 - код функции ПЕРЕДАЧА А из формирователя 19 КОДОВ. Таким образом, в шестом-восьмом арифметических блоках .1 выполняется сложение 12-разрядного смещения с младшими двенадцатью разрядгхми базы, а в третьем-пятом арифметических блоках 1 выполняется распространение переноса на стадии 12-ти разрядов базы. Функция первого и второго арифметических блоков 1 в данной операции безразлична, так как результирующий адрес состоит только из 24-х разрядов. .После завершения выполнения операции базирования адрес с выходов треть§го-восьмого арифметических блоков 1 заносится в третью-восьмую соответственно разрядные группы 3 регистра 2 результата. Если в регистре 21 состояний триггер 48 нулевой базы установлен в единицу (необходимость в базировании отсутствует) в шифраторе 17 по возбужденной линии 41 микроопе- рации БАЗИРОВАНИЕ срабатывает элемент И 36 и в результате возбуждаются элементы ИЛИ 26-31, что вызывает появление сигналов на втором-восьмом выходах 16 шифратора 17 Первый и второй выходы 16 остаются невозбужденными. В формирователе 19 кодов разрешающий потенциал на линии 59 состояния БАЗА НУЛЕВАЯ приводит к срабатыванию элемента И 57 и, далее, элемента ИЛИ 55. На управляющие входы мультиплексоров 50-52 подается код 001, в результате чего через эти мультиплексорьа передается код, соответствующий коммутации их вторых кодовых входов, в частности, через мультиплексор 51 на третий-пятый выходы 18 формирователя 19 кодов вьщается код ООН, соответствующий функции ВЫРАБОТКА НУЛЕЙ, а через мультиплексор 52 на шестой-восьмой выходы 18 - код 1010, соответствующий функции ПЕРЕДАЧА В. На управляю щие входы первого и второго арифметических блоков 1 с выхода операционной группы 12 разрядов регистра 11 микрокоманды подается код функци СЛОЖЕНИЕ (в данном случае безразлич но, какой код подается в старшие ра ряды, так как они не участвуют в формировании адреса), на управляющи входы третьего-пятого арифметических блоков 1 - код функции ВЫРАБОТК НУЛЕЙ и на управляющие входы шестого-восьмого арифметических блоков 1 - код функции ПЕРЕДАЧА B-tr-CQOX-ветствующих выходов 18 формирователя 19 кодов.Таким образом, шестой-восьмой арифметические блоки 1 выполняют передачу без изменения 12 разрядного смещения, а третьим-пяты арифметическим блокам 1 в старших разрядах адреса формируются нули. Таким образом, операция БАЗИРОВА НИЕ выполняется в течение одного ра бочего такта, управляемого одной микрокомандой, причем совокупность .функций, выполняемая арифметическим блоками 1, определяется равенством нулю или единице триггера 48 нулево базы в регистре 21 состояний (т.е. признаком, указывающим наличие или отсутствие необходимости использовать базу при формировании адреса). При индексировании (в предположе нии, что оно выполняется после бааирования) в шесть мл-адших разрядных групп б регистра 4 первого операнда помещается 24-разрядный индек адреса, а в шесть младших разрядных групп 7 регистра 5 второго операнда 24-разрядный пробазированный адрес. Микрокоманда, управляющая рабочим тактом индексирования содержит в операционной группе 12 разрядов ре .гистра 11 микрокоманды код функции СЛОЖЕНИЕ, а в управляющей группе 13 разрядов - код микрооперации ИНДЕКСИРОВАНИЕ. На втором выходе 23 деши ратора 15 микроопераций возбуждается линия 42 микрооперации ИНДЕКСИРОВАНИЕ. Если в регистре 21 состоя НИИ триггер 49 нулевого индекса уст HOBJpeH в нуль (т.е. необходимо выполнять индексирование), в шифраторе 17 на элементе И 37 отсутствует совпадение и не срабатывает ни один из элементов ИЛИ 24-31, в результате чего все арифметические блоки 1 выполняют операцию СЛОЖЕНИЕ. Если же триггер 49 нулевого индекса установлен в единицу, в шифраторе 17 срабатывает элемент И 37 и, по его выходу, элементы ИЛИ 26-31. В формирователе 19 кодов срабатывает элемент И 56 (потенциал на линии 58 состояния ИНДЕКС НУЛЕВОЙ решает срабатывание), и на выходах элементов ИЛИ 53-55 формируется код 011, соответствующий передаче через мультиплексоры 50-52 информации на их четвертых кодовых входах, В частности, через мультиплексоры 51 и 52 на третий-восьмой выходы 18 формирователя 19 кодов выдается код 1010, соответствующий функции ПЕРЕДАЧА В. Таким образом, при необходимости выполнять индексирование в арифметических блоках 1 пробазированный адрес и индекс складываются, а при отсутствии такой необходимости пробазированный адрес передается через арифметические блоки 1 без изменения. Потетрадная перекомпоновка. Рассматривают работу процессора на примере выполнения операций с замещением старшей или младшей тетрад в каждом байте исходных операндов (команды ПЕРЕСЫЛКА ЗОН и ПЕРЕСЫЛКА ЦИФВ в ЕС ЭВМ). При выполнении пересылки зон возбуждения линии 39 микрооперации ПЕРЕСЫЛКА ЗОН, а при П ресылке цифр - линия 40 микрооперации ПЕРЕСЫЖА ЦИФР, причем в первом случае в шифраторе 17 срабатывают элементы ИЛИ 24, 26, 28 и 30 и возбуждены все нечетные выходы 16 шифратора 17, во втором случае возбуждены все четные выходы 16 шифратора 17. Микрокоманда, управляющая рабочим тактом пересылки з.он или цифр, в операционной группе 12 разрядов регистра 11 микрокоманды содержит код функции. ПЕРЕДАЧА В, а в управляющей разрядной группе 13 разрядов - код мик-рооперации ПЕРЕСЫЛКА ЗОН или ПЕРЕСЫЛКА ЦИФР. На всех выходах 18 формирователя 19 кодов вырабатывается код функции ПЕРЕДАЧА А. Таким образом, при пересылке зон нечетные (первый, третий и т.д.) арифметические блоки 1 выполняют функцию ПЕРЕДАЧА А, а все четные - функцию ПЕРЕДАЧА В. После завершения выполнения рабочего такта пересылки зон в регистре 2 результата формируется информация, каждый байт которой в старшей тетраде (нечетные разрядные группы 3) содерлсит соответствующую тетраду из регистра 4 первого операнда, а в младший тетраде (четные разряд- . ные группы 3) - соответствующую тет-: раду из регистра 5 второго операнда. Операция пересылки цифр выполняется совершенно аналогично, только в шифраторе 17 возбуждаются все четные выходы 16, функцию ПЕРЕДАЧА А выполняют четные, а ПЕРЕДАЧА В - нечетные арифметические блоки 1, в старших тетрадах байтов регистра 2 результата формируется информация из регистра 5 второго операнда, а в младших тетрадах - из регистра 4 первого операнда. Плавающая арифметики и маскирова ние,Операция нормализации в плавающе арифметике заключается в выполнении левых сдвигов мантиссы и одновремен ном вычитании единицы их характерис тики. В предлагаемом процессоре сдв мантиссы выполняется в шести младших арифметических блоках 1, а вычитание единицы их характеристики в двух старших. При этом первому и второму арифметическим блокам 1 с выхода формирователя 19 кодов задае ся выполнения функции А МИНУС 1 (са мым старшим арифметическим блоком 1 эта функция интерпретируется как вычитание только при появлении заем из предыдущей тетрады), третьемувосьмому арифметическим блокам 1 с выхода операционной группы 12 разря дов регистра 11 микрокоманды задается выполнение функции. СДВИГ ВЛЕВО Исходное исло с плавающей точки по мещается в регистр 4 первого операн да, после каждого шага нормализации нормализуемое число через регистр 2 результата вновь пересылается в регистр 4 первого операнда. Предлагаемый процессор позволяет также выполнять обычные операции ма кирования, т.е. выделение из исходной информации определенных байтов по маске. Для каждого байта данных в регистре 21 состояний предусмотре триггер маски (триггеры 44-47 масок нулевого-третьего байтов). Если обработка какого-либо байта запрещена (замаскирована) соответствующим триггером 44-47 маски, то по микрооперации ОПЕРАЦИЯ ПО МАСКЕ (возбуждена линия 43 микрооперации ОПЕРАЦИЯ ПО МАСКЕ; возбуждается соответствующая пара выходов 16 шифратора 17, и соответствующая пара арифметических блоков 1 выполняет функцию ВЫРАБОТКА НУЛЕЙ, задаваемую формиро вателем 19 кодов. Если обработка данного байта разрешена, то в соответствующей паре арифметических бло.ков 1 выполняется функция, определяемая операционной группой 12 разрядов регистра 11, микрокоманды. Учет повышения быстродействия про цессора только на адресной арифметике показывает, что предлагаемый процессор .позволяет сократить на оди рабочий такт как операцию базирования, так и операцию индексирования. Поскольку базирование и индексирование выполняются в выборке каждой команды RX формата, базирование однократно в выборке каждой команды RS, SI и дважды - SS форматов, то в программах, использующих и базирование, и индексирование, время выполнения для команды RS-и SI формато уменьшается на один рабочий такт, а для наиболее весомых команд форматов RX и SS - на два рабочих такта, например, операция сложения с фиксированной запятой (и большинство аналогичных команд) формата RX в ЭВМ ЕМ-1022 выполняется за семь-девять рабочих тактов, применение предлагаемого устгройства позволяет сократить это время на один-два такта, что означает увеличение быстродействия на таких командах примерно на 19% Формула изобретения 1. Микропрограммный процессор, содержащий группу из N арифметических блоков, регистр результата, регистры первого и второго операндов, память микропрограмм, регистр адреса, регистр состояния, регистр микрокоманды, дешифратор микроопераций , причем выходы арифметических блоков соединены с соответствующими входами регистра результата, выходы которого соединены с соответс вующими входами регистров первого и втоpoto операндов, выходы регистра первого операнда соединены с первыми информационными входами соответствующих арифметических блоков, вторые информационные входы которых соединены с соответствующими выходами регистра второго операнда,, выход памяти микропрограмм подключен ко входам регистра микрокоманд, адресный выход которого соединен со входом регистра адреса, выход которого подключен ко входу памяти микропрограмм, управляющий выход регистра микрокоманд соединен со входом дешифратора микроопераций, первый выход которого подключен к входу регистра состояний, отличающийс я тем, что, с целью повышения быстродействия, в него введены шифратор, формирователь кодов и группа из N селекторов, причем выход каждого селектора подключен к управляющему входу соответствующего арифметического блока, выход регистра состояния соединен с первым входом формирователя кодов и первым входом шифратора, выходы которого соединены с управляющими входами соответствующих.селекторов, первые информационные входы которых подключены к выходу операций регистра микрокоманд, а вторые информационные входы - к соответствующим выходам формирователя кодов, второй вход которого соединен со вторым выходом дешифратора и вторым входом шифратора. 2. Процессор по п.1, о т л и чающийся тем, что формирователь кодоб содержит два элемента И, три элемента ИЛИ, элемент НЕ, генератор логического нуля и три мультиплексора, причем первый вход формирователя кодов соединен со вторыми входами элементов И, второй вход формирователя .кодов соединен с первыми входами элементов И, с четырьмя входами первого элемента , с тремя входами второго элемента ИЛИ, третьим и четвертым входами третьего элемента ИЛИ, первый и второй входы которого соединены с выходами первого и второго элементов И соответственно , выходы элементов ИЛИ соединены с управляющими входами трех мультиплексоров, выходы которых

соединены с выходами формирователя кодов, выход генератора логического нуля соединен с информационными входами мультиплексоров и входом элемента НЕ, выход которого соединен с информационными входами мультиплексоров .

Источники информации, принятые во внимание при экспертизе

I/.

L.

-J

l.e

Авторы

Даты

1981-09-30—Публикация

1980-01-18—Подача