Изобретенйе относится к вычислительной технике и может быть использовано для быстрой векторной обработки геофизической, медицинской и визуальной информации дпя АРМ и САПР, дпя управления сложными технологическими объектами и научным экспериментом.

Цель изобретения - повьшение производительности.

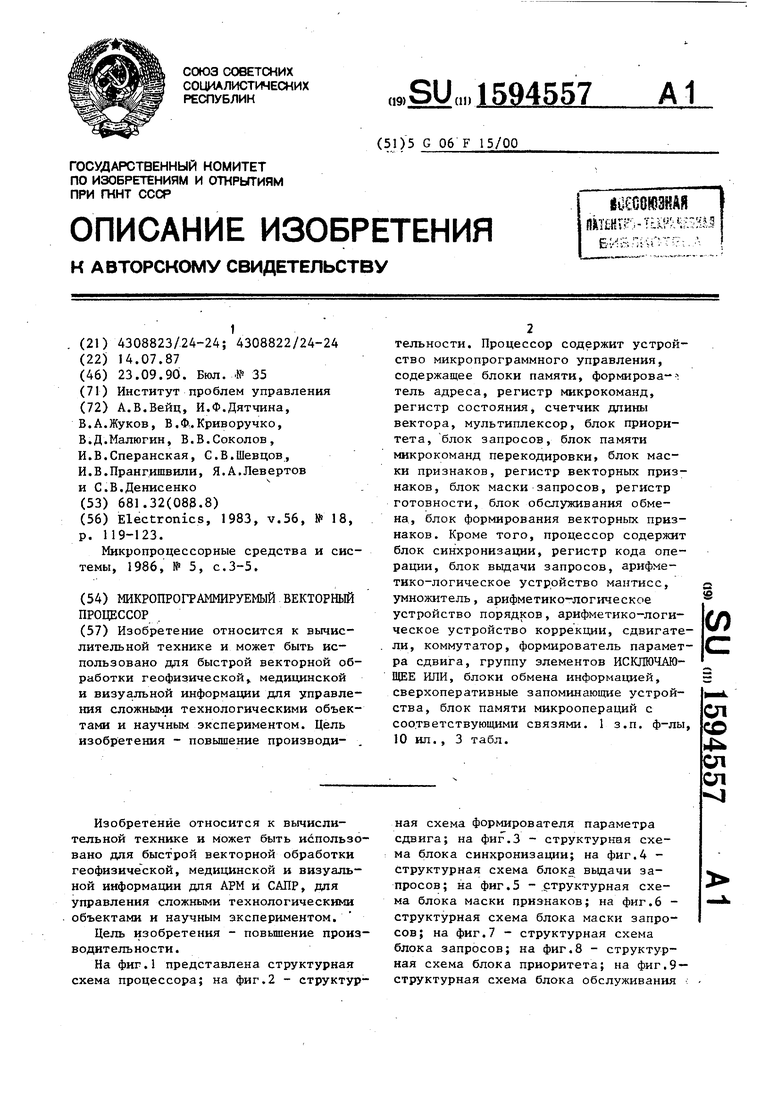

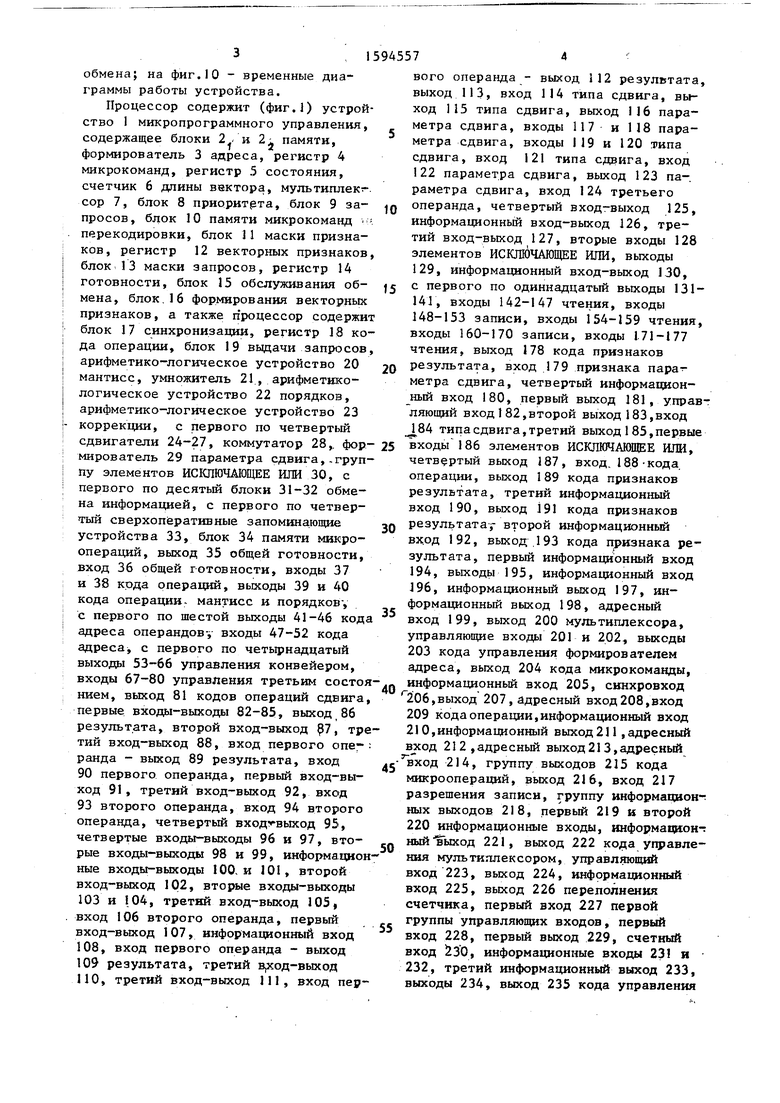

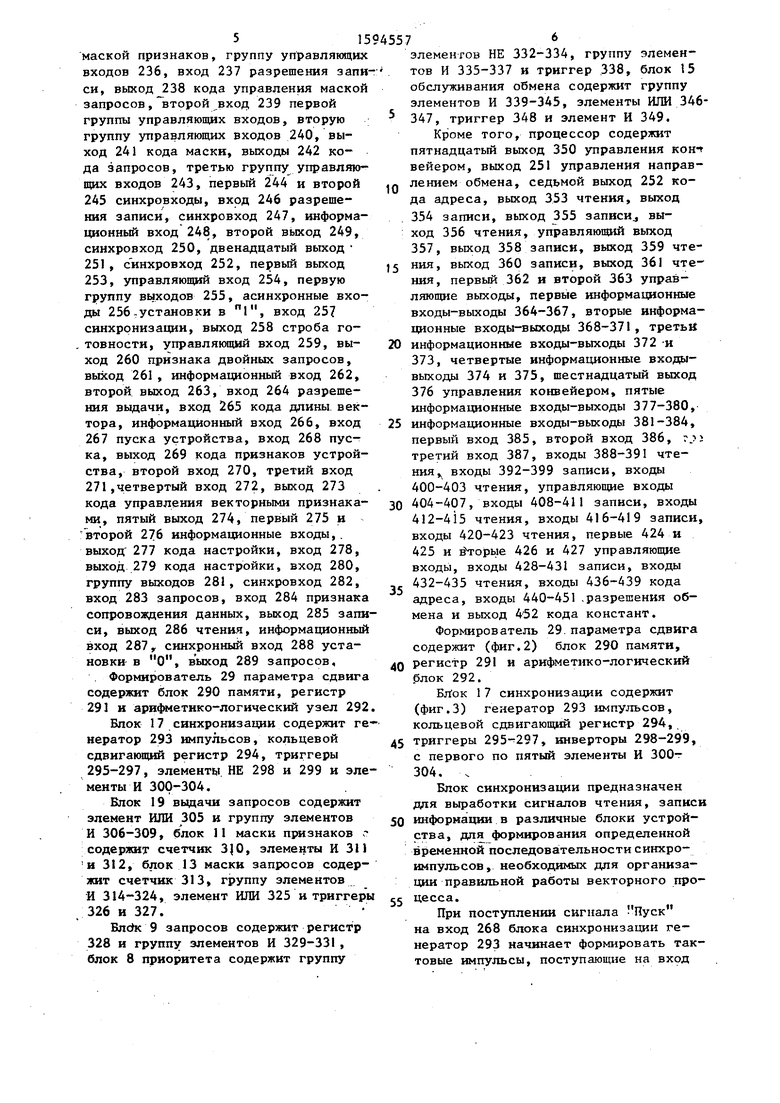

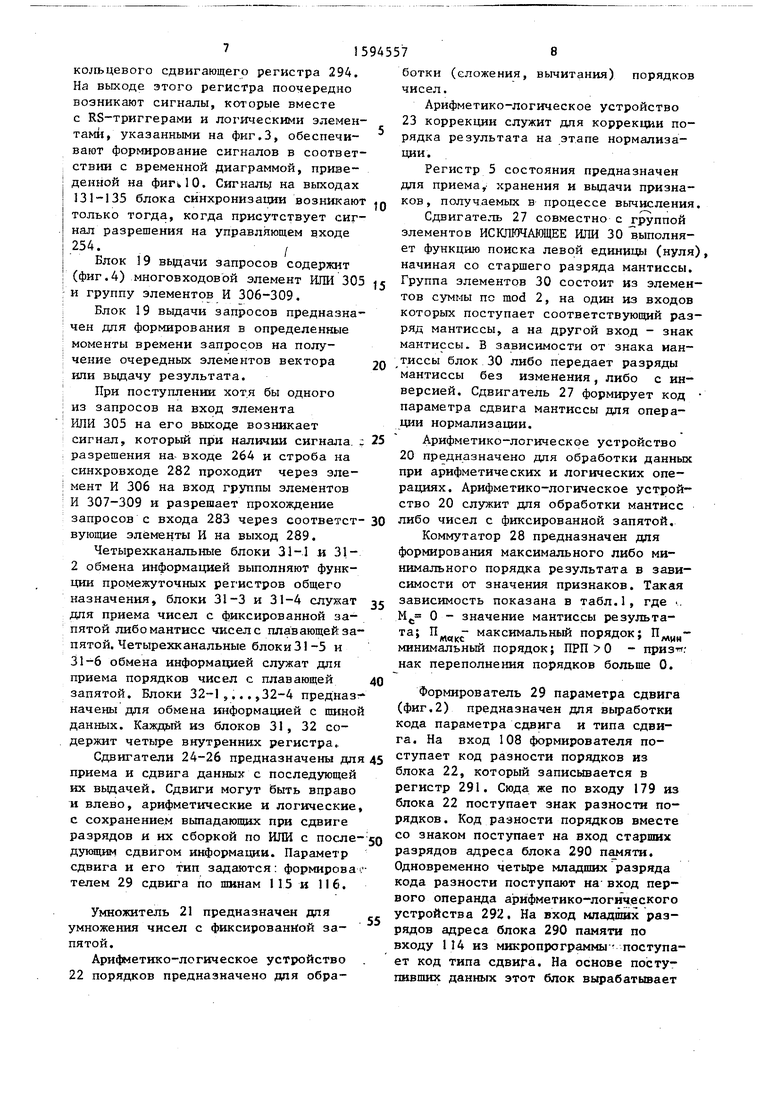

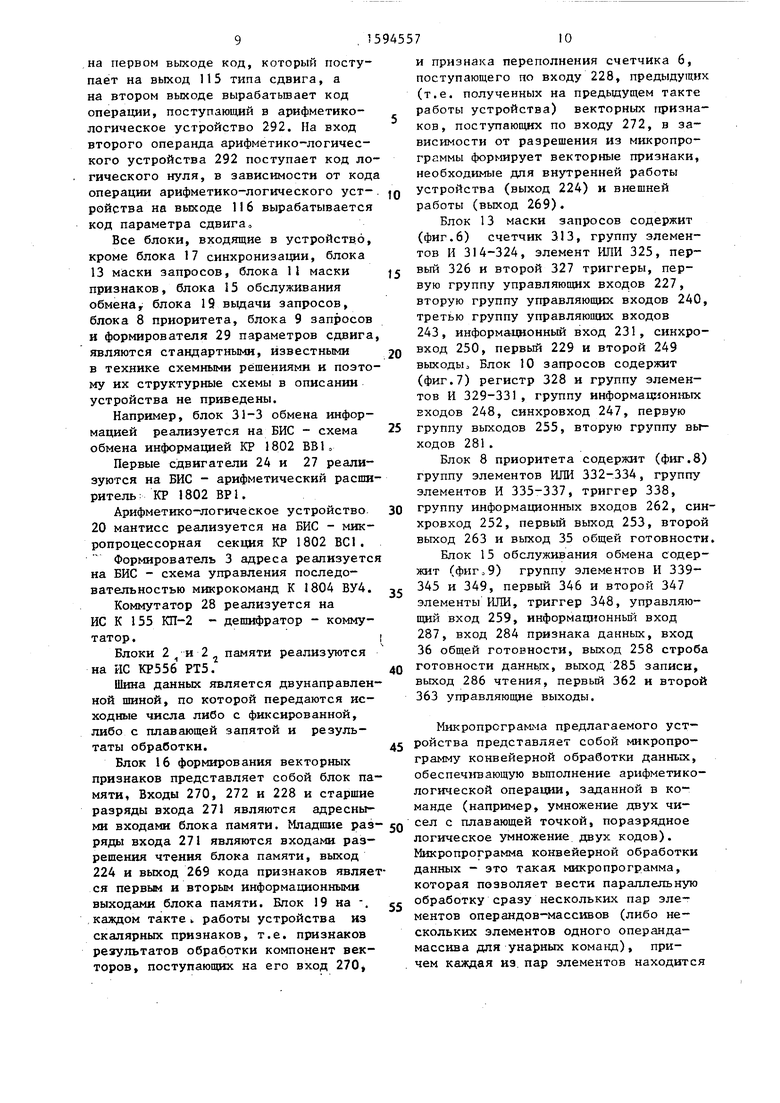

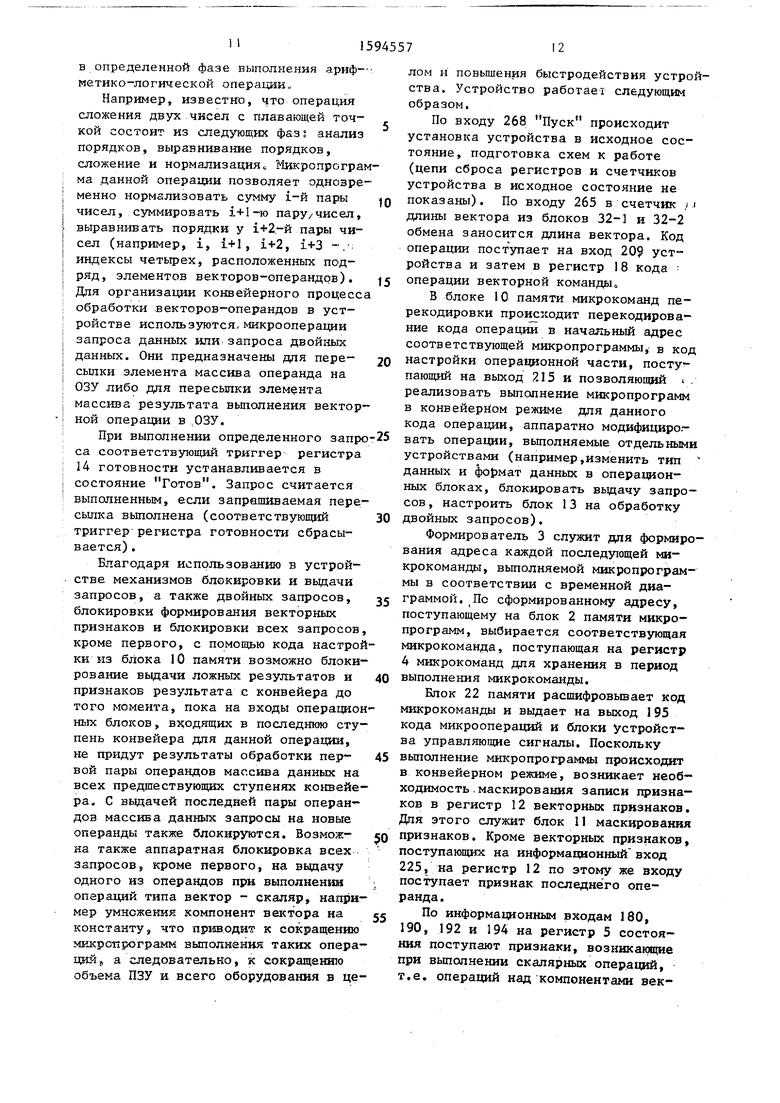

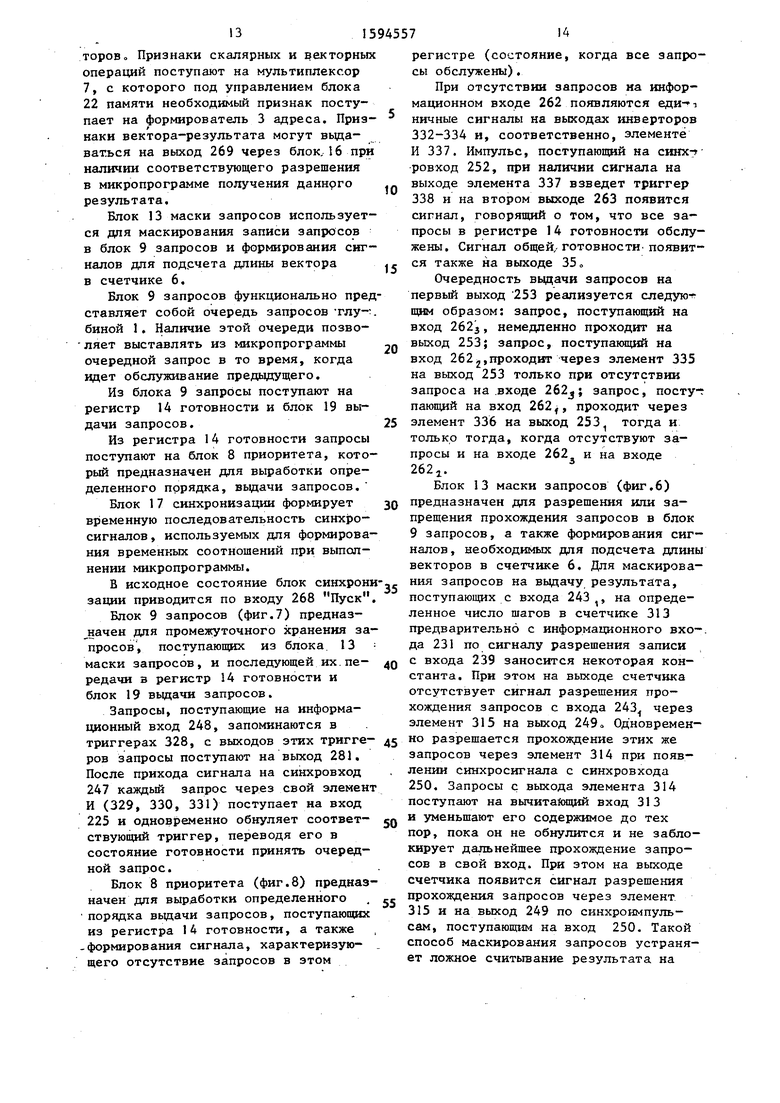

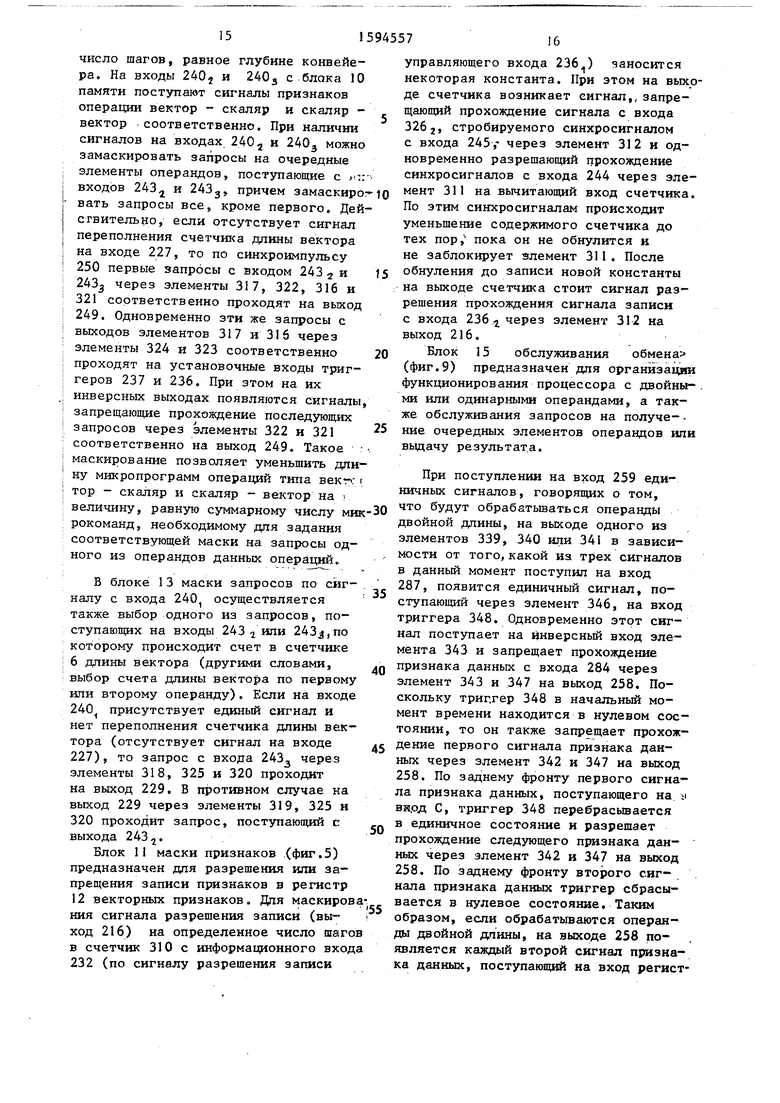

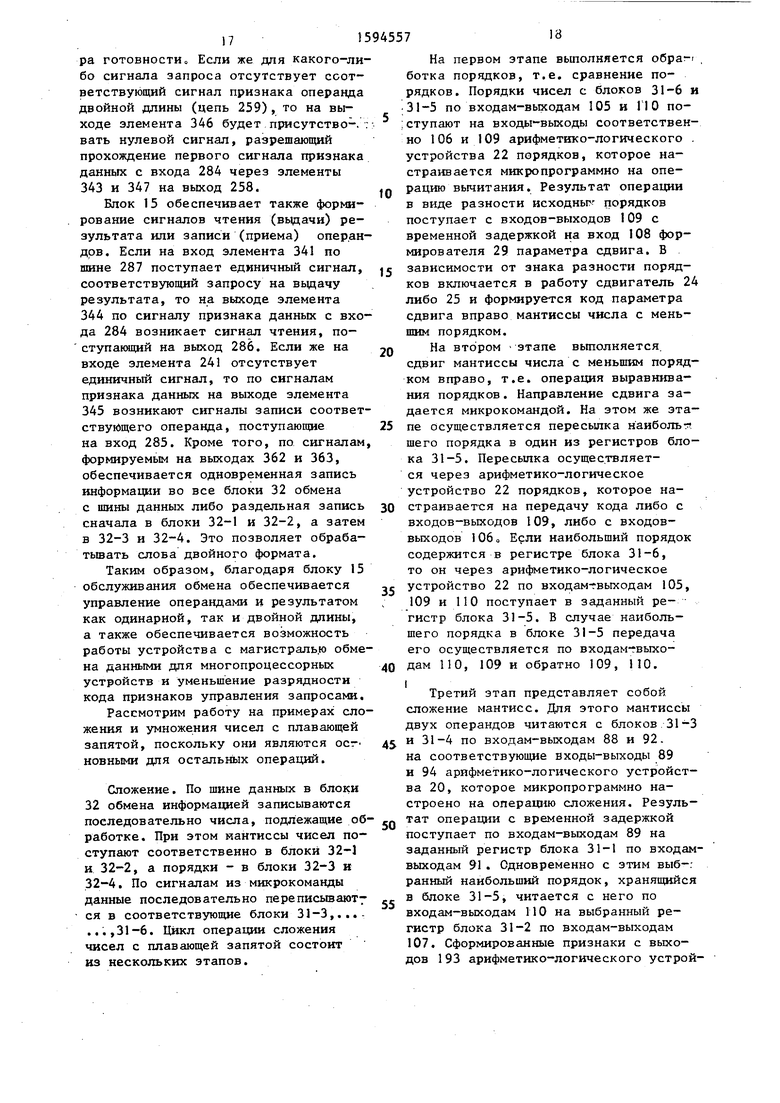

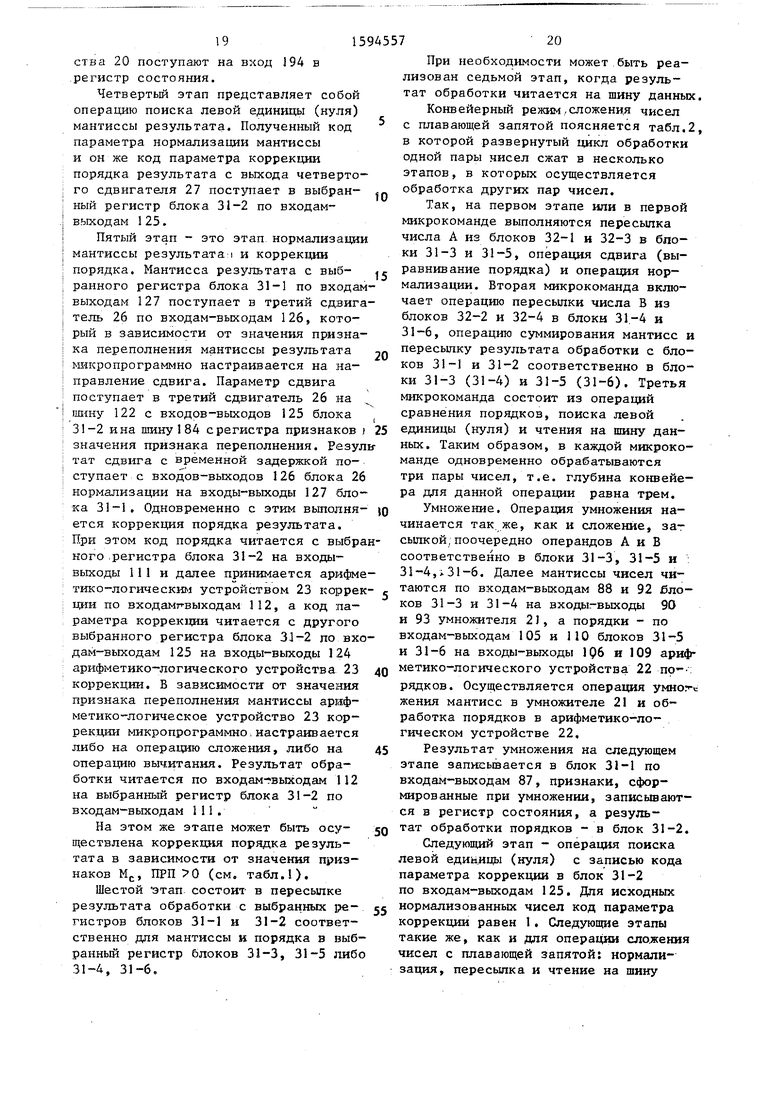

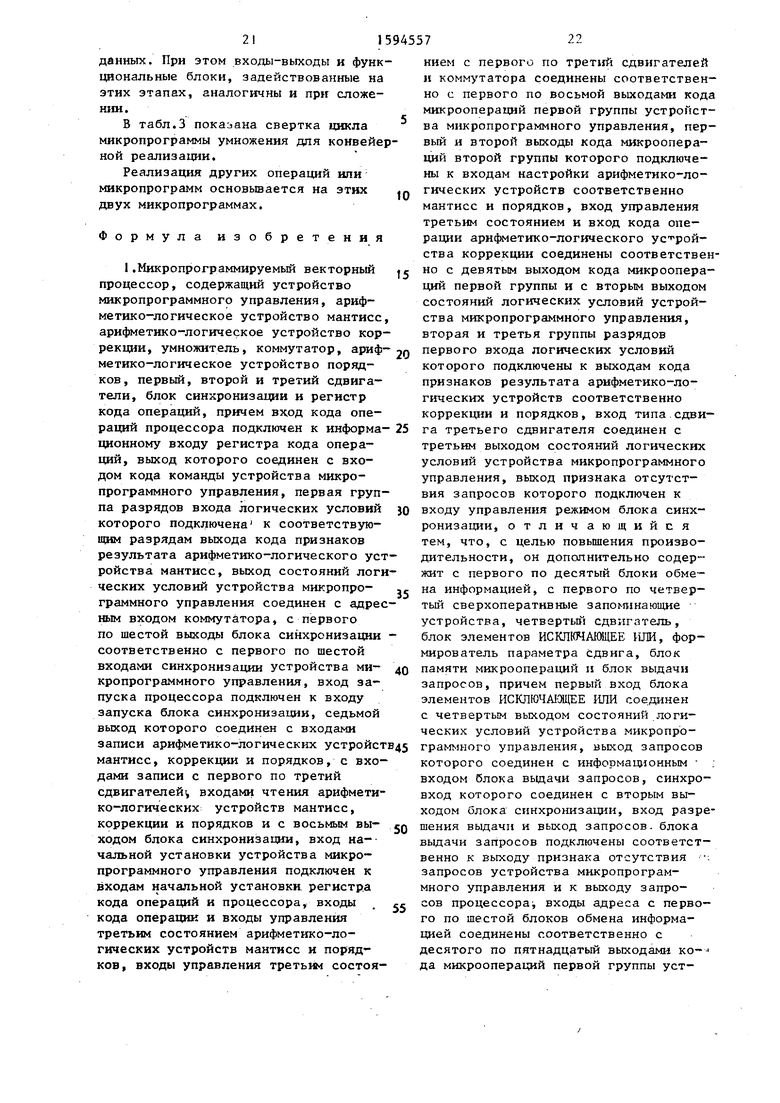

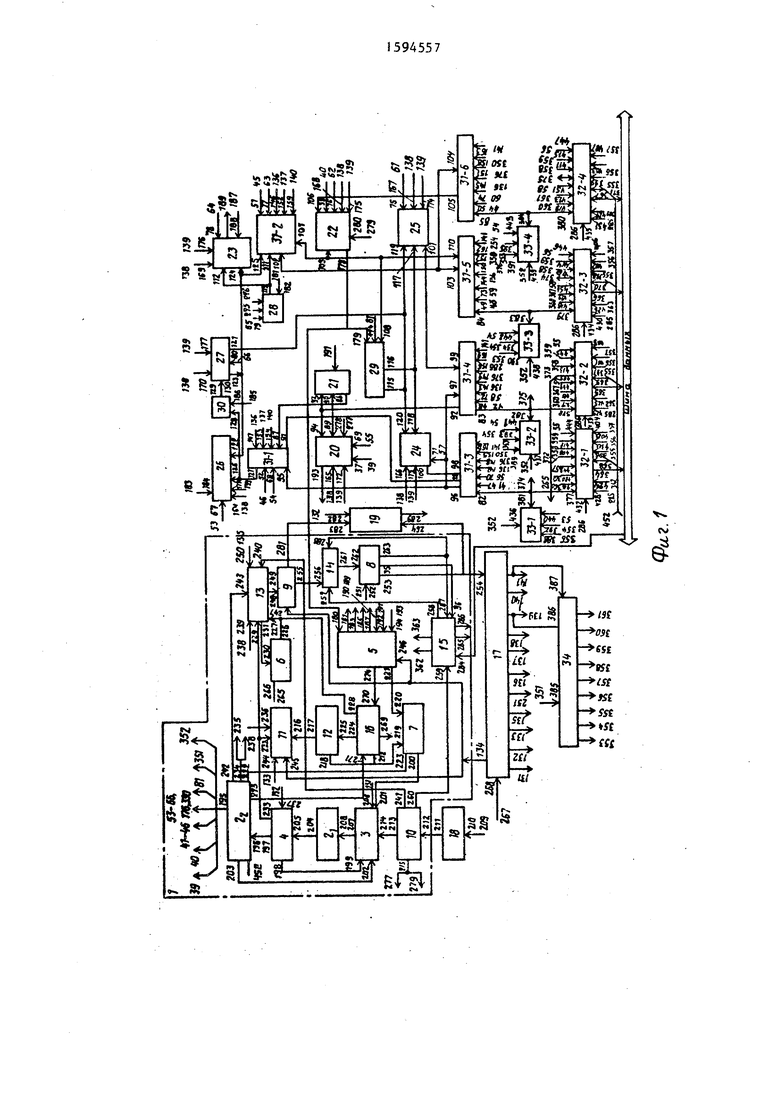

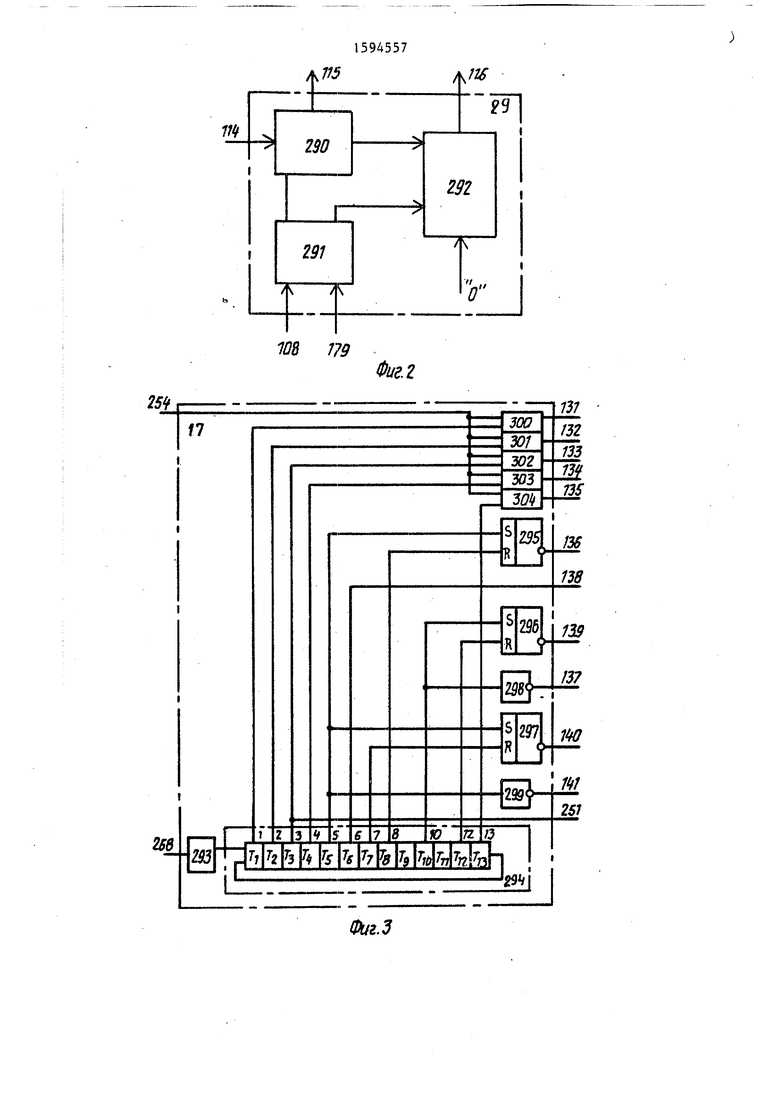

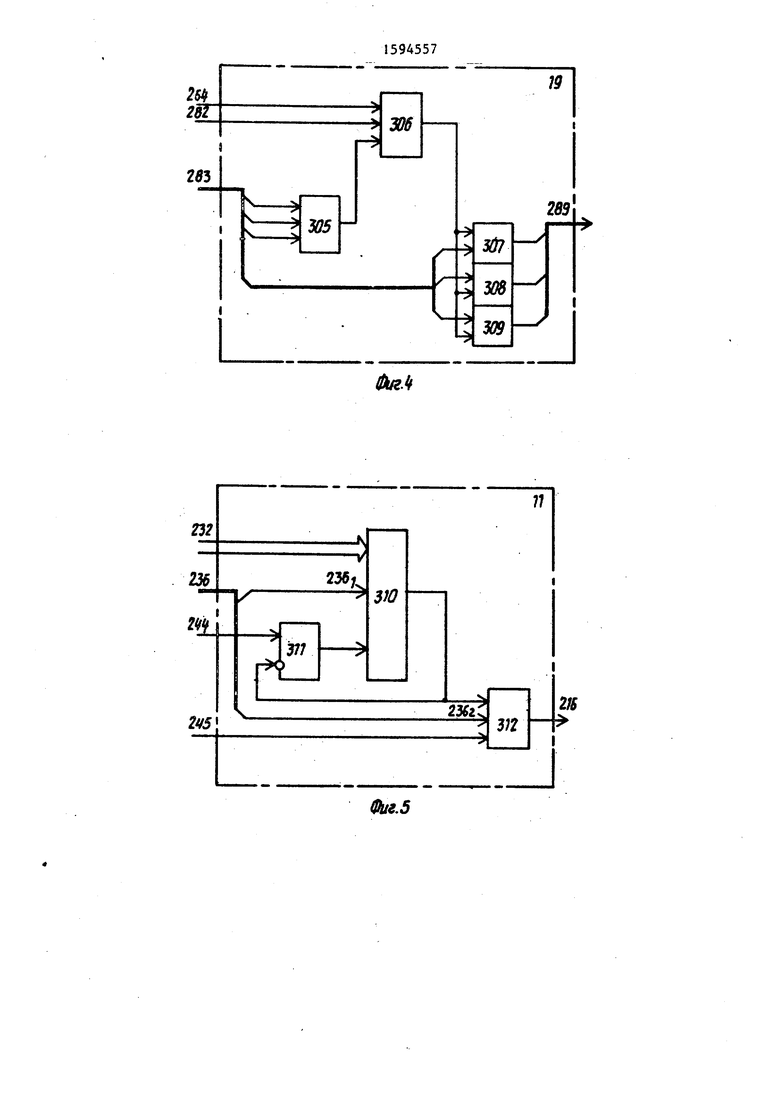

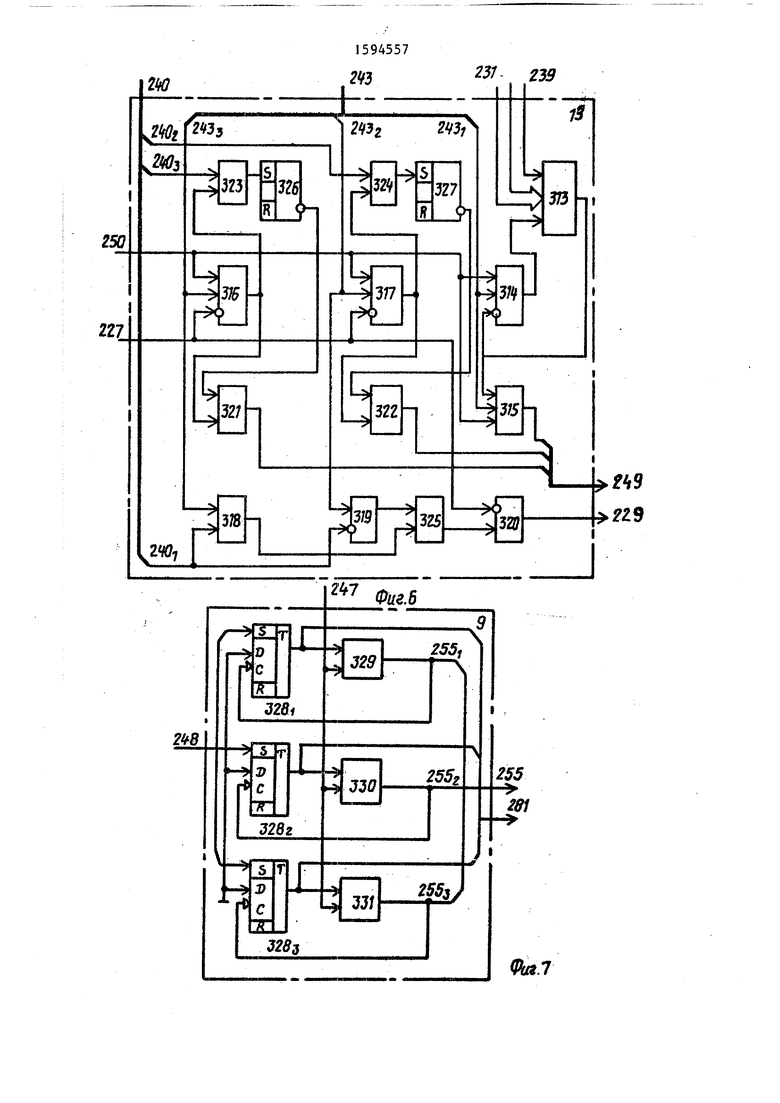

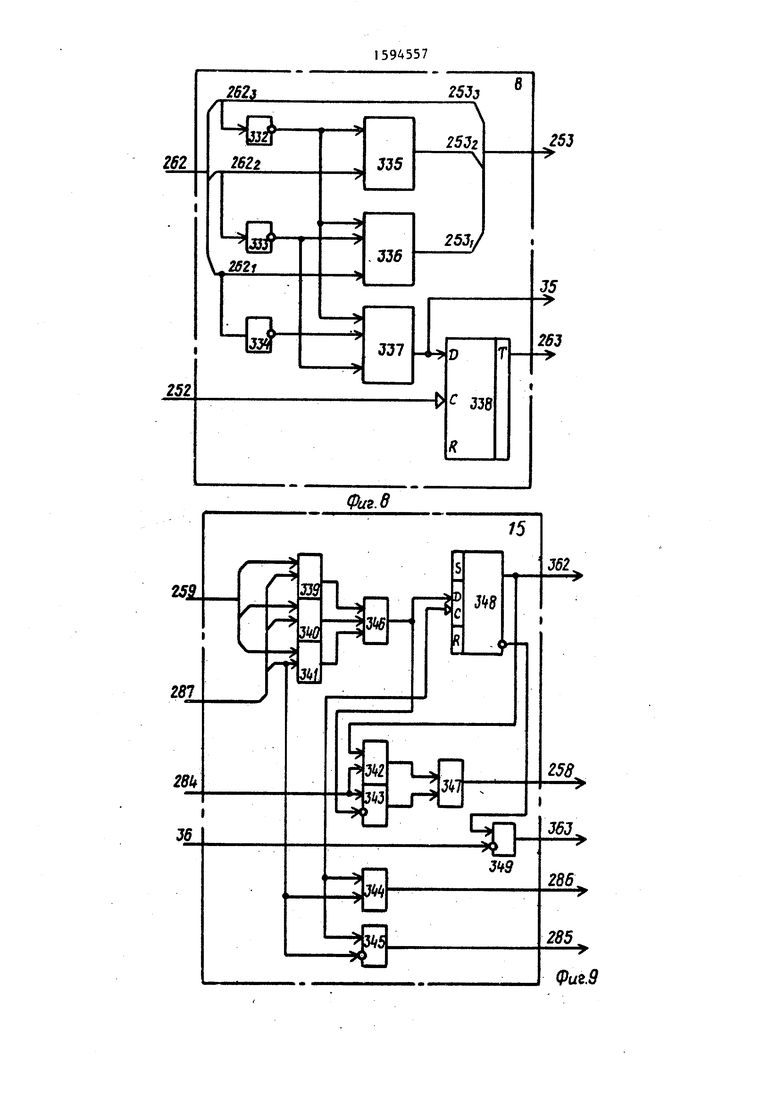

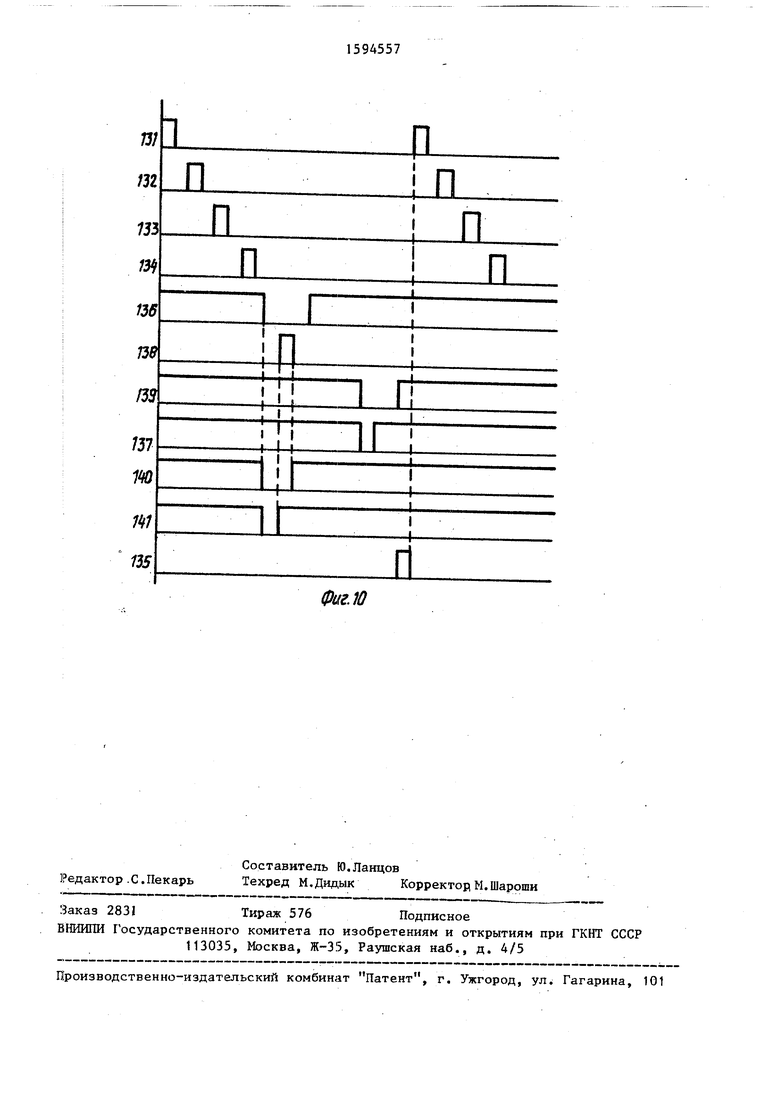

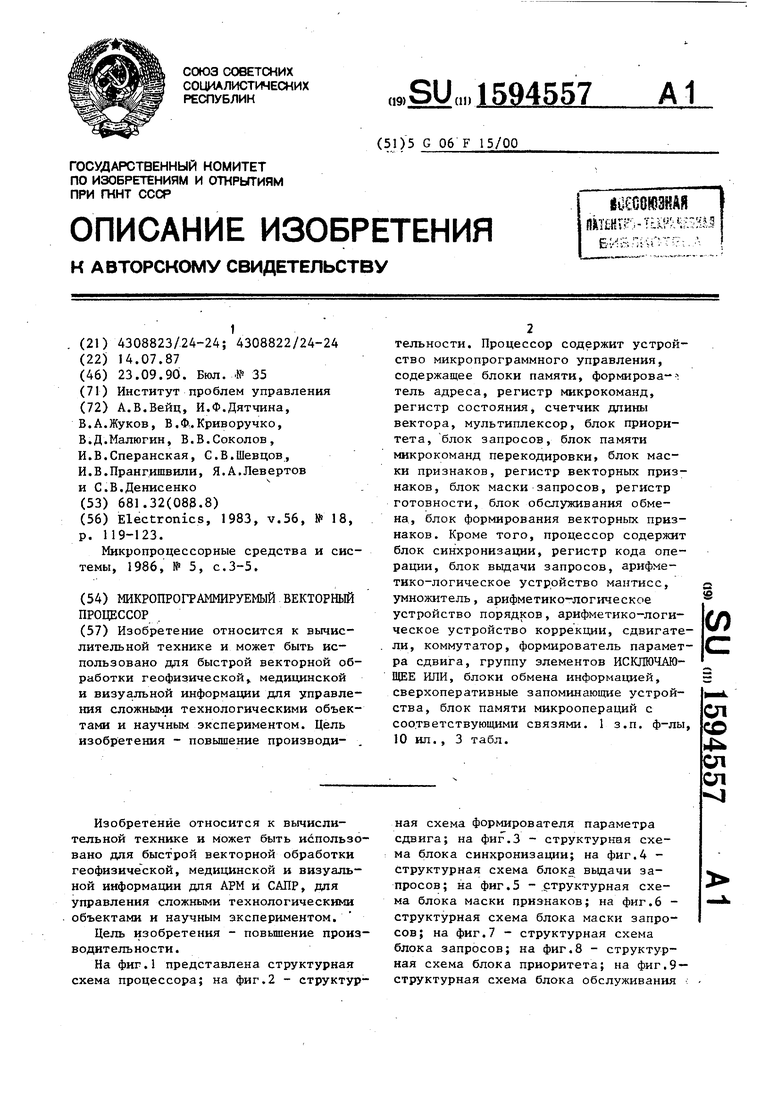

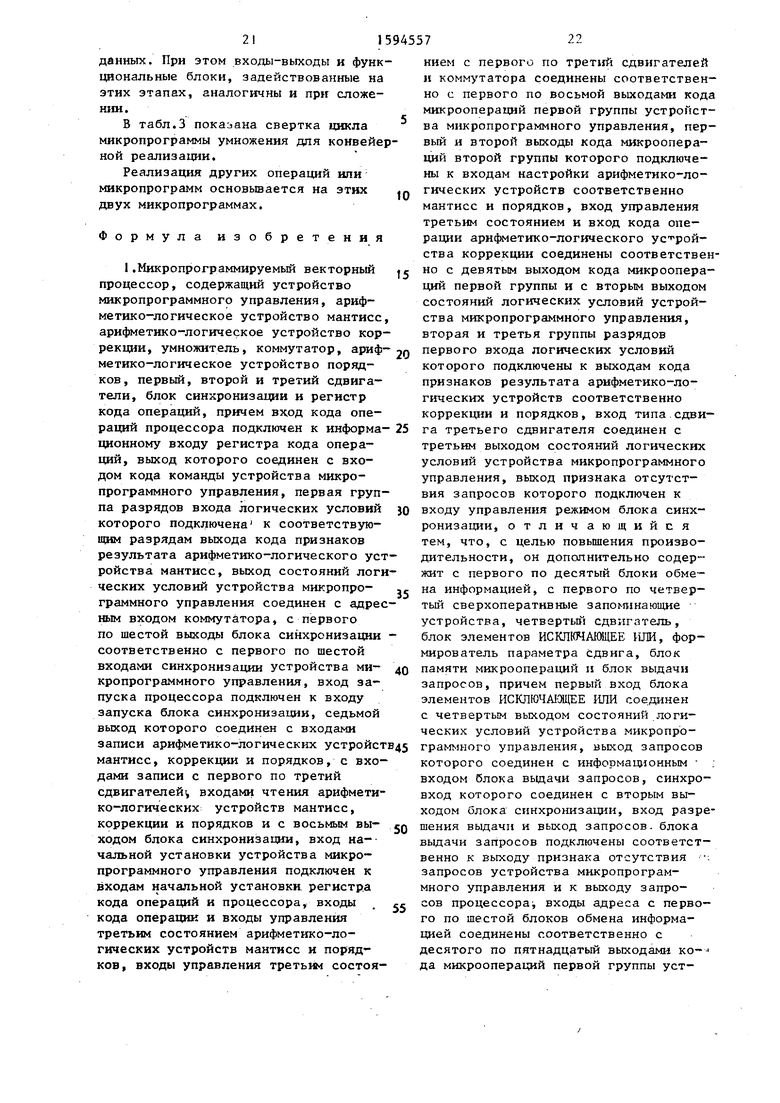

На фиг.1 представлена структурная схема процессора; на фиг.2 - структурная схема формирователя параметра сдвига; на фиг.З - структурная схема блока синхронизации; на фиг.4 - Структурная схема блока выдачи запросов; на фиг.5 -структурная схема блока маски признаков; на фиг.6 - структурная схема блока маски запросов; на фиг.7 - структурная схема блока запросов; на фиг.8 - структурная схема блока приоритета; на фиг.9- структурная схема блока обслуживания

обмена; на фиг.10 - временные диаграммы работы устройства.

Процессор содержит (фиг.) устройство 1 микропрограммного управления, содержащее блоки и 2j памяти, формирователь 3 адреса, регистр 4 микрокоманд, регистр 5 состояния, счетчик 6 длины вектора, мультиплекг-. сор 7, блок 8 приоритета, блок 9 запросов, блок 10 памяти микрокоманд ; перекодировки, блок 11 маски признаков, регистр 12 векторных признаков, блок 3 маски запросов, регистр 14 готовности, блок 15 обслуживания обмена, блок.16 формирования векторных признаков, а также п роцессор содержит блок 17 синхронизации, регистр 18 кода операции, блок 19 выдачи запросов, арифметико-логическое устройство 20 мантисс, умножитель 21., арифметико- логическое устройство 22 порядков, арифметико-логическое устройство 23 коррекции, с первого по четвертый

вого операнда - выход 112 резулвтата, выход 113, вход 114 типа сдвига, выход 115 типа сдвига, выход 116 пара- метра сдвига, входы 117 и 118 параметра сдвига, входы 119 и 120 типа сдвига, вход 121 типа сдвига, вход 122 параметра сдвига, выход 123 параметра сдвига, вход 124 третьего

to операнда, четвертый вход-выход 125, информационный вход-выход J26, третий вход-выход 127, вторые входы 128 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, выходы 129, информационный вход-выход 130,

J5 с первого по одиннадцатый выходы 131- 141, входы 142-147 чтения, входы 148-153 записи, входы 154-159 чтения, входы 160-170 записи, входы 171-177 чтения, выход 178 кода признаков

20 результата, вход 179 признака пара метра сдвига, четвертый информационный вход 180, первый выход 181, управляющий вход 182,второй выход 183,вход 84 типа сдвига,третий выход 185,первые

сдвигатели 24-27, коммутатор 28,, фор-25 входы 186 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ,

мирователь 29 параметра сдвига,.группу элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 30, с первого по десятый блоки 31-32 обмена информацией, с первого по четвертый сверхоперативные запомина.ющш2 устройства 33, блок 34 памяти мшсро- операций, выход 35 общей готовности, вход 36 общей готовности, входы 37 и 38 кода операций, выходы 39 и 40 кода операции, мантисс и порядков-.

четвертый выход 187, вход. 188-кода, операции, выход 189 кода признаков резулвтата, третий информационный вход 190, выход 191 кода призиаков 30 результата/ второй информационный

вх.од 192, выход 193 кода признака результата, первый информационный вход 194, выходы 195, информационный вход J96, информационный выход 197, информационный выход 198, адресный

Г---л- -- ..4.v,v, « , чJ Jpмaциuнныи ВЫХОД 1 уй, адресныи

с первого по шестой выходы 41-46 кода вход 199, выход 200 мультиплексора, адреса операндов-, входы 47-52 кода управляющие входы 201 и 202, выходы адреса, с первого по четьфнадцатый 203 кода управления формирователем выходы 53-66 управления конвейером, адреса, выход 204 кода микрокоманды, входы 67-80 управления третыш состоя- информационный вход 205, синхровход нием, выход 81 кодов операций сдвига, 206,выход 207, адресный вход208,вход первые входы-выходы 82-85, выход, 86 209 кода операции, информационный вход результата, второй вход-выход 7, тре- 210,информационный выход211,адресный тий вход-выход 88, вход первого one- : 212, адресный выход 213, адресный

45 вход 214, группу выходов 215 кода микроопераций, выход 216, вход 217 разрешения записи, группу информацнон- ных выходов 218, первый 219 к второй 220 информационные входы, информацкон-: ный шлход 221, выход 222 кода управления мультиплексором, управляющий вход 223, выход 224, информационный вход 225, выход 226 переполнения счетчика, первый вход 227 первой группы управляющих входов, первый вход 228, первый выход 229, счетный вход ИЗО, информационные входы 23 и 232, третий информационный выход 233, выходы 234, выход 235 кода управления

ранда - выход 89 результата, вход 90 первого операнда, первый вход-выход 91, третий вход-выход 92, вход 93 второго операнда, вход 94 второго операнда, четвертый входтвыход 95, четвертые входы-выходы 96 и 97, вторые входы-выходы 98 и 99, информационные входы-выходы 100. и 101, второй вход-выход 102, вторые входы-выходы 103 и 104, третий вход-выход 105, вход 106 второго операнда, первый: вход-выход 107, информационный вход 108, вход первого операнда - выход 109 результата, третий врсод-выход 110, третий вход-выход 111, вход пер50

55

945574

вого операнда - выход 112 резулвтата, выход 113, вход 114 типа сдвига, выход 115 типа сдвига, выход 116 пара- метра сдвига, входы 117 и 118 параметра сдвига, входы 119 и 120 типа сдвига, вход 121 типа сдвига, вход 122 параметра сдвига, выход 123 параметра сдвига, вход 124 третьего

to операнда, четвертый вход-выход 125, информационный вход-выход J26, третий вход-выход 127, вторые входы 128 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, выходы 129, информационный вход-выход 130,

J5 с первого по одиннадцатый выходы 131- 141, входы 142-147 чтения, входы 148-153 записи, входы 154-159 чтения, входы 160-170 записи, входы 171-177 чтения, выход 178 кода признаков

20 результата, вход 179 признака пара метра сдвига, четвертый информационный вход 180, первый выход 181, управляющий вход 182,второй выход 183,вход 84 типа сдвига,третий выход 185,первые

25 входы 186 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ,

5 входы 186 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ,

четвертый выход 187, вход. 188-кода, операции, выход 189 кода признаков резулвтата, третий информационный вход 190, выход 191 кода призиаков 0 результата/ второй информационный

вх.од 192, выход 193 кода признака результата, первый информационный вход 194, выходы 195, информационный вход J96, информационный выход 197, информационный выход 198, адресный

чJ Jpмaциuнныи ВЫХОД 1 уй, адресныи

вход 199, выход 200 мультиплексора, управляющие входы 201 и 202, выходы 203 кода управления формирователем адреса, выход 204 кода микрокоманды, информационный вход 205, синхровход 206,выход 207, адресный вход208,вход 209 кода операции, информационный вход 210,информационный выход211,адресный 212, адресный выход 213, адресный

аской признаков, группу уп равляющих входов 236, вход 237 разрешения записи, выход 238 кода управления маской запросов, второй вход 239 первой группы управляющих входов, вторую группу управляющих входов 2АО, выход 241 кода маски, выходы 242 кода запросов, третью группу управляющих входов 243, первый 244 и второй 245 синхровходы, вход 246 разрешения записи, синхровход 247, информационный вход 248, второй выход 249, синхровход 250, двенадцатый выход 251 , с инхровход 252, первый выход 253, управляющий вход 254, первую группу выходов 255, асинхронные входы 256-установки в 1, вход 257 синхронизации, выход 258 строба го- товности, управляющий вход 259, выход 260 признака двойных запросов, выход 261 , информационный вход 262, второй выход 263, вход 264 разрешения выдачи, вход 265 кода длины вектора, информационный вход 266, вход 267 пуска устройства, вход 268 пуска, выход 269 кода признаков устройства, второй вход 270, третий вход 271,четвертый вход 272, выход 273 кода управления векторными признаками, пятый выход 274, первый 275 и второй 276 информационные входы,. ВЫХОД 277 кода настройки, вход 278, выход 279 кода настройки, вход 280, группу выходов 281, синхровход 282, вход 283 запросов, вход 284 признака сопровождения данных, выход 285 записи, выход 286 чтения, информационный вход 287 f синхронный вход 288 установки в О, в ыход 289 запросов.

Формирователь 29 параметра сдвига содержит блок 290 памяти, регистр 291 и арифметико-логический узел 292.

Блок 17 синхронизации содержит ге- нератор 293 импульсов, кольцевой сдвигающий регистр 294, триггеры 295-297, элементы НЕ 298 и 299 и элементы И 300-304.

Блок 19 вьщачи запросов содержит элемент ИЛИ 305 и группу элементов И 306-309, блок 11 маски признаков . содержит счетчик 3|0, элементы И 31) и 312, блок 13 маски запросов содержит счетчик 313, группу элементов И 314-324, элемент ИЛИ 325 и триггеры 326 и 327.

Блсйс 9 запросов содержит регистр 328 и группу элементов И 329-331 , блок 8 приоритета содержит группу

94557

.

элеменгов НЕ 332-334, группу элементов И 335-337 и триггер 338, блок 15 обслуживания обмена содержит группу элементов И 339-345, элементы ИЛИ 346 347, триггер 348 и элемент И 349. Кроме того, процессор содержит пятнадцатый выход 350 управления конт вейером, выход 251 управления направ- ,Q лением обмена, седьмой выход 252 кода адреса, выход 353 чтения, выход 354 записи, выход 355 запася выход 356 чтения, управляющий выход 357, выход 358 записи, выход 359 чте- J5 ния, выход 360 записи, выход 361 чтения, первый 362 и второй 363 управляющие выходы, первые информационные входы-выходы 364-367, вторые информационные входы-выходы 368-371, третьи

20 информационьше входы-выходы 372 -и 373, четвертые информационные входы- выходы 374 и 375, шестнадцатый выход 376 управления конвейером, пятые ннформа1щонные входы-выходы 377-380,

25 информационные входы-выходы 381-384, первый вход 385, второй вход 386, г.; третий вход 387, входы 388-391 чтения, входы 392-399 записи, входы 400-403 чтения, управляющие входы

30 404-407, входы 408-411 записи, входы 412-415 чтения, входы 416-419 записи, входы 420-423 чтения, первые 424 и 425 и йт-орые 426 и 427 управляющие входы, входы 428-431 записи, входы 432-435 чтения, входы 436-439 кода адреса, входы 440-451.разрешения обмена и выход 452 кода констант.

Формирователь 29. параметра сдвига содержит (фиг.2) блок 290 памяти,

дл регистр 291 и арифметико-логический блок 292.

BrfoK 17 синхронизации содержит (фиг.З) генератор 293 HMnyjnjcoB, кольцевой сдвигающий регистр 294,.

45 триггеры , инверторы 298-299, с первого по пятый элементы И 300- 304. .

Блок синхронизации предназначен для выработки сигналов чтения, записи

50 информации в различные блоки устройства, для формирования определенной временной последовательности синхроимпульсов , необходимых для организации правильной работы векторного про-

55 цесса.

При поступлении сигнала Пуск на вход 268 блока синхронизации генератор 293 начинает формировать тактовые импульсы, поступающие на вход

кольцевого сдвигающего регистра 294. На выходе этого регистра поочередно возникают сигналы, которые вместе с КЗ-триггерами и логическими элементами, указанными на фнг.З, обеспечивают формирование сигналов в соответствии с временной диаграммой, приведенной на фигьЮ. Сигналь; на выходах 131-135 блока синхронизации вознакают только тогда, когда присутствует сигнал разрешения на управляющем входе 254.I

Блок 19 вьщачи запросов содержит

10

ботки (сложения, вычитания) порядков чисел.

Арифметико-логическое устройство 23 коррекции служит для коррекции порядка результата на этапе нормализации.

Регистр 5 состояния предназначен для приема, хранения и выдачи признаков, получаемых в процессе вычисления.

Сдвигатель 27 совместно с группой элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 30 выполняет функцию поиска левой единицы (нуля) начиная со старшего разряда мантиссы.

-Г1- -- . - V - 1 ff ft. I tCLfl t ni.,V.Ol

СФИГ.4; многовходовой элемент ИЛИ 305 5 РУппа элементов 30 состоит из элемеии группу элементов И 306-309.

Блок 19 выдачи запросов предназначен для формирования в определенные моменты времени запросов на получение очередных элементов вектора или выдачу результата.

При поступлении хотя бы одного из запросов на вход элемента ИЛИ 305 на его выходе возникает сигнал, который при наличии сигнала разрешения на- входе 264 и строба на синхровходе 282 проходит через элемент И 306 на вход группы элементов И 307-309 и разрешает прохождение

тов суммы по mod 2, на один из входов которых поступает соответствующий разряд мантиссы, а на другой вход - знак мантиссы. В зависимости от знака иан- 20 ,™С1СЫ блок 30 либо передает разряды мантиссы без изменения, либо с инверсией. Сдвигатель 27 формирует код параметра сдвига мантиссы для операции нормализации. ; 25 Арифметико-логическое устройство

20 предназначено для обработки данных при арифметических и логических операциях. Арифметико-логическое устройство 20 служит для обработки мантисс

35

запросов с входа 283 через соответст- 30 либо чисел с фиксированной запятой, вующие элементы И на выход 289.

Четырехканальные блоки 31-1 и 31- 2 обмена информацией выполняют функции промежуточных регистров общего назначения, блоки 31-3 и 31-4 служат для приема чисел с фиксированной запятой либо мантисс чисел с плавающей запятой. Четырехканальные блоки 31-5 и 31-6 обмена информацией служат для приема порядков чисел с плавающей 40 запятой. Блоки 32-1 ,... ,32-4 предназг- начены для обмена информацией с шиной данных. Каждый из блоков 31, 32 содержит четьфе внутренних регистра..

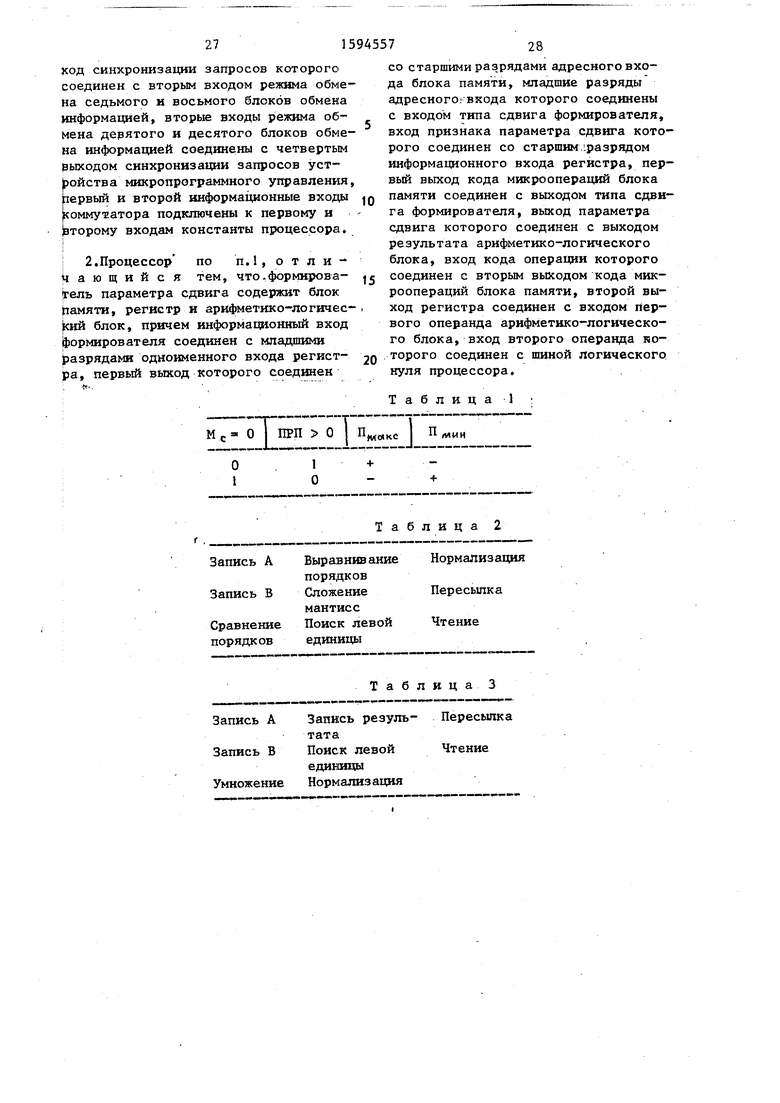

Коммутатор 28 предназначен для формирования максимального либо минимального порядка результата в зависимости от значения признаков. Такая зависимость показана в табл.1, где .. М О - значение мантиссы результата; П максимальный порядок; минимальньй порядок; ПРП О - призтг; нак переполнения порядков больше 0.

Формирователь 29 параметра сдвига (фиг.2) предназначен дпя вьфаботки кода параметра сдвига и типа сдвига. На вход 108 формирователя поСдвигатели 24-26 предназначены для 45 ступает код разности порядков из

приема и сдвига данных с последующей их вьодачей. Сдвиги могут быть вправо и влево, арифметические и логические, с сохранением выпадающих при сдвиге

блока 22, который записывается в регистр 291. Сюда же по входу 179 из блока 22 поступает знак разности порядков. Код разности порядков вместе

разрядов и их сборкой по ИЛИ с после- сп знаком поступает на вход старших

дукнцим сдвигом информации. Параметр сдвига и его тип задаются: формирова телам 29 сдвига по шинам 115 и 116.

Умножитель 21 предназначен дпя умножения чисел с фиксированной запятой.

Арифметико-логическое устройство 22 порядков предназначено дпя обра55

разрядов адреса блока 290 памяти. Одновременно четыре младших разряда кода разности поступают иа вход первого операнда арифметико-логического устройства 292. На вход младших разрядов адреса блока 290 памяти по входу 114 из микропрограммы-поступает код типа сдвига. На основе поступивших данных этот блок вырабатьшает

ботки (сложения, вычитания) порядков чисел.

Арифметико-логическое устройство 23 коррекции служит для коррекции порядка результата на этапе нормализации.

Регистр 5 состояния предназначен для приема, хранения и выдачи признаков, получаемых в процессе вычисления.

Сдвигатель 27 совместно с группой элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 30 выполняет функцию поиска левой единицы (нуля), начиная со старшего разряда мантиссы.

-- . - V - 1 ff ft. I tCLfl t ni.,V.Ol

РУппа элементов 30 состоит из элемеи 5 РУппа элементов 30 состоит из элемеитов суммы по mod 2, на один из входов которых поступает соответствующий разряд мантиссы, а на другой вход - знак мантиссы. В зависимости от знака иан- 20 ,™С1СЫ блок 30 либо передает разряды мантиссы без изменения, либо с инверсией. Сдвигатель 27 формирует код параметра сдвига мантиссы для операции нормализации. 25 Арифметико-логическое устройство

20 предназначено для обработки данных при арифметических и логических операциях. Арифметико-логическое устройство 20 служит для обработки мантисс

либо чисел с фиксированной запятой,

Коммутатор 28 предназначен для формирования максимального либо минимального порядка результата в зависимости от значения признаков. Такая зависимость показана в табл.1, где .. М О - значение мантиссы результата; П максимальный порядок; минимальньй порядок; ПРП О - призтг; нак переполнения порядков больше 0.

Формирователь 29 параметра сдвига (фиг.2) предназначен дпя вьфаботки кода параметра сдвига и типа сдвига. На вход 108 формирователя поступает код разности порядков из

блока 22, который записывается в регистр 291. Сюда же по входу 179 из блока 22 поступает знак разности порядков. Код разности порядков вместе

знаком поступает на вход старших

разрядов адреса блока 290 памяти. Одновременно четыре младших разряда кода разности поступают иа вход первого операнда арифметико-логического устройства 292. На вход младших разрядов адреса блока 290 памяти по входу 114 из микропрограммы-поступает код типа сдвига. На основе поступивших данных этот блок вырабатьшает

на первом выходе код, который поступает на выход 115 типа сдвига, а на втором выходе вырабатьшает код операции, поступающий в арифметико- логическое устройство 292. На вход второго операнда арифметико-логического устройства 292 поступает код логического нуля, в зависимости от кода операции арифметико-логического уст- . ройства на выходе 1I6 вырабатывается код параметра сдвига,

Все блоки, входящие в устройств.6, кроме блока 17 синхронизации, блока 13 маски запросов, блока П маски признаков, блока 15 обслуживания обменау блока 19 выдачи запросов, блока 8 приоритета, блока 9 запросов и формирователя 29 параметров сдвига, являются стандартными, известными в технике схемными решениями и поэтому их структурные схемы в описании устройства не приведены.

Например, блок 31-3 обмена информацией реализуется на БИС - схема обмена информацией КР 1802 ВВК

Первые сдвигатели 24 и 27 реализуются на БИС - арифметический расширитель: КР 1802 ВР1.

Арифметико-логическое устройство. 20 мантисс реализуется на БИС - микропроцессорная секция КР 1802 ВС1. Формирователь 3 адреса реализуется на БИС - схема управления последовательностью микрокоманд К 1804 ВУ4.

Коммутатор 28 реализуется на ИС К 155 КП-2 - дешифратор - коммутатор.

Блоки 2 и 2 памяти реализуются на ИС КР556 РТ5.

Шина данных является двунаправленной шиной, по которой передаются исходные числа либо с фиксированной, либо с плавающей запятой и результаты обработки.

Блок 16 формирования векторных признаков представляет собой блок памяти. Входы 270, 272 и 228 и старшие разряды входа 271 являются адресиыto

15

20

25

30

35

40

и признака переполнения счетчика 6, поступающего по входу 228, предыдущ (т.е. полученных на предыдущем такт работы устройства) векторных призн ков, поступающих по входу 272, в за висимости от разрешения из микропро граммы фop шpyeт векторные признаки необходимые для внутренней работы устройства (выход 224) и внешней работы (выход 269).

Блок 13 маски запросов содержит (фиг.6) счетчик 313, группу элемен тов И 314-324, элемент ИЛИ 325, пер вый 326 и второй 327 триггеры, первую группу управляющих входов 227, вторую группу управляющих входов 24 третью группу управляюпшх входов 243, информационный вход 231, синхр вход 250, первый 229 и второй 249 выходыо Блок 10 запросов содержит (фиг.7) регистр 328 и группу элемен тов И 329-331, группу информационны входов 248, синхровход 247, первую группу выходов 255, вторую группу в ходов 281 .

Блок 8 приоритета содержит (фш. группу элементов ИЛИ 332-334, групп элементов И 335-337, триггер 338, группу информационных входов 262, с хровход 252, первый выход 253, втор выход 263 и выход 35 общей готовнос

Блок 15 обслуживания обмена соде жит () группу элементов И 339 345 и 349, первый 346 и второй 347 элементыИЛИ, триггер 348, управляю щий вход 259, информацноиньй вход 287, вход 284 признака данньк, вход 36 общей готовности, выход 258 стро готовности данньгх, вьпсод 285 записи выход 286 чтения, первый 362 и втор 363 управляющие выходы.

Микропрограмма предлагаемого уст- дг ройства представляет собой микропро грамму конвейерной обработки данных обеспечивающую выполнение арифметик логической операции, заданной в команде (например, умножение двух чими входами блока памяти. Младшие раз- 50 плавающей точкой, поразрядное

ряды входа 271 являются входами разрешения чтения блока памяти, выход 224 и выход 269 кода признаков является первым и вторым информационными выходами блока памяти. Блок 19 на . jg каждом такте i. работы устройства из скалярных признаков, т.е. признаков реагультатов обработки компонент векторов, поступающих на его вход 270

логическое умножение двух кодов). Микропрограмма конвейерной обработки данных - это такая микропрограмма, которая позволяет вести параллельную обработку сразу нескольких пар элементов операндов-массивов (либо нескольких элементов одного операнда- массива для унарных команд), причем каждая из. пар элементов находит

и признака переполнения счетчика 6, поступающего по входу 228, предыдущих (т.е. полученных на предыдущем такте работы устройства) векторных признаков, поступающих по входу 272, в зависимости от разрешения из микропрограммы фop шpyeт векторные признаки, необходимые для внутренней работы устройства (выход 224) и внешней работы (выход 269).

Блок 13 маски запросов содержит (фиг.6) счетчик 313, группу элементов И 314-324, элемент ИЛИ 325, первый 326 и второй 327 триггеры, первую группу управляющих входов 227, вторую группу управляющих входов 240, третью группу управляюпшх входов 243, информационный вход 231, синхро- вход 250, первый 229 и второй 249 выходыо Блок 10 запросов содержит (фиг.7) регистр 328 и группу элементов И 329-331, группу информационных входов 248, синхровход 247, первую группу выходов 255, вторую группу выходов 281 .

Блок 8 приоритета содержит (фш.8) группу элементов ИЛИ 332-334, группу элементов И 335-337, триггер 338, группу информационных входов 262, синхровход 252, первый выход 253, второй выход 263 и выход 35 общей готовности.

Блок 15 обслуживания обмена содержит () группу элементов И 339- 345 и 349, первый 346 и второй 347 элементыИЛИ, триггер 348, управляющий вход 259, информацноиньй вход 287, вход 284 признака данньк, вход 36 общей готовности, выход 258 строба готовности данньгх, вьпсод 285 записи, выход 286 чтения, первый 362 и второй 363 управляющие выходы.

Микропрограмма предлагаемого уст- ройства представляет собой микропрограмму конвейерной обработки данных, обеспечивающую выполнение арифметико- логической операции, заданной в команде (например, умножение двух чи плавающей точкой, поразрядное

логическое умножение двух кодов). Микропрограмма конвейерной обработки данных - это такая микропрограмма, которая позволяет вести параллельную обработку сразу нескольких пар элементов операндов-массивов (либо нескольких элементов одного операнда- массива для унарных команд), причем каждая из. пар элементов находитс

в определенной фазе выполнения арифметико-логической операции

Например, известно, что операция сложения двух чисел с плавающей точкой состоит из следующих фаз ашшиз порядков, выравнивание порядков, сложение и нормализация Микропрогра I ма данной операз даи позволяет однозре : менно нормализовать сумму i-й парны I чисел, суммировать i+1-ю пару/чисел, выравнивать порядки у i+2-й пары чи- I сел (например, i, i+l , i+2, i+3 -.-: j индексы четьфех, расположенных под- 1 ряд, элементов векторов-операндов). ; Для организации конвейерного процесс ; обработки .векторов-операндов в уст- ; ройстве использ1тотся-микрооперации запроса данных или запроса двойных I данных. Они предназначены для пере- I сьшки элемента массива операнда на I ОЗУ либо для пересыпки элемента I массива результата выполнения вектор- I ной операции в ,ОЗУ. ; При выполнении определенного запро

са соответствующий триггер регистра 14 готовности устанавливается в состояние Готов. Запрос считается ; выполненным, если запрашиваемая пересылка вьтолнена (соответствующий триггер регистра готовности сбрасывается) .

Благодаря использованию в устройстве механизмов блокировки и выдачи запросов, а также двойных запросов, блокировки формирования векторных признаков и блокировки всех запросов, кроме первого, с помощью кода настройки из блока 10 памяти возможно блокирование вьщачи ложных результатов и признаков результата с конвейера до того момента, пока на входы опера:цион ных блоков, входящих в последнюю ступень конвейера для данной операции, не придут результаты обработки пер- вой пары операндов массива данных на всех предшествующих ступенях KOimeue- ра. С выдачей последней пары операндов массива данных запросы на новые операнды также блокируются. Возмож- на также аппаратная блокировка всех запросов, кроме первого, на вьщачу одного из операндов при выполненюн операций типа вектор - скаляр, напрк- мер умножения компонент вектора на константу, что приводит к сокращению микропрограмм выполнения таких операций , а следовательно, к сокращению объема ПЗУ и всего оборудования в целом и повышения быстродействия устроства. Устройство работает следующим образом.

По входу 268 Пуск происходит установка устройства в исходное состояние, подготовка схем к работе (цепи сброса регистров и счетчиков устройства в исходное состояние не показаны). По входу 265 в счетчик j длины вектора из блоков 32-1 и 32-2 обмена заносится длина вектора. Код операции пост упает на вход 20 устройства и затем в регистр 18 кода операции векторной команды.

В блоке 10 памяти микрокоманд перекодировки происходит перекодирование кода операции в начальный адрес соответствующей микропрограммы, в ко настройки операционной части, поступающий на выход 215 и позволяющий реализовать выполнение микропрограмм в конвейерйом режиме для данного кода операции, аппаратно модифициро.- вать операции, вьщолняемые отдельным устройствами (например,изменить тип данных и формат данных в операционных блоках, блокировать вьщачу запросов, настроить блок 13 на обработку двойных запросов).

Формирователь 3 служит для формирвания адреса каждой последующей микрокоманды, вьтолняемой микропрограммы в соответствии с временной диаграммой. По сформированному адресу, поступающему на блок 2 памяти микропрограмм, выбирается соответствующая микрокоманда, поступающая на регистр 4 микрокоманд для хранения в период выполнения микрокоманды.

Блок 22 памяти расщифровьюает код микрокоманды и выдает на выход 95 кода микроопераций и блоки устройства управляющие сигналы. Поскольку вьтолнение микропрограммы происходит в конвейерном режиме, возникает необходимость .маскирования записи признаков в регистр 12 векторных признаков. Дпя этого служит блок 11 маскирования признаков. Кроме векторных признаков, поступающих на информационный вход 225, на регистр 12 по этому же входу поступает признак последнего операнда .

По информационным входам 180, 190, 192 и 194 на регистр 5 состояния поступают признаки, возникающие при выполнении скалярных операций, т.е. операций над компонентами век13

торов о Признаки скалярных и векторных операций поступают на мультиплексор 7, с которого под управлением блока 22 памяти необходимьй признак поступает на формирователь 3 адреса. Признаки вектора-результата могут выдаваться на выход 269 через блок, 16 при наличии соответствующего разрешения в микропрограмме получения даннрго результата.

Блок 13 маски запросов используется для маскирования записи запросов в блок 9 запросов и формирования сигналов для подрчета длины вектора в счетчике 6.

Блок 9 запросов функционально представляет собой очередь запросов тлу-биной 1. Наличие этой очереди позво- ляет выставлять из микропрограммы очередной запрос в то время, когда идет обслуживание предыдущего.

Из блока 9 запросы поступают на регистр 14 готовности и блок 19 выдачи запросов.

Из регистра 14 готовности запросы поступают на блок 8 приоритета, который предназначен для выработки определенного порядка, вьщачи запросов.

Блок 17 синхронизации формирует временную последовательность синхросигналов, используемых для формирования временных соотношений при выполнении микропрограммы.

455714

регистре (состояние, когда все запросы обслужены).

При отсутствии запросов на информационном входе 262 появляются ничные сигналы на выходах инверторов 332-334 и, соответственно, элементе И 337. Импульс, поступающий на синх7 ровход 252, при наличии сигнала на выходе элемента 337 взведет триггер 338 и на втором выходе 263 появится

10

5

0

5

0

сигнал, говорящий о том, что все запросы в регистре 14 готовности обслужены. Сигнал общей/ГОТОВНОСТИ появится также на выходе 35

Очередность вьщачи запросов на первый выход 253 реализуется следую- щим образом: запрос, поступающий на вход 262з, немедленно проходит на выход 253; запрос, поступающий на вход 2622«проходит через элемент 335 на выход 253 только при отсутствии запроса на .входе запрос, поступающий на вход 262, проходит через элемент 336 на выход 253 тогда и только тогда, когда отсутствуют запросы и на входе 262 и на входе 262.

Блок 13 маски запросов (фиг.6) предназначен для разрешения или запрещения прохождения запросов в блок 9 запросов, а также формирования сигналов, необходимых для подсчета длины векторов в счетчике 6. Для маскирова

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство микропрограммного управления | 1987 |

|

SU1539776A1 |

| Операционное устройство | 1985 |

|

SU1367012A1 |

| Устройство для обработки данных | 1985 |

|

SU1287146A1 |

| Устройство для обработки данных | 1987 |

|

SU1513443A1 |

| Однородная вычислительная система | 1984 |

|

SU1275458A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Микропроцессор | 1984 |

|

SU1242975A1 |

| Специализированный процессор для вычисления элементарных функций | 1985 |

|

SU1330627A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Центральный процессор | 1991 |

|

SU1804645A3 |

Изобретение относится к вычислительной технике и может быть использовано для быстрой векторной обработки геофизической, медицинской и визуальной информации для управления сложными технологическими объектами и научным экспериментом. Цель изобретения - повышение производительности. Процессор содержит устройство микропрограммного управления, содержащее блоки памяти, формирователь адреса, регистр микрокоманд, регистр состояния, счетчик длины вектора, мультиплексор, блок приоритета, блок запросов, блок памяти микрокоманд перекодировки, блок маски признаков, регистр векторных признаков, блок маски запросов, регистр готовности, блок обслуживания обмена, блок формирования векторных признаков. Процессор, кроме того, содержит блок синхронизации, регистр кода операции, блок выдачи запросов, арифметико-логическое устройство мантисс, умножитель, арифметико-логическое устройство порядков, арифметико-логическое устройство коррекции, сдвигатели, коммутатор, формирователь параметра сдвига, группу элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, блоки обмена информацией, сверхоперативные запоминающие устройства, блок памяти микроопераций с соответствующими связями. 1 з.п. ф-лы, 10 ил., 2 табл.

В исходное состояние блок синхрони-,- ния запросов на вьщачу результата, зации приводится по входу 268 Пуск. поступающих с входа 243,, на опредеБлок 9 запросов (фиг.7) предназ- начен для промежуточного хранения запросов, поступающих из блока 13

40

маски запросов, и последующей их.передачи в регистр 14 готовности и блок 19 вьщачи запросов.

Запросы, поступающие на информационный вход 248, запоминаются в триггерах 328, с выходов этих тригге- 45 ров запросы поступают на выход 281. После прихода сигнала на синхровход 247 каждый запрос через свой элемент И (329, 330, 331) поступает на вход 225 и одновременно обнуляет соответ- JQ ствующий триггер, переводя его в состояние готовности принять очередной запрос.

Блок 8 приоритета (фиг.8) предназначен для выработки определенного .

порядка вьщачи запросов, поступающих из регистра 14 готовности, а также

-формирования сигнала, характеризую- . щего отсутствие запросов в этом

ленное число шагов в счетчике 313 предварительно с информационного входа 231 по сигналу разрешения записи с входа 239 заносится некоторая константа. При этом на выходе счетчика отсутствует сигнал разрешения прохождения запросов с входа 243. через элемент 315 на выход 249 Одновременно разрешается прохождение этих же запросов через элемент 314 при появлении синхросигнала с синхровхода 250. Запросы с выхода элемента 314 поступают на вычитаАкций вход 313 и уменьшают его содержимое до тех пор, пока он не обнулится и не заблокирует дальнейшее прохождение запросов в свой вход. При этом на выходе счетчика появится сигнал разрешения прохождения запросов через элемент 315 и на выход 249 по синхроимпульсам, поступающим на вход 250. Такой способ маскирования запросов устраняет ложное считывание результата на

ния запросов на вьщачу результата, поступающих с входа 243,, на определенное число шагов в счетчике 313 предварительно с информационного вхо да 231 по сигналу разрешения записи с входа 239 заносится некоторая константа. При этом на выходе счетчика отсутствует сигнал разрешения прохождения запросов с входа 243. через элемент 315 на выход 249 Одновременно разрешается прохождение этих же запросов через элемент 314 при появлении синхросигнала с синхровхода 250. Запросы с выхода элемента 314 поступают на вычитаАкций вход 313 и уменьшают его содержимое до тех пор, пока он не обнулится и не заблокирует дальнейшее прохождение запросов в свой вход. При этом на выходе счетчика появится сигнал разрешения прохождения запросов через элемент 315 и на выход 249 по синхроимпульсам, поступающим на вход 250. Такой способ маскирования запросов устраняет ложное считывание результата на

число шагов, равное глубине конвейера. На входы 240j и 240з с блока 10 памяти поступают сигналы признаков операции вектор - скаляр и скаляр - вектор соответственно. При наличии сигналов на входах 240, и 240 можно замаскировать запросы на очередные элементы операндов, поступающие с г.-- входов 243, и 2433, причем замаскиро ю вать запросы все, кроме первого. Действительно, если отсутствует сигнал переполнения счетчика длины вектора на входе 227, то по синхроимпульсу 250 первые запросы с входом 243 и

243

Ij через элементы 317, 322, 316

15

и

321 соответственно проходят на вь:код 249. Одновременно эти же запросы с выходов элементов 317 и 316 через элементы 324 и 323 соответственно проходят на установочные входы триггеров 237 и 236. При этом на их инверсных выходах появляются сигналы, запрещающие прохождение последующих запросов через элементы 322 и 321 соответственно на выход 249. Такое маскирование позволяет уменьшить длину микропрограмм операций типа векг-: г тор - скаляр и скаляр - вектор на

20

25

управляющего входа 236) заносит некоторая константа. При этом на де счетчика возникает сигнал,, зап щающий прохождение сигнала с вход 3262, стробируемого синхросигнало с входа 245,- через элемент 312 и новременно разрешающий прохождени синхросигналов с входа 244 через мент 311 на вычитающий вход счетч По этим синхросигналам происходит уменьшение содержимого счетчика д тех пор, пока он не обнулится и не заблокирует элемент 311. После обнуления до записи новой констан : на выходе счетчика стоит сигнал р решения прохождения сигнала запис с входа 236, через элемент 312 на выход 216.

Блок 15 обслуживания обме (фиг.9) предназначен для организ функционирования процессора с дво ми или одинарными операндами, а т же обслуживания запросов на получ ние очередных элементов операндов выдачу результата.

При поступлении на вход 259 еди ничных сигналов, говорящих о том.

величину, равную суммарному числу мик-30 будут обрабатьшаться операнды

рокоманд, необходимому для задания соответствующей маски на запросы одного из операндов данных операций,,

двойной длины, на выходе одного из элементов 339, 340 щги 341 в завис мости от того, какой иа трех сигнал в данный момент поступил на вход 287, появится единичный сигнал, по ступающий через элемент 346, на вх триггера 348. Одновременно этот си нал поступает на инверсный вход эл мента 343 и запрещает прохождение признака данньк с входа 284 через элемент 343 и 347 на выход 258. По скольку триг.гер 348 в начальный мо мент времени находится в нулевом с тоянии, то он также запрещает прох дение первого сигнала признака дан ных через элемент 342 и 347 иа вых 258. По заднему фронту первого сиг ла признака данных, поступающего н внрд С, триггер 348 перебрасываетс в единичное состояние и разрешает прохождение следующего признака да ных через элемент 342 и 347 иа вых 258. По заднему фронту второго с.иг нала признака данных триггер сбрас вается в нулевое состояние. Таким образом, если обрабатываются опера ды двойной дпины, на выходе 258 по является каждый второй сигиал приз ка данных, поступающий иа вход рег

блоке

13 маски 240.

запросов по сиг-

В

налу с входа 240, осуществляется также выбор одного из запросов, поступающих на входы 243 1 или 243j,по которому происходит счет в счетчике 6 длины вектора (другими словами, выбор счета длины вектора по первому или второму операнду). Если на входе 240 присутствует единый сигнал и нет переполнения счетчика длины вектора (отсутствует сигнал на входе 227), то запрос с входа 243,j через элементы 318, 325 и 320 проходит на выход 229. В противном случае на выход 229 через элементы 319, 325 и 320 проходит запрос, поступающий с выхода 2432.

Блок 11 маски признаков (фиг.5) предназначен для разрешения или запрещения записи признаков в регистр 12 векторных признаков. Для маскиров ния сигнала разрешения записи (выход 216) на определенное число шаго в счетчик 310 с информациоиного вход 232 (по сигналу разрешения записи

5

0

5

управляющего входа 236) заносится некоторая константа. При этом на выходе счетчика возникает сигнал,, запрещающий прохождение сигнала с входа 3262, стробируемого синхросигналом с входа 245,- через элемент 312 и одновременно разрешающий прохождение синхросигналов с входа 244 через элемент 311 на вычитающий вход счетчика. По этим синхросигналам происходит уменьшение содержимого счетчика до тех пор, пока он не обнулится и не заблокирует элемент 311. После обнуления до записи новой константы : на выходе счетчика стоит сигнал разрешения прохождения сигнала записи с входа 236, через элемент 312 на выход 216.

Блок 15 обслуживания обмена (фиг.9) предназначен для организации функционирования процессора с двойиы-. ми или одинарными операндами, а также обслуживания запросов на получе- ние очередных элементов операндов или выдачу результата.

При поступлении на вход 259 единичных сигналов, говорящих о том.

30 будут обрабатьшаться операнды

5

0

5

0

5

двойной длины, на выходе одного из элементов 339, 340 щги 341 в зависимости от того, какой иа трех сигналов в данный момент поступил на вход 287, появится единичный сигнал, поступающий через элемент 346, на вход триггера 348. Одновременно этот сигнал поступает на инверсный вход элемента 343 и запрещает прохождение признака данньк с входа 284 через элемент 343 и 347 на выход 258. Поскольку триг.гер 348 в начальный момент времени находится в нулевом состоянии, то он также запрещает прохождение первого сигнала признака данных через элемент 342 и 347 иа выход 258. По заднему фронту первого сигнала признака данных, поступающего на внрд С, триггер 348 перебрасывается в единичное состояние и разрешает прохождение следующего признака данных через элемент 342 и 347 иа выход 258. По заднему фронту второго с.иг нала признака данных триггер сбрасывается в нулевое состояние. Таким образом, если обрабатываются операнды двойной дпины, на выходе 258 появляется каждый второй сигиал признака данных, поступающий иа вход регист

j7{

pa готовности Если же для какого-либо сигнала запроса отсутствует соответствующий сигнал признака операнда двойной длины (цепь 259) , то на выходе элемента 346 будет присутство-. вать нулевой сигнал, разрешающий прохождение первого сигнала признака данных с входа 284 через элементы

343и 347 на выход 258.

Блок 15 обеспечивает также формирование сигналов чтения (ввдачи) результата или записи (приема) операндов. Если на вход элемента 341 по шине 287 поступает единичный сигнал, соответствующий запросу на вьщачу результата, то на выходе элемента

344по сигналу признака данных с входа 284 возникает сигнал чтения, по-

ступающий на выход 286. Если же на входе элемента 241 отсутствует единичный сигнал, то по сигналам признака данных на выходе элемента

345возникают сигналы записи соответствующего операнда, поступающие

на вход 285. Кроме того, по сигналам формируемым на выходах 362 и 363, обеспечивается одновременная запись информации во все блоки 32 обмена с шины данных либо раздельная запись сначала в блоки 32-1 и 32-2, а затем в 32-3 и 32-4. Это позволяет обраба- тьшать слова двойного формата.

Таким образом, благодаря блоку 15 обслуживания обмена обеспечивается управление операндами и результатом как одинарной, так и двойной длины, а также обеспечивается возможность работы устройства с магистралью обмена данными для многопроцессорных устройств и уменьшение разрядности кода признаков управления запросами.

Рассмотрим работу на примерах сложения и умножения чисел с плавающей

запятой, поскольку они являются ОСГ

новными для остальш 1х операций.

Сложение. По шине данных в блоки 32 обмена информацией записываются последовательно числа, подлежащие обработке. При этом мантиссы чисел поступают соответственно в блоки 32-1 и 32-2, а порядки - в блоки 32-3 н 32-4. По сигналам из микрокоманды данные последовательно переписьюают7 ся в соответствующие блоки 31-3,...- ...,31-6. Цикл операции сложения чисел с плавающей запятой состоит из нескольких этапов.

7

18

На первом этапе выполняется обра- , ботка порядков, т.е. сравнение порядков. Порядки чисел с блоков 31-6 и 31-5 по входам-вькодам 105 и 110 поступают на входы-выходы соответственно 106 н 109 арифметико-логического . устройства 22 порядков, которое настраивается микропрограммно на операцию вычитания. Результат операции в виде разности исходны порядков поступает с входов-выходов 109 с временной задержкой на вход 108 формирователя 29 параметра сдвига. В зависимости от знака разности порядков включается в работу сдвигатель 24 либо 25 и формируется код параметра сдвига вправо мантиссы числа с меньшим порядком.

На втором этапе вьтолняется. сдвиг мантиссы числа с меньшим порядком вправо, т.е. операция выравнивания порядков. Направление сдвига задается микрокомандой. На этом же этапе осуществляется пересылка наибольтп шего порядка в один из регистров блока 31-5. Пересылка осущес.твляет- ся через арифметико-логическое устройство 22 порядков, которое настраивается на передачу кода либо с входов-выходов 109, либо с входов- выходов 106 о Если наибольший порядок содержится в регистре блока 31-6, то он через арифметико-логическое устройство 22 по входам-выходам 105, 109 и 110 поступает в заданный регистр блока 31-5. В случае наибольшего порядка в блоке 31-5 передача его осуществляется по входамгвыхо- дам 110, 109 и обратно 109, 110.

5

0

5

Третий этап представляет собой сложение мантисс. Для этого мантиссы двух операндов читаются с блоков 31-3 и 31-4 по входам-выходам 88 и 92. на соответствующие входы-вьпсоды 89 и 94 арифметико-логического устройства 20, которое микропрограммно настроено на операцию сложения. Результат операции с временной задержкой поступает по входам-выходам 89 на заданный регистр блока 31-1 по входам- выходам 91. Одновременно с этим выб-: ранный наибольший порядок, хранящийся в блоке 31-5, читается с него по входам-выходам ПО на выбранный регистр блока 31-2 по входам-выходам 107. Сформированные признаки с выходов 193 арифметико-логического устройства 20 поступают на вход J94 в регистр состояния.

Четвертый этап представляет собой операцию поиска левой единицы (нуля) мантиссы результата. Полученный код параметра нормализации мантиссы и он же код параметра коррекции порядка результата с выхода четвертого сдвигателя 27 поступает в выбранный регистр блока 31-2 по входам- выходам 1 25.

Пятый этап - это этап нормализации мантиссы результата: и коррекции порядка. Мантисса результата с выбранного регистра бло.ка 31-1 по входам- выходам 127 поступает в третий сдвига- тель 26 по входам-выходам 126, который в зависимости от значения признака переполнения мантиссы результата микропрограммно настраивается на направление сдвига. Параметр сдвига поступает в третий сдвигатель 26 на Ш1ну 122 с входов-выходов 125 блока

31-2 ина шину 1 84 срегистра признаков ) 25 единицы (нуля) и чтения на шину данзначения признака переполнения. Результат сдвига с временной задержкой по- ступает с входов-выходов 126 блока 26 нормализации на входы-выходы 127 блока 31-1, Одновременно с этим выполняется коррекция порядка результата. При этом код порядка читается с выбранного .регистра блока 31-2 на входы- выходы 111 и далее принимается арифметико-логическим устройством 23 коррек- с таются по входам-выходам 88 и 92 Блоции по входамг выходам 112, а код параметра коррекции читается с другого выбранного регистра блока 34-2 по входам-выходам 125 на входы-выходы 1 24 арифметико-логического устройства 23 40 коррекции. В зависимостиг от значения признака переполнения мантиссы арифметико-логическое устройство 23 коррекции микропрограммно.настраивается либо на операцию сложения, либо на 45 операцию вычитания. Результат обработки читается по входам- выходам 112 на выбраннгзш регистр блока 31-2 по входам-выходам 111.

На этом же этапе может быть осу- jQ ществлена коррекщш порядка результата в зависимости от значения признаков Мр, ПРП Р О (см. табл.).

Шестой этап состоит в пересыпке результата обработки с выбранных 55 гистров блоков 31-1 и 31-2 соответственно для мантиссы к порядка в выбранный регистр блоков 31-3, 31-5 либо 31-4, 31-6.

ков 31-3 и 31-4 на входьь-выходы 90 и 93 умножителя 21, а порядки - по входам-выходам 105 и ПО блоков 31-5 и 31-6 на входы-выходы 1Q6 и 109 арифметико-логического устройства 22 по--: рядков. Осуществляется операция умногс жения мантисс в умножителе 21 и обработка порядков в арифметико-логическом устройстве 22.

Результат умножения на следующем этапе записывается в блок 31-1 по входам-выходам 87, признаки, сформированные при умножении, записываются в регистр состояния, а результат обработки порядков - в блок 31-2.

Следующий этап - операция поиска левой едии.И) (нуля) с записью кода параметра коррекции в блок 31-2 по входам-выходам 125. Для исходных нормализованных чисел код параметра коррекции равен 1, Следующие этапы такие же, как и для операции сло.жения чисел с плавающей запятой: нормализация, пересыпка и чтение на шину

0

5

0

При необходимости может быть реализован седьмой этап, когда результат обработки читается на шину данных.

Конвейерный режим/сложения чисел с плавающей запятой поясняется табл.2, в которой развернутый цикл обработки одной пары чисел сжат в несколько этапов, в которых осуществляется обработка других пар чисел.

Так, на первом этапе или в первой микрокоманде выполняются пересыпка числа А из блоков 32-1 и 32-3 в блоки 31-3 и 31-5, операция сдвига (выравнивание порядка) и операция нормализации. Вторая микрокоманда включает операцию пересылки числа В из блоков 32-2 и 32-4 в блоки 31-4 и 31-6, операцию суммирования мантисс и пересылку результата обработки с блоков и 31-2 соответственно в блоки 31-3 (31-4) и 31-5 (31-6). Третья микрокоманда состоит из операций сравнения порядков, поиска левой

ных. Таким образом, в каждой микрокоманде одновременно обрабатываются три пары чисел, т.е. глубина конвейера для данной операции равна трем. Умножение. Операция умножения начинается так. же, как и сложение, засылкой; поочередно операндов А и В соответственно в блоки 31-3, 31-5 и : 31-4,i31-6. Далее мантиссы чисел чиков 31-3 и 31-4 на входьь-выходы 90 и 93 умножителя 21, а порядки - по входам-выходам 105 и ПО блоков 31-5 и 31-6 на входы-выходы 1Q6 и 109 арифметико-логического устройства 22 по--: рядков. Осуществляется операция умногс жения мантисс в умножителе 21 и обработка порядков в арифметико-логическом устройстве 22.

Результат умножения на следующем этапе записывается в блок 31-1 по входам-выходам 87, признаки, сформированные при умножении, записываются в регистр состояния, а результат обработки порядков - в блок 31-2.

Следующий этап - операция поиска левой едии.И) (нуля) с записью кода параметра коррекции в блок 31-2 по входам-выходам 125. Для исходных нормализованных чисел код параметра коррекции равен 1, Следующие этапы такие же, как и для операции сло.жения чисел с плавающей запятой: нормализация, пересыпка и чтение на шину

данных. При этом входы-выходы и функциональные блоки, задействованные на этих этапах, аналогичны и при сложеН1Ш.

в табл.3 показана свертка цикла микропрограммы умножения для конвейерной реализации.

Реализация других операций или микропрограмм основьшается на этих двух микропрограммах.

Формула изобретения

JO

раций процессора подключен к информа- 25 га третьего сдвигателя соединен с циоиному входу регистра кода операций, выход которого соединен с входом кода команды устройства микропрограммного управления, первая группа разрядов входа логических условий которого подключена к соответствующим разрядам выхода кода признаков результата арифметико-логического устройства мантисс, выход состояний логических условий устройства микропрограммного управления соединен с адресным входом коммутатора, с первого по шестой выходы блока синхронизации - соответственно с первого по шестой входами синхронизации устройства микропрограммного управления, вход запуска процессора подключен к входу запуска блока синхронизации, седьмой выход которого соединен с входами

третьим выходом состоянии логическ условий устройства микропрограммно управления, выход признака отсутст вия запросов которого подключен к входу управления режимом блока син ронизации, отличающийся тем, что, с целью повьш1ения произв дительности, он дополнительно соде жит с первого по десятый блоки обм ас на информацией, с первого по четве тый сверхоперативные запот нающие устройства, четвертьп сдвигатель, блок элементов ИСКЛЮЧАЩЕЕ ИЛИ, фо мирователь параметра сдвига, блок памяти микроопераций и блок выдачи запросов, причем первый вход блока элементов ИСКЛЮЧА1-ЭДЕЕ ИЛИ сое.динен с четвертым выходом состояний логи ческих условий устройства микропро

40

записи арифметико-логических устройствдз граммного управления, выход запросов мантисс, коррекции и порядков, с вхо- которого соединен с информационным дами записи с первого по третий входом блока выдачи запросов, синхро- сдвигателей входами чтения арифметико-логических устройств мантисс,

50

коррекции и порядков и с восьмым выходом блока синхронизации, вход начальной установки устройства микропрограммного управления подключен к входам начальной установки регистра кода операций и процессора, входы кода операции и входы управления третьим состоянием арифметико-логических устройств мантисс и порядков, входы управления третьим состоя55

вход которого соединен с вторым выходом блока синхронизации, вход разрешения выдачи и выход запросов, блока выдачи запросов подключены соответственно к выходу признака отсутствия . запросов устройства микропрограммного управления и к вькоду запросов процессора входы адреса с первого по шестой блоков обмена информацией соединены соответственно с десятого по пятнадцатый выходами ко- да микроопераций первой группы уст

нием с первого по третий сдвигателей и коммутатора соединены соответственно с первого по восьмой выходами кода микроопераций первой группы устройства микропрограммного управления, первый и второй выходы кода микроопераций второй группы которого подключены к входам настройки арифметико-логических устройств соответственно мантисс и порядков, вход управления третьим состоянием и вход кода операции арифметико-логического ства коррекции соединены соответственно с девятым выходом кода микроопераций первой группы и с вторым выходом состояний логических условий устройства микропрограммного управления, вторая и третья группы разрядов

первого входа логических условий

которого подключены к выходам кода признаков результата арифметико-логических устройств соответственно коррекции и порядков, вход типа.сдви-

га третьего сдвигателя соединен с

третьим выходом состоянии логических условий устройства микропрограммного управления, выход признака отсутствия запросов которого подключен к входу управления режимом блока синхронизации, отличающийся тем, что, с целью повьш1ения производительности, он дополнительно содержит с первого по десятый блоки обме- на информацией, с первого по четвертый сверхоперативные запот нающие устройства, четвертьп сдвигатель, блок элементов ИСКЛЮЧАЩЕЕ ИЛИ, формирователь параметра сдвига, блок памяти микроопераций и блок выдачи запросов, причем первый вход блока элементов ИСКЛЮЧА1-ЭДЕЕ ИЛИ сое.динен с четвертым выходом состояний логических условий устройства микропро

граммного управления, выход запросов которого соединен с информационным входом блока выдачи запросов, синхро-

вход которого соединен с вторым выходом блока синхронизации, вход разрешения выдачи и выход запросов, блока выдачи запросов подключены соответственно к выходу признака отсутствия . запросов устройства микропрограммного управления и к вькоду запросов процессора входы адреса с первого по шестой блоков обмена информацией соединены соответственно с десятого по пятнадцатый выходами ко- да микроопераций первой группы уст

ройства микропрограммного управления, с шестнадцатого по двадцать первый выходы кода микроопераций цервой группы которого соединены с выходами управления третьим состоянием соответственно с первого по шестой блоков обмена информагдией, пер- в|ые информационные входы и выходы Первого и третьего блоков обмена информацией подключены к информацион- р|ому входу-выходу арифметико-логи- iecKoro устройства мантисс и входу rjepBoro операнда умножителя,- выход Е|езультата которого соединен с BTopiJM 1 нформационным входом-выходом пер- 4ого блока обмена информацией, тре- 1|ий информационный вход-выход кото- ijoro соединен с информационным вхо- Дом-выходом третьего сдвигателя и iJTopbiM входом блока элементов ИС1ШО- НАЮЩЕЕ или, выход которого соединен d информационным входом-выходом четвертого сдвигателя, вход управления Третьим состоянием, вход записи и дход чтения которого подключены соот- етственно к двадцать второму выходу йода микроопераций первой группы устройства микропрограммного управ- и к седьмому и восьмому выхойам блока синхронизации, девятый йыход которого соединен с первыми фходами чтения с первого по шестой блоков обмена информацией, входы за- йиси первого и второго блоков обмена информацией соединены с десятым выходом блока синхронизации, одиннадца Т ый выход которого соединен с вторы;- ми входами чтения первого и второго блоков обмена информацией, четвертый информационный вход-выход первого блка обмена информацией подключен к второму информационному входу-выходу третьего и к первому информационному Входу-выходу четвертого блоков Обме на информацией, информационный вход арифметико-логического устройства матисс соединен с входом второго операнда умножителя и подключен к второму информационному входу-выходу чет-

вертого блока обмена информацией, тртий и четвертый информационные входы выходы которого соединены соответстг- венно с информационным,- входом-выхог дом второго сдвигателя и первым информационным входом-выходом восьмого блока обмена информацией, второй .Шг1- формационный вход-выход которого соединен с первым информационным вхо

0

0

5

с JQ

30

35

40

45

55

дом-выходом седьмого блока.обмена информацией и подключен к входу задания кода дпины вектора устройства микропрограммного управления, двадцать третий выход кода микрооперации первой группы которого соединен с первыми входами записи с третьего по шестой блоков обмена информацией, вторые входы записи которых подключены к двенадцатому выходу блока синхронизации и первому входу разрешения блока памяти микроопераций, входы чтения третьего, пятого и шестого блоков обмена информацией подключены к двадцать четвертому выходу кода микроопераций первой группы устройства микропрограммного управления первый выход синхронизации запросов которого соединен с входами записи с седьмого по десятый блоков обмена информацией, входы чтения которых и четвертого блока обмена информагщей соединены с вторым выходом синхронизации запросов устройства микропрограммного управления, двадцать пятый выход кода микроопераций первой группы которого подключен к входу типа сдвига формирователя параметра сдвига, выход типа сдвига которого подключен к входам типа сдвига первого, второго и четвертого сдвигателей, выход параметра сдвига четвертого сдвигателя подключен к входу параметра сдвига третьего сдвигателя, информационному входу арифметико-логическогочустройства коррекции и к первому информационному входу-выходу второго -блока обмена информацией, второй информационный вход-выход которого подключен к информационному входу-выходу арифметико-логического устройства коррекции и к вькоду коммутатора, третий информационный вход-выход второго сдвигателя подключен к первым информационным входам-выходам пятого н шестого блоков обмена информацией, четвертый информационный вход-выход второго блока обмена информацией подключен к информационному входу формирователя параметра сдвига, второму информационному входу-выходу пятого блока обмена информацией и к информационному входу-выходу арифметико-логического устройства порядков, информационный вход и выход кода признаков результата которого соединены соответственно с вторым информационным входом-выходом шестого блока обмена

10

15

информацией и входом признака параметра сдвига формирователя параметра сдвига, выкод параметра сдвига которого соединен с входами параметра сдвига первого и второго сдвигателей, информационный вход-выход первого сдвигателя соединен с третьим информационным входом-выходом третьего блока обмена информацией, четвертый информационный вход-выход которого соединен с информационным входом-выходом первого сверхоперативного запоминающего устройства,, с вто- рьм информационным входом-выходом седьмого блока обмена информацией и первым информационным входом-выходом девятого блока обмена информацией, первые входы разрешения обмена седьмого и восьмого блоков обмена инфорг- мацией соединены с третьим выходом кода микроопераций первой группы устройства микропрограммного управления, восьмой выход кода микроопераций первой группы которого соединен с входами разрешения обмена первого и второго сверхоперативных запоминающих устройств, входы адреса которых и третьего и четвертого сверхоперативных запоминающих устройств соединены с двадцать щестым выходом кода микроопераций первой группы микропрограммного устройства управления, шестнадцатый выход кода микроопераций первой группы которого соединен с входами разрешения обмена третьего и четвертого сверхоперативных запоминающих устройств, входы чтения которых и первого и второго сверхоперативных запоминающих устройств соединены с первым выходом блока памяти микроопераций, второй выход которого соединен с входом записи с первого по четвертый сверхопе-

го

25

30

40

обмена которого и десятого блока обмена информацией соединены с восемнадцатым выходом кода микроопераций первой группы устройства микропрогра много управления, пятый выход кода микроопераций первой группы которого соецинен с вторьми входами разрешения обмена седьмого и восьмого блоко обмена информацией, первые входы записи которых и девятого и десятого блоков обмена информацией подключены к третьему выходу блока памяти микроопераций, четвертый выход которого соединен с первыми входами чте ния с седьмого по десятый блоков об-, мена информацией, первые входы режима обмена которых соединены с пятым выходом блока памяти микроопераций, шестой выход которого соединен с вторыми входами записи с седьмого по десятый блоков обмена информацией, вторые входы чтения которых соет динены с седьмым выходом блока памяти микроопераций, восьмой выход которого соединен с третьими входами записи с седьмого по десятый блоков обмена информацией, третьи входы чтения которых соединены с девятым выходом блока памяти микроопераций, второй вход разрешения и адресный вход которого соединены соответственно с восьмым выходом блока синхронизации и двадцать седьмым выходом кода микроопераций первой группы устройства микропрограммного управления, девятнадцатый выход кода микроопераций первой группы которого соединен с вторыми входами разрешения обмена девятого и десятого блоков обмена информацией, второй информационный вход-вьжод десятого блока об- мена информацией соединен с информационным входом-выходом четвертого

50

ративных запоминающих устройств, ин- 45 сверхоперативного запоминающего уст- формационный вход-выход второго сверхоперативного запоминающего устройства соединен с первым информационным входом-выходом восьмого блока обмена информацией и первым 1ш- формационным входом-вьпсодом десятого блока обмена информа;цией, информационный вход-выход третьего сверхопе-.

ративного запоминающего устройства .

соединен с третьим информационным Bxovj подключены к информационному входу- дом-выходом пятого блока обмена ин- . выходу процессора, вход признака нали- формацией и вторым информационным чия данных которого подключен к вхо- входом-выходом девятого блока обмена ду признака данных устройства микро- информацией, первые входы разрешения программного управления, третий выройства и с третьим информационным входом-выходом шестого блока обмена информацией, двадцать восьмой выход кода микроопераций первой группы устройства микропрограммного управления подключен к третьим информационным входам-выходам с седьмого по десятый блоков обмена информацией, четвертые информационные входы-выходы которых

10

5

о

5

0

0

обмена которого и десятого блока обмена информацией соединены с восемнадцатым выходом кода микроопераций первой группы устройства микропрограммного управления, пятый выход кода микроопераций первой группы которого соецинен с вторьми входами разрешения обмена седьмого и восьмого блоков обмена информацией, первые входы записи которых и девятого и десятого блоков обмена информацией подключены к третьему выходу блока памяти микроопераций, четвертый выход которого соединен с первыми входами чте ния с седьмого по десятый блоков об-, мена информацией, первые входы режима обмена которых соединены с пятым выходом блока памяти микроопераций, шестой выход которого соединен с вторыми входами записи с седьмого по десятый блоков обмена информацией, вторые входы чтения которых соет динены с седьмым выходом блока памяти микроопераций, восьмой выход которого соединен с третьими входами записи с седьмого по десятый блоков обмена информацией, третьи входы чтения которых соединены с девятым выходом блока памяти микроопераций, второй вход разрешения и адресный вход которого соединены соответственно с восьмым выходом блока синхронизации и двадцать седьмым выходом кода микроопераций первой группы устройства микропрограммного управления, девятнадцатый выход кода микроопераций первой группы которого соединен с вторыми входами разрешения обмена девятого и десятого блоков обмена информацией, второй информационный вход-вьжод десятого блока об- мена информацией соединен с информационным входом-выходом четвертого

сверхоперативного запоминающего уст-

.

подключены к информационному входу- выходу процессора, вход признака нали- чия данных которого подключен к вхо- ду признака данных устройства микро- программного управления, третий выройства и с третьим информационным входом-выходом шестого блока обмена информацией, двадцать восьмой выход кода микроопераций первой группы устройства микропрограммного управления подключен к третьим информационным входам-выходам с седьмого по десятый блоков обмена информацией, четвертые информационные входы-выходы которых

код синхронизации запросов которого соединен с вторым входом режима обме- На седьмого и восьмого блоков обмена информацией, вторые входы режима об- мена дерятого и десятого блоков обмена информацией соединены с четвертым выходом синхронизации запросов устройства микропрограммного управяешш ервый и второй информационные входы оммуЕатора подключены к первому и Ьторому входам константы процессора.

: 2.Процессор по п.1, о т л и - Дающийся тем, что.форьшрова- {гель параметра сдвига содержит блок памяти, регистр и арифметико-логичес сий блок, причем информационный вход формирователя соединен с младшими разрядами одноименного входа регист- ра, первый выход которого соединен

М

°Т ° I J

О 1

1

О

Выравнивание Нормализация

порядков Сложение Пересылка

мантисс

Поиск левойЧтение

единицы

ТаблицаЗ

Запись резуль- Пересылка

тата Поиск левой Чтение

еди1- ицы Нормализация

со старшими разрядами адресного входа блока памяти, младшие разряды адресного входа которого соединены с входом типа сдвига формирователя, вход признака параметра сдвига которого соединен со старшим/разрядом информационного входа регистра, первый выход кода микроопераций блока памяти соединен с выходом типа сдвига формирователя, выход параметра сдвига которого соединен с выходом результата арифметико-логического блока, вход кода операции которого соединен с вторым выходом кода микроопераций блока памяти, второй выход регистра соединен с входом первого операнда арифметико-логического блока, вход второго операнда которого соединен с шиной логического нуля процессора.

Т а б л и ц а 1 ;

(иин

Таблица 2

т 179

S Jg i7 Ig y .

1 5 fs JTzfe b Иб|7Ь|7;г аЬ I

--- - ggyj

Фиг.З

Фиг. 2

th9 f29

Фаг.д

(риб.9

w т

753 13

737

т w

135

te.;

| Electronics, 1983, v.56, № 18, p | |||

| Способ получения камфоры | 1921 |

|

SU119A1 |

| Микропроцессорные средства и системы, 1986, № 5, с.3-5. | |||

Авторы

Даты

1990-09-23—Публикация

1987-07-14—Подача