Jf 19

to

о: со

ел

Изобретение относится к вычислительной технике и может быть использовано при построении обрабатывающих блоков из микропроцессорных секций.

Цель изобретения повьоцение. производительности.

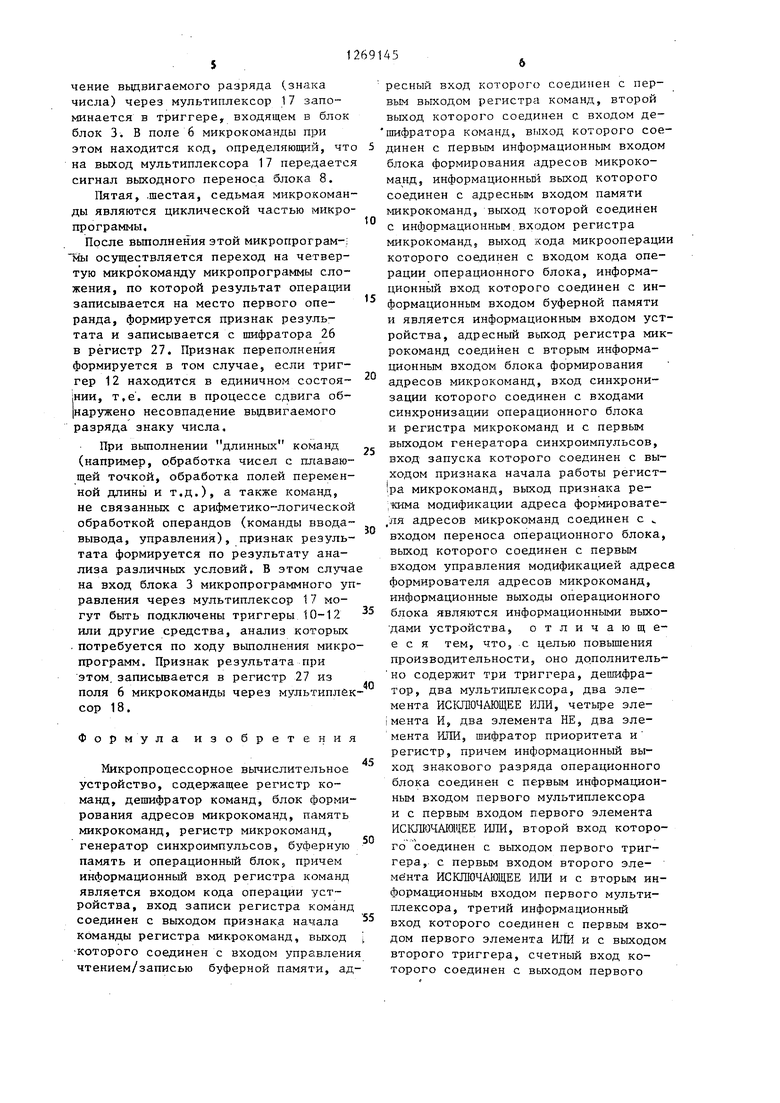

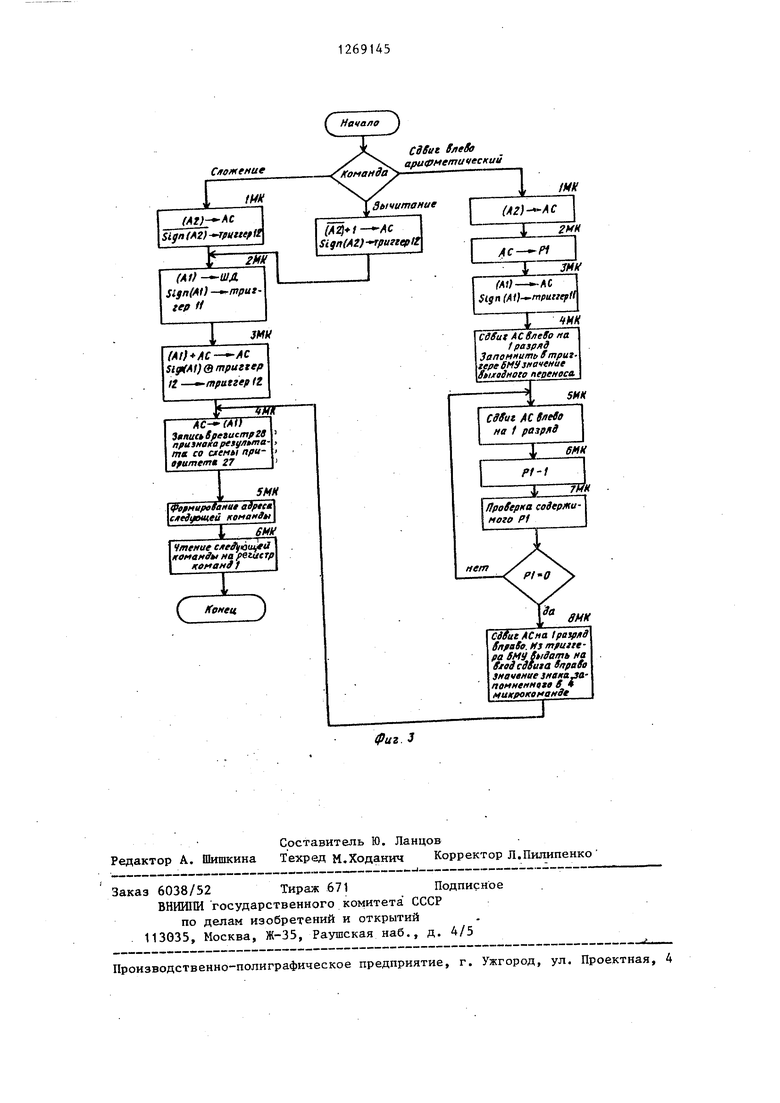

На фиг.1 представленаструктурная схема устройства; на фиг о 2 - формат команды; на фиг.З - графические схемы алгоритмов выполнения команд.

Микропроцессорное вычислительное устройство содержит регистр 1 команд дешифратор 2 команд, блок 3 формирования адресов микрокоманд, память 4 микрокоманд, регистр 5 микрокоманд с выходами 6 признака типа микрооперахщи, буферную память 7, операционный блок 8, генератор 9 синхроимпульсов, первый 10, третий 11 и второй 12 триггеры, элементы НЕ 13 и 14, первый ; 15 и второй 16 элементы ИСКЛЮЧАЮЩЕЕ ШТИ, первый 17 и ВТОРОЙ 18 мультиплексоры, дешифратор 19, второй 20, четвертый 21, первый 22 и третий 23 элементы И, второй 24 и первый 25 элементы ИЛИ, шифратор 26 приоритета, реги.стр 27, вход 28 Кода операции, информационные выходы 29, выход 30 знакового разряда и информационный вход 31,

Работа устройства описывается, на .примере выполнения команд сложения, вычитания, сдвига арифметического влево в формате регистр-регистр, (формат команды приведен на фиг. 2), поле КОП определяет код операции, поле А1 - адрес (номер) регистра, содержащего первый операнд, поле А2 адрес (номер) регистра, содержащего второй операнд,

В операциях сдвига содержимое регистра, определяемое полем А2 команды, зддает количество двоичньгх разрядов, на которое должен быть сдёинут первый операнд.

На фиг.З и в описании приняты следующие обозначения: А1, А2 - поля команды, определяющие адреса первого и второго операндов соответственно, (А1), (А2) - операнды по адресам А1 и А2 соответственно, АС - аккумулятор матрицы центральных процессорных элементов;: SignN - знак числа знак передачи содержимого, ®сложение по модулю два; МК - микрокоманда, ШД - шина данных,

Вьтолнение команд считьшания-вычитания в форме регистр-регистр

занимает 6 МК: 1 МК - передача второго операнда в аккумулятор операционного блока; 2 МК - чтение первого операнда из буферной памяти; 3 МК чтение первого операнда из буферной памяти и выполнение требуемой операции в операционном блоке; 4 МК передача результата на место первого операнда; 5 МК - формирование адреса следующей команды, 6 МК - выборка сл.ед,ую1цей команды на регистр команд

При вьшоЛнении команды сложение устройство работает следующим образом.

Перед вьшолнением команды триггеры 10-12 находятся в нулевом состоянии. Первой микрокомандой операнд, выбранный из буферной памяти 7 по адресу, определяемому полем А2 команды, передается в аккумулятор операционного блока 8, В поле 6 данной микрокоманды находится код, указывающий, что необходимо з-аписать. инверсное значение знакового разряда в триггер 11, Этот код с первого выхода поля 6 регистра 5 поступает на дешифратор 19, который вырабатывает микрооперацию на третьем выходе

SignN®триггер 11- триггер 11.

По этой- микрооперации инверсное значение Sign (А2) через элементы НЕ 14, И 21 и ИЛИ 24 поступает на счетньй вход триггера 11, которьй либо остается в нулевом состоянии (при Sign (А2) 1), либо устанавли вается в единичное состояние (при Jsign (А2) 0).

Таким образом, после выполнения первой микрокоманды в триггере 11 хранится инверсное- значение знака вторЪго операнда.

По второй микрокоманде производится чтение первого операнда, определяемого полем; А1 команды, В поле 6 микрокоманды находится код, по которому дешифратор 19 вырабатывает на первом выходе микрооперацию

Sign А1-t триггер 11.

Таким образом, после второй микро команды состояние триггера 10 указывает на знак первого операнда.

Третьей микрокомандой операнд, выбранньй .из буферной памяти 7 по адресу, определяемому полем А1 команды, складывается с операндом, хра нящимся в аккумуляторе операционного блока результат помещается в аккумулятор, В поле 6 этой микрокоманды находится кстд, по которому дешифратор 19 вы рабатывает микрооперацию на соответствующем выходе SignN®триггер 11-w триггер 11. По микрооперации на соответствую щем выходе дешифратора 19 значение Sign (А1) поступает через элементы И 20 и ИЛИ 24 на счетный вход тригг ра 1 1 , которьй либо остается в преж нем состоянии (при Sign (А1) 0), пибо принимает противоположное значение (при Sign (А1) 1). Таким образом, после третьей микрокоманды состояние триггера 11 указывает на соответствие знаков оп рандов (нулевое состояние триггера 11 указывает на то, что знаки операн дов разные, единичное - что знаки операндов одинаковые), а состояние триггера 10 соответствует знаку первого операнда. По четвертой микрокоманде содер жимое аккумулятора операционного бло ка 8 передается в буферную память 7 по адресу, определяемому полем А1 команды. По информации на выходе 29 и состоянию триггеров 10 и 11 про исходит формирование признака резуль тата по следующим правилам. Если триггер 11 находится в единичном состоянии, т.е. операнды имеют одинаковый знак, возможно переполнение, которое определяется по соответствию знака результата знаку операнда, значение которого сохранено в триггере 10. Это соответствие определяется элементом ИСКЛЮЧАЮЩЕЕ ИЛИ 15, который при несовпадении сигналов на его входах формирует на выходе сигнал единичного уровня, пос тупающий через элементы И 23 и ИЛИ 2 на первый вход шифратора 26 приорите та.- Одновременно элементом НЕ 13 фор мируется сигнал, соответствующий нулевой информации на выходе 29. Этот сигнал подается на второй вхбд шифратора 26 приоритета. На третий и четвертый входы шифратора 26 приоритета поступает инвертированное и пря мое значение знакового разряда. При поступлении сигналов на входы шифратора 26 приоритета на его выходах формируются сигналы в следующе порядке: Переполнение - на первом, Нуль результата - на втором, Результат больше нуля - на четвердом и Результат меньше нуля - на третьем выходах. По четвертой микрокоманде в поле 6 записан код, определяющий формирование следующих микроопераций: передача на выход мультиплексора 18 информации с его второй группы входов, т.е. с шифратора 26 приоритета; запись информации в регистр 27. Таким образом, после вьшолнения четвертой микрокоманды результат one- . рации записан на место исходного (первого) операнда в буферную память 7, а в регистре 27 находится признак результата операции. По пятой микрокоманде формируется адрес следующей- команды, а по шес1той - чтение команды из основной- памяти (не показана) на регистр 1 команд и сброс триггеров 10-12. Блок 3 формирует начальный адрес MiKponpограммы, соответствующий вновь принятому коду операции, и цикл работы устройства повторяется. Выполнение вычитания отличается от выполнения сложения только первой микрокомандой. Б операции вычитания по первой микрокоманде значение второго операнда, определяемого полем А2 команды, передается в аккумулятор блока 8 в дополнительном коде, а в триггер 11 через элементы И 20 и ИЛИ 24 записывается прямое значение знакового разряда. Остальные микрокоманды являются oбщIiми с микропрограммой сложения. При выполнении арифметического ; сдвига влево первой и второй микрокомандами содержимое регистра, опрецеляемое полем А2 команды (количестj3O двоичных разрядов, на которое необходимо сдвинуть первый операнд), передается из буферной памяти 7 через арифметико-логический узел и аккумулятор операционного блока в один из регистров регистровой памяти операционного блока 8. По третьей микрокоманде содержимое, определяемое полем А1 команды (сдвигаемое число), передается из буферной памяти 7 в аккумулятор блока 8, при этом значение знака числа запоминается в триггере 10 (аналогично микропрограмме сложения). По четвертой микрокоманде содержимое аккумулятора блока 8 через арифметико-логический узел блока 8 сдвигается на один разряд влево, значение вьщвигаемого разряда (знака числа) через мультиплексор 17 запоминается в триггере, входящем в блок блок 3. В поле 6 микрокоманды при этом находится код, определяющий, чт на выход мультиплексора 17 передаетс сигнал выходного переноса блока 8. Пятая, .шестая, седьмая микрокоман ды являются циклической частью микро программы. После выполнения этой микропрограм-: мы осуществляется переход на четвертую микрокоманду микропрограммы сложения, по которой результат операции записывается на место первого операнда, формируется признак результата и записывается с шифратора 26 в регистр 27. Признак переполнения формируется в том случае, если триггер 12 находится в единичном состояНИИ, т,е. если в процессе сдвига обнаружено несовпадение выдвигаемого разряда знаку числа. При выполнении длинных команд (например, обработка чисел с ш-савающей точкой, обработка полей переменной длины и т.д.), а также команд, не связанных с арифметико-логической обработкой операндов (команды вводавывода, управления), признак результата формируется по результату анализа различных условий. В этом случа на вход блока 3 микропрограммного уп равления через мультиплексор 17 могут быть подключены триггеры 10-12 или другие средства, анализ которых . потребуется по коду вьшолнения микро программ. Признак результата при этом.записьшается в регистр 27 из 6 микрокоманды через мультиплек сор 18. Формула изобретения Микропроцессорное вычислительное устройство, содержащее регистр команд, дешифратор команд, блок формирования адресов микрокоманд, память микрокоманд, регистр микрокоманд, генератор синхроимпульсов, буферную память и операционный блок5 причем информационный вход регистра команд является входом кода операции устройства, вход записи регистра команд соединен с выходом признака начала команды регистра микрокоманд, выход которого соединен с входом управлени чтением/записью буферной памяти, ад ресный вход которого соединен с первым выходом регистра команд, второй выход которого соединен с входом дешифратора команд, выход которого соединен с первым информационным входом блока формирования адресов микрокоманд, информационньв выход которого соединен с адресным входом памяти микрокоманд, выход которой соединен с информационным,входом регистра микрокоманд, выход кода микрооперации которого сое;: инен с входом кода операции операционного блока, информационный вход которого соединен с информационным входом буферной памяти и является информационным входом устройства, адресный выход регистра микрокоманд соединен с вторым информационным входом блока формирования адресов микрокоманд, вход синхронизации которого соединен с входами синхронизации операционного блока и регистра микрокоманд и с первым выходом генератора синхроимпульсов, вход запуска которого соединен с выходом признака начала работы регист ра микрокоманд, выход признака ре,кнма модификации адреса формировате,ля адресов микрокоманд соединен с входом переноса операционного блока, выход которого соединен с первым входом управления модификацией адреса формирователя адресов микрокоманд, информационные выходы операционного блока являются информационными выходами устройства, отличающееся тем, что, с целью повышения производительности, оно дрполнительно содержит три триггера, дешифратор, два мультиплексора, два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, четыре элемента И, два элемента НЕ, два элемента ИЛИ, шифратор приоритета и регистр, причем информационный выход знакового разряда операционного блока соединен с первым информационным входом первого мультиплексора и с первым входом первого элемента ИСКШЗЧАЮЩЕЕ ШШ, второй вход которого соединен с выходом первого триггера, с первым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и с вторым информационным входом первого мультиплексора, третий информационный вход которого соединен с первым входом первого элемента ШШ и с выходом второго триггера, счетный вход которого соединен с выходом первого

элемента И, псфвый и второй вхоДы которого соединены соответственно с выходом первого элемента ИСКЛЮЧАЮЩЕЕ ШШ и с первым выходом дешифратора, второй выход которого соединен с входом синхронизации первого триггера, информационный вход которого соединен с выходом знакового разряда оперативной памяти, с первым входом второго элемента И, с входом пер вого и второго элементов НЕ, с первым входом шифратора приоритета и с вторым входом второго элемента ИСКЛЮЧАИЦЕЕ ИЛИ, выход которого соединен с первым входом третьего элемента И, второй вход которого соединен с выходом третьего триггера и с четвертым информационным входЬм первого мультиплексора, выход которого соединен с вторым входом управления модификацией адреса формирователя адресов микрокоманд, управляющий вход мультиплексора соединен с первы выходом признака типа микрооперации регистра микрокоманд, второй выход признака типа микрооперации которого соединен с входом дешифратора, третий выход которого соединен с вторым входом второго элемента И, выход которого соединен с первым входом второго элемента ИЖ, второй вход

которого соединен с выходом четвертого элемента И, первый вход которого соединен с четвертым выходом деишфратора, пятый выход которого соединен с входом записи регистра, информационный вход которого соединен с выходом второго мультиплексора, управляющий вход которого соединен с третьим выходом признака типа микрооперации регистра микрокоманд, четвертый выход признака, типа микрооперации которого соединен с первым информационным входом второго мультипл ексора, второй информационный вход которого соединен с выходом шифратора приоритета второй вход которого соединен с-выходом первого элемента НЕ и с вторым входом четвертого элемента И, третий и че1твертый входы шифратора приоритета соединены.соответственно с выходом второго элемента НЕ и с выходом первого элемента ИЛИ, второй вход которого соединен с выходо третьего элемента И, выход второго элемента ИЛИ соединен.с входом синхронизации третьего триггера, счетный вход которого соединен с вторым выходом генератора синхроимпульсов, выход регистра является выходом знакового разряда устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммный процессор | 1980 |

|

SU868766A1 |

| Процессор с совмещением операций | 1982 |

|

SU1138805A1 |

| Перестраиваемый микропрограммный процессор | 1981 |

|

SU983713A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1124299A1 |

| Микропроцессор | 1982 |

|

SU1119021A1 |

| Процессор для обработки массивов данных | 1982 |

|

SU1381532A1 |

| Микропроцессор | 1984 |

|

SU1179363A1 |

| Микропрограммный процессор | 1981 |

|

SU980095A1 |

| Вычислительное устройство | 1987 |

|

SU1430962A1 |

| Устройство для обмена данными между электронно-вычислительной машиной и абонентами | 1985 |

|

SU1277125A1 |

Изобретение относится к вычислительной технике и может быть .использовано при построении обрабатывающих блоков из микропроцессорных секций. Цель изобретения - повышение производительности. Устройство содержит регистр команд 1, дешифра- i тор 2 команд, блок 3 формирования адресов микрокоманд, буферную память 7, операционный блок 8, генератор 9 синхроимпульсов, три триггера 10, 11,12, два элемента НЕ 13, 14, два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 15,16,. два мультиплексора 17,18, дешифратор 19, четыре элемента И 20-23, два элемента ИЛИ 24,25, шифратор 26 приоритета, регистр 27. Указанная совокупность признаков позволяет СЛ достигнуть цели изобретения. 3 ил.

Фаг. 2

( Начаяо j

CiioMfHUf

Sign(A2)

i

2Hk

(A1) Sifnf n - mputtfpff

JWW

(At) AC- AC SI f(A))® триггер li - mpatieii ff

ЦЧМК

AC-(At)

Звяиа Soetuemfie nfusHOKa peiy/lunaтя CO сиеми npuafumeme Z7

3V4

(, Sign (Al)- rnpuaeftl

i

4«

CdSut AC влево на

I разряд

Запомнить f триггере бМУ значение StiJiaiHOto перенеси.

±

C9Sut АС taeSo на t разряЗ

6МН

ipefHufetaMat aopte c eiifomeu команЗн

i

tf

Чтение яоманЗы на p tatrp кон and j

I

f Конец )

Проверка содержимого Р1

Cifue АС на t разряд SfifaSo. Ifj триггера ему Видать на SfodcdSuta вправо значение знака апомненн9Ю в микроконанЗе

| Микропроцессор | 1978 |

|

SU746532A1 |

| Прибор для нагревания перетягиваемых бандажей подвижного состава | 1917 |

|

SU15A1 |

| Береэенко А.И., Корягин Л.И., Назарьян А.Р | |||

| Микропроцессорные комплекты повьппенного быстродействия.М.: Радио и связь, 1981, с.85, pHCjji9 а. | |||

Авторы

Даты

1986-11-07—Публикация

1982-12-23—Подача