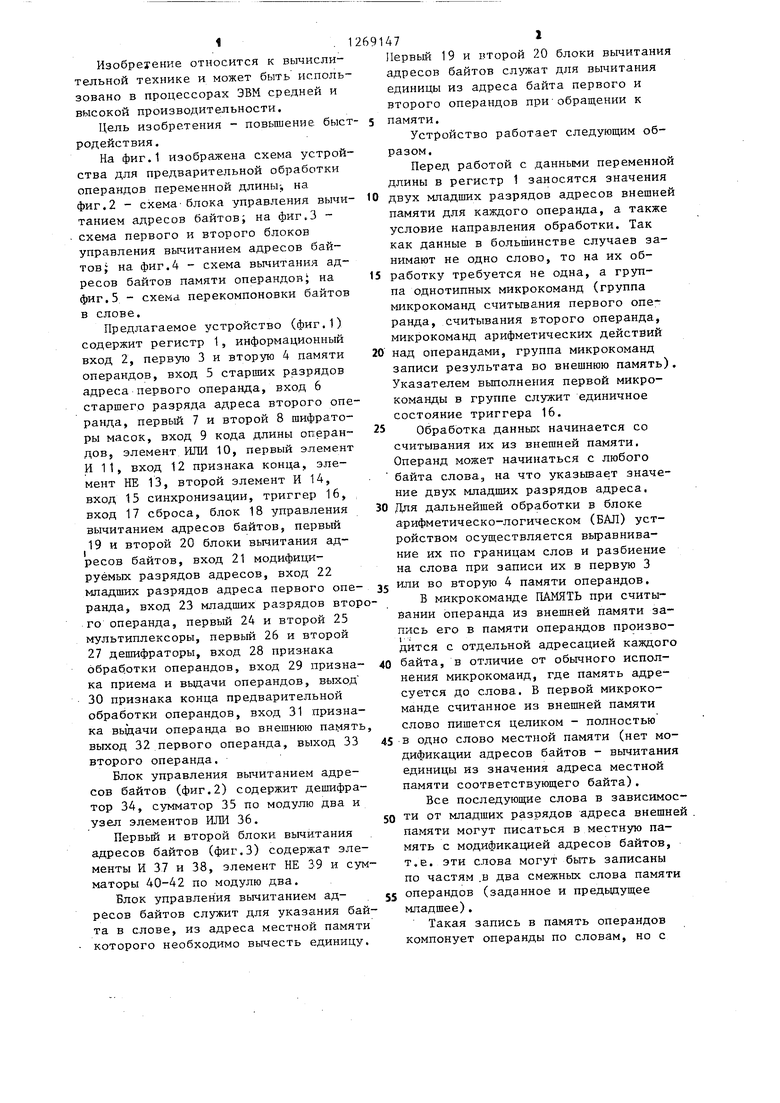

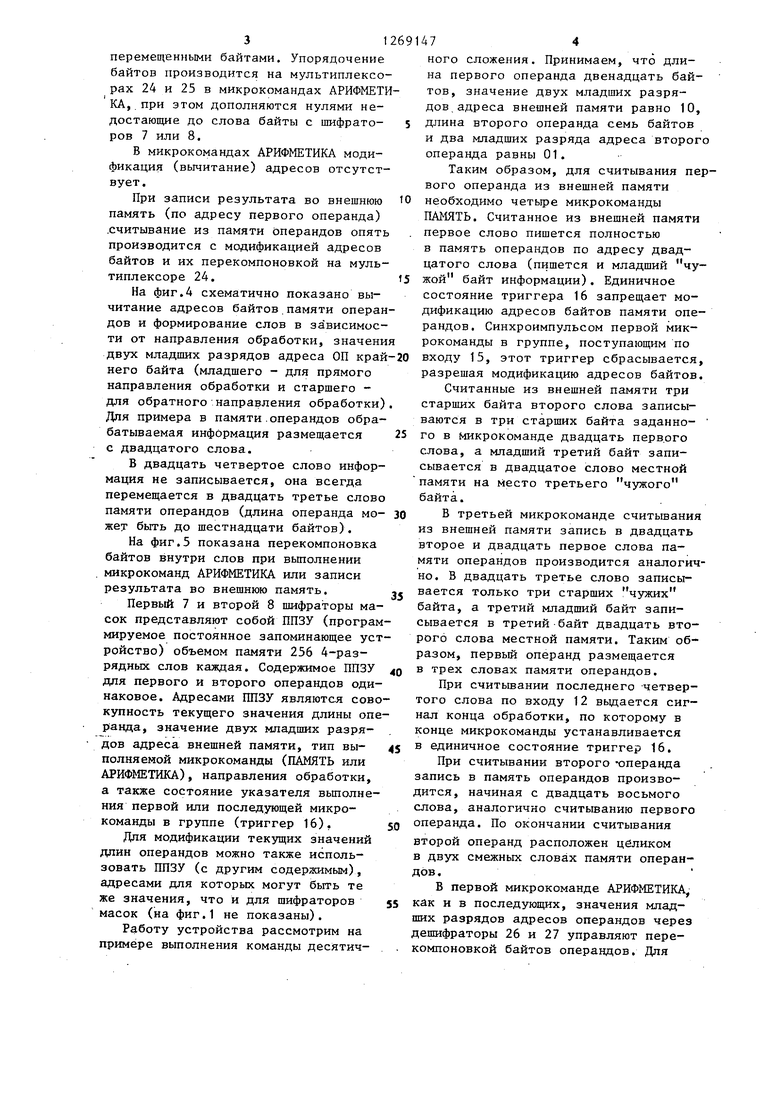

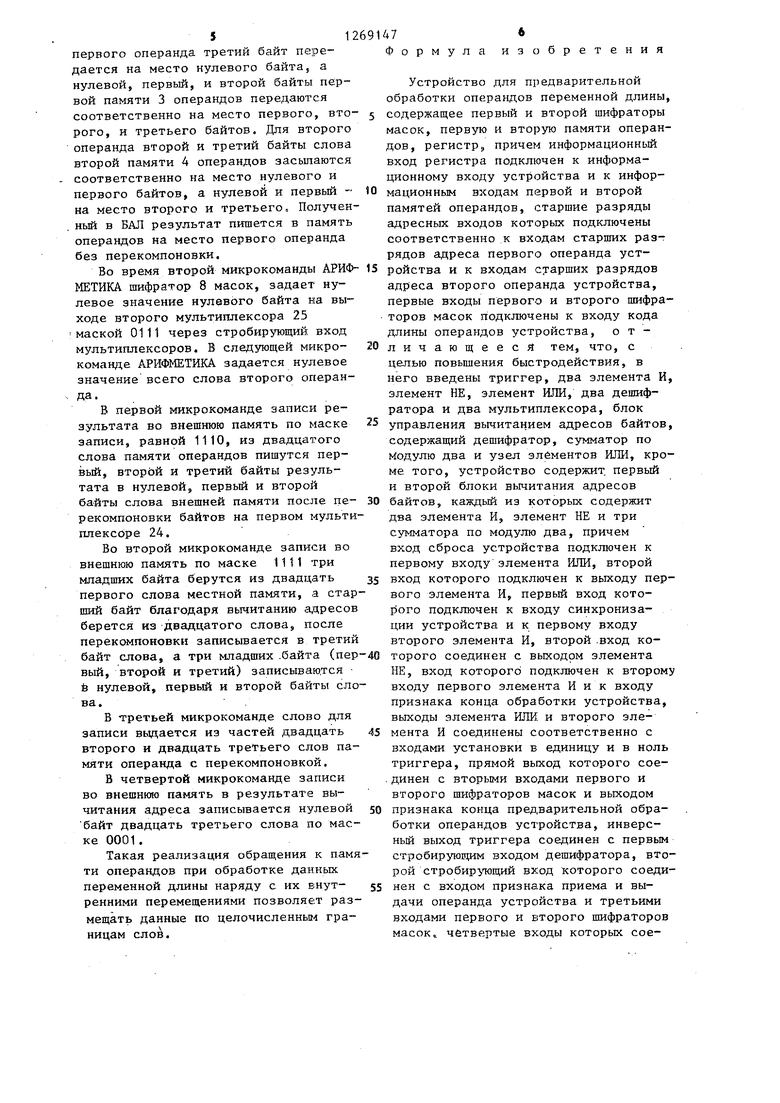

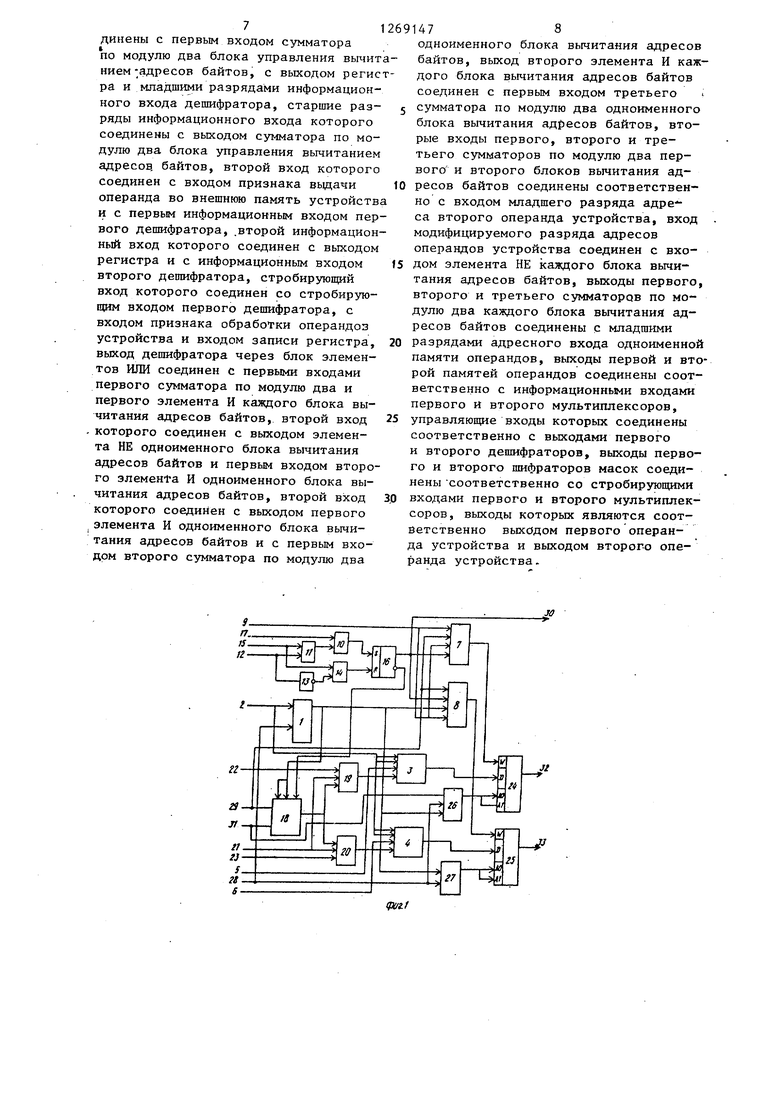

Изобретение относится к вычислительной технике и может быть исполь зовано в процессорах ЭВМ средней и высокой производительности. Цель изобретения - повышение, быс родействия. На фиг.1 изображена схема устрой ства для предварительной обработки операндов переменной длины-, на фиг.2 - схема-блока управления вычи танием адресов байтов; на фиг.З схема первого и второго блоков управления вычитанием адресов байтов; на фиг.4 - схема вычитания адресов байтов памяти операндов; на фиг.5 - схема перекомпоновки байтов в слове. Предлагаемое устройство (фиг.1) содержит регистр 1, информационный вход 2, первую 3 и вторую 4 памяти операндов, вход 5 старших разрядов адреса первого операнда, вход 6 старшего разряда адреса второго опе ранда, первый 7 и второй 8 шифраторы масок, вход 9 кода длины операндов, элемент, ИЛИ 10, первый элемент И 11, вход 12 признака конца, элемент НЕ 13, второй элемент И 14, вход 15 синхронизации, триггер 16, вход 17 сброса, блок 18 управления вычитанием адресов байтов, первый 19 и второй 20 блоки вычитания адресов байтов, вход 21 модифицируемых разрядов адресов, вход 22 младших разрядов адреса первого опе ранда, вход 23 младших разрядов вто го операнда, первый 24 и второй 25 мультиплексоры, первый 26 и второй 27 дешифраторы, вход 28 признака обработки операндов, вход 29 призна ка приема и выдачи операндов, выход 30 признака конца предварительной обработки операндов, вход 31 призна ка выдачи операнда во внешнюю памят выход 32 первого операнда, выход 33 второго операнда. Блок управления вычитанием адресов байтов (фиг.2) содержит дешифра тор 34, сумматор 35 по модулю два и узел элементов ИЛИ 36. Первый и второй блоки вычитания адресов байтов (фиг.З) содержат эле менты И 37 и 38, элемент НЕ 39 и су маторы 40-42 по модулю два. Блок управления вычитанием адресов байтов служит для указания ба та в слове, из адреса местной памят которого необходимо вычесть единицу Первый 19 и второй 20 блоки вычитания адресов байтов служат для вычитания единицы из адреса байта первого и второго операндов приобращении к памяти. Устройство работает следующим образом. Перед работой с данными переменной длины в регистр 1 заносятся значения двух младших разрядов адресов внешней памяти для каждого операнда, а также условие направления обработки. Так как данные в большинстве случаев занимают не одно слово, то на их обработку требуется не одна, а группа однотипных микрокоманд (группа микрокоманд считьгаания первого операнда, считывания второго операнда, микрокоманд арифметических действий над операндами, группа микрокоманд записи результата во внешнюю память). Указателем вьшолнения первой микрокоманды в группе служит единичное состояние триггера 16. Обработка данньпс начинается со считывания ик из внешней памяти. Операнд может начинаться с любого байта слова, на что указьшает значение двух младших разрядов адреса. Для дальнейшей обработки в блоке арифметическо-логическом (БАЛ) устройством осуществляется вьфавнивание их по границам слов и разбиение на слова при записи их в первую 3 или во вторую 4 памяти операндов. В микрокоманде ПАМЯТЬ при считывании операнда из внешней памяти запись его в памяти операндов производится с отдельной адресацией каждого байта, в отличие от обычного исполнения микрокоманд, где память адресуется до слова. Б первой микрокоманде считанное из внешней памяти слово пишется целиком - полностью в одно слово местной памяти (нет модификации адресов байтов - вычитания единицы из значения адреса местной памяти соответствующего байта). Все последующие слова в зависимости от младших разрядов адреса внешней памяти могут писаться в местную память с модификацией адресов байтов, т.е. эти слова могут быть записаны по частям .в два смежных слова памяти операндов (заданное и предыдущее младшее). Такая запись в память операндов компонует операнды по словам, но с

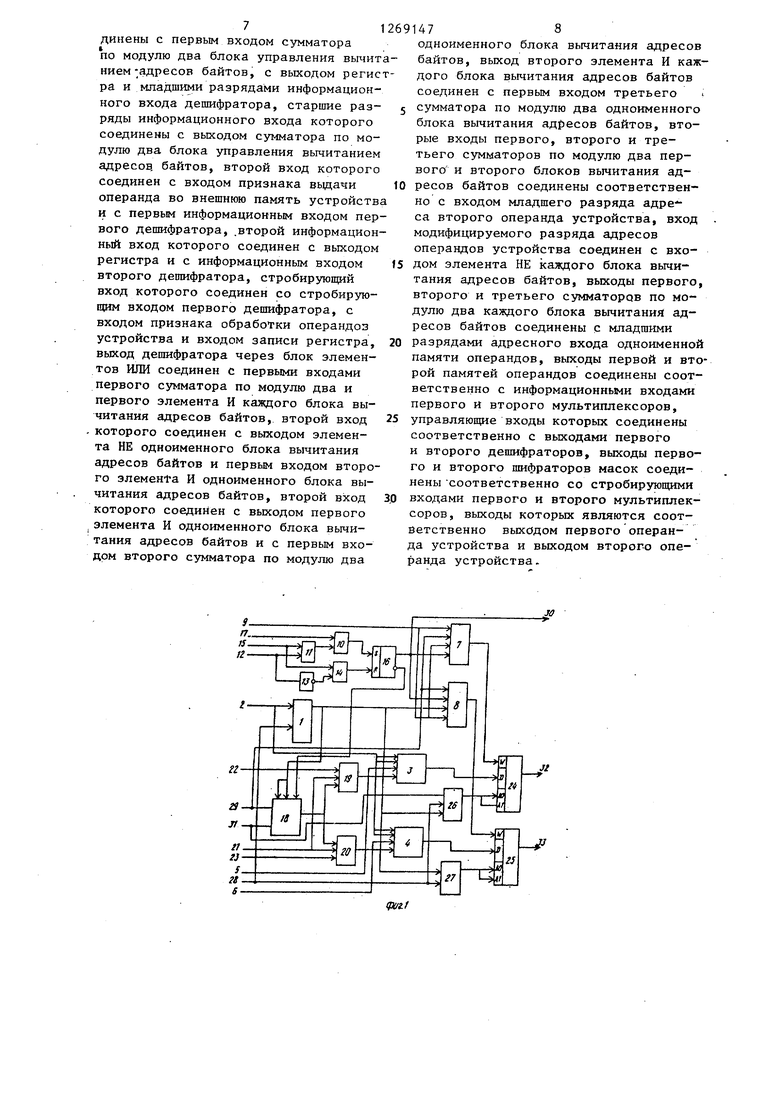

перемещенными байтами. Упорядочение байтов производится на мультиплексорах 24 и 25 в микрокомандах АРИФМЕТИКА, . при этом дополняются нулями недостающие до слова байты с шифраторов 7 или 8.

В микрокомандах АРИФМЕТИКА модификация (вычитание) адресов отсутствует.

При записи результата во внешнюю память (по адресу первого операнда) .считывание из памяти операндов опять производится с модификацией адресов байтов и их перекомпоновкой на мультиплексоре 24,

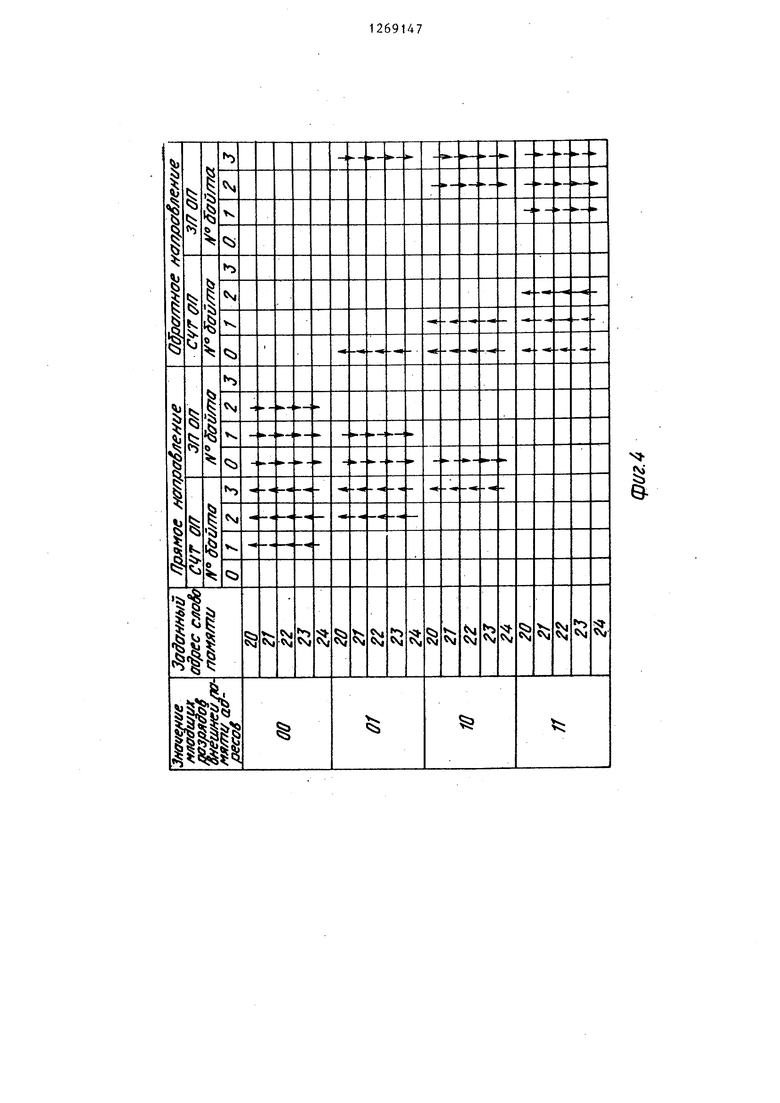

На фиг.4 схематично показано вычитание адресов байтов.памяти операндов и формирование слов в зависимости от направления обработки, значени двух младших разрядов адреса ОП край него байта (младшего - для прямого направления обработки и старшего для обратного направления обработки) Для примера в памяти .операндов обрабатываемая информация размещается с двадцатого слова.

В двадцать четвертое слово информация не записывается, она всегда перемещается в двадцать третье слово памяти операндов (длина операнда может быть до шестнадцати байтов).

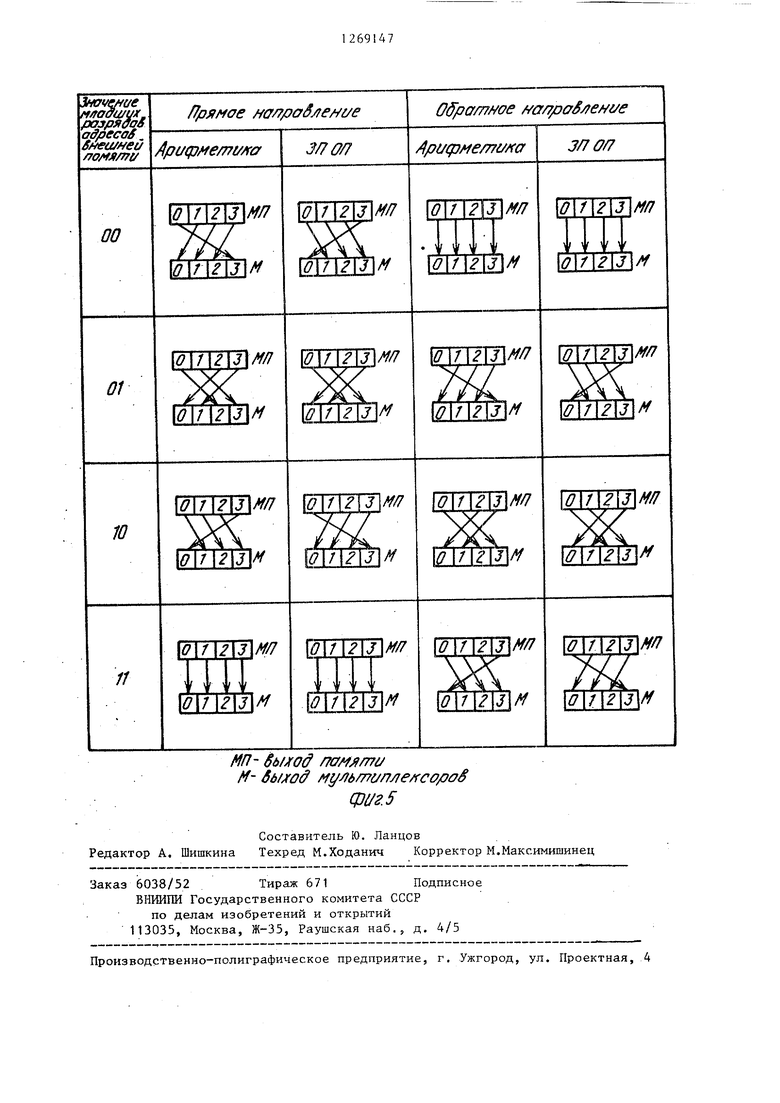

На фиг.5 показана перекомпоновка байтов внутри слов при вьшолнении микрокоманд АРИФМЕТИКА или записи результата во внешнюю память.

Первый 7 и второй 8 шифраторы масок представляют собой ППЗУ (программируемое постоянное запоминающее устройство) объемом памяти 256 4-разрядных слов каждая. Содержимое ППЗУ для первого и второго операндов одинаковое. Адресами ППЗУ являются совокупность текущего значения длины операнда, значение двух младших разрядов адреса внешней памяти, тип выполняемой микрокоманды (ПАМЯТЬ или АРИФМЕТИКА), направления обработки, а также состояние указателя вьшолнения первой или последующей микрокоманды в группе (триггер 16),

Для модификации текущих значений длин операндов можно также использовать ППЗУ (с другим содержимым), адресами для которых могут быть те же значения, что и для шифраторов масок (на фиг.1 не показаны).

Работу устройства рассмотрим на примере выполнения команды десятичного сложения. Принимаем, что длина первого операнда двенадцать байтов, значение двух младших разрядов адреса внешней памяти равно 10, длина второго операнда семь байтов и два младших разряда адреса второг операнда равны 01.

Таким образом, для считывания певого операнда из внешней памяти необходимо четыре микрокоманды ПАМЯТЬ. Считанное из внешней памяти первое слово пишется полностью в память операндов по адресу двадцатого слова (пишется и младший чужой байт информации). Единичное состояние триггера 16 запрещает модификацию адресов байтов памяти операндов. Синхроимпульсом первой микрокоманды в группе, поступающим по входу 15, этот триггер сбрасывается разрешая модификацию адресов байтов

Считанные из внешней памяти три старших байта второго слова записываются в три старших байта заданного в Микрокоманде двадцать перв.ого слова, а младший третий байт записывается в двадцатое слово местной памяти на место третьего чужого байта.

В третьей микрокоманде считывания из внешней памяти запись в двадцать второе и двадцать первое слова памяти операндов производится аналогично. В двадцать третье слово записывается только три старших чужих байта, а третий младший байт записывается в третий-байт двадцать второго слова местной памяти. Таким образом, первый операнд размещается в трех словах памяти операндов.

При считьшании последнего -четвертого слова по входу 12 вьщается сигнал конца обработки, по которому в конце микрокоманды устанавливается в единичное состояние триггер 16.

При считывании второго -операнда запись в память операндов производится, начиная с двадцать восьмого слова, аналогично считьшанию первого операнда. По окончании считывания

второй операнд расположен целиком в двух смежных словах памяти операндов.

В первой микрокоманде АРИФМЕТИКА, как и в последующих, значения младших разрядов адресов операндов через дешифраторы 26 и 27 управляют перекомпоновкой байтов операндов. Для

512

первого операнда третий байт передается на место нулевого байта, а нулевой, первый, и второй байты первой памяти 3 операндов передаются соответственно на место первого, второго, и третьего байтов. Для второго операнда второй и третий байты слова второй памяти 4 операндов засыпаются соответственно на место нулевого и первого байтов, а нулевой и первый на место второго и третьего. Полученный в БАЛ результат пишется в память операндов на место первого операнда без перекомпоновки.

Во время второй микрокоманды АРИФМЕТИКА шифратор 8 масок, задает нулевое эначение нулевого байта на выходе второго мультиплексора 25 маской 0111 через стробирующий вход мультиплексоров. Б следующей микрокоманде АРИФМЕТИКА задается нулевое значение всего слова второго операнда.

В первой микрокоманде записи результата во внешнюю память по маске записи, равной 1110, из двадцатого слова памяти операндов пишутся первый, второй и третий байты результата в нулевой, первый и второй байты слова внешней памяти после перекомпоновки байтов на первом мультиплексоре 24,

Во второй микрокоманде записи во внешнюю память по маске 1111 три младших байта берутся из двадцать первого слова местной памяти, а старший байт благодаря вычитанию а,чресов берется из двадцатого слова, после перекомпоновки записывается в третий байт слова, а три младших .байта (пер вый, второй и третий) записываются Ё нулевой, первый и второй байты слова.

В третьей микрокоманде слово д,ля записи выдается из частей двадцать второго и двадцать третьего слов памяти операнда с перекомпоновкой.

В четвертой микрокоманде записи во внешнюю память в результате вычитания адреса записывается нулевой байт двадцать третьего слова по маске 0001.

Такая реализация обращения к памяти операндов при обработке дан;ных переменной длины наряду с их внутренними перемещениями позволяет размещать данные по целочисленным границам слов.

476

Формула изобретения

Устройство для предварительной обработки операндов переменной длины содержащее первый и второй шифраторы масок, первую и вторую памяти операндов, регистр;, причем информационный вход регистра подключен к информационному входу устройства и к информационным входам первой и второй памятей операндов, старшие разряды адресных входов которых подключены соответственно к входам старших разрядов адреса первого операнда устройства и к входам старших разрядов адреса второго операнда устройства, первые входы первого и второго шифраторов масок подключены к входу кода длины операндов устройства, отличающееся тем, что, с целью повышения быстродействия, в него введены триггер, два элемента И элемент НЕ, элемент ИЛИ, два дешифратора и два мультиплексора, блок управления вычитанием адресов байтов содержащий дешифратор, сумматор по Модулю два и узел элементов ИЖ1, кроме того, устройство содержит, первый и второй блоки вычитания адресов байтов, каждый из которых содержит два элемента И, элемент НЕ и три сумматора по модулю два, причем вход сброса устройства подключен к первому входу элемента ИЛИ, второй вход которого подключен к вьпсоду первого элемента И, первый вход которого подключен к входу синхронизации устройства и к первому входу второго элемента И, второй .вход которого соединен с выходом элемента НЕ, вход которого подключен к втором входу первого элемента И и к входу признака конца обработки устройства, выходы элемента ИЛИ и второго элемента И соединены соответственно с входами установки в единицу и в ноль триггера, прямой выход которого соединен с вторыми входами первого и второго шифраторов масок и выходом признака конца предварительной обработки операндов устройства, инверсный выход триггера соединен с первым стробирующим входом дешифратора, второй стробир тощий вход которого соединен с входом признака приема и выдачи операнда устройства и третьими входами первого и второго шифраторов масок„ четвертые входы которых соединены с первым входом сумматора по модулю два блока управления вычит нием адресов байтов, с выходом регис ра и младшими разрядами информационного входа дешифратора, старшие разряды информационного входа которого соединены с выходом сумматора по модулю два блока управления вычитанием адресов, байтов, второй вход которого соединен с входом признака вьщачи операнда во внешнюю память устройств и с первым информационным входом пер вого дешифратора, .второй информацион ный вход которого соединен с выходом регистра и с информационным входом второго дешифратора, стробирующий вход которого соединен со стробируюпрш входом первого дешифратора, с входом признака обработки операндов устройства и входом записи регистра, выход дешифратора через блок элементов ИЛИ соединен с первыми входами первого сумматора по модулю два и первого элемента И каждого блока вычитания адресов байтов, второй вход которого соединен с выходом элемента НЕ одноименного блока вычитания адресов байтов и первым входом второ го злeмeнta И одноименного блока вычитания адресов байтов, второй вход которого соединен с выходом первого элемента И одноименного блока вычитания адресов байтов и с первым входом второго сумматора по модулю два 147S одноименного блока вычитания адресов байтов, выход второго элемента И каждого блока вычитания адресов байтов соединен с первым входом третьего i сумматора по модулю два одноименного блока вычитания ад)есов байтов, вторые входы первого, второго и третьего сумматоров по модулю два первого и второго блоков вычитания адресов байтов соединены соответственно с входом младшего разряда адреса второго операнда устройства, вход модифицируемого разряда адресов операндов устройства соединен с входом элемента НЕ каждого блока вьяитания адресов байтов, выходы первого, второго и третьего сумматоров по модулю два каждого блока вычитания адресов байтов соединены с младшими разрядами адресного входа одноименной памяти операндов, выходы первой и второй памятей операндов соединены соответственно с информационньми входами первого и второго мультиплексоров, управляющие входы которых соединены соответственно с выходами первого и второго дешифраторов, выходы первого и второго шифраторов масок соединены соответственно со стробирующими входами первого и второго мультиплексоров, выходы которых являются соответственно выходом первого операнда устройства и выходом второго операнда устройства.

физ.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммный процессор | 1980 |

|

SU868766A1 |

| Процессор | 1984 |

|

SU1247884A1 |

| Процессор с совмещением операций | 1982 |

|

SU1138805A1 |

| Устройство для обработки данных переменной длины | 1986 |

|

SU1675897A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Мультиплексный канал | 1984 |

|

SU1167613A1 |

| Устройство для сопряжения периферийных устройств с процессором и оперативной памятью | 1983 |

|

SU1156084A1 |

| Микропроцессор | 1979 |

|

SU894715A1 |

| Селекторный канал | 1983 |

|

SU1103218A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1264172A1 |

Изобретение относится к области вычислительной техники и может бьггь использовано в процессорах ЭВМ средней и высокой производительности. Цель изобретения - повьппение быстродействия. Устройство содержит регистр, блок управлений вычитанием адресов байтов, два блока вычитания адресов байтов, две памяти операндов, два дешифратора, два мультиплексора, два шифратора масок, два элемента И, элемент ИЛИ, триггер и элемент НЕ. Указанная цель достигается реализаi цией возможности размещения операндов различной длительности по целочисленW ным границам слой. 5 ил.

фи,3

x

| Устройство для обработки информационных полей переменной длины | 1978 |

|

SU767769A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для обработки данных переменной длины | 1976 |

|

SU648984A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-11-07—Публикация

1984-04-06—Подача