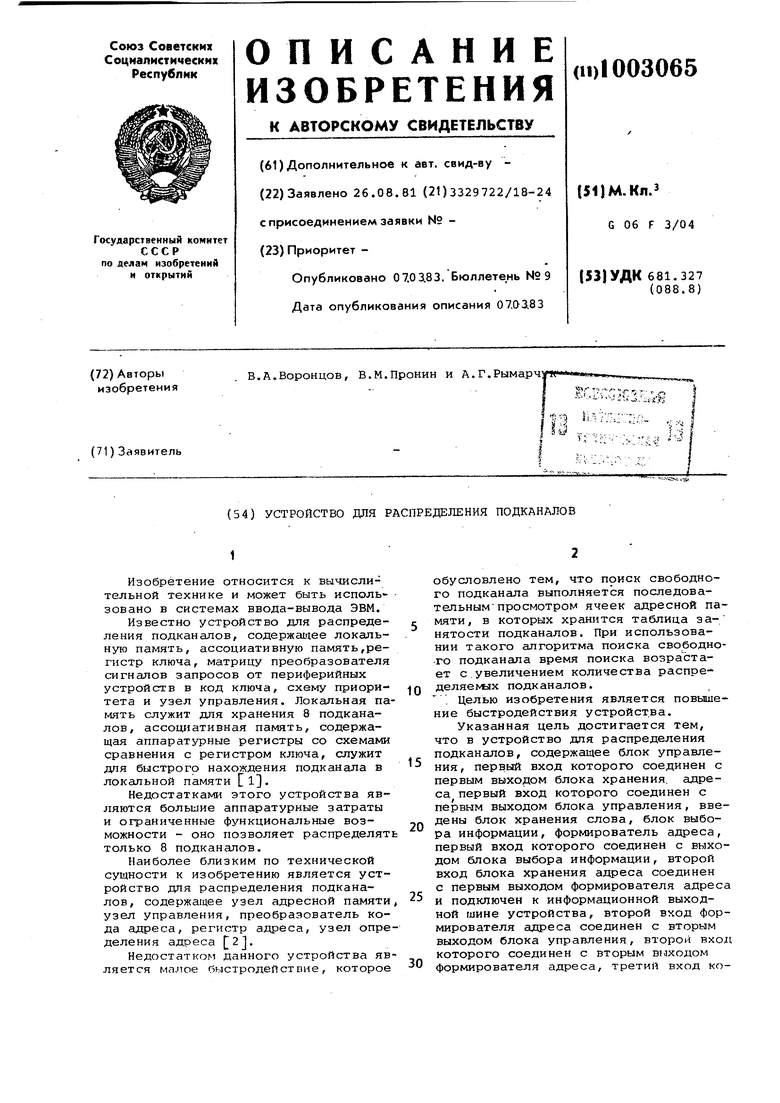

Изобретение относится к вычислительной технике и может быть исполь- зёвано в системах ввода-вывода ЭВМ.

Известно устройство для распределения подканалов, содержаь1ее локальную память, ассоциативную память,регистр ключа, матрицу преобразователя сигналов запросов от периферийных устройств в код ключа, схему приоритета и узел управления. Локальная служит для хранения В подканалов, ассоциативная память, содержащая аппаратурные регистры со схемами сравнения с регистром ключа, служит для быстрого нахождения подкангша в локальной памяти CllНедостатками этого устройства являются большие аппаратурные затраты и ограниченные функциональные возможности - оно позволяет распределять только 8 подканалов.

Наиболее близким по технической сущности к изобретению является устройство для распределения подканалов, содержащее узел адресной памяти, узел управления, преобразователь кода адреса, регистр адреса, узел определения адреса 2.

Недостатком данного устройства является малое быстродействие, которое

обусловлено тем, что покск свободного подканала выполняется последовательным просмотром ячеек адресной памяти, в которых хранится таблица занятости подканалов. При использовании такого алгоритма поиска свободного подканала время поиска возрастает с увеличением количества распре деляемлх подканалов.

10

Целью изобретения является повышение быстродействия устройства.

Указанная цель достигается тем, что в устройство для распределения подканалов, содержащее блок управле15ния, первый вход которого соединен с первым выходом блока хранения, адреса первый вход которого соединен с первым выходом блока управления, введены блок хранения слова, блок выбо20ра информации, формирователь адреса, первый вход которого соединен с выходом блока выбора информации, второй вход блока хранения адреса соединен с первым выходом формирователя адреса

25 и подключен к информационной выходной шине устройства, второй вход формирователя адреса соединен с вторым выходом блока управления, второй вход которого соединен с вторым выходом

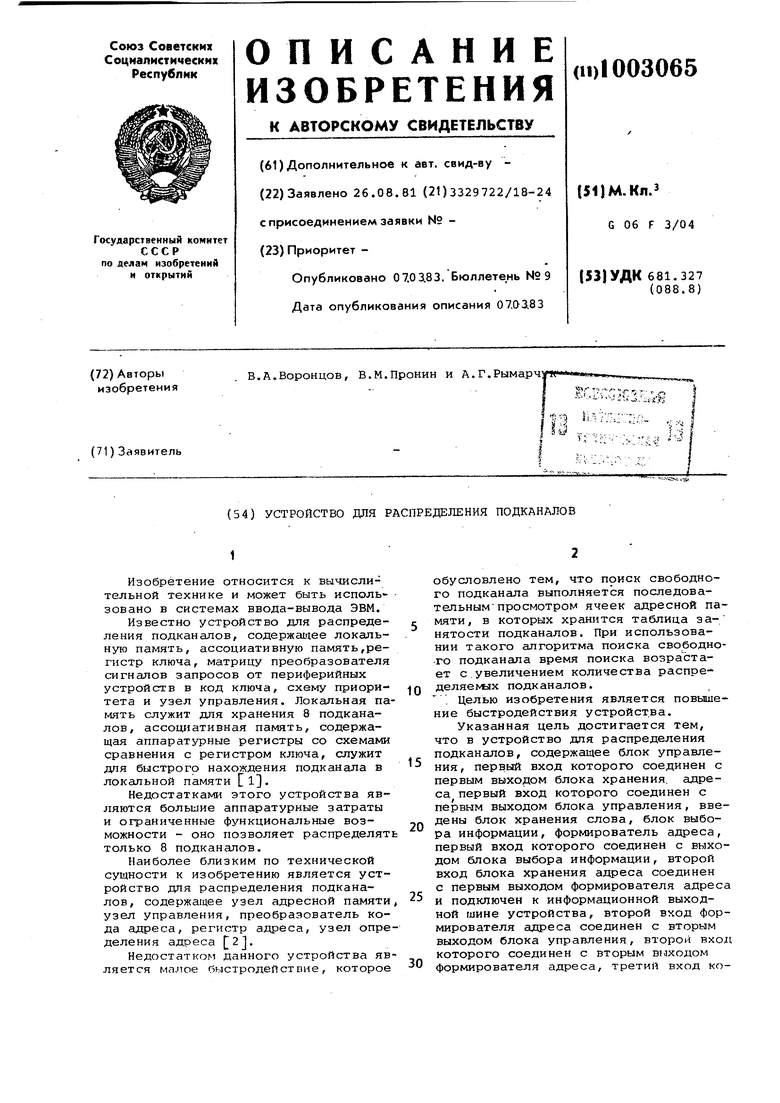

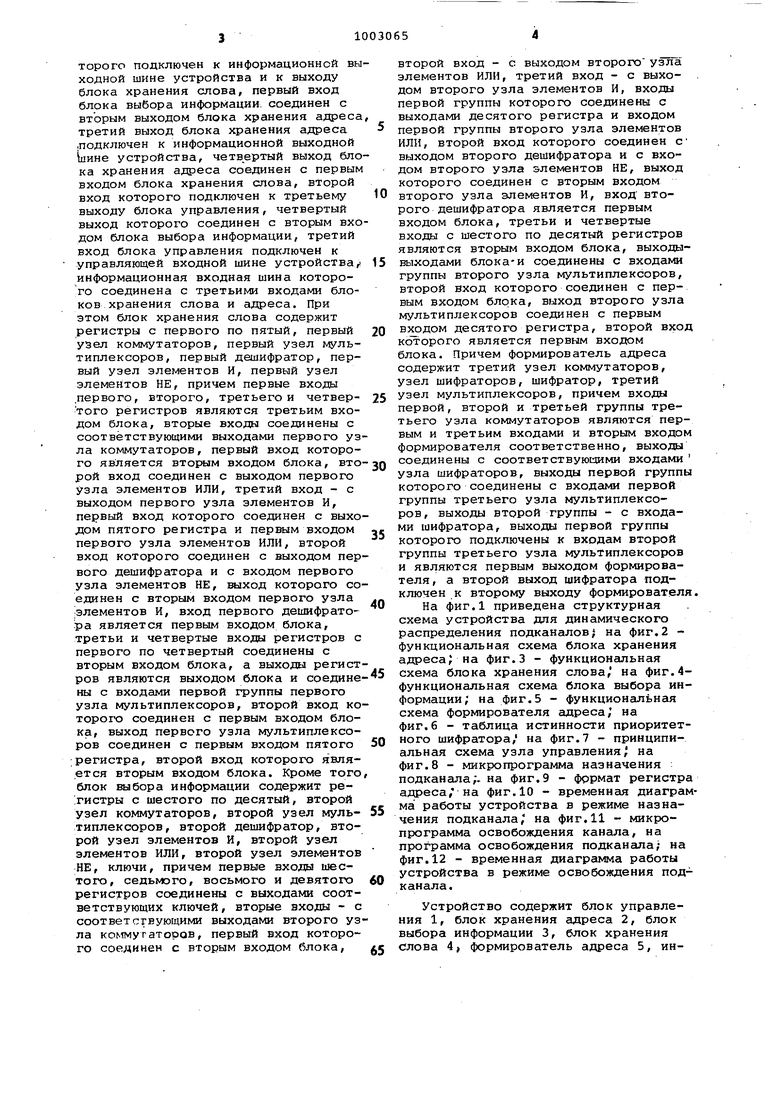

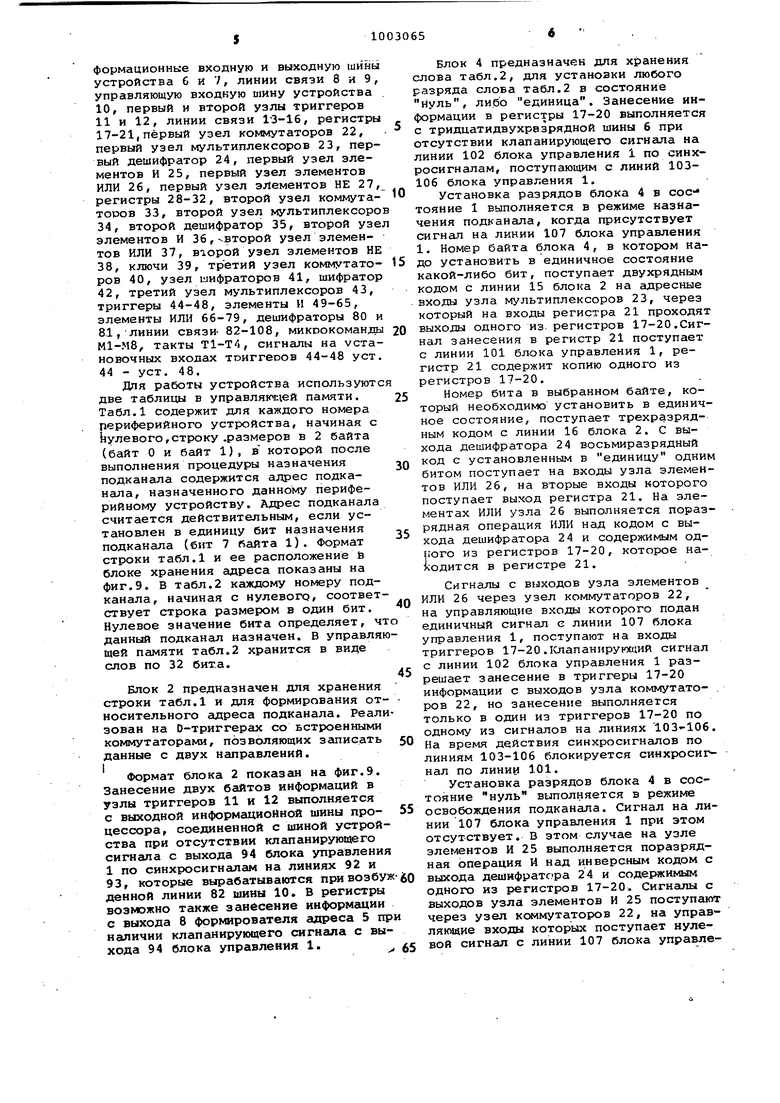

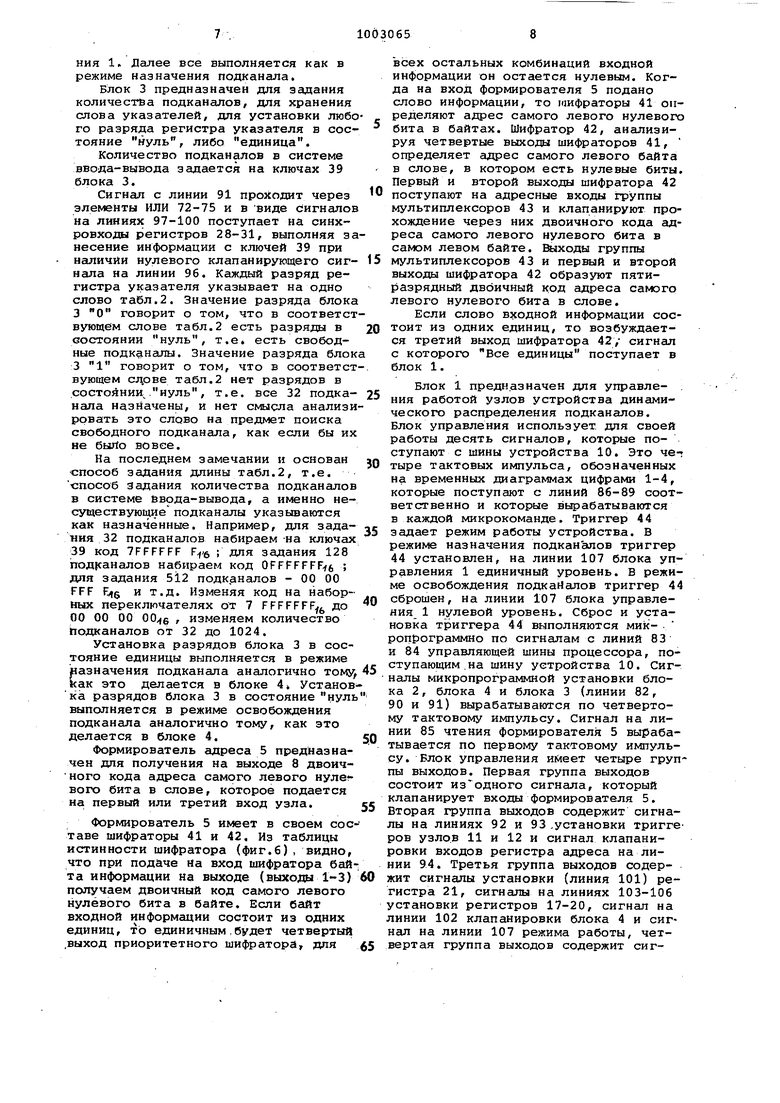

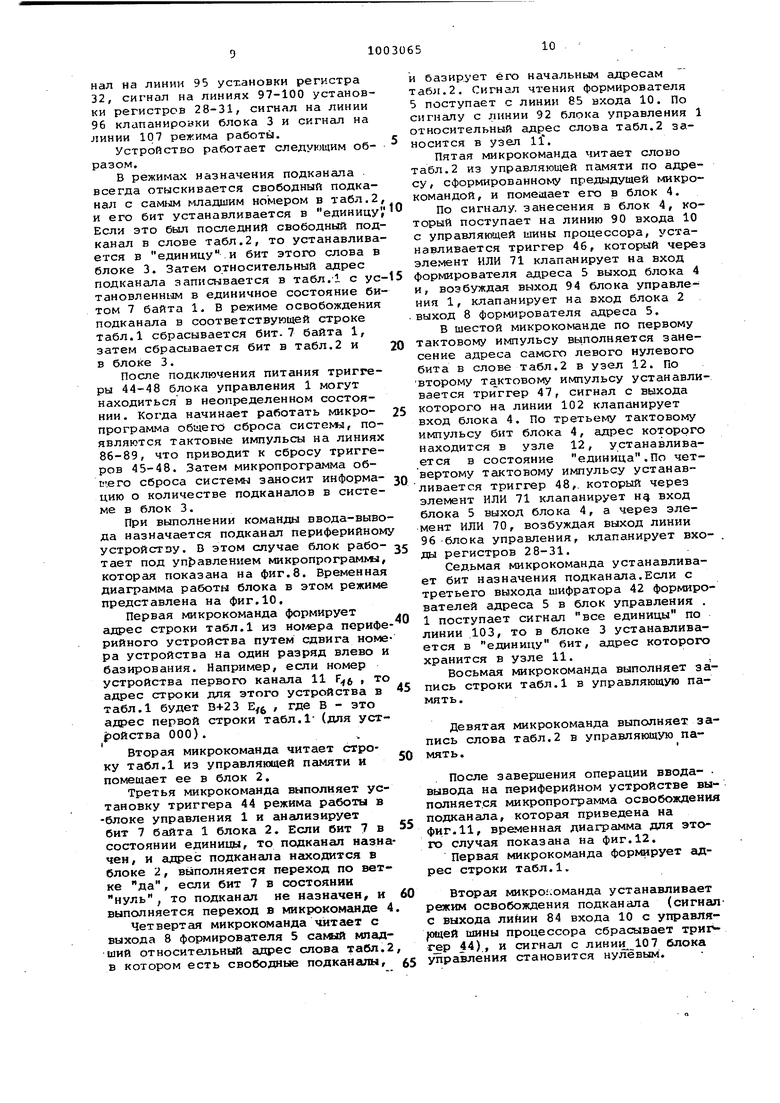

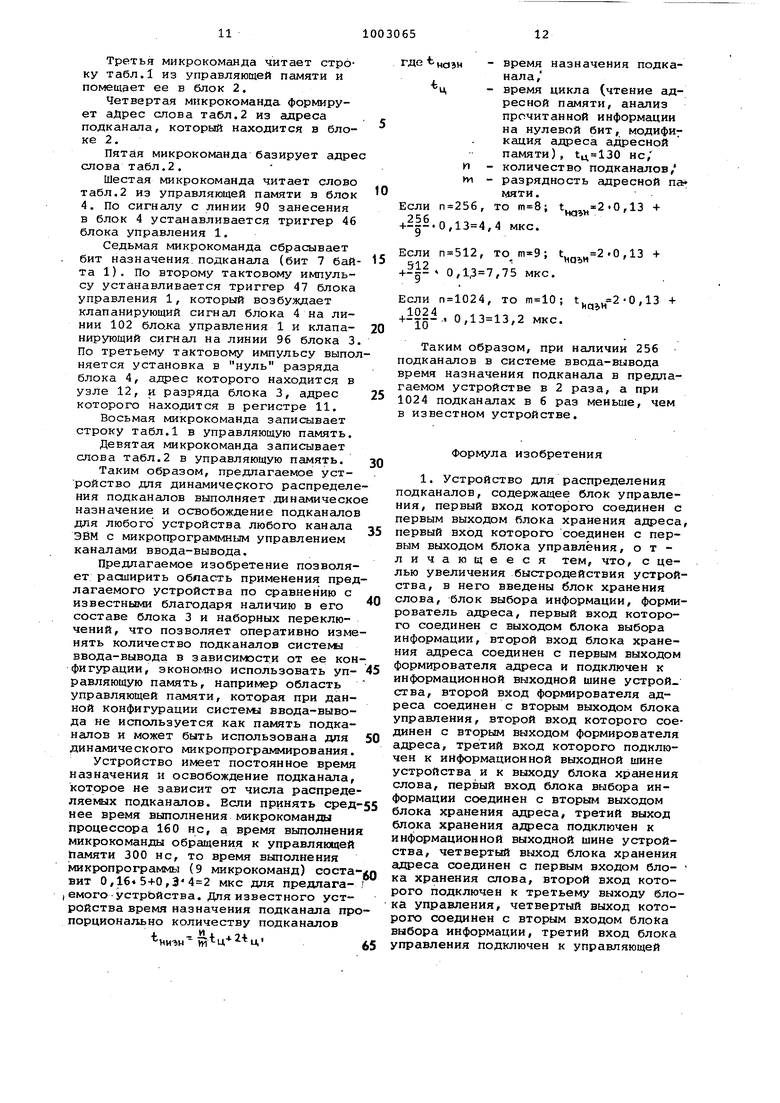

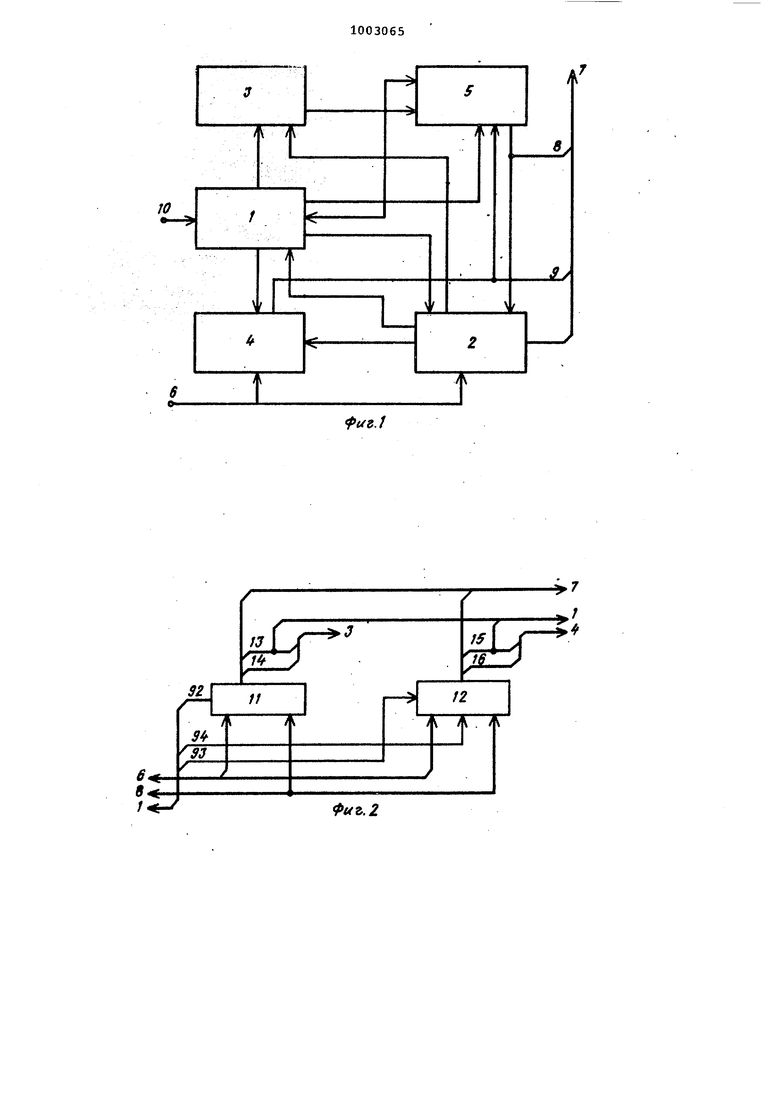

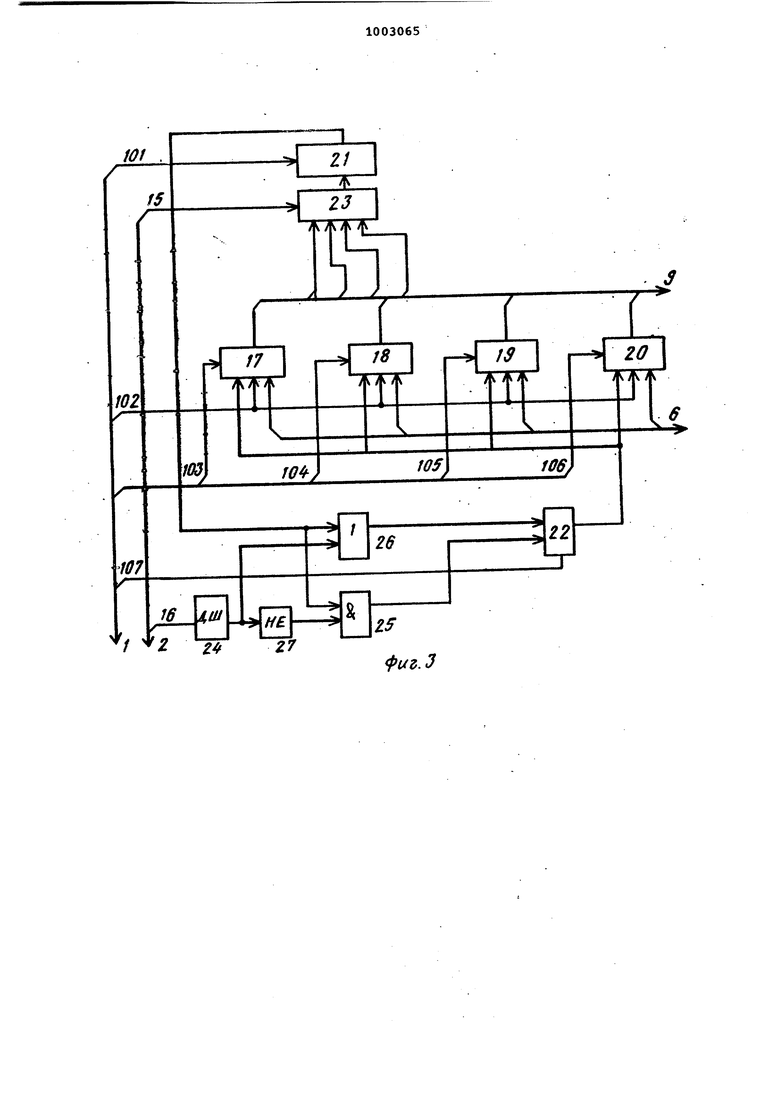

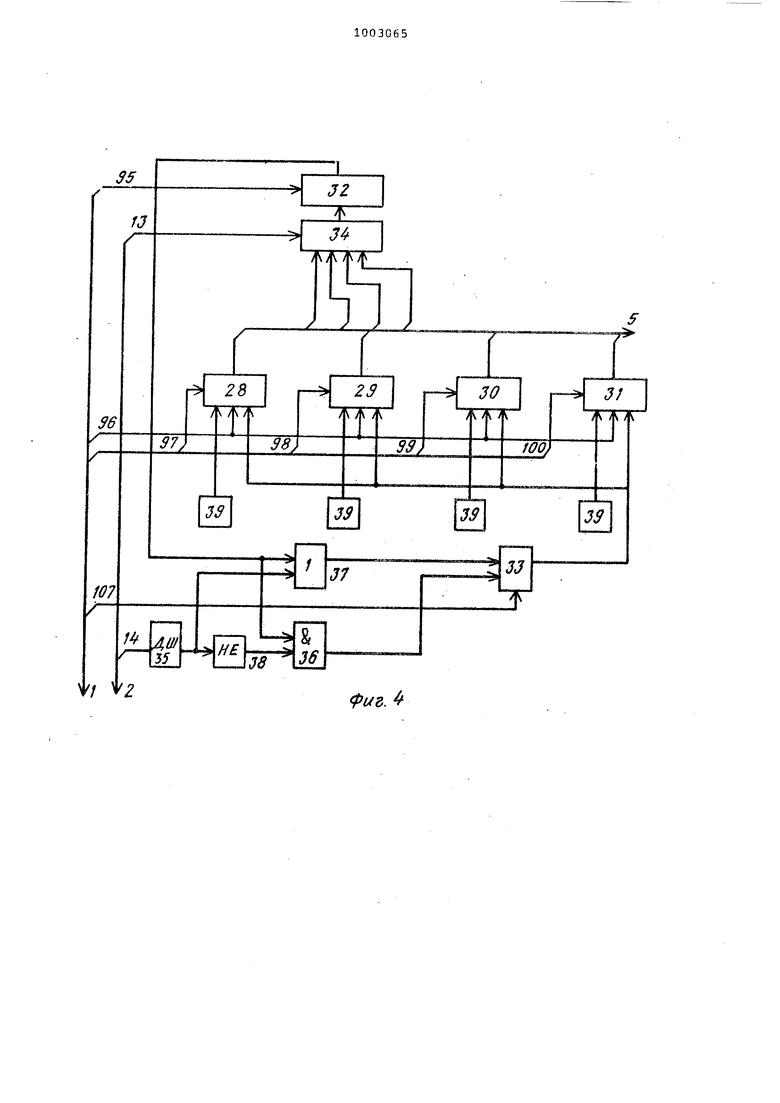

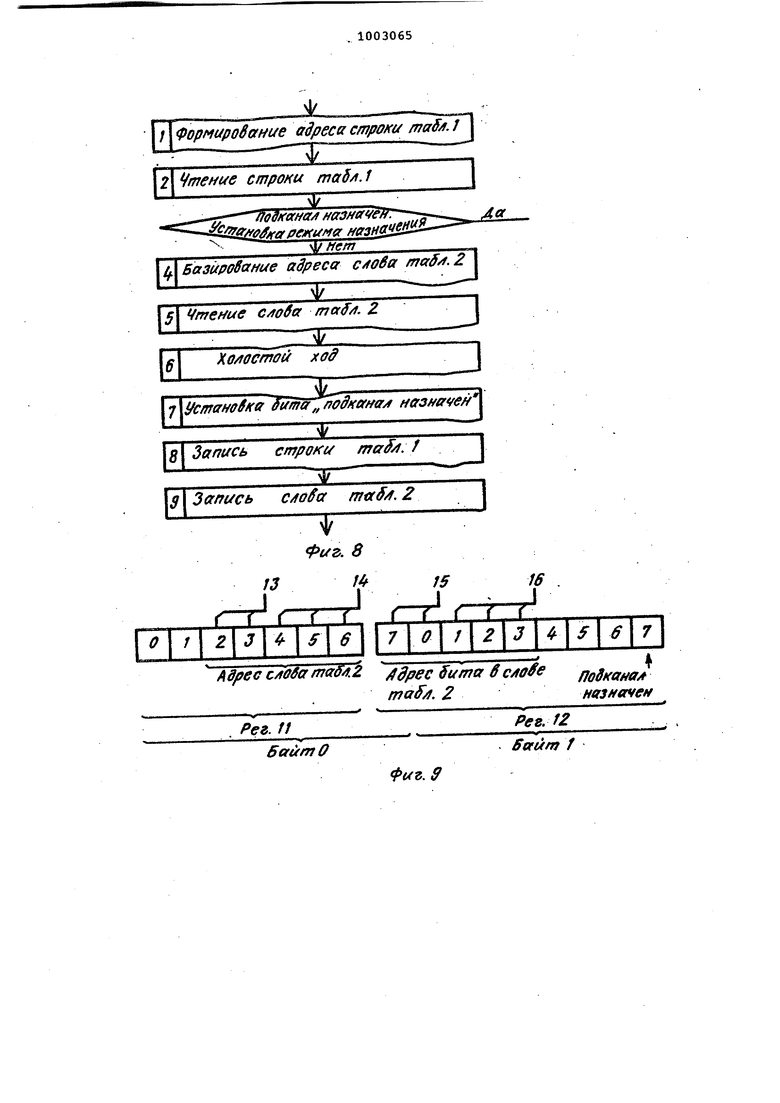

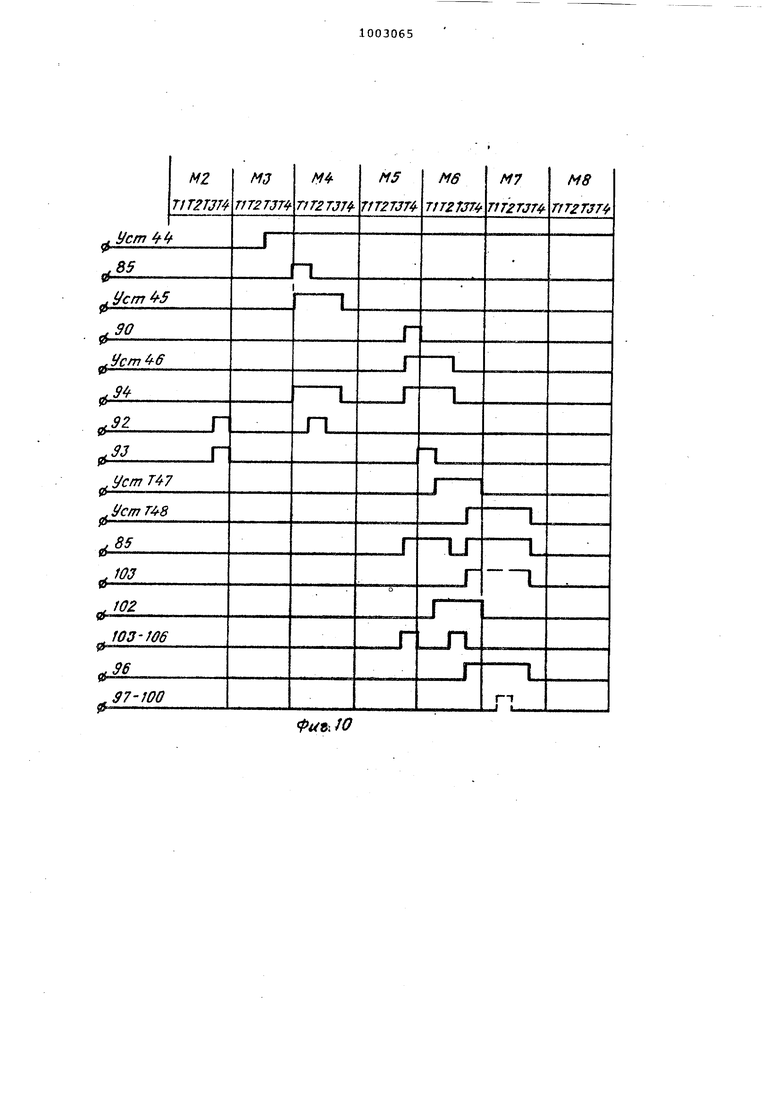

30 формирователя адреса, третий вход которого подключен к информационной вы ходной шине устройства и к выходу блока хранения слова, первый вход блока выбора информации, соединен с вторым выходом блока хранения адреса третий выход блока хранения адреса .подключен к информационной выходной иине устройства, четвертый выход бло ка хранения адреса соединен с первым входом блока хранения слова, второй вход которого подключен к третьему выходу блока управления, четвертый выход которого соединен с вторым вхо дом блока выбора информации, третий вход блока управления подключен к управляющей входной шине устройства информационная входная шина которого соединена с третьими входами блоков хранения слова и адреса. При этом блок хранения слова содержит регистры с первого по пятый, первый узел коммутаторов, первый узел мультиплексоров, первый дешифратор, первый узел элементов И, первый узел элементов НЕ, причем первые входы .первого, второго, третьего и четвертого регистров являются третьим входом блока, вторые входы соединены с соответствующими выходами первого уз ла коммутаторов, первый вход которого является вторым входом блока, вто рой вход соединен с выходом первого узла элементов ИЛИ, третий вход - с выходом первого узла элементов И, первый вход которого соединен с выхо дом пятого регистра и первым входом первого узла элементов ИЛИ, второй вход которого соединен с выходом пер вого дешифратора и с входом первого узла элементов НЕ, выход которого со единен с вторым входом первого узла элементов И, вход первого дешифратора является первым входом блока, третьи и четвертые входы регистров с первого по четвертый соединены с вторым входом блока, а выходы регист ров являются выходом блока и соедине ны с входами первой группы первого узла мультиплексоров, второй вход ко торого соединен с первым входом блока, выход первого узла мультиплексоров соединен с первым входом пятого :регистра, второй вход которого является вторым входом блока. Кроме того блок выбора информации содержит ретистры с шестого по десятый, второй узел коммутаторов, второй узел мультиплексоров, второй дешифратор, второй узел элементов И, второй узел элементов ИЛИ, второй узел элементов НЕ, ключи, причем первые входы шестого, седьмого, восьмого и девятого регистров соединены с выходами соответствующих ключей, вторые входы - с соответствующими выходапш второго уз ла коммутаторов, первый вход которого соединен с вторым входом блока, второй вход - с выходом второго узла элементов ИЛИ, третий вход - с выходом второго узла элементов И, входы первой группы которого соединены с выходами десятого регистра и входом первой группы второго узла элементов ИЛИ, второй вход которого соединен с выходом второго дешифратора и с входом второго узла элементов НЕ, выход которого соединен с вторым входом второго узла элементов И, вход второго дешифратора является первым входом блока, третьи и четвертые входы с шестого по десятый регистров являются вторым входом блока, выходывыходами блока-и соединены с входами группы второго узла мультиплексоров, второй вход которого соединен с первым входом блока, выход второго узла мультиплексоров соединен с первым входом десятого регистра, второй вход ксэторого является первым входом блока. Причем формирователь адреса содержит третий узел коммутаторов, узел шифраторов, шифратор, третий узел мультиплексоров, причем входы первой, второй и третьей группы третьего узла коммутаторов являются первым и третьим входами и вторым входом формирователя соответственно, выходы соединены с соответствующими входами узла шифраторов, выходы первой группы которого соединены с входами первой группы третьего узла мультиплексоров, выходы второй группы - с входами шифратора, выходы первой группы которого подключены к входам второй группы третьего узла мультиплексоров и являются первым выходом формирователя, а второй выход шифратора подключен к второму выходу формирователя. На фиг.1 приведена структурная схема устройства для динамического распределения подканалов; на фиг.2 функциональная схема блока хранения адреса; на фиг.З - функциональная схема блока хранения слова, на фиг.4функциональная схема блока выбора информации; на фиг.5 - функциональная схема формирователя адреса; на фиг.б - таблица истинности приоритетного шифратора, на фиг. 7 - принципиальная схема узла управления; на фиг.8 - микропрограмма назначения подканала;, на фиг.9 - формат регистра адреса,-на фиг.10 - временне1я диаграмма работы устройства в режиме назначения подканала, на фиг. 11 - микропрограмма освобождения канала, на программа освобождения подканала,- на фиг.12 - временная диаграмма работы устройства в режиме освобождения подканала. Устройство содержит блок управления 1, блок хранения адреса 2, блок выбора информации 3, блок хранения слова 4, формирователь адреса 5, информационные входную и выходную шины устройства б и 7, линии связи 8 и 9 управляющую входную шину устройства 10, первый и второй узлы триггеров 11 и 12, линии связи 13-16, регистры 17-21,первый узел коммутаторов 22, первый узел мультиплексоров 23, первый дешифратор 24, первый узел элементов И 25, первый узел элементов ИЛИ 26, первый узел элементов НЕ 27 регистры 28-32, второй узел коммутаTODOB 33, второй узел мультиплексоро 34, второй дешифратор 35, второй узе элементов И 36, -.второй узел элементов ИЛИ 37, вюрой узел элементов НЕ 38, ключи 39, третий узел коммутаторов 40, узел шифраторов 41, шифратор 42, третий узел мультиплексоров 43, триггеры 44-48, элементы И 49-65, элементы ИЛИ 66-79, дешифраторы 80 и 81, линии связи- 82-108, микрокоманды М1-М8, такты Т1-Т4, сигналы на установочных входах тпиггепов 44-48 уст 44 - уст. 48. Для работы устройства используютс две таблицы в управляющей памяти. Табл.1 содержит для каждого номера периферийного устройства, начиная с йулевого,строку .размеров в 2 байта (байт О и байт 1) , в которой после выполнения процедуры назначения подканала содержится адрес подканала, назначенного данному периферийному устройству. Адрес подканала считается действительным, если установлен в единицу бит назначения подканала (бит 7 байта 1). Формат строки табл.1 и ее расположение в блоке хранения адреса показаны на фиг.9. В табл.2 каждому номеру подканала, начиная с нулевого, соответ ствует строка размером в один бит. Нулевое значение бита определяет, ч данный подканал назначен, В управля щей памяти табл.2 хранится в виде слов по 32 бита. Блок 2 предназначен для хранения строки табл.1 и для Формирования относительного адреса подканала. Реали зован на D-триггерах со встроенными коммутаторами, позволяющих записать данные с двух направлений. Формат блока 2 показан на фиг,9. Занесение двух байтов информации в узлы триггеров 11 и 12 выполняется с выходной информационной шины процессора, соединенной с шиной устройства при отсутствии клапанирующего сигнсша с выхода 94 блока управления 1 по синхросигналам на линиях 92 и 93, которые вырабатываются привозбу денной линии 82 шины 10. В регистры возможно также занесение информации с выхода 8 формирователя гщреса 5 пр наличии клапанирующего сигнала с выхода 94 блока управления 1. Блок 4 предназначен для хранения слова табл.2, для установки любого разряда слова табл.2 в состояние нуль, либо единица. Занесение информации в регистры 17-20 выполняется с тридцатидвухразрядной шины 6 при отсутствии клапанирующего сигнала на линии 102 блока управления 1 по синхросигналам, поступающим с линий 103106 блока управления 1. Установка разрядов блока 4 в сос тояние 1 выполняется в режиме назначения подканала, когда присутствует сигнал на линии 107 блока управления 1. Номер байта блока 4, в котором надо установить в единичное состояние какой-либо бит, поступает двухрядным кодом с линии 15 блока 2 на адресные входы узла мультиплексоров 23, через который на входы регистра 21 проходят выходы одного из, регистров 17-20.Сигнал занесения в регистр 21 поступает с линии 101 блока управления 1, регистр 21 содержит копию одного из регистров 17-20. Номер бита в выбранном байте, который необходимо установить в единичное состояние, поступает трехразрядным кодом с линии 16 блока 2. С выхода дешифратора 24 восьмиразрядный код с установленным в единицу одним битом поступает на входы узла элементов ИЛИ 26, на вторые входы которого поступает выход регистра 21. На элементах ИЛИ узла 26 выполняется поразрядная операция ИЛИ над кодом с выхода дешифратора 24 и содержимым од(;ого из регистров 17-20, которое на ;одится в регистре 21. Сигналы с выходов узла элементов ИЛИ 26 через узел коммутаторов 22, на управляющие входы которого подан единичный сигнал с линии 107 блока управления 1, поступают на входы триггеров 17-20 .1Слапанирую ций сигнал с линии 102 блока управления 1 разрешает занесение в триггеры 17-20 информации с выходов узла коммутато- . ров 22, но занесение выполняется только в один из триггеров 17-20 по одному из сигналов на линиях ЮЗ-Юб. На время действия синхросигналов по линиям 103-106 блокируется синхросигнал по линии 101, Установка разрядов блока 4 в состояние нуль выполняется в режиме освобождения подканала. Сигнал на линии 107 блока управления 1 при этом отсутствует. В этом случае на узле элементов И 25 выполняется поразрядная операция И над инверсным кодом с выхода дешифратсра 24 и содержимым одного из регистров 17-20. Сигналы с выходов узла элементов И 25 поступают через узел коммутаторов 22, на управ ляющие входы которых поступает нулевой сигнал с линии 107 блока управления 1, Далее все выполняется как в режиме назначения подканала.

Блок 3 предназначен для задания количества подканалов, для хранения слова указателей, для установки любого разряда регистра указателя в соетояние нуль, либо единица.

Количество подканалов в системе ввода-вывода задается на ключах 39 блока 3.

Сигнал с линии 91 проходит через элементы ИЛИ 72-75 и в виде сигналов на линиях 97-100 поступает на синхровходы регистров 28-31, выполняя занесение информации с ключей 39 при наличии нулевого клапанирующего сигнала на линии 96. Каждый разряд регистра указателя указывает на одно слово табл.2. Значение разряда блока 3 О говорит о том, что в соответствующем слове табл.2 есть разряды в состоянии нуль, т.е. есть свободные подкангшы. Значение разряда блок 3 1 говорит о том, что в сортветст вующем сдове табл.2 нет разрядов в состойнии нуль, т.е. все 32 подканала назначены, и нет смысла анализировать это слово на предмет поиска свободного подканала, как если бы их не быЛо вовсе.

На последнем замечании и основан способ задания длины табл.2, т.е. способ задания количества подканалов в системе йврда-вывода, а именно несуществующие подканалы указываются как назначенные. Например, для задаНИН 32 подканалов набираем на ключах 39 код 7FFFFFF ; для задания 128 подканалов набираем код OFFFFFFF ; для задания 512 подканалов - 00 00 FFF и т.д. Изменяя код на наборных переключателях от 7 FFFFFFF j, до 00 00 00 / изменяем количество Подканалов от 32 до 1024.

Установка разрядов блока 3 в состояние единицы выполняется в режиме (назначения подканала аналогично тому, как это делается в блоке 4 Установ ка разрядов блока 3 в состояние нуль выполняется в режиме освобождения подканала аналогично тому, как это делается в блоке 4.

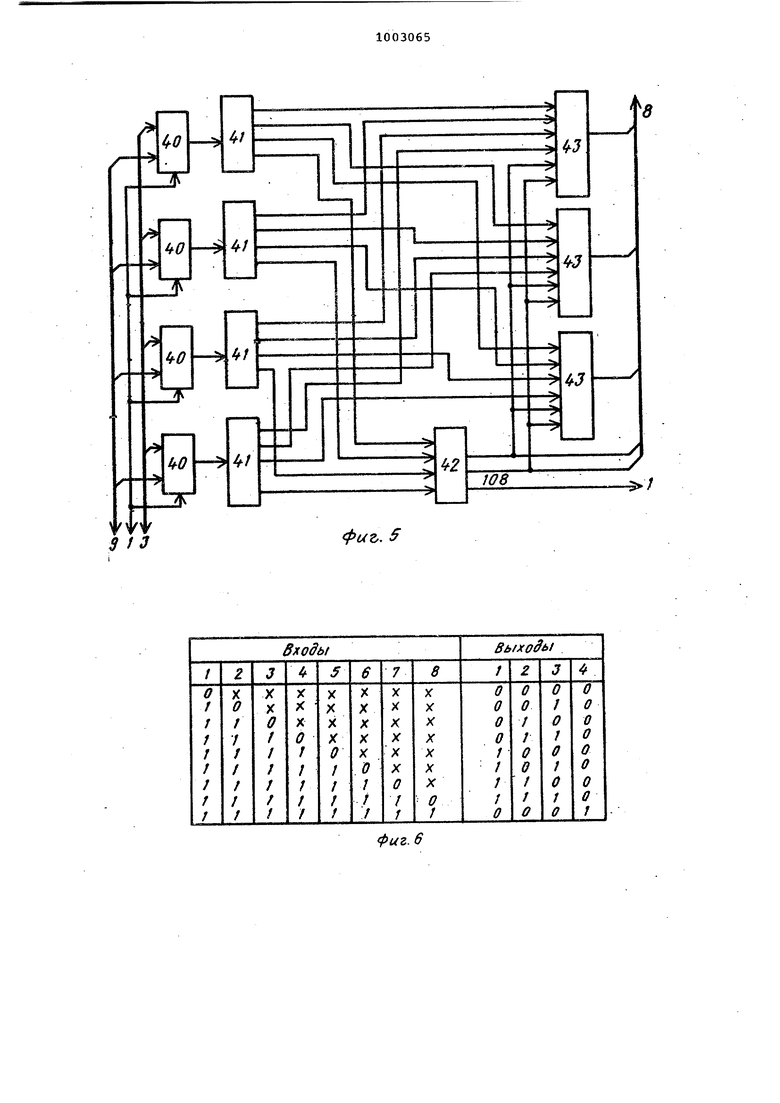

Формирователь адреса 5 предназначен для получения на выходе 8 двоичного кода адреса самого левого нуле вого бита в слове, которое подается на первый или третий вход узла.

Формирователь 5 имеет в своем соетаве шифраторы 41 и 42. Из таблицы истинности шифратора (фиг.6), видно, что при подаче на вход шифратора байта информации на выходе (выходы 1-3} получаем двоичный код самого левого нулевого бита в байте. Если бс1йт входной информации состоит из одних единиц, то единичным .будет четвертый .выход приоритетного шифратора, для

всех остальных комбинаций входной информации он остается нулевым. Когда на вход формирователя 5 подано слово информации, то шифраторы 41 определяют адрес самого левого нулевого бита в байтах. Шифратор 42, анализируя четвертые выходы шифраторов 41, определяет адрес самого левого байта в слове, в котором есть нулевые биты. Первый и второй выходы шифратора 42 поступают на адресные входы группы мультиплексоров 43 и клапанируют прохождение через них двоичного кода адреса самого левого нулевого бита в самом левом байте, шходы группы мультиплексоров 43 и первый и второй выходы шифратора 42 образуют пятиразрядный двоичный код адреса самого левого нулевого бита в слове.

Если слово вгсодной информации состоит из одних единиц, то возбуждается третий выход шифратора 42/ сигнал с которого Все единицы поступает в блок 1.

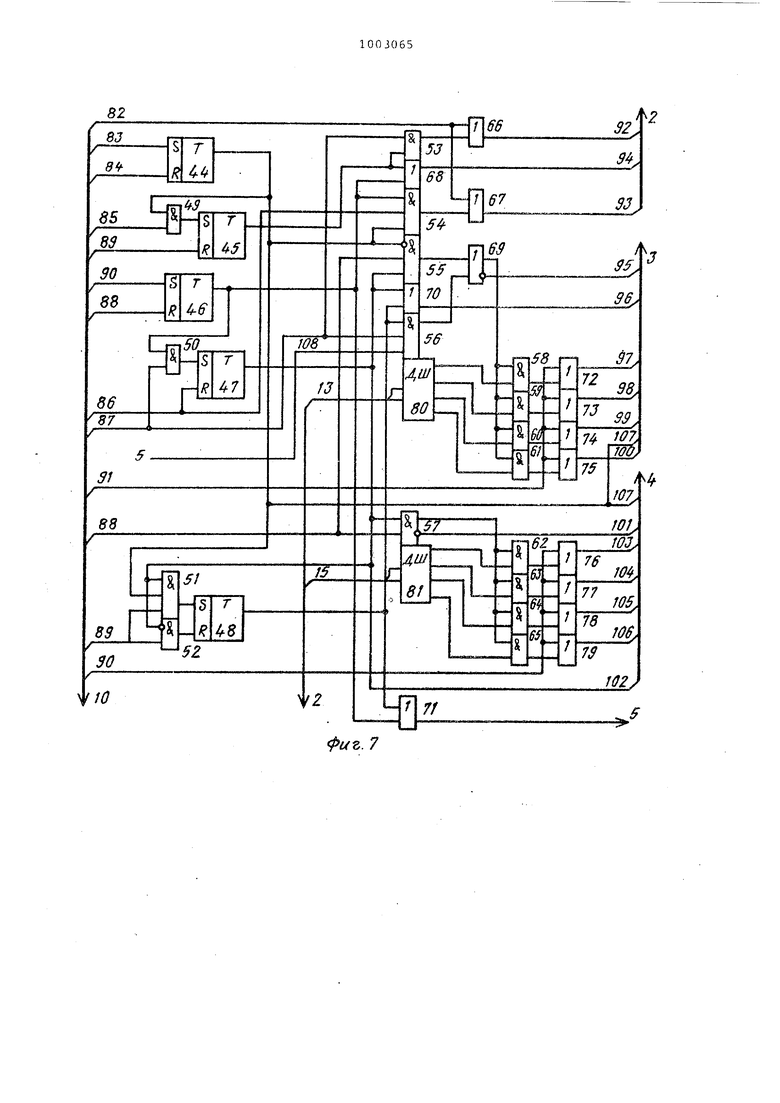

Блок 1 предн.азначен для управления работой узлов устройства динамического распределения подканалов. БЛОК управления использует для своей работы десять сигналов, которые поступают с шины устройства 10. Это четыре тактовых импульса, обозначенных на временных диаграммах цифрами 1-4, которые поступают с линий 86-89 соответственно и которые вырабатываются в каждой микрокоманде. Триггер 44 задает режим работы устройства. В режиме назначения подканалов триггер 44 установлен, на линии 107 блока управления 1 единичный уровень. В режиме освобождения подканалов триггер 44 сброшен, на линии 107 блока управления 1 нулевой уровень. Сброс и установка триггера 44 выполняются микропрограммно по сигналам с линий 83 и 84 управляющей шины процессора, поступающим.на шину устройства 10. Сигналы микропрограммной установки блока 2 , блока 4 и блока 3 (линии 82, 90 и 91) вырабатываются по четвертому тактовому импульсу. Сигнал на линии 85 чтения формирователя 5 вырабатывается по первому тактовому импульсу. Блок управления ийеет четыре группы выходов. Первая группа выходов состоит изодного сигнала, который клапанирует входы формирователя 5. Вторая группа выходов содержит сигналы на линиях 92 и 93 .установки триггеров узло.в 11 и 12 и сигнал клапанировки входов регистра адреса на линии 94. Третья группа выходов содержит сигналы установки (линия 101) регистра 21, сигналы на линиях 103-106 установки регистров 17-20, сигнал на линии 102 клапанировки блока 4 и сигнал на линии 107 режима работы, четвертая группа выходов содержит сигнал на линии 95 усхановки регистра 32, сигнал на линиях 97-100 установки регистров 28-31, сигнал на линии 96 клапанировки блока 3 и сигнал на линии 107 режима работй.

Устройство работает следующим образом.

В режимах назначения подканала всегда отыскивается свободный подканал с caMfJM младшим номером в табл.2, и его бит устанавливается в единицу, Если это был последний свободньИ подканал в слове табл.2, то устанавливается в единицу.и бит этого слова в блоке 3. Затем относительный адрес подканала записывается в табл.-1 с установленным в единичное состояние битом 7 байта 1. В режиме освобождения подканала в соответствующей строке табл.1 сбрасывается бит-7 байта 1, затем сбрасывается бит в табл,2 и в блоке 3.

После подключения питания триггеры 44-48 блока управления 1 могут находиться в неопределенном состоянии . Когда начинает работать микропрограмма общего сброса системы, появляются тактовые импульсы на линиях 86-89, что приводит к сбросу триггеров 45-48. Затем микропрограмма обс.его сброса системы заносит информацию о количестве подканалов в системе в блок 3.

При выполнении команды ввода-вывода назначается подканал периферийному устройству. Б этом случае блок работает под управлением микропрограммы, которая показана на фиг.8. Временная диаграмма работы блока в этом режиме представлена на фиг.10.

Первая микрокоманда формирует

адрес строки табл.1 из периферийного устройства путем сдвига номера устройства на один разряд влево и базирования. Например, если номер устройства первого канала 11 F , то адрес строки для этого устройства в табл.1 будет В+23 Е , где В - это адрес первой строки табл.1- (для устpofiCTBa 000).

Вторая микрокоманда читает строку табл.1 из управляющей памяти и помещает ее в блок 2.

Третья микрокоманда выполняет установку триггера 44 режима работы в -блоке управления 1 и анализирует бит 7 байта 1 блока 2. Если бит 7 в состоянии единицы, то подканал назначен , и адрес подканала находится в блоке 2, выполняется переход по ветке да, если бит 7 в состоянии нуль , то подканал не назначен, и выполняется переход в микрокомгшде 4

Четвертая микрокоманда читает с выхода 8 формирователя 5 самый младший относительный адрес слова табл.2 в котором есть свободные подканалы,

и базирует его начальным адресам табл.2. Сигнал чтения формирователя 5 поступает с линии 85 входа 10. По сигналу с линии 92 блока управления 1 относительный адрес слова табл.2 заносится в узел if.

Пятая микрокоманда читает слово табл.2 из управляющей памяти по адресу , сформированному предыдущей микрокомандой, и noMeiuaeT его в блок 4.

По сигналу, занесения в блок 4, который поступает на линию 90 входа 10 с управляющей шины процессора, устанавливается триггер 46, который через элемент ИЛИ 71 клапанирует на вход формирователя адреса 5 выход блока 4 и, возбуждая выход 94 блока управления 1, клапанирует на вход блока 2 выход 8 формирователя адреса 5.

В шестой микрокоманде по первому тактовому импульсу выполняется занесение адреса самого левого нулевого бита в слове табл.2 в узел 12. По второму тактовому импульсу устанавливается триггер 47, сигнал с выхода которого на линии 102 клапанирует вход блока 4. По третьему тактовому импульсу бит блока 4, адрес которого находится в узле 12, устанавливается в состояние единица.По четвертому тактовому импульсу устанавливается триггер 48,. который через элемент ИЛИ 71 клапанирует н вход блока 5 выхол блока 4, а через элемент ИЛИ 70, возбуждая выход линии 96 блока управления, клапанирует входы регистров 28-31.

Седьмая микрокоманда устанавливает бит назначения подканала.Если с третьего выхода шифратора 42 формирователей адреса 5 в блок управления . 1 поступает сигнал все единицы по линии 103, то в блоке 3 устанавливается в единицу бит, адрес которого хранится в узле 11.

Восьмая микрокоманда выполняет запись строки табл.1 в управляющую память.

Девятая микрокоманда выполняет запись слова табл.2 в управляющую память.

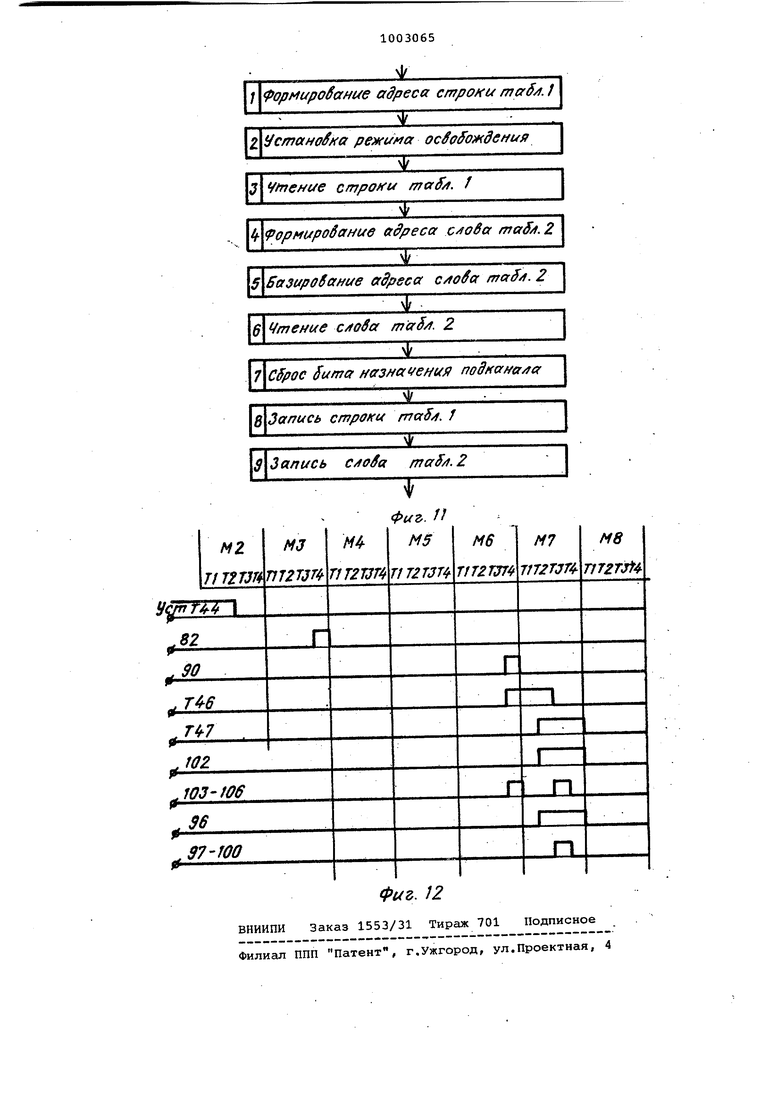

После завершения операции ввода- вывода на периферийном устройстве выполняется микропрограмма освобождения подканала, которая приведена на фиг.11, временная диаграмма для этого случая показсша на фиг.12.

Первая микрокоманда формирует адрес строки табл.1.

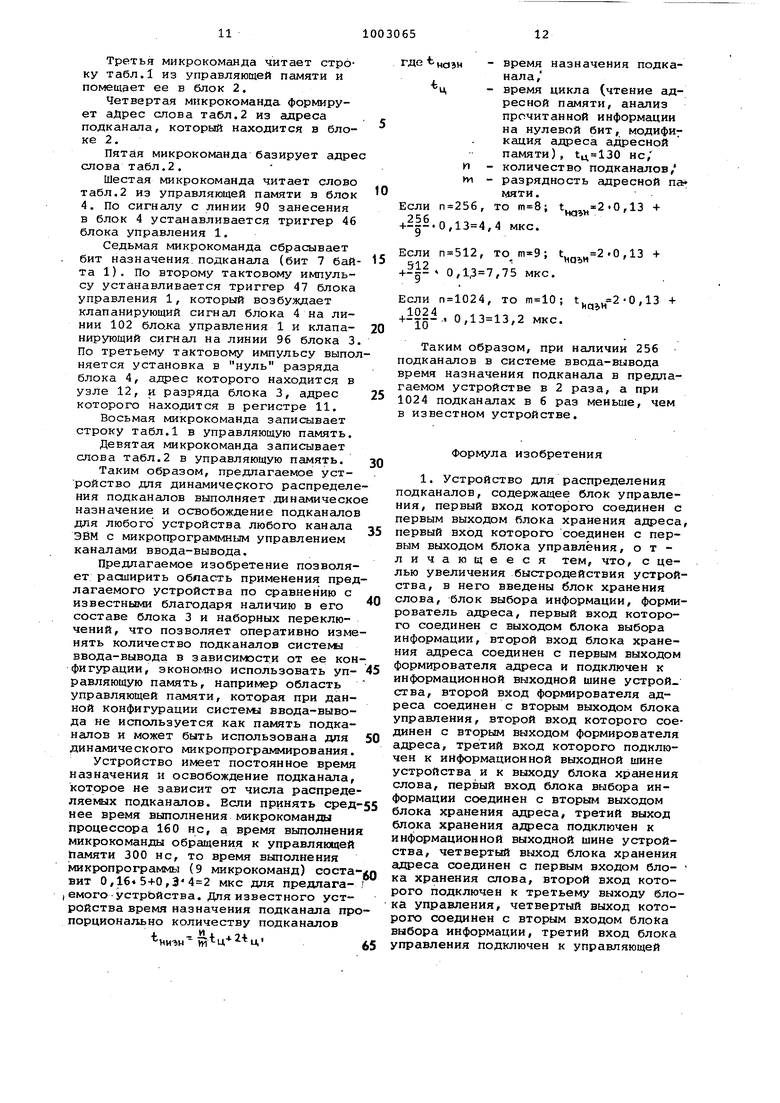

Вторая микро;;оманда устанавливает режим освобождения подканала (сигналс выхода линии 84 входа 10 с управлярцей шины процессора сбрасывает триг rjep 44), и сигнал с линии 107 блока управления становится нулевым. Третья микрокоманда читает строку табл,1 из управляющей памяти и помещает ее в блок 2, Четвертая микрокоманда формирует адрес слова табл.2 из адреса подканала, который находится в блоке 2. Пятая микрокоманда базирует адре слова табл.2. Шестая микрокоманда читает слово табл.2 из управляющей памяти в блок 4. По сигналу с линии 90 занесения в блок 4 устанавливается триггер 46 блока управления 1. Седьмая микрокоманда сбрасывает бит назначения, подканала (бит 7 бай та 1). По второму тактовому импульсу устанавливается триггер 47 блока управления 1, который возбуждает клапанирующий сигнал блока 4 на линии 102 блока управления 1 и клапанирующий сигнал на линии 96 блока 3 По третьему тактовому импульсу выпо няется установка в нуль разряда блока 4, адрес которого находится в узле 12, и разряда блока 3, адрес которого находится в регистре 11. Восьмая микрокоманда записывает строку табл.1 в управляющую память. Девятая микрокоманда записывает слова табл.2 в управляющую память. Таким образом, предлагаемое устройство для динамического распредел ния подканалов выполняет динамическо назначение и освобождение подканало для любого устройства любого канала ЭВМ с микропрограммным управлением каналами ввода-вывода. Предлагаемое изобретение позволя ет расширить область применения пред лагаемого устройства по сравнению с известными благодаря наличию в его составе блока 3 и наборных переключений, что позволяет оперативно изме нять количество подканалов систе ы ввода-вывода в зависимости от ее кон фигурации, эконогдао использовать управляющую память, например область управляющей памяти, которая при данной конфигурации систе ввода-вывода не используется как память подканалов и может быть использована для динамического микропрограммирования Устройство имеет постоянное время назначения и освобождение подканала которое не зависит от числа распреде ляемых подканалов. Если принять сред нее время выполнения микрокоманды процессора 160 не, а время выполнени микрокоманды обращения к управляющей Памяти 300 НС, то время выполнения микропрограммы (9 микрокоманд) соста вит 0,16 5+0, МКС для предлагаIемого-устрЬйства. Для известного устройства время назначения подканала пр порционально количеству подканалов гдеЬцд н - время назначения подканала, ц- время цикла (чтение адресной памяти, анализ прочитанной информации на нулевой бит, модифИ7 кация адреса адресной памяти) , 1ц 130 НС, и - количество подканалов, VV1 - разрядность адресной па мяти. Если , то t.,..-2 «0,13 + +-22.0,,4 МКС. Если п 512, то т«9; ,13 + 0,1,3 7,75 МКС. 2-0,13 + ЕСЛИ , то т 10; 1, ,2 МКС. Таким образом, при наличии 256 подканалов в системе ввода-вывода времен назначения подканала в предлагаемом устройстве в 2 раза, а при 1024 подканалах в 6 раз меньше, чем в известном устройстве. Формула изобретения 1. Устройство для распределения подканалов, содержащее блок управления, первый вход которого соединен с первым выходом блока хранения адреса, первый вход которого соединен с первым выходом блока управления, отличающееся тем, что, с целью увеличения быстродействия устройства, в него введены блок хранения слова, блок выбора информации, формирователь адреса, первый вход которого соединен с выходом блока выбора информации, второй вход блока хранения адреса соединен с первым выходом формирователя адреса и подключен к информационной выходной шине устройства, второй вход формирователя адреса соединен с вторым выходом блока управления, второй вход которого соединен с вторым выходом формирователя адреса, третий вход которого подключен к информационной выходной шине устройства и к выходу блока хранения слова, первый вход блока выбора информации соединен с вторым выходом блока хранения адреса, третий выход блока хранения адреса подключен к информационной выходной шине устройства, четвертьй выход блока хранения адреса соединен с первым входом бло- ка хранения слова, второй вход которого подключен к третьему выходу блока управления, четвертый выход которого соединен с вторым входом блока выбора информации, третий вход блока управления подключен к управляющей входной шине устройства, информационная входная шинакоторого соединена с третьими входами блоков хранения слова и адреса. 2. Устройство по п.-1, о т л и ч аю щ е е с я тем, что блок хранения слова содержит регистры с первого по пятый, первый узел коммутаторов, первый узел мультиплексоров, первый дешифратор, первый узел-элементов И, первый узел элементов НЕ, причем первые входы первого, второго, третьего и четвертого регистров являются третьим входом блока, вторые входы соединены с соответствующими выходами первого узла ког-«мутаторов, первый вход которого является вторым входом блока, второй вход соединен с выходом первого узла элементов ИЛИ, третий вход - с выходом первого узла элементов И, первый вход КОТОРОГО соединен с выходом пятого регистра и с первым входом первого узла элементов ИЛИ, второй вход которого соединен с выходом первого дешифратора и с входом первого узла элементов НЕ, выход последнего соединен с вторым входом первого узла элементов И, вход первого дешифратора является первым входом блока, третьи и четвертые входы регистров с первого по четвертый соединены с вторым входом блока, а выходы регистров являются выходом блока и соединены с входами первой группы первого узла мультиплексоров, второй вход которого соединен с первым входом блока, ,выход первого узла мультиплексоров соединен с первым входом пятого регистра, второй вход которого является вторым вхолюм блока. 3. Устройство ПОП.1, отлич аю щ е е с я тем, что блок выбора информации содержит регистры с шестого по десятый, второй узел коммутаторов второй узел мультиплексоров, второй дешифратор, второй узел элементов И, второй узел элементов ИЛИ, второй узел элементов НЕ, ключи, причем первые входы шестого, седьмого, восьмого и девято1о регистров соединены с выходами соответствующих ключей, вторые входы - с соответствующими выходами второго узла коммутаторов, первый вход которого соединен с вторым входом блока, второй вход - с выходом второго узла ИЛИ, третий вход - с выходом второго узла элементов И, входы первой группы которого соединены с выхоДами десятого регистра и с входом первой группы второго узла элементов ИЛИ, второй вход которого соединен с выходом второго дешифратора и с входом второго узла элементов НЕ, выход которого соединен с вторым входом второго узла элементов И, вход второго дешифратора является первым входом блока, третьи и четвертые входы с шестого по десятый регистров являются вторым входом блока, выходы - выходами блока и соединены с входами группы второго узла мультиплексоров, второй вход которого соединен с первым входом блока, в1-1ход второго узла мультиплексоров соединен с первым входом десятого регистра, второй вход которого является первым входом блока. 4. Устройство ПОП.1, отличающее, с я тем, что формирователь адреса содержит третий узел коммутаторов, узел шифраторов, шифратор, третий узел мультиплексоров, причем входы первой, второй и третьей группы третьего узла коммутаторов являются первым и третьим входами и вторым входом форг-мрователя соот ветственно, выходы соединены с соответствующими входами узла шифраторов, выходы первой группы которого соединены с входами первой группы третьего узла мультиплексоров, выходы второй группы - с входами шифратора, выходы первой группы которого подключены к входам второй группы третьего узла . мультиплексоров и являются первым выходом формирователя, а второй выход шифратора подключен к второму выходу формирователя. Источники информации, принятые во внимание при экспертизе 1.Патент США 3408632, кл. 340-172.5, опублик. 1968. 2.Авторское свидетельство СССР 514287, кл. G 06 F 3/04, 1976 (прототип).

i I

8.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммный мультиплексный канал | 1985 |

|

SU1305693A2 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1280642A2 |

| Комбинированный канал | 1986 |

|

SU1405067A1 |

| Устройство для сопряжения периферийных устройств с процессором и оперативной памятью | 1983 |

|

SU1156084A1 |

| Устройство для назначения подканалов | 1984 |

|

SU1264189A1 |

| Устройство для обмена информацией | 1983 |

|

SU1198528A1 |

| Система ввода-вывода для микропрограммируемой ЭВМ | 1988 |

|

SU1667084A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1278867A2 |

| Устройство для сопряжения электронно-вычислительной машины с внешним устройством | 1986 |

|

SU1388880A2 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

риг.1

фиг.З

S f3

фиг. 6

риг.7

f I Формирование адреса строки /na&f. 1

Чтение строни mad.f

Ж

.. JfodiftxHtt/i ffa3Hc(t/eJr SlSlfff /fapeiKUMa wj//g ggf i/ Нет

Базйробание адреса слова тс(б,2

т

Чтение с/гоба . Z

Xo/iocmou ход

4i

l/coTffHofKff burner odKOfffff HCfSffCft/en

строки , fI

Ж

c/io$o .2

Г

Pt/e. в

/J

r-rlr

2 J

Адрес mffff4.2 Зрес Suma в подкамгя

. Рег. ft

беги/770

/j /5/

r r ( Л r

/

. 2

назначен

Ре 9, 12 Байт /

Фиг, 9

W

Нормирование адреса строки тсгб/). /

-1ШпуТПИ11ЯГГМЦ|||М1ШЛиШ11 С | и-г лШЛ | JIM-lT 1., tf-г ,, -т-ДГИГLJ 11Г

CfnanoiSffa режима ocSofondeffua Ч(пение cmpoffu /ncrf/t. /I

« «« «««viBWMMaMMMMMiBM BBaHMVMNBiMHMtiBHHaqnMiuinMnwBiiMMMBMW BBMHHgBMM B

Рормиродание адреса maff/t. 2

I- I-

5 Базиро$ание ffBpsca та. 2

(fmetfue c/ioSa mcrS/f. 2

AcSpoc Sumof исезмск ения nod/fcrva ff

8 строка mctS. 1

b Запись maS/}. 2

l

ж:

±.

Ж

JL

Фиг. //

Авторы

Даты

1983-03-07—Публикация

1981-08-26—Подача