2И-ИЛИ-НЕ, причем первый вход блока анализа знака разности аргументов соединен с первым входом элемента 2И-ИЛИ-НЕ и через первый элемент НЕ с вторым входом элемента 2И-11ЛИ-НЕ, второй вход блока анализа знака соединен с третьим входом элемента

2И-ИЛИ-НЕ и через второй элемент НЕ с четвертым входом элемента 2И-ИЛИ-НЕ выход которого соединен через третий элемент НЕ с первым выходом блока, второй выход которого соединен с выходом элемента 2И-ИЛИНЕ..

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой функциональный преобразователь | 1977 |

|

SU684552A1 |

| Функциональный преобразователь | 1981 |

|

SU960836A1 |

| Устройство для извлечения корня @ -й степени | 1982 |

|

SU1084789A1 |

| Функциональный преобразователь двух переменных | 1984 |

|

SU1168964A1 |

| Устройство для цифрового функционального преобразования | 1981 |

|

SU993271A1 |

| Функциональный преобразователь | 1983 |

|

SU1115069A1 |

| Цифровой функциональный преобразователь | 1981 |

|

SU960837A1 |

| Калибратор сигналов, нормированных по коэффициенту гармоник | 1988 |

|

SU1555677A1 |

| Устройство для аппроксимации функций | 1980 |

|

SU934481A1 |

| Функциональный преобразователь | 1984 |

|

SU1176344A1 |

1. ЦИФРОВОЙ ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ, содержащий генератор импульсов, три блока перезаписи, регистр, дешифратор, управляемый делитель частоты, реверсивный счетчик, блок формирования начального кода, вычитающий блок, вычитающий счетчик, дешифратор нуля, триггер и элемент И, причем управляющий вход и информационные входы первого блока перезаписи соединены соответственно с управляющим входом и информационными входами преобразователя, выходы первого блока перезаписи через регистр и дешифратор соединены с входами управляемого делителя частоты, первый выход которого соединен с управляющими входами второго и третьего блоков пере- , записи, выходы которых соединены со-, ответственно с входами реверсивного и вычитающего счетчиков, управляющий вход вычитающего счетчика соединен с вторым выходом управляемого делителя частоты, управляющий вход которого соединен с первым входом установки преобразователя, а тактовый вход - с выходом элемента И и счетным входом реверсивного счетчика, входы элемента И соединены со у ,tjответственно с выходами генератора импульсов и триггера, первый и второй входы которого соединены соответственно с входом запуска преобразователя и выходом дешифратора нуля, выходы которого соединены с выходами вычитающего счетчика, входы второго блока перезаписи соединены с первой группой выходов блока формирования начального кода,, вторая группа выходов которого подключена к первой группе входов вычитающего блока, выходы которого соединены с входами третьего блока перезаписи, входы блока формирования начального кода и вторая труппа входов вычитающего блока соединены с входами дешифратора и регистра соответственно, вход установки регистра соединен с вторым установочным входом преобразователя и входом установки в О реверсивного счетчика, выходы которого являются выходами преобразоваО теля, отличающийся тем. со со что, с целью повьш1ения быстродействия, в него введен блок анализа знасо ка разности аргументов, первьп и второй выходы которого соединены соответственно с выходом знакового .разряда вычитающего блока и третьим выходом управляемого делителя частоты, первый и второй выходы блока анализа знака разности аргументов подклю ены соответственно к входам сложения и вычитания реверсивного счетчика. 2. Преобразователь по п. 1, отличающийся тем, что блок анализа знака разности аргументов содержит три элемента НЕ и элемент

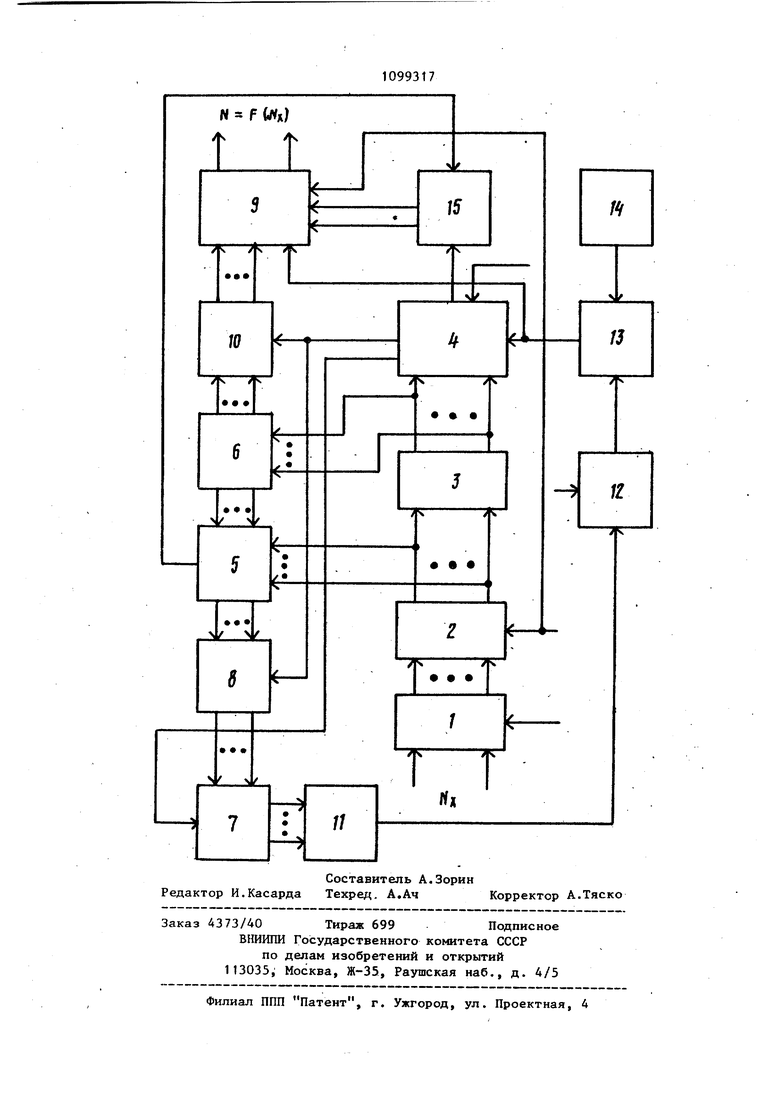

Изобретение относится к вычислительной технике. Известен функциональный преобразователь, содержащий два блока памя ти, генератор импульсов, дополнительньй генератор импульсов, два генератора ступенчатого напряжения, блок вьщеления временного интервала матрицу совпадений и многозвенный потенщ1альный элемент ij . Однако такое устройство сложно, обладает низким быстродействием и не может воспроизводить участки с отрицательной первой производной. Наиболее близким по технической сущности к предлагаемому является функциональный преобразователь, содержащий регистр, блоки перезапис дешифратор, блок формирования начального кода, вычитакяций счетчик, реверсивный счетчик, блок анализа кода на нуль, триггер, элемент И, генератор импульсов, вычитаннций блок, . управляемый делитель частоты причем первьй и второй выходьГ уп-равляемого делителя частоты соединены соответственно с входами Сложение и Вычитание реверсивного счетчика 2J . Недостатком данного преобразователя является его низкое быстродейс вие. Цель изобретения - повьшение быстродействия устройства. Поставленная цель достигается те что в цифровой функциональный преобразователь, содержащий генератор импульсов, три блока перезаписи, .регистр, дешифратор, управляемый д литель частоты,реверсивный счетчик блок формирования начального кода, вычитаю1ций блок вычитающий счетчик дешифратор нуля, триггер и элемент причем управляющий вход и информационные входы первого блока перезаписи соединены соответственно с управляющим йходом и информационными входами преобразователя, выходы первого блока перезаписи через регистр и дешифратор соединены с входами управляемого делителя частоты первьй выход которого соединен с управляющими входами второго и третьего блоков перезаписи, выходы которых соединены соответственно с входами реверсивного и вычитающего счетчиков, управляющий вход вычитающего счетчика соединен с вторым выходом управляемого делителя частоты, управлякяций вход которого соединен с первым входом установки преобразователя, а тактовый вход с выходом элемента И и счетным входом реверсивного счетчика, входы элемента И соединены соответственно с выходами генератора импульсов и триггера, первый и второй входы которого соединены соответственно с входом запуска преобразователя и выходом дешифратора нуля, входьГкоторого соединены с выходами вычитающего счетчика, входы второго блока перезаписи соединены с первой группой выходов блока формирования начального кода, вторая группавыходов которого подключена к первой группе входов вычитающего блока, выходы которого соединены с входами третьего блока перезаписи, входы блока формирования начального кода и вторая группа входов вычитающего блока соединены с выходами Дешифратора и регистра соответственно, вход установки регистра соединен с вторым установочным входом преобразователя и входом установки в О реверсивного счетчика, выходы которого являются выходами преобразователя, дополнительно введен блок ана лиза знака разности аргументов, пер вый и второй входы которого соединены соответственно с выходом зна кового разряда вычитающего блока.и третьим выходом управляемого делителя частоты, первый и второй вЫход блока анализа знака разности аргументов подключены соответственно к входам сложения и вычитания реверсивного счетчика. Блок анализа знака разности аргу ментов содержит три элемента НЕ и элемент 2И-ИЛИ-НЕ, причем первый вход блока анализа знака разности аргументов соединен с первым входом элемента 2И-ИЛИ-НЕ, и через первьй элемент НЕ - с вторым входом элемента 2И-ИЛИ-НЕ, второй вход блока анализа знака соединен с третьим входом элемента 2И-ИЛИ-НЕ и через второй элемент НЕ - с четвертым входом элемента 2И-ИЛИ-НЕ, выход которого соединен через третий элемент НЕ с первым выходом блока второй вькод которого соединен с вы ходом элемента 2И-ИЛИ-НЕ. На чертеже представлена блок-схе ма преобразователя. Преобразователь содержит блок 1 перезаписи, регистр 2, дешифратор 3 управляемый делитель 4 частоты, вычитающий блок 5, блок 6 формировани начального кода, вычитакиций счетчик 7, блок 8 перезаписи, реверсивный счетчик 9, блок 10 перезаписи, дешифратор 11 нуля, триггер 12, элемент 13 И, генератор 14 импульсо и блок 15 анализа знака разности аргументов. Блоки 1, 10, 8 перезаписи представляют собой группы двухвходовых элементов И, первые входы которых служат входами блоков перезаписи, а вторые соединены между собой и служат управляющим входом. Выходами блоков перезаписи являются выходы этих элементов. Дешифратор 3 представляет собой комбинационную логическую схему, которая определяет заданньп коэффициент деления делителя 4 частоты в зависимости от кода аргумента , соответствующего определенному участку воспроизводимой кусочно линейной функции. Эта схема вьщает сигнал, например, в виде логической единицы, на некотором выходе при коде равном или большем определенного кода аргумента, а при коде меньшем чем это значение кода аргумецта - сигнал логического нуля. Структура схемы определяется структурой разбиения функци на участки линейной зависимости. Делитель 4 частоты представляет собой двоичный счетчик с запоминающими и логическими элементами для установки заданного коэффициента деления с поступлением импульса установки и определения знака наклона участка линейности. Вычитакщий блок 5 представляет собой двоичный сумматор с логическими элементами для формирования абсолютного значения разности аргументов. Блок 6 формирования начального кода может быть комбинационной логической схемой иди постоянным запоминающим устройством. Входным узлом преобразователя является регистр 2, в который через блок 1 перезаписи записывается код аргумента Ny. Цикл преобразования начинается с приходом импульса установки исходного состояния, который устанавливает регистр 2 и счетчик 9 в исходное нуле- вое состояние. С интервалом времени, который определяется переходными .процессами в регистре 2, на блок 1 перезаписи поступает управляю1ций импульс, который записывает в регистр 2 код аргумента N, С регистра 2 код аргумента поступает на вычитающий блок 5 и дешифратор 3. С выхода дешифратора 3 сигналы поступают на делитель 4 частоты и блок 6 формирования начального кода, который, в свою очередь, вьдает значения начальных кодов аргумента и функции, соответствующих определенному участку линейности воспроизводимой кусочно-линейной функции. С выхода блока 6 формирования начального кода начальный код поступает на блок 10 перезаписи и вычитающий блок 5, который вычитает из заданного значения аргумента в регистре 2 начальное значение аргумента соответствующего участка. Абсолютное значение результата вычитания R с вычитающего блока 5 поступает на блок 8 перезаписи. По управляющему сигналу для управляемого делителя 4 устанавливается соответствующий коэффициент деления. Проходя через управляемый делитель 4 частоты на его второй выход этот, сигнал осуществляет занесение начального значения функции через блок 10 перезаписи в реверсивный счетчик 9 и занесение кода R через блок 8 перезаписи в вычитающий счетчик 7. Блок -15 анализа знака разности . аргументов по полученному знаку величины R из. вычитающего блока 5 и по сигналу с делителя 4 частоты, соответствующему знаку угла наклона участка, устанавливает для ревер синного счетчика 9 или режим Сложения или режим Вычитания. Причем если знак разности R Плюс и знак угла наклона участка Плюс, то для счетчика устанавливается режим .Сложения. Если же знак R Плюс, а знак угла наклона Минус, то для реверсивного счетчика 9 устанавливается режим Вычитания. Для случая, когй .знак R Минус, а знак угла наклон принимает значения Плюс и Минус блок 15 анализа знака разности аргументов устанавливает соответственно режимы Вычитаний и Сложения. При поступлении импульса запуска на триггер 12, он устанавливает ся в единичное состояние. Через эле мент И 13 на-входы управляемого дел теля 4 частоты и реверсивного счетч ка 9 начинают поступать импульсы с периодом TQ генератора 14 импульсов На выходе управляемого делителя 4 частоты возникает последовательность импульсов с периодом. т; к; Т , где К; - коэффициент для деления частоты для соответствующего i -го участка. Эти импульсы поступают на вход вычитающего счетчика 7. Когда вычитанлций счетчик 7, под действием импульсов делителя частоты, обнуляе ся, на выходе дещифратора 11 нуля возникает сигнал, устанавливающий триггер 12 в исходное состояние. Пр этом прекращается поступление через элемент И 13 импульсов с генератора 14 импульсов на вход управляемого делителя 4 частоты и реверсивного счетчика 9. В реверсивном счетчике 9 регистрируется код, который являт ,ется функцией аргумента (Nj() . Устройство-прототип при выборе начальных значений аргумента и функции, как координат точки, лежащей на середине участка линейности, правильно работать не может, поскольку в этом случае для определения значений функтдий в различных точках заданного участка необходимы режимы и Сложения и Вычитания импульсов в реверсивном счетчике, а устройство обеспечивает для всех точек участка лищь один, определенный по знаку угла наклона участка, режим работы. Это приводит к тому, что в точках, лежащих справа от точки определяющей начальные значения, функция вычисляется верно, а в точках которые лежат слева - неверно. Необходим анализ взаимного расположения точки, в которой вычисляется значение функции и точки в которой задаются начальные значения. Результатом этого анализа должен являться правильно установлениый режим работы реверсивного счетчика. Очевидно, что расположение точек можно-анализировать по знаку разности R их аргументов. Если R О, точка, в которой определяется значение функции, лежит справа, если - то слева. Максимальное время t,, необходимое для определения значения функции на том же участке предлагаемым устройством, равно 11 ,. (Mx,i-f-l- lx,0 max 5 где N, i и %, i+1 - значения аргумента в начальных точках i-ro и j(i+1)-ro отрезков. Для прототипа Ь„д,Тд (N , i+1-N ,2). Таким образом, быстродействие предлагаемого устройства в 2 раза выше, чем устройства-прототипа. Это релает возможным снизить требования к быстродействию элементной базы и, как следствие, снизить требования к линиям связи и монтажу, что ведет к удешевлению и упрощению устройства при его практической реализации.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Функциональный преобразователь | 1973 |

|

SU473195A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Цифровой функциональный преобразователь | 1977 |

|

SU684552A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-06-23—Публикация

1980-01-07—Подача