Изобретение относится к автоматике и вычислительной технике и може быть использовано для связи аналоговых источников информации с цифровым вычислительным устройством.

Цель изобретения -упрощение преобразователя путем использования одного блока функционального преобразования кода в код для каналов точного и грубого отсчетов.

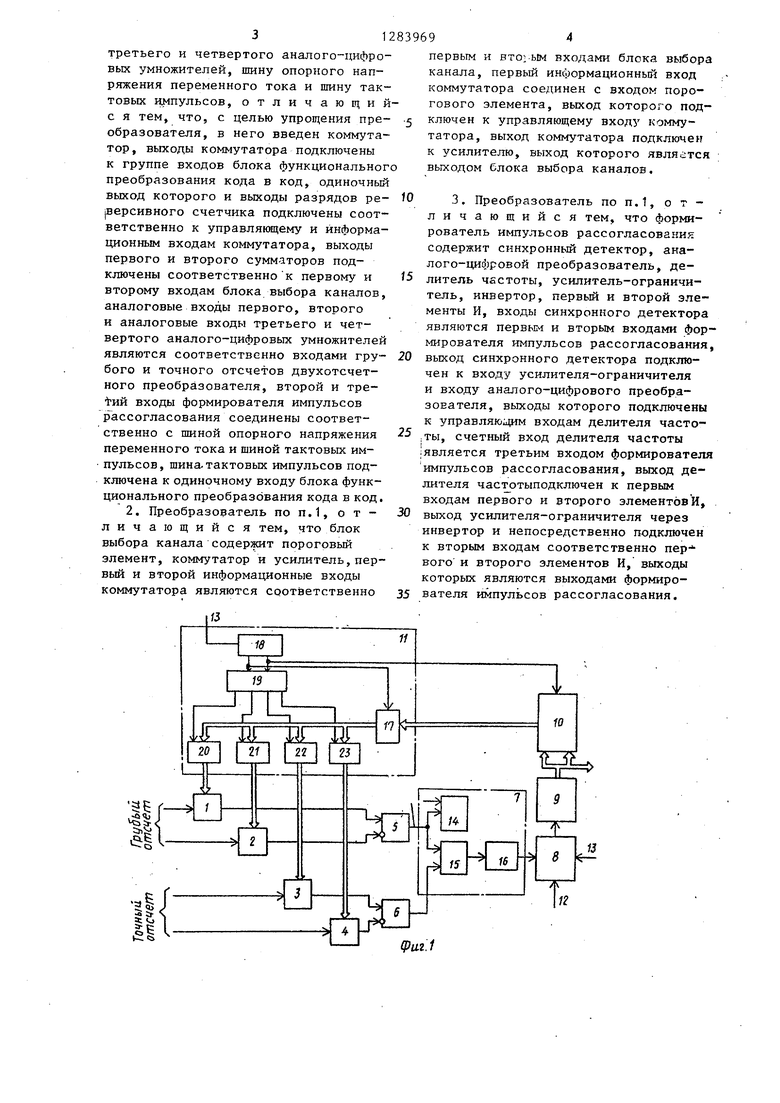

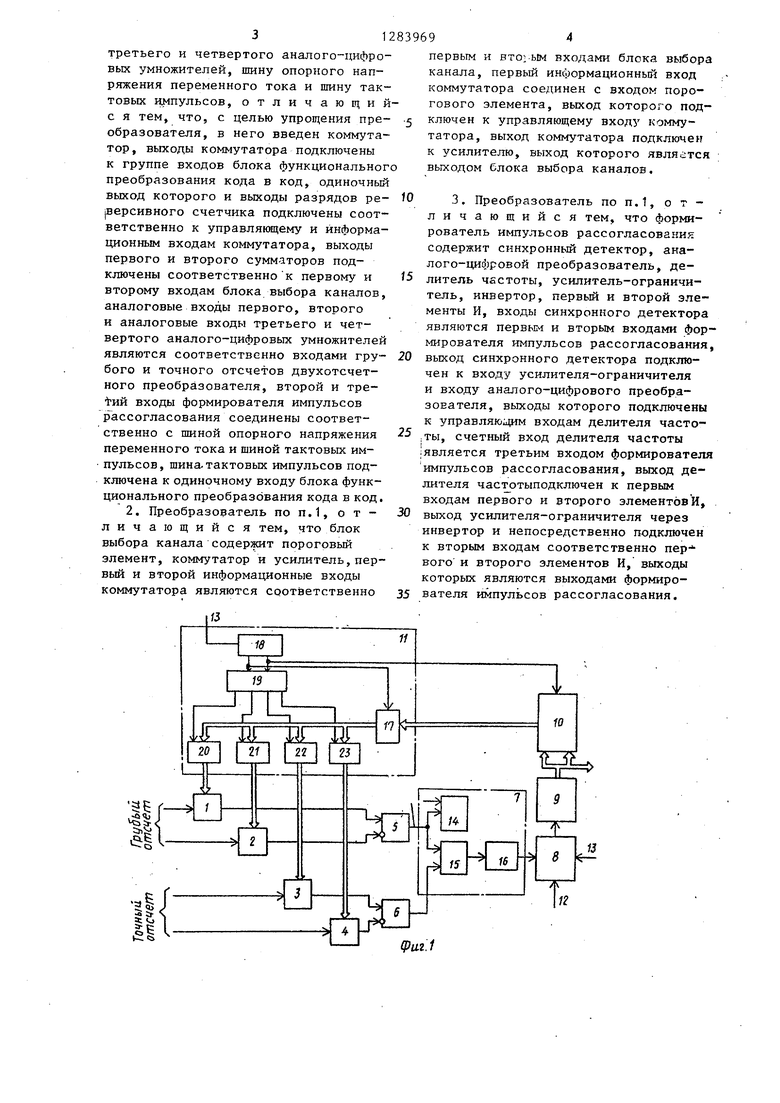

На фиг. 1 представлена структурна схема двухотсчетного преобразователя на фиг,2 - структурная схема формирователя импульсов I - рассогласования

Двзгхотсчетный преобразователь 1(фиг.1) содержит первый 1, второй 2, третий-3 и четвертый 4 аналого-цифровые умножители, первый 5 и второй 6 сумматоры, блок 7 выбора канала, формирователь 8 импульсов рассогласова- ния, реверсивный счетчик 9, коммутатор 10, блок 11 функционального преобразования кода в код, пшну 12 опорного напряжения переменного тока и пшну 13 тактовых импульсов. Блок 7 выбора канала (фиг.1) содержит пороговый элемент 14, коммутатор 15 и усилитель 16. Блок 11 функциональног преобразования кода в код (фиг.1) содержит блок 17 памяти, счетчик 18, дешифратор 19, первый 20, второй 21, третий 22 и четвертый 23 регистры. Формирователь 8 импульсов рассогласования (фиг«2) содержит синхронный детектор 24, аналого-цифровой преобразователь 25, делитепь 26 частоты усилитель-ограничитель 27, инвертор 28, первый 29 и второй 30 -элементы И Двухотсчетный преобразователь работает следующим образом.

На входы грубого и точного отсчетов преобразователя поступают баланс но-модулированные сигналы в функзщи синуса и косинуса угла d

U,.U sinoL Uj UrtSinPoi

U,i UnCOSot Ui UnCOSPdL,

где Un U sino5t - опорное напряжение; P - коэффициент редукции

между грубым и точны « отсчетами.

В реверсивном счетчике 9 формируется кодовый эквивалент N угла . Старшие N или младшие N разряды

1

1р ,, -.

реверсивного счетчика 9.через коммутатор 10 поступают на группу входов блока 11, в котором поочередно по сигналам дешифратора 19 формируюся коды косинуса cos NC и синуса sin N J, грубого отсчета и коды коси

9

нуса

cosNj и Эти

2

синуса sinN точного

sinN,,. На формируются

отсчета. коды запоминаются в выходных регистрах 20-23 блока 11„ Управление коммутатором 10 производится выходным сигналом счетчика 18. В аналого-цифровых умножителях 1 и 2 производится перемножение сигналов и , и Uj на коды cosN(.H sinN, соответственно, а в умножителях 3 и 4 - сигналов U-J и Ц, на коды cosN, и выходе сумматоров 5 и 6

сигналы

Sin (Ы-N ), Ug Un s in (Ш -N), равные разности выходных сигналов аналого-цифровых умножителей 1-4 соответственно.

При -больших углах рассог 1дсования между оС и N пороговьй элемент 14 подключает на выход блока 7 усиленное напряжение U . Блок 8 формирует на одном-из своих выходов импульсы в зависимости от фазы выходного сигнала блока 7. Частота выходных импульсов формирователя 8 пропорциональна амплитуде выходного сигнала блока 7. Реверсивный счетчик 9 от

рабатывает рассогласованиеoi -N малом значении ot-Nj, срабатывает

, При

почерез

16 . Рероговый элемент 14 и подключает коммутатор 15 к входу усилителя выходное напряжение сумматора 6, версивньй счетчик 9 отрабатывает рассогласование . В результате на выходах разрядов реверсивного счетчика 9 формируется кодовый эквивалент N угласт .

Формула изобретения

0

40

1. Двухотсчетный преобразователь синусно-косинусно-модулированных сигналов переменного тока в код, содержащий первый и второй аналого- цифровые умножители, выходы которых

45 подключены к входам первого сумматора, третий и четвертый аналого-тдиф- ровые умножители, выходы которых подключены к входам второго сумматора, блок выбора канала, выход которого

50 подключен к первому входу формирователя импульсов рассогласования, выходы формирователя импульсов рассогласования подключены к входам сложения и вычитания реверсивного счет55 чика, блок функционального преобразования кода в код, первая, вторая, третья и четвертая группы выходов которого подключены к цифровым входам соответственно первого, второго.

третьего и четвертого аналого-цифровых умножителей, шину опорного напряжения переменного тока и шину тактовых импульсов, отличающий с я тем, что, с целью упрощения пре- образователя, в него введен коммутатор, выходы коммутатора подключены к группе входов блока функциональног преобразования кода в код, одиночньй выход которого и выходы разрядов ре- |версивного счетчика подключены соответственно к управляющему и йнформа- ционньгм входам коммутатора, выходы первого и второго сумматоров подключены соответственно к первому и второму входам блока выбора каналов, аналоговые входы первого, второго и аналоговые входы третьего и четвертого аналого-цифровых умножителей являются соответственно входами гру- бого и точного отсчетов двухотсчет- ного преобразователя, второй и тре- 5гий входы формирователя импульсов рассогласования соединены соответственно с шиной опорного напряжения переменного тока и шиной тактовых импульсов, шина тактовых импульсов подключена к одиночному входу блока функционального преобразования кода в код.

2. Преобразователь по п.1, о т - личающийся тем, что блок выбора канала содержит пороговый элемент, коммутатор и усилитель, первый и второй информационные входы коммутатора являются соответственно

if3

первым и вто;.ым входами блока выбора канала, первый информационный вход коммутатора соединен с входом порогового элемента, выход которого подключен к управляющему входу коммутатора, выход коммутатора подключен к усилителю, выход которого является выходом блока выбора каналов.

3, Преобразователь по п.1, о т - личающийся тем, что формирователь импульсов рассогласования содержит синхронный детектор, аналого-цифровой преобразователь, делитель частоты, усилитель-ограничитель, инвертор, первьш и второй элементы И, входы синхронного детектора являются первьм и вторьм входами формирователя импульсов рассогласования выход синхронного детектора подключен к входу усилителя-ограничителя и входу аналого-цифрового преобразователя, выходы которого подключены к управляющим входам делителя часто- ;ТЫ, счетный вход делителя частоты является третьим входом формирователя импульсов рассогласования, выход делителя частртыподключен к первым входам первого и второго элементбвИ, выход усилителя-ограничителя через инвертор и непосредственно подключен к вторым входам соответственно пер- вого и второго элементов И, выходы которых являются выходами формирователя импульсов рассогласования.

«Рдг.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Двухотсчетный преобразователь угла поворота вала в код | 1977 |

|

SU734776A1 |

| Двухотчетный преобразователь углового перемещения в цифровой код | 1975 |

|

SU526932A1 |

| Двухотсчетный преобразователь угла поворота вала в код | 1977 |

|

SU732955A1 |

| Преобразователь угла поворота вала в код | 1985 |

|

SU1279068A1 |

| Преобразователь балансно-модулированных сигналов переменного тока в код | 1986 |

|

SU1349006A1 |

| Преобразователь балансно-модулированных сигналов переменного тока в код | 1985 |

|

SU1283970A1 |

| Двухотсчетный преобразователь угла поворота вала в код | 1985 |

|

SU1269265A1 |

| Двухотсчетный преобразователь углапОВОРОТА ВАлА B КОд | 1979 |

|

SU840995A1 |

| Преобразователь перемещения в код | 1988 |

|

SU1531221A1 |

| Преобразователь угла поворота вала в код | 1986 |

|

SU1320902A1 |

Изобретение относится .к области автоматики и вычислительной техники и может быть использовано для связи аналоговых источников информации с цифровым вычислительным устройством. ;С целью упрощения преобразователя путем использования одного блока функционального преобразования кода в код для каналов точного и-грубого отсчетов, в преобразователь, содержащий первый, второй, третий и .четвертый аналого-цифровые умножители, первый и второй сумматоры, блок выбора ка- нала, формирователь импульсов рассогласования, реверсивный счетчик. блок функционального преобразования кода в код, шину опорного напряжения переменного тока и шину тактовых импульсов, введен коммутатор, который :подключает к входам блока функционального преобразования кода в- код попеременно старшие и младшие разряды реверсивного счетчика. Блок функционального преобразования кода в код поочередно формирует коды косинуса и синуса для старших и младших разрядов реверсивного счетчика.При больших рассогласованияхмежду углом и кодомК блок выбора канала подключает кформирователю импульсов рассогласования сигнал переменного тока,пропорциональный синусуразности междууглом грубого отсчета икодом старших разрядов реверсивного счетчика. Код старших разрядов реверсивного счетчика изменяется до устранения рассогласования. Затем к формирователю импульсов рассогласования автоматически подключается сигнал рассогласования между углом точного отсчета и кодом младших разрядов реверсивного счетчика. В результате на выходах реверсивного счетчика формируется кодовый эквивалент угла . 2 з.п. ф-лы, 2 ил. (Л

| Преобразователь уга поворота вала в код | 1976 |

|

SU595755A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Датчики в цифровых системах,/Перевод с англ.под.ред | |||

| А.С.Яроменка; М.: Энергоиздат, 1981, с.158, рис.6.15. | |||

Авторы

Даты

1987-01-15—Публикация

1985-06-26—Подача