(54) СЛЕДЯЩИЙ УМНОЖИТЕЛЬ ЧАСТОТЫ

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегратор азимутных импульсов | 1977 |

|

SU691877A2 |

| Интегратор азимутных импульсов | 1977 |

|

SU732907A1 |

| Преобразователь частоты в код | 1978 |

|

SU744974A1 |

| Интегратор азимутных импульсов | 1977 |

|

SU736123A2 |

| Следящий умножитель частоты | 1977 |

|

SU732866A1 |

| Умножитель частотно-импульсных сигналов | 1981 |

|

SU968812A1 |

| Цифровой линейный экстраполятор | 1979 |

|

SU868769A1 |

| Устройство для интегрирования частотно-импульсных сигналов | 1984 |

|

SU1160444A1 |

| Интегратор импульсов | 1978 |

|

SU750508A1 |

| Умножитель частоты | 1980 |

|

SU868756A1 |

Изобретение относится к автоматик и вычислительной технике и может быт использовано, в частности, в импульсных системах для преобразования информации, представленной в частотн импульсной форме. Известен умножитель частоты, содержащий блоки перераспределения и выделения разности периодов, реверсивный счетчик, преобразователь коднапряжение, делители частоты, генератор управляемой частоты, триггеры, инвертор и элементы И и ИЛИ 1 . Недостаток устройства - пониженная точность. в Известен также следящий умножител частоты, содержащий измеритель рассогласования, генератор импульсов, триггер, элемент И, счетчик, реверсивньай счетчик, дешифратор и управля емые делители частоты 2. Недостаток этого устройства - низкое быстродействие за счет значительного времени отработки больших приращений входной частоты. Наиболее близким к предлагаемому является следящий умножитель частоты содержащий измеритель рассогласования первый вход которого подключен к пер вому импульсному входу блока коррекции и к шине ввода умножаемой частоты, а выходы - к входам модуля и знака рассогласования блока управления, соединенного входом коррекции с выходом блока коррекции, входом опорной частоты - с выходом генератора импульсов, а выходами - с управляющими входами первого управляемого делителя частоты и с кодовыми входами блока коррекции, подключенного вторым импульсным входом к выходу генератора импульров и к сигнальному входу первого управляемого делителя частоты, выход которого соединен с выходной шиной следящего умножителя частоты и с входом делителя частоты, подключенного выходом к второму входу измерителя рассогласования. .Блок управления содержит элемент.И и реверсивный счетчик, выходы которого являются выходами блока управления, вход управления реверсом - входом знака рассогласования блока управления, а счетный вход подключен к выходу элемента и, первый, второй и третий входы которого соответственно являются входом коррекции, входом опорной частоты и входом модуля рассогласования блока управления. Блок коррекции содержит триггер и счетчик,

подключенный выходом переполнения к первому входу триггера, второй вход которого соединен с входом управления установкой кода счетчика и является первым импульсным входом блок коррекции, а выход триггера является рыходом блока коррекции, установочные входы счетчика - кодовыми входам блока коррекции 3,

Недостаток устройства - низкое быстродействие, обусловленное значительным временем отработки больших приращений умножаемой частоты.

Цель, изобретения - повышение быстродействия.

С этой целью в следящий умножител частоты, содержащий измеритель рассогласования, первый вход которого подключен к первому импульсному вход блока коррекции и к шине ввода умножаемой частоты, а выходы - к входам модуля и знака рассогласования блока управления, соединенного входом коррекции с выходом блока коррекции, входом опорной частоты - с выходом генератора импульсов, а выходами с управляющими входами первого управляемого делителя частоты и с кодовыми входами блока коррекции, подключенного вторым импульсным входом к выходу ге.нератора импульсов и к сигнальному входу первого управляемого делителя частоты, выход которого соединен с выходной шиной следящего умножителя частоты, дополнительно введены блок уставки управления и второй управляемый делитель частоты, подключенный сигнальным входом к выходу первого управляемого делителя частоты, управляющими входами - к шине ввода кода коэффициента умножения и к кодовым выходам блока уставки управления,а выходом-к второму входу измерителя рассогласования, причем блок уставки управления соединен первым импульсным входом с шиной ввода умножаемой частоты вторым импульсным входом - с выходом генератора импульсов, а выходами с входами кода уставки блока управления.

Блок уставки управления содержит управляемый делитель частоты, подключенный выходом к счетному входу счетчика, соединенного входом обнуления с выходом элемента задержки, входом управления считыванием - с входом элемента задержки,а выходамис входами регистра, выходы которого являются выходами блока управления, причем вход, элемента задержки и сигнальный вход управляемого делителя частоты являются соответственно первым и вторым импульсными входами блока уставки управления, а упрайляющие входы управляемого делителя ча,стоты - кодовыми входами блока ус-, тавки управления.

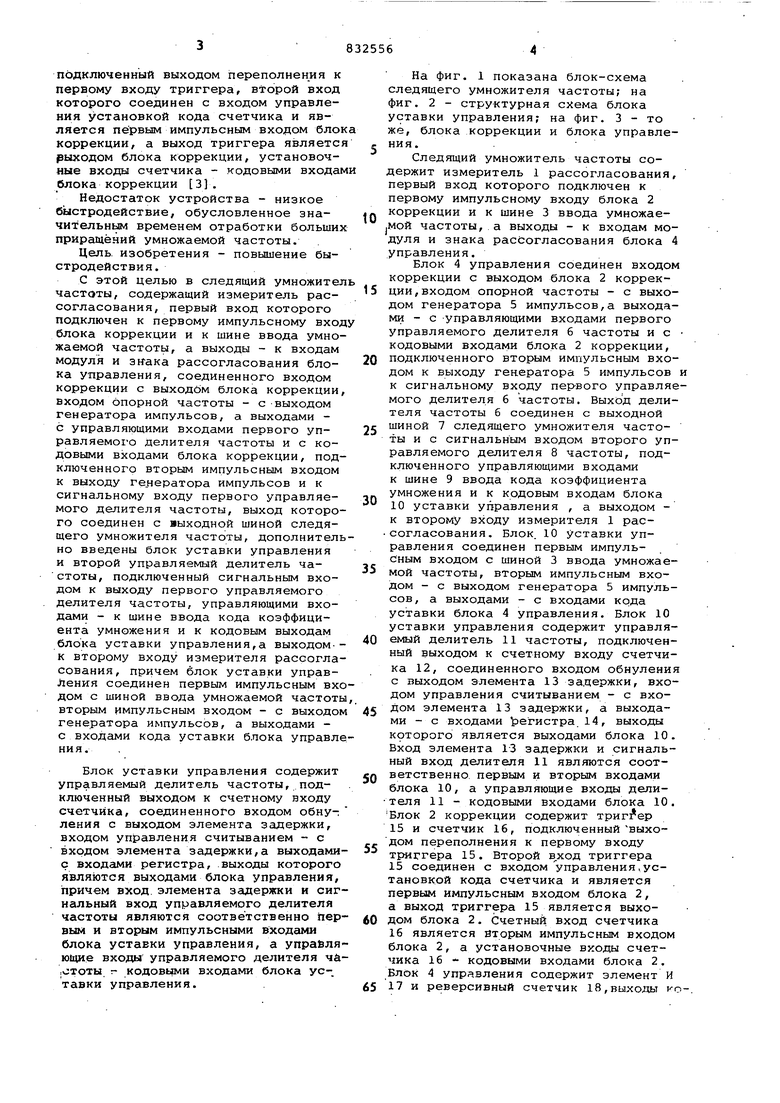

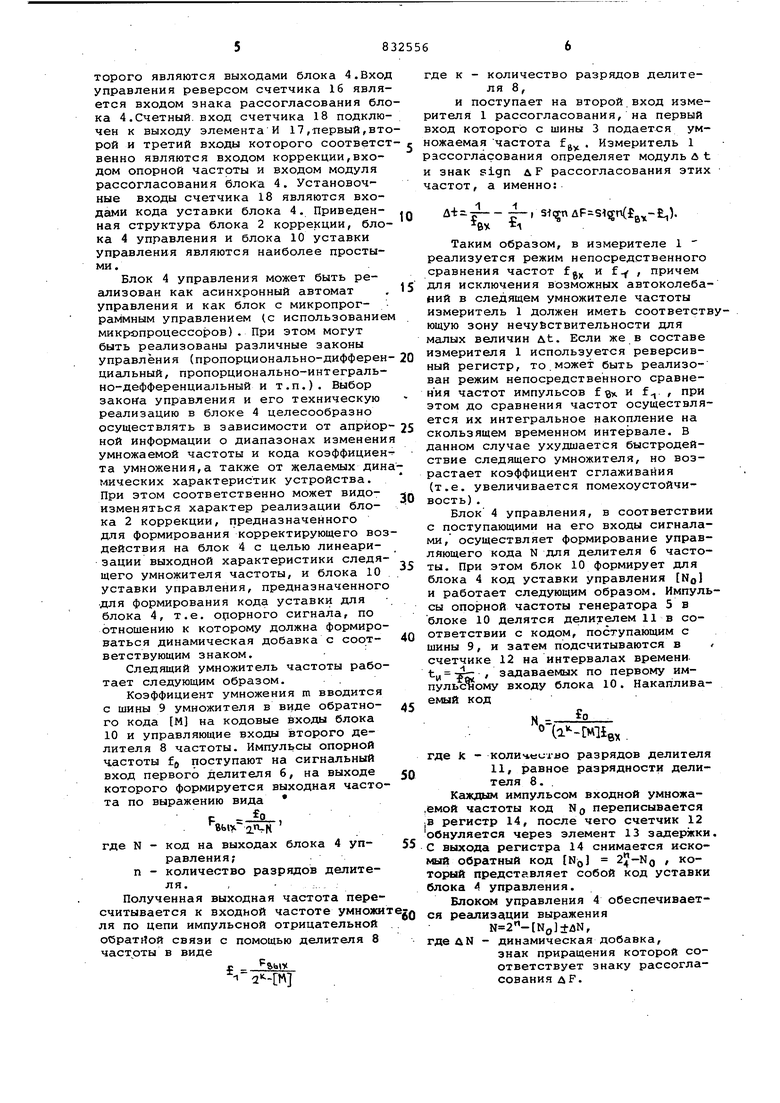

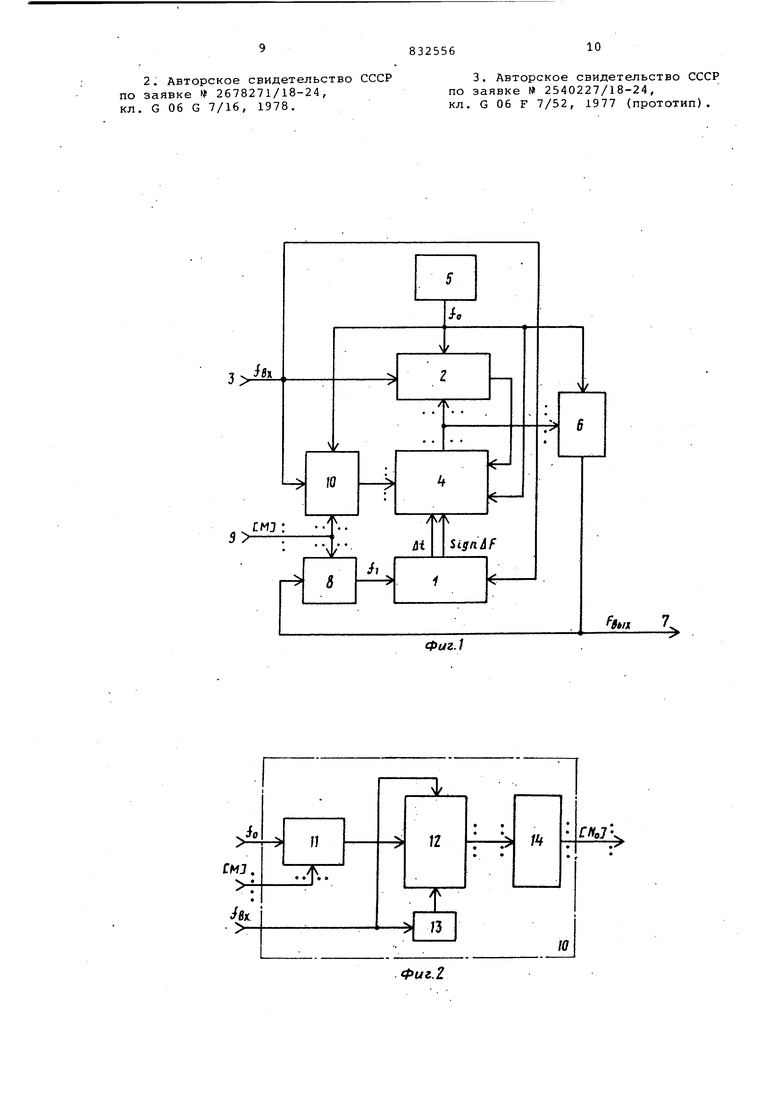

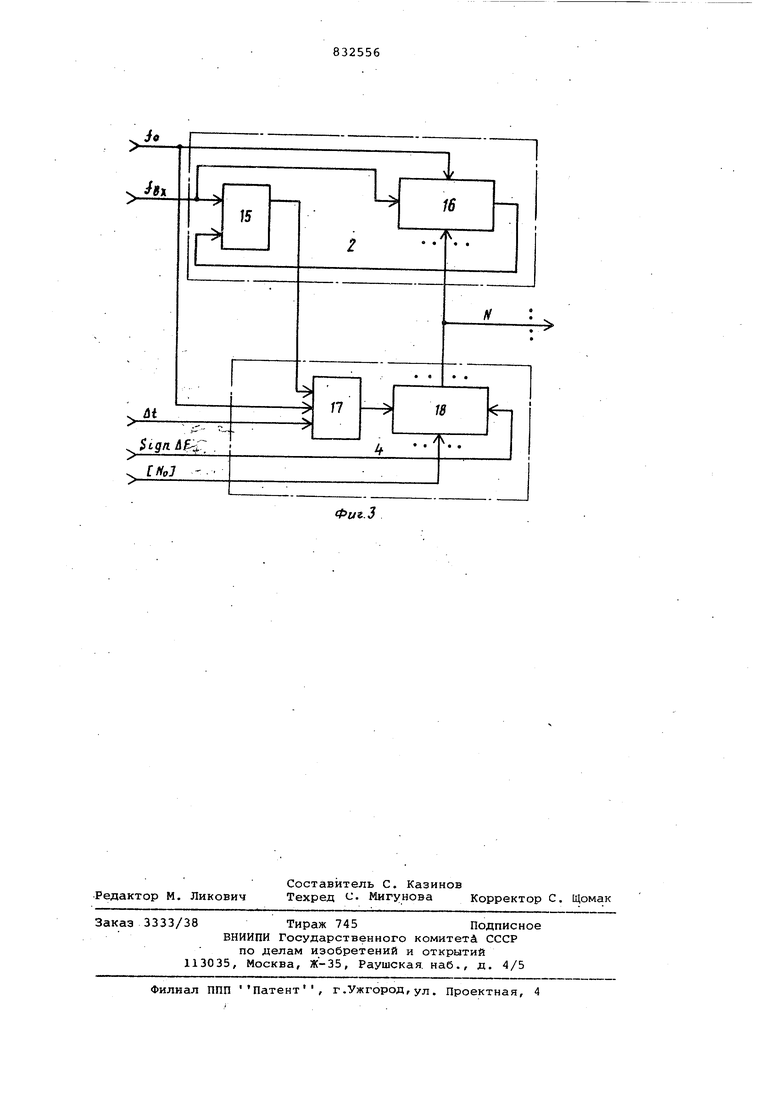

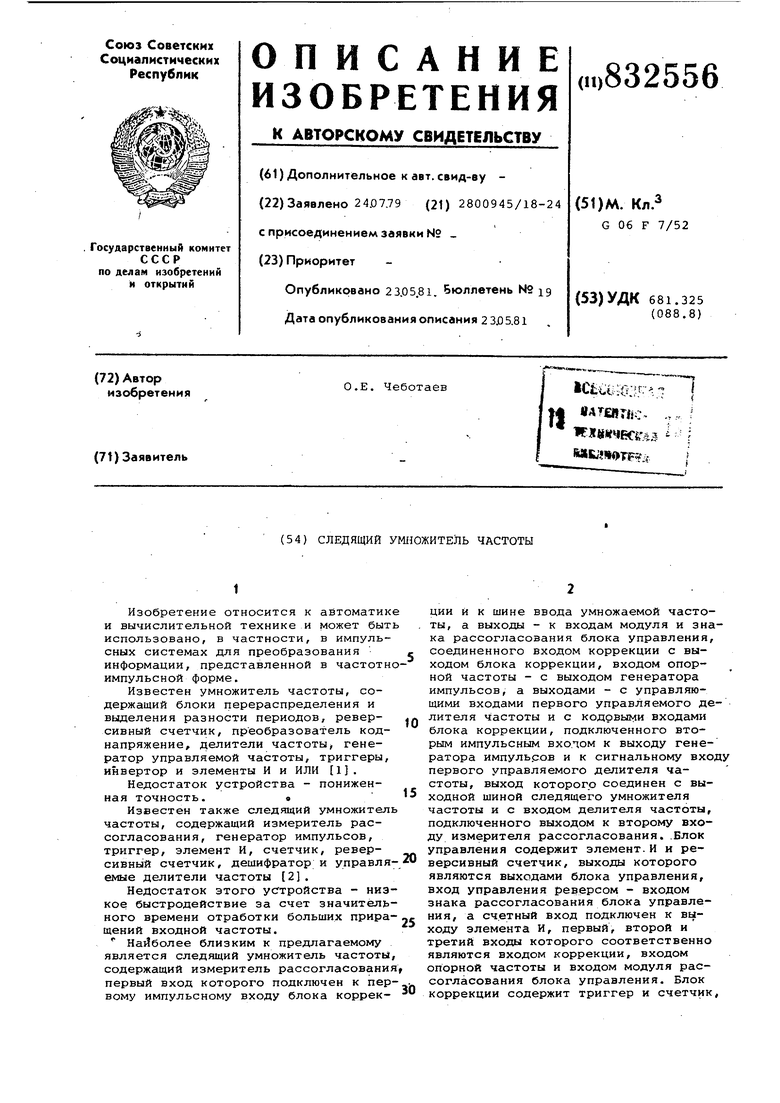

На фиг. 1 показана блок-схема следящего умножителя частоты; на фиг. 2 - структурная схема блока уставки управления; на фиг. 3 - то же, блока коррекции и блока управления.

Следящий умножитель частоты содержит измеритель 1 рассогласования, первый вход которого подключен к первому импульсному входу блока 2 коррекции и к шине 3 ввода умножае.мой частоты, а выходы - к входам модуля и знака рассогласования блока 4 управления.

Блок 4 управления соединен входом коррекции с выходом блока 2 коррекции, входом опорной частоты - с выходом генератора 5 импульсов,а выходами - с управляющими входами первого управляемого делителя б частоты и с кодовыми входами блока 2 коррекции, подключенного вторым импульсным входом к выходу генератора 5 импульсов к сигнальному входу первого управляемого делителя 6 частоты. Выход делителя частоты 6 соединен с выходной шиной 7 следящего умножителя частоты и с сигнальным входом второго управляемого делителя 8 частоты, подключенного управляющими входами к шине 9 ввода кода коэффициента умножения и к кодовым входам блока 10 уставки управления , а выходом к второму входу измерителя 1 рассогласования. Блок. 10 уставки управления соединен первым импульсным входом с шиной 3 ввода умножаемой частоты, вторым импульсным входом - с выходом генератора 5 импульсов, а выходами - с входами кода уставки блока 4 управления. Блок 10 уставки управления содержит управляемый делитель 11 частоты, подключенный выходом к счетному входу счетчика 12, соединенного входом обнулени с выходом элемента 13 задержки, входом управления считыванием - с входом элемента 13 задержки, а выходами - с входами регистра 14, выходы которого является выходами блока 10 Вход элемента 13 задержки и сигнальный вход делителя 11 являются соответственно первым и вторым входами блока 10, а управляющие входы делителя 11 - кодовыми входами блока 10 Ълок 2 коррекции содержит триггер

15 и счетчик 16, подключенныйвыходом переполнения к первому входу триггера 15. Второй триггера

15соединен с входомуправления установкой кода счетчика и является первым импульсным входом блока 2,

а выход триггера 15 является выходом блока 2. Счетный вход счетчика

16является вторым импульсным входом блока 2, а установочные входы счетчика 16 - кодовыми входами блока 2. Блок 4 управления содержит элемент И

17и реверсивный счетчик 18,выходьт кторого являются выходами блока 4.Вхо управления реверсом счетчика 16 явля ется входом знака рассогласования бл ка 4.Счетный, вход счетчика 18 подклю чен к выходу элемента И 17 ,-первый,вт рой и третий входы которого соответс венно являются входом коррекции,входом опорной частоты и входом модуля рассогласования блока 4. Установочные входы счетчика 18 являются входами кода уставки блока 4. Приведенная структура блока 2 коррекции, бло ка 4 управления и блока 10 уставки управления являются наиболее простыми . Блок 4 управления может быть реализован как асинхронный автомат управления и как блок с микропрограммным управлением (с использовани микропроцессоров). При этом могут быть реализованы различные законы управления (пропорционально-диффере циальный, пропорционально-интеграль но-дефференциальный и т.п.). Выбор закона управления и его техническую реализацию в блоке 4 целесообразно осуществлять в зависимости от апрйор ной информации о диапазонах изменени умножаемой частоты и кода коэффициен та умножения,а также от желаемых дин мических характеристик устройства. При этом соответственно может видоизменяться характер реализации блока 2 коррекции, предназначенного для формирования корректирующего во действия на блок 4 с целью линеаризации выходной характеристики следя щего умножителя частоты, и блока 10 уставки управления, предназначенног для формирования кода уставки для блока 4, т.е. оцорного сигнала, по отношению к которому должна формиро ваться динамическая добавка с соответствующим знаком. Следящий умножитель частоты рабо тает следующим образом. . Коэффициент умножения m вводится с шины 9 умножителя в виде обратного кода М на кодовые входы блока 10 и управляющие входы JBTOporo делителя 8 частоты. Импульсы опорной частоты fj поступают на сигнальный вход первого делителя 6, на выходе которого формируется выходная часто та по выражению вида р , fp SbixiVN где N - код на выходах блока 4 управления;п - количество разрядов делителя. , J. Полученная выходная частота пересчитывается к входной частоте умножи ля по цепи импульсной отрицательной оСратйой связи с помощью делителя 8 частоты в виде г E&hiv где к - количество разрядов делителя 8, и поступает на второй вход измерителя 1 рассогласования, на первый вход которого с шины 3 подается умножаемая частота f . Измеритель 1 рассогласования определяет модуль л t и знак sign дР рассогласования этих частот, а именно: , (,). Таким образом, в измерителе 1 реализуется режим непосредственного сравнения частот f f , причем для исключения возможных автоколебаний в следящем умножителе частоты измеритель 1 должен иметь соответствующую зону нечувствительности для малых величин At. Если же в составе измерителя 1 используется реверсивный регистр, то.может быть реализован режим непосредственного сравнения частот импульсов и f. , при этом до сравнения частот осуществляется их интегральное накопление на скользящем временном интервале. В данном случае ухудшается быстродействие следящего умножителя, но возрастает коэффициент сглаживания {т.е. увеличивается помехоустойчивость) . Блок 4 управления, в соответствии с поступающими на его входы сигналами, осуществляет формирование управляющего кода N для делителя 6 частоты. При этом блок 10 формирует для блока 4 код уставки управления Nol и работает следующим образом. Импульсы опорной частоты генератора 5 в блоке 10 делятся делителем 11 в соответствии с кодом, поступающим с шины 9, и затем подсчитываются в счетчике 12 на интервалах времени t, :yrJ, задаваемых по первому импульсТ10му входу блока 10. Накапливаемый код ° (a -rwii, где k - количе1;хао разрядов делителя 11, равное разрядности делителя 8. Каждым импульсом входной умножаемой частоты код Nn переписывается В регистр 14, после чего счетчик 12 бнуляется через элемент 13 задержки. выхода регистра 14 снимается искоый обратный код N(j , коорый представляет собой код уставки лока 4 управления. Блоком управления 4 обеспечиваетя реализации выражения , де AN - динамическая добавка, знак приращения которой соответствует знаку рассогласования д Р.

Величина лН равна количеству импульсов , поступивших через элемент И 17 блока 4 управления на счетный вход реверсивного счетчика 18 за время

A-b A-t--r(fg), где T(tg) - время, определяемое бло ком 2 корреляции. Блок 2 коррекции, осуществляющий коррекцию блока 4 управления, позволяет линес1ризЬвать выходную характеристику следящего умножителя (нелинейность которого обусловлена- нелинейностью характеристики первого управляемого делителя б частоты. При в области низких входных частот fg ,а также при малых значениях коэффициента умножения m корректирующее воздействие на блок 4 управления незначительно и оно возрастает с ростом fa и m , Блок 2 коррекции работает следующим образом. На установочные входы счетчика 16 блока 2 поступает код N.(e) (где S - старшие разряды этого кода с выходов блока 4 управления. В зависимости от N и fgy ,поступающей на второй вход триггера 15 (вход установки триггера в единичное состояние) , формируется импульс переполнения счетчика 16, определяющий длител ность заполнения счетчика 16 импульсами опорной частоты, начиная от момента установки в счетчике 16 кода N(P). Импульс переполнения возвраща ет триггер 15 по его первому входу в исходное обнуленное состояние. Таким образом длительность импульса коррекции на выходе триггера 15 рав t -iiM где L - емкость счетчика 16. . Выходной сигнал триггера 15 и по ступает на вход коррекции блока 4 управления. Таким образом, блок 2 коррекции осуществляет ограничение сверху при динамическом регулировании кода N в блоке 4 управления. Сформированный код N с выходов блок 4 поступает на управляющие входы делителя 6 частоты. В установившемс состоянии частота на выходной.шине устройства с точностью до статической ошибки равна Fgbix m fg , где m . Следует отметить, что в устройст с помощью блоков 2,4 и 10 образуетс сочетание двух контуров регулирования: первого - для грубого умножени частоты, второго - для точного умно жения частоты. Такое сочетание по сравнению с известными устройствами позволяет значительно уменьшить вре мя отработки больших приращений вхо ной умножаемой частоты в широком ди

пазряе изменения fg и m без ухудшения других характеристик. При этом аппаратурные затраты увеличиваются незначительно (приблизительно на Ю20%) . Формула изобретения 1.Следящий умножитель частоты, содержащий измеритель рассогласования, первый вход которого подключен к первому импульсному входу блока коррекции и к шине ввода умножаемой частоты, а выходы - к входам модуля и знака рассогласования блока управления, соединенного входом коррекции с выходом блока коррекции,входом опорной частоты - с выходом генератора импульсов , а выходами - с управляющими входами первого управляемого делителя частоты и с кодовыми входами блока коррекции, подключенного вторым импульсным входом к выходу генератора импульсов и к сигнальному входу первого управляемого делителя частоты, выход которого соединен с выходной шиной следящего умножителя частоты, отличающийся тем, что, с целью повышения быстродействия, в него дополнительно введены блок уставки управления и второй управляемый делитель частоты, подключенный сигнальным входом к выходу первого управляемого делителя частоты, управляющими входами - к шине ввода кода коэффициента умножения и кодовым входам блока- уставки управления, а выходом - к второму входу измерителя рассогласования, причем блок уставки управления соединен первым импульсньли входом с шиной ввода умножаемой частоты, вторым импульсным входом - с выходом генератора импульсов, а выходами - с входами кода уставки блока управления. 2.Умножитель по п. 1, о т л и чающийс я тем, что блок уставки управления содержит управляемый делитель частоты, подключенный выходом к счетному входу счетчиКа, соединенного входом обнуления с выходом элемента задержки, входом управления считыванием - с выходом элемента задержки,а выходами - входами регистра, выходы которого являются выходами блока уставки управления,причем вход элемента задержки и сигнальный вход управляемого делит.еля частоты являются соответственно первым и вторым импульсными входами блока уставки управления, а управляющие входы управляемого делителя частоты - кодовыми входами блока уставки управления. Источники информации, принятые SBC внимание при экспертизе 1. Авторское свидетельство СССР 475620, кл. G 06 F 7/39, 1971.

Фиг.2

Авторы

Даты

1981-05-23—Публикация

1979-07-24—Подача