. 1 . . -. Изобретение относится к импульсной технике и может найти применение в устройствах измерительной и шлчисли тельной техники, Известен измеритель длительности интервалов времени, содержащий задающий генератор, формирователи стробимпульсов Старт и Стоп, пересчетный прибор и блок индикации, удвоители частоты, строб-смесители и блок логики, причем выходы блока логики соединены со входами блока индикации , а входы - с выходами стробсмесителей, аналоговые входы которых через последовательно соединенные. удвоители частоты подключены к выходу згщающего генератора. Управляющие входы соединены с выходами формироваСтарттелей строб-импульсов (jTon 1 . Недостатком указанного устройства является сложность. Известен также цифррвой измеритель временных интервалов, содержащий последовательно соединенные пересчетные декады, выходы которых соединены со входами соответствующих дешифраторов коммутатор, выполненный нд двоичном счетчике, выходы которого соединены со входами дешифратора кода порядка; электронные ключи, вход каждого из которых соединен с шиной, соответствующей эталонной частоте, схемууправления, выходы которой соединены со входами опроса всех дешифраторов и входами сброса пересчетных декад и двоичного счетчика, триггер управления, выход которого соединен с.управляющими входами всех электронных.ключей, дифференциальную схему. Причем выход пересчетной декады старшего разряда соединен со входом двоичного счетчика и через дешифрирующую схему со входом этой же пересчетной декады, выходы двоичного счетчика соединены со входами соответствующих электронных ключей 2. Недостатком этого устройства является сложность. Наиболее близким к предлагаемому, являете цифровой измеритель интервалов времени, содержащий входной формирователь, основную линию задержки, схемы совпадения по числу отводов линии задержки и запоминающий регистр, причем в него включена дополнительная линия задержки, вход .которой соединен с одним из выходов входного формирователя, а; ее отводьа через соответствующие схемы совпадения подключены к запоминающему регистру 3 .

Недостатком известного устройства является сложность, поскольку в измерителе используется количество элементов совпадения по числу различных комбинаций отводов обеих линий задержки и соответствующее им число ячеек запоминающего регистра.

Целью изобретения является повышение надежности устройства за счет его упрощения.

Указанная цель достигается тем, что в цифровой измеритель интервалов времени, содержащий входной формирователь , основную и дополнительную линии задержки, входы которых подключены к первому и второму выходам формирователя соответственно, блок элементов совпадения, выходы которого подключены к информационным входам .основного регистра памяти, а первые входы - к выходам основной линии задержки, дополнительно введены блок элементов совпадения, регистр памяти, триггер и два элемента ИЛИ, причем г выходы основной линии задержки через первый элемент ИЛИ подключены к первому, входу дополнительного блока элементов совпадения, вторые входы которого соединены с выходами дополнительной линии задержки, первый выход входного формирователя соединен со входами сброса основного и дополнительного регистров памяти, информационные входы последнего из которых подключены к выходам дополнительного блока элементов совпадения, выходы основного блока элементов совпадения через второй элемент ИЛИ., подключены к первому входу триггера, второй вход которого соединен со вторым выходом входного формирователя, выход триггера подключен ко вторым входам основного блока элементов Совпадения.

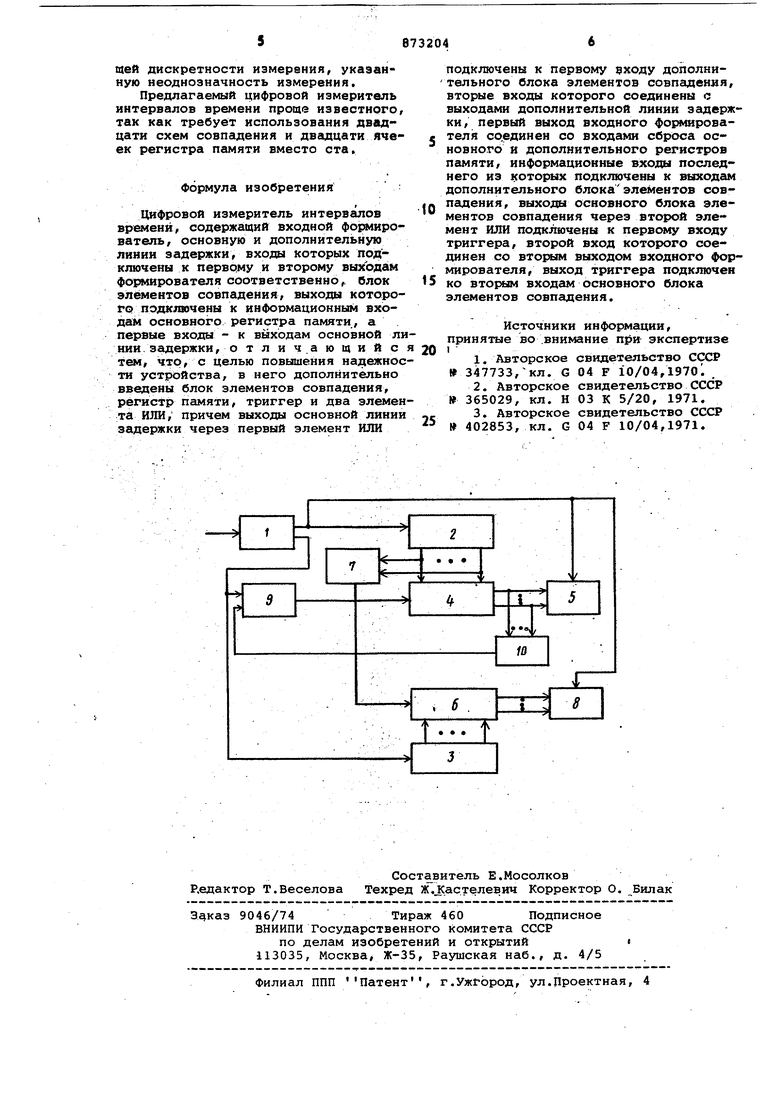

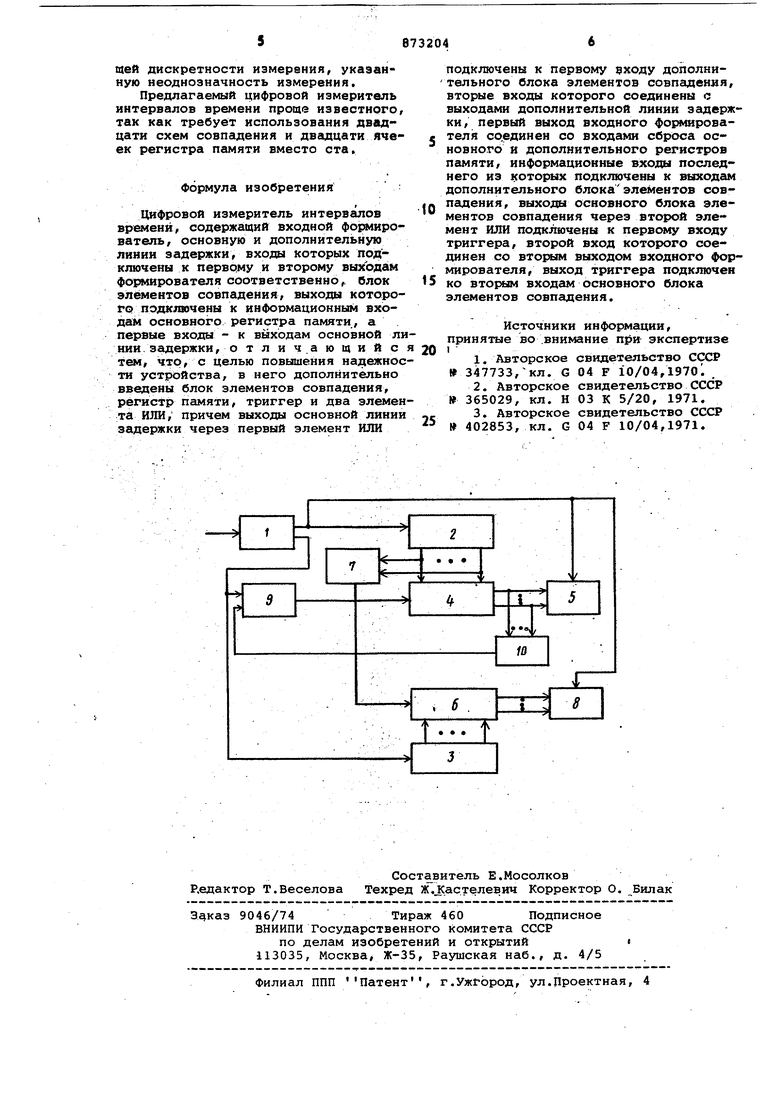

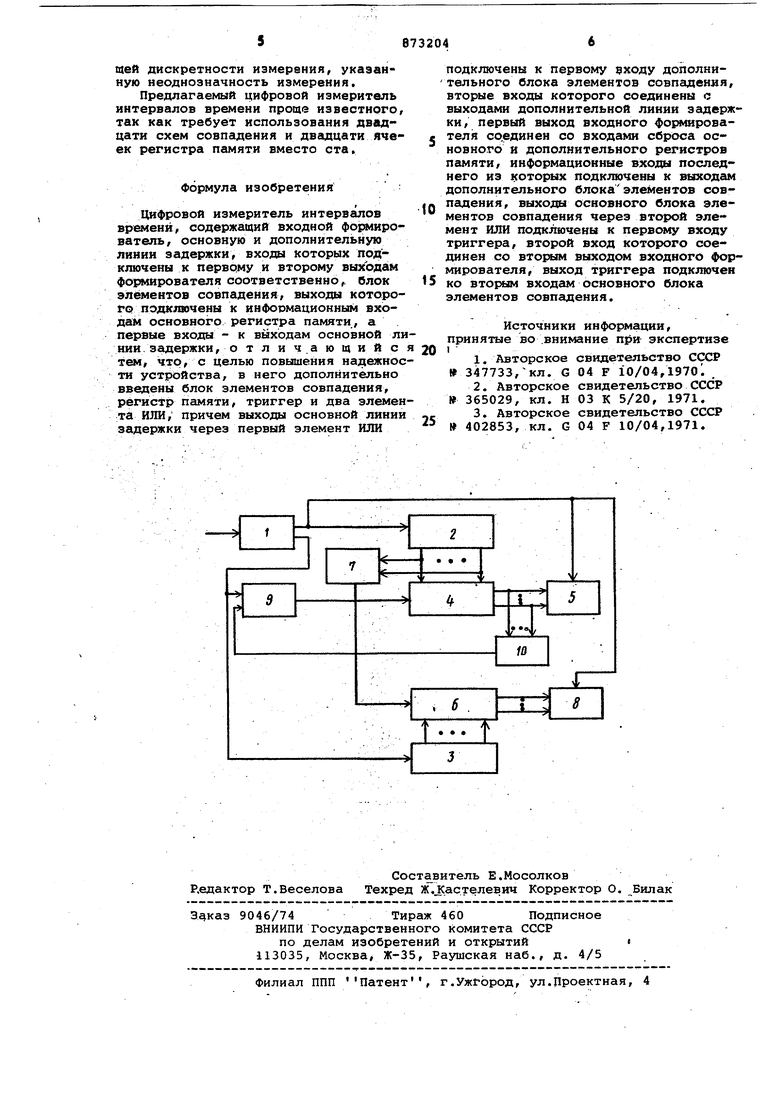

На чертеже представлена функциональная электрическая схема устройства.

Цифровой измеритель интервалов времени содержит входной формирователь 1, основную 2 и дополнительную 3 линии задержки,, подключенные к первому и второму выходам формирователя 1, основной блок 4 элементов совпадения, содержащий элементы совпадения по числу отводов основной линии задержки 2, основной регистр

5памяти с индикацией, подключенный

к выходу блока 4, дополнительный блок

6элементов совпадения содержит элементы совпадения по числу отводов дополнительной линии задержки 3, первые входы которых через элемент 7 ИЛИ соединены с выходами основной линии задержки 2, а выходы соединены с дополнительным регистром 8. памяти. Один вход триггера 9 соединен со вторым выходом входного, формирователя 1, а другой через второй элемент 10 ИЛИ с выходом блока 4, выход триггера. 9 соединен со вторым входом блока 4, входы сброса регистров памяти 5 и 8 соединены с первым выходом входного формирователя 1.

Работа устройства начинается с .поступления на вход входного формирователя 1 измеряемого интервала времени . Входной формирователь 1 формирует два импульса, соответствующие началу и концу измеряемого интервала Импульс начала измеряемогОц.интервала- подается на входы сброса регистров 5 и В памяти и приводит их в исходное нулевое состояние. Импульс начала поступает также на основную линию задержки 2, имеющую дискретность задержки Г , с отводов которой задержанные импульсы поступают на первые входы элеме.нтов совпадения блока 4,. а также через первый элемент 7 ИЛИ - на первые входы элементов совпадения блока 6.

Импульс конца измеряемого интервала подается на вход триггера 9 и переводит его.в состояние, пригкотором на выходе триггера 9 возникает скачок напряжения, который прикладывается ко вторым входам элементов совпадения блока 4 элементов совпадения При совпадении импульсного напряжения триггера 9 с одним из импульсов основной линии задержки 2 на выходе соответствующего элемента совпадения вырабатывается импульс, производящий запись в регистр 5 памяти кода, определяемого порядковым номером сработавшего элемента совпадения. Указанный импульс посредством второго элемента 10 ИЛИ, также подается на вход триггера 9, переводя его в исходное нулев 5е состояние, при котором на выходе триггера 9 скачок напряжения перестает существовать.

Импульс конца измеряемого интервала также подается на вход дополнительной линии задержки 3, имеющей дискретность , которая выбирается из условия (гделС зх i .i требуемая дискретность измерения), с отводов которой импульсы поступают на первые входы элемен.тов совпадения блока 6. Подобный -способ выбора времен задержки между отводами основной и дополнительной линии задержки позволяет с точностью, равной требуемой дискретности измерения, оценить интервал времени между появлением последнего импульса основной линии задержки (до прихода импульса конца измеряемого интервала) и импульса конца измеряемого интервала. При совпадении импульсов от двух линий задержки на входе одного из элементов совпадения блока б на его выходе появляется импульс, который производит запись в регистр 8 памяти кода, дающего возможность оценить с точностью, соответствую«ей дискретности измерения, указанную неоднозначность измерения. Предлагаемый цифровой измеритель интервалов времени проще известного так как требует использования двадцати схем совпадения и двадцати ячеек регистра памяти вместо ста. Формула изобретения Цифровой измеритель интервалов времени, содержащий входной формирователь/ основную и дополнительную линии задержки, входы которых подключены к первому и второму выходам фо1 а1рователя соответственно,, блок элементов совпадения, выходы которого подключены к информационным входам основного регистра памяти, а первые входы - к выходам основной л нии, задержки, о тлич.ающийс тем, что, с целью повышения надежнос ти устройства, в него дополнительно введены блок элементов совпадения, регистр памяти, триггер и два элемен та ИЛИ, причем выходы основной линии задержки через первый элемент ИЛИ подключены к первому еходу дополнительного блока элементов совпадения, вторые входы которого соединены о выходами дополнительной линии задержки, первый выход входного формирователя соединен со входами сброса основного и дополнительного регистров пгшяти, информационные входы последнего из 1соторых подключены к выходам дополнительного блокаэлементов совпгшения, выходы основного блока элементов совпадения через второй элемент ИЛИ подключены к первому входу триггера, второй вход которого соединен со вторым выходом входного формирователя, выход триггера подключен ко вторым входам основного блока элементов совпадения. Источники информации, принятые во .внимание прн экспертизе 1.Авторское свидетельство СССР 347733,кл. G 04 F 10/04,197о1 2.Авторское свидетельство СССР 365029, кл. Н 03 К 5/20, 1971. 3.Авторское свидетельство СССР 402853, кл. G 04 F 10/04,1971.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой частотомер с нониусной интерполяцией | 1980 |

|

SU868612A1 |

| Устройство для измерения угла закручивания вращающегося вала | 1991 |

|

SU1795312A1 |

| Цифровой измеритель частоты | 1980 |

|

SU938187A1 |

| Цифровой измеритель скважности прямоугольных импульсов | 1990 |

|

SU1725152A1 |

| Цифровой компенсационный фазометр | 1980 |

|

SU920563A1 |

| Цифровое фазосдвигающее устройство | 1984 |

|

SU1241148A1 |

| ЦИФРОВОЙ ИЗМЕРИТЕЛЬ СЕРИИ ВРЕМЕННЫХ ИНТЕРВАЛОВ | 1968 |

|

SU208038A1 |

| Измеритель длительности временных интервалов | 1980 |

|

SU949625A1 |

| Измеритель временных интервалов | 1983 |

|

SU1155990A1 |

| СЕЛЕКТОР ИМПУЛЬСОВ | 2011 |

|

RU2474043C1 |

Авторы

Даты

1981-10-15—Публикация

1979-11-15—Подача