(54) УСТРОЙСТВО ПРИЕМА РЕКУРРЕНТНОГО СИГНАЛА ФАЗОВОГО ПУСКА

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство выделения рекуррентного сигнала с обнаружением ошибок | 1986 |

|

SU1327308A2 |

| Устройство выделения рекуррентного синхросигнала с обнаружением ошибок | 1983 |

|

SU1102050A2 |

| Устройство выделения рекуррентного синхросигнала с обнаружением ошибок | 1976 |

|

SU604173A2 |

| Устройство фазового пуска | 1979 |

|

SU866773A1 |

| Устройство фазового пуска | 1986 |

|

SU1415447A2 |

| Устройство для приема рекуррентного сигнала фазового пуска | 1990 |

|

SU1730732A1 |

| Устройство фазового пуска | 1984 |

|

SU1282347A1 |

| Устройство для выделения рекуррентного синхросигнала | 1983 |

|

SU1116547A1 |

| Анализатор рекуррентного сигнала фазового пуска | 1981 |

|

SU995361A2 |

| Приемник рекуррентных последовательностей | 1985 |

|

SU1256232A1 |

I

Изобретение относится к технике связи и может использоваться в аппаратуре с1ёансной связи при разработке помехоустойчивых устройств приема . рекуррентных сигналов фазового пуска.

Известно устройство приема рекуррентного сигнала фазового пуска, содержащее последовательно соединенные переключатель режимов, блок проверки на рекуррентность, дешифратор и элемент И, другой вход которого соединен с выходом триггера, соединенным с первьш входом переключателя f режимов, второй вход которого является входом устройства и соединен через последовательно соединенные блок сравнения и элемент НЕ с одним входом счетчика совпадений, другой вход которого соединен с выходом первого элемента ИЛИ, другой is выход блока проверки на рекуррентность соединен с другим входом блока сравнения и третьим входом переключателя режимов, npir-этом выход элемента И является выходом устройства 1 ..

Однако известное устройство имеет не- 20 достаточную точность.

Цель изобретения - повышение точности приема.

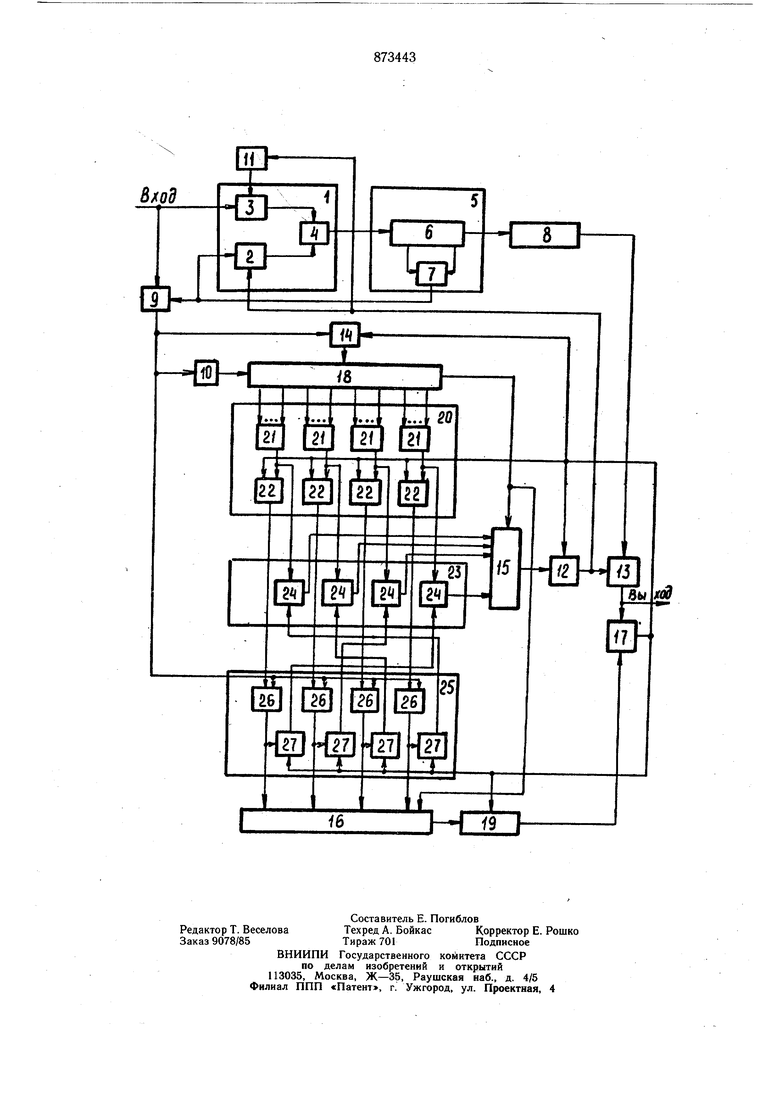

Цель достигается тем, что в устройство приема рекуррентного сигнала фазового пуска, содержашее последовательно соединенные переключатель режимов, блок проверки на рекуррентность, дешифратор н элемент И, другой вход которого соединен с выходом триггера, соединенным с первым входом переключателя режимов, второй вход которого является входом устройства и соединен через последовательно соединенные блок сравнения и элемент НЕ с одним входом счетчика совпадений, другой вход которого соединен с выходом первого элемента ИЛИ, другой выход блока проверки на рекуррентность соединен с другим входом блока сравнения и третьим входом переключателя режимов, при этом выход элемента И является выходом устройства, введены дополнительный элемент НЕ, анализатор, блок выделения порога, блок опроса, три элемента ИЛИ и счетчик времени, причем выходы счетчика совпадений соединены с входами анализатора, одни выходы которого соединены с входами блока выделения порога, другие - с одними входами блока опроса, другие входы которого соединены с выходом блока сравнения, а выходы - с входами второго элемента ИЛИ, соответствующий вход которого соединен с выходом счетчика совпадений, соединенным с одним входом третьего элемента ИЛИ, другие входы которого соединены с выходами блока выделения порога, а выход- с одним входом триггера, другой вход которого соединен с выходом четвертого элемента ИЛИ, соединенным с соответствующим входом анализатора, одним входом первого элемента ИЛИ, другой, вход которого соединен с выходом блока сравнения, третьими входами блока опроса и первым входом счетчика времени, второй вход которого соединен с выходом второго элемента ИЛИ, а выход - с первым входом четвертого элемента ИЛИ, второй вход которого соединен с выходом элемента И, причем вход триггера через дополнительный элемент НЕ соединен с четвертым входом переключателя режимов, а другие выходы блока опроса соединены с соответствующими входами блока выделения порога. На чертеже представлена структурная электрическая схема предложенного устройства. Устройство содержит переключатель 1 режимов, включающий элементы И 2 и 3 и элемент ИЛИ 4, блок 5 проверки на рекуррентность, включающий регистр 6 сдвига и сумматор 7 по модулю два, дешифратор 8, блок 9 сравнения, элемент НЕ 10, дополнительный элемент НЕ 11, триггер 12, элемент И Ю, элементы ИЛИ 14-17, счетчик 18 совпадений, счетчик 19 времени, анализатор 20, включающий элементы И 21 и триггеры 22, блок выделения порога 23, состоящий из элементов И 24, блок 25 опроса, состоящий из элементов И 26 и триггера 27. Устройство работает следующим образом. В режиме ожидания принимаемая из канала связи информация поступает на блок 9 сравнения и одновременно через элементы И 3 и ИЛИ 4 переключателя 1 режимов - на вход регистра 6 сдвига блока 5 проверки на рекуррентность. Получаемая на дополни ельном выходе блока 5 (на выходе сумматора 7 по модулю два) информация последовательно поступает в блок 9 сравнения, где сравнивается с входной последовательностью. Если входная последовательность является рекуррентной и не искажена, то на выходе блока 9 получается последовательность нулей, которая через элемент НЕ 10 поступает в счетчик 18 совпадений, подсчитыващий на выходе блока 9 сравнения число подряд следующих нулей. Каждый сигнал несовпадения (единичный сигнал) с выхода блока 9 сравнения через элемент ИЛИ 14 поступает на сбрасывающий вход счетчика 18 совпадений, устанавливая его в нулевое состояние. В случае безыскаженного приема рекуррентной последовательности заданной длины сигнала с основного выхода счетчика 18 совпадений через элемент ИЛИ 16 запускает счетчик 19 времени, а через элемент ИЛИ 15 - триггер 12, выходной сигнал с которого открывает элемент И 13, элемент И 2 и закрывает через элемент НЕ 11 элемент И 3 переключателя 1 режимов. Тем самым блок 5 проверки на рекуррентность переводится в режим генерации рекуррентной последовательности, которая с основного выхода блока 5 проверки на рекуррентной последовательности выделяет определенную комбинацию и выдает через открытый элемент И 13 сигнал фазового пуска на выход устройства, и через элемент ИЛИ 17 на установочные входы анализатора 20, блока 25 опроса, счетчика 9 времени и триггера 12, устанавливая устррйство в исходное состояние. В случае невыделения дешифратором 8 сигнала фазового пуска в течение определенного интервала счетчик 19 времени выдает сигнал, который через элемент ИЛИ 17 также устанавливает устройство в исходное состояние. Для обеспечения выделения сигнала фазового пуска при наличии помех в канале связи введен ряд анализаторов, представляющих собой элементы И 21, подключенных входами к соответствующим дополнительным выходам счетчика 18 совпадений. Элементы И 21 выдают сигналы в том случае, когда счётчик 18 совпадений насчитывает определенное число совпадении, например 10 15, 20 и 25 совпадений. Сигналы, выдаваемые элементами И 21, запоминаются триггерами 22 анализатора 20, с выхода которых они поступают на элементы И 26 блоки 25 опроса. Единичный сигнал на выходе блока 9 сравнения сбрасывает через элемент ИЛИ 14 счетчик 18 совпадений и поступает на второй вход элемента И 26 блока 25 опроса, опрашивая состояние триггеров 27 анализатора 20. Если число нулей, подсчитываемое счетчиком совпадений, прёвыщает одно из анализируемых значений, то с выхода одной или нескольких элементов И 26 блока 25 опроса через элемент ИЛИ 16 на запуск счетчика 19 времени поступает сигнал. Результать опроса запоминаются также на триггерах 27, сигналы с выхода которых поступают на вторые входы соответствующих элементов И 24 блока 23 выделения порога. При поступлении второй серии нулей с выхода блока 9 сравнения сигналы с выхода элементов И 24 анализатора 20 поступают на первые входы элементов И 24 блока 23 выделения порога, при этом если сумма двух серий «нулей превышает пороговое значение, необходимое для достижения требуемой вероятности правильного приема сигнала фазового пуска, то на выходе одного из элементов И 24 блеска 23 выделения порога появляется сигнал, который через элемент ИЛИ 15 поступает на запуск триггера 12, при этом осуществляется ранее рассмотренный алгоритм работы устройства. На чертеже в качестве примера приведены четыре анализатора. Если пороговое значение числа нулей (совпадений) выбрать равным 35, то анализаторы можно построить на 10, 15, 20 и 25 совпадений, тогда выход триггера 27 блока 25 опроса, соответствующий числу совпадений, равному, например 10, необходимо соединить со вторым входом того элемента И 24 выделения порога, который первым входом подключен к анализатору на 25 совпадений. Таким образом суммарное значение нулей в двух сериях превыщает пороговое значение, равное 35, и тем самым обеспечивается требуемая вероятность правильного приема сигнала фазового пуска. В отличие от известного устройства, в котором для выделения сигнала фазового пуска необходимо принять один, достаточно длинный, неискаженный участок рекуррентной последовательности, в предлагаемом дополнительно принимается рещение о выделении сигнала фазового пуска при приеме двух неискаженных участков рекуррентной последовательности меньщей длины, в рёзультате чего увеличивается вероятность правильного приема сигнала фазового пуска и соответственно точность приема. Формула изобретения Устройство приема рекуррентного сигнала фазового пуска, содержащее последовательно соединенные переключатель режимов, блок проверки на рекуррентность, дещифратор и элемент И, другой вход которого соединен с выходом триггера, соединенным с первым входом переключателя режимов, второй вход которого является входом устройства и соединен через последовательно соединенные блок сравнения и элемент НЕ с одним входом счетчика совпадений, другой вход которого соединен с выходом первого элемента ИЛИ, другой выход блока проверки на рекуррентность соединен с другим входом блока сравнения и третьим входом переключателя режимов, при этом выход элемента И является выходом устройства, отличающееся тем, что, с целью повыщения точности приема, введены дополнительный элемент НЕ, анализатор, блок выделения порога, блок опроса, три элемента ИЛИ и счетчик времени, причем выходы счетчика совпадений соединены с входами анализатора, одни выходы которого соединены с входами блока выделения порога, другие -: с одними входами блока опроса, другие входы которого соединены с выходом блока сравнения, а выходы - с входами второго элемента ИЛИ, соответствующий вход которого соединен с выходом счетчика совпадений, соединенным с одним входом третьего элемента ИЛИ, другие входы кс1торого соединены с выходами блока выделения порога, а выход - с одним входом триггера, другой вход которого соединен с выходом четвертого элемента ИЛИ, соединенным с соответствующим входом анализатора, одним входом первого элемента ИЛИ, другой вход которого соединен с выходом блока сравнения, третьими входами блока опроса и первым входом счетчика времени, второй вход которого соединен с выходом второго элемента ИЛИ, а выход - с первым входом четвертого элемента ИЛИ, второй вход которого соединен с выходом элемента И, причем выход триггера через дополнительный элемент НЕ соединен с четвертым входом переключателя режимов, а другие выходы блока опроса соединены с соответствующими входами блока выделения порога, Источники информации, принятые во внимание при экспертизе 1. Мартынов Е. М. Синхронизация в системах передачи дискретных сообщений. М., «Связь, 1972, с. 200 (прототип).

Авторы

Даты

1981-10-15—Публикация

1979-12-12—Подача