и аргумента utf несимметрии напряжений сети. Первый управляющий вход вычислителя корректирующих углов подсоединен к выходу генератора симметричной последовательности импульсов, а второй через элемент ИЛИ - к вы1

Изобретение относится к электротехнике и может быть использовано в преобразовательной технике для управления многофазными выпрямителями, к которым предъявляются .высокие требования, по качеству выходного напряжения и тока.

Цель изобретения - повьшение эффективности компенсации неканомичес- кой гармоники выпрямленного напряжения, обусловленной несимметрией напржений питающей сети при сохранении всокой симметрии формирования управляющих импульсов,

На фиг,1 изображена блок-схема устройства; на фиг,2 - блок-схема вычислителя корректирующих углов; на фиг,3 - принципиальная схема узла согласования, содержащегося в блоках развертки,в

На фиг,1 изображены формирователь 1 т-кратной частоте сети симметричной последовательности импульсов из однофазного сетевого напряжения, подключенный к линейному напряжению Цд питающей сети, распределитель импульсов на т/2 канала 2, выход каждого из которых подключен к установочному входу блока развертки 3, а вход 4 подключен к выходу распределителя 2, Блок развертки 3 состоит из генератора высокочастотной последовательности импульсов 5, блока согласования 6 и счетчика 7 импульсов. При этом, выход генератора 5 подключен ко второму входу блока 6, а оба выхода последнего подключены соответственно к суммирующему, и обнуляющему входам счетчика импульсов. Выходы блоков развертки 3 подсоединены к первым входам компараторов 8, ко вторым входам которых подключены выходы двухвходовых сумматоров 9, Выход каждого компаратора подключен к

ходам компараторов. Вычислитель корректирующих углов 13 формирует корректирующие углы в соответствии с заданным алгоритмом и выполнен на цифровых элементах, 1 з,п, ф-лы, 3 ил,, 2 табл.

обнуляющему входу блока развертки 3 и одновременно ко входам блока формирования управляющих импульсов 10,

вторая группа которых подключена к фазам трехфазного напряжения сети. Первые входы сумматоров 9 подключены к источнику управляющего напряжения 11 через арккосинусный преобразователь 12, Вторые входы каждого сумматора подключены к соответствующим выходам вычислителя корректирующих углов 13, первый информационный вход которого подключен к выходу .арккосинусного преобразователя 12, а второй и третий информационные входы - к выходам измерителя 14 параметров несимметрии сети, содержащих соответственно информацию о модуле и аргументе несимметрии сети. Первый управляющий вход блока 13 подключен к выходам компараторов 8 -через элемент ИЖ 15, а второй - к выходу блока 1,. Вычислитель корректирующих углов

(фиг,2) содержит блок входных регистров 16, первый и второй выходы которого подключены ко входам- блоков логарифмирования 17 и 18, Первый и третий выходы блока 16 подключены к

первому и второму входам блока вычисления угла 19, содержащего двухвходо- вый сумматор 20 и арифметико-логическое устройство 21 (АЛУ), При этом входы сумматора 20 являются первым и вторьм входами блока 19, выход узла 20 подключен к. первому входу устройства 21, а второй и информационный вход его, являющийся третьим входом блока 19, подключен к формирователю

22 кода числа, равного ТГ/З, Управляющий вход устройства 21 и блока 19 подключен к выхЬду блока формирования команд 23, содержащему генератор 24, суммирующий счетчик 25 и постоянное .запоминающее устройство 26, Выход ге

нератора 2Д подключен к суммирующему входу счетчика импульсов 25, выходы его подсоецниены ко входам узла 26. Обнуляющий вход счетчика 25 подключе ковторому управляющему входу вычислителя корректирующих углов 13. Вы- ходы блоков 17 и 18 подключены к первым двум входам блока суммирования 27, а третий вход его подключен к выходу блока вычисления угла 19 через блок логарифмирования 28. Выход блока 27 через блок вычисления, антилогарифма 29 подсоединен ко входу демультиплексора 30, управляющий вход которого подключен к выходу блока формирования команд 23. Выходы блока 30 подсоединены к соответствующим входам блока выходных регистров 31, управляющий вход ко- торого подключен к первому управляющему входу вычислителя корректирующих углов.

Принципиальная схема блока согласования приведена на фиг.З. Инверторы 32 и 33 связывают обнуляющий и установочный входы блока с R-S триггерами 34. Прямой выход триггера 34 подключен к первому входу элемента И 35, второй вход которого соединен с выходом генератора 5, Выход элемента И 35 подключается к суммирующему входу счетчика 7. Инверсный выход триггера 34 через блок задержки на элементах 36 и 37 подключается к обнуляющему входу счетчика 7.

Устройство работает следующим образом.

Формирователь 1 формирует из линейного напряжения , симметричную последовательность импульсов частоты mfj. (fc - частота сети). Эта последовательность распределителем 2 распределяется по каналам таким образом, что первьм импульс, формируемый в момент перехода напряжения Цд, через нуль, распределяется в первый канал (верхний на фиг.1). Остальные импульсы распределяются по каналам с интервалом 2Т/3, Импульсы с выхода блока 2 поступают на входы блоков согласования и через инвертор 32 пере- брасьгоают R-S триггер 34 в состояние при котором на его прямом выходе появляется сигнал, соответствующий логической единице. Этот сигнал дает разрешение элементу И 35 пропускать на вход счетчика 7 (фиг.1) импульсы с выхода генератора 5. При

0

0

поступлении импульсов на вход счетчика 7 на его выходе появится двойной код, увеличивающийся во времени. В момент времени, когда выходной код счетчика 7 будет равен двоичному коду сигнала, поступающего с выхода сумматора 9, компаратор 8 выдает сигнал (единичный импульс) , которьй одновре-: менно подается на вход блока 10 для формирования управляющего импульса, на второй управдяющий вход вычислителя корректирующих углов 13 как команда на ввод информации во входные

5 регистры блока 13.

Этим обеспечивается запись информации с блока 14 о параметрах несимметрии и, с аркокосинусного преобразователя 12, о рабочем угле включения вентилей. Одновременно импульс с выхода компаратора 8 поступает на обнуляющий вход генератора развертки (на вход инвертора 33, фиг.З) и переводит R-S триггер 34 в нулевое сос5 тояние. Этим обеспечивается запирание ключевого элемента 35 и импульс с генератора 5 (фиг.1) не будет поступать на суммирующий вход счетчика 7. В то же время и шульс с инверсного выхода R-S триггера через задержку, обеспечиваемую элементами 36 и 37, поступает на обнуляющий вход счетчика 7 и обнуляет его выход. Информация, поступающая на вход компаратора 8 с выхода сумматора 9, представляет собой алгебраическую сумму управляющего сигнала и сигнала, поступающего на второй вход сумматора с соответствующего выхода вычислителя корректирующих углов 13. На каждом выходе вычислителя 13 появляется сигнал, пропорциональный требуемой величине корректирующего угла с момента подачи на первый управляющий вход его импульса с выхода формирователя 1.

Величина корректирующ 1х сигналов вычисляется вычислителем 13 в соответствии с формулами:

0 uoifte, (i -нг С -ТГ/З)

0

5

0

5

iir -т- cos(oL + ir/3) sinot

sinoi

55 Ъ cos(oi + b(j;)

Их реализация осуществляется вычислителем 13 (фиг.2). Запись ни

формации в блок входных регистров осуществляется при подаче импульса на второй управляющий вход с выхода компараторов 8. На первый вход блока 13 информация о величине угла включения вентилей первого канала поступает с выхода арккосинуснога преобразователя 11 (фиг.-1). На второ и третий информационные входы блока 13 информация о модуле и аргументе л q несимметрии поступает с выхода измерителя 14 параметров несимметрии

Учитывая сложность реализации умножения . в цифровой форме записи информации, вычисление корректирующих углов ЛЫ; проще реализовать в логарифмическом масштабе. В этом случае вычисление сводится к выполнению операций, соответствующих логарифмированию, суммированию и вЬгаислению антилогарифма. При этом, выполнение операций логарифмирования и вычисления антилогарифма реализуется с помощью программируемых постоянных запоминающих устройств.

Блок- входных регистров 16 выполнен с открытым выходом, поэтому записанная в нем информация сразу же подается на входы последующих блоков - блоков логарифмирования 17 и 18 и на входы сумматора 20 блока вычисления угла 19. Информация с выходов блоков 17 и 18 поступает на первые дв входа блока 27, При этом, на первом входе сумматора 27 будет место информация5 соответствующая InCl/sin а на втором - информация, соответствующая In 6.

Информация с выхода сумматора 20 блока 19, определяемая суммой oi +Д(;, поступает на первый вход-арифметико- логического устройства (АЛУ) 21, на второй информационный вход которого подается код сигнала, пропорционального числу ir/3. Вычисление каждого из трех возможных значений угла

Q, Q,

ci + Ду

-ei, + uV + ТГ/З

Qj - ЧГ/З

осуществляется по командам, поступающим на управляющий вход S АЛУ 21 с блока формирования команд 23.

Формирование команд в блоке 23 осуществляется следующим образом.

10

15

.

аi)

20

3634056

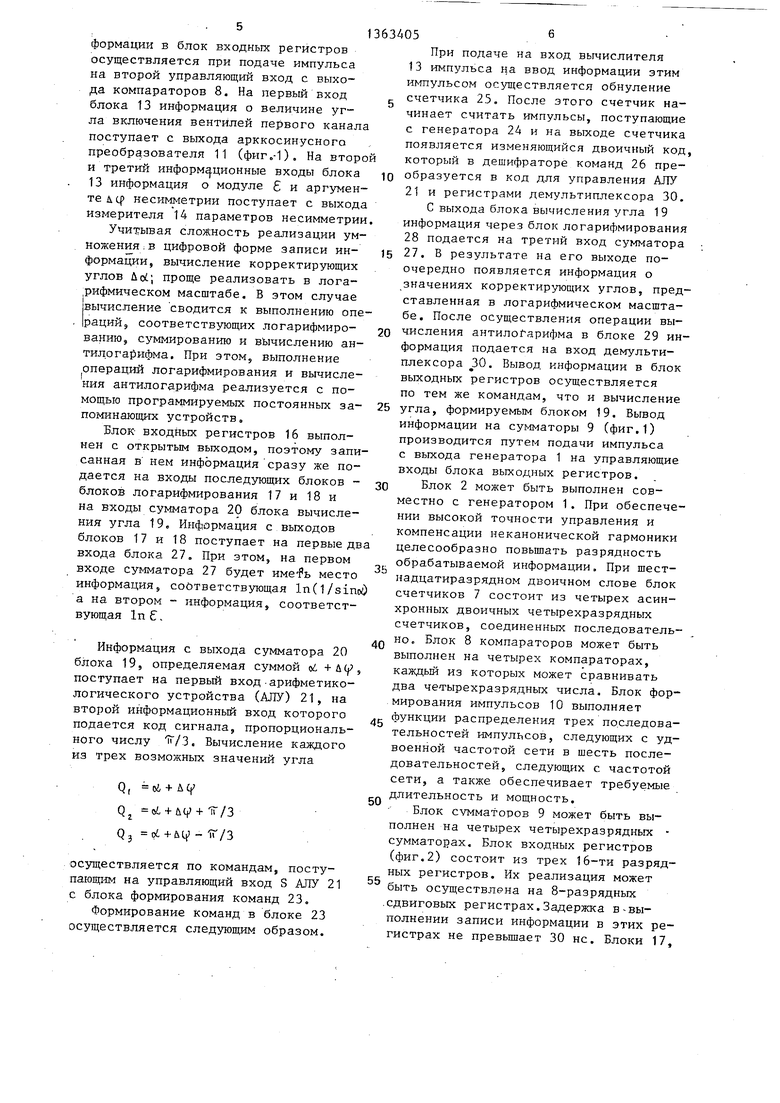

При подаче на вход вычислителя 13 импульса на ввод информации этим импульсом осуществляется обнуление счетчика 25, После этого счетчик начинает считать иьшульсы, поступающие с генератора 24 и на выходе счетчика появляется изменяющийся двоичный код, который в дешифраторе команд 26 преобразуется в код для управления АЛУ 21 и регистрами демультиплексора 30,

С выхода блока вычисления угла 19 информация через блок логарифмирования 28 подается на третий вход сумматора 27. В результате на его выходе поочередно появляется информация о значениях корректирующих углов, представленная в логарифмическом масштабе. После осуществления операции вычисления антилогарифма в блоке 29 информация подается на вход демультиплексора 30, Вывод информации в блок выходных регистров ос тцествляется по тем же командам, что и вычисление 25 угла, формируемым блоком 19. Вывод информации на су -таторы 9 Сфиг.1) производится путем подачи импульса с выхода генератора 1 на управляющие входы блока выходных регистров.

Блок 2 может быть выполнен совместно с генератором 1. При обеспечении высокой точности управления и компенсации неканонической гармоники целесообразно повышать разрядность обрабатываемой информации. При шестнадцатиразрядном двоичном слове блок счетчиков 7 состоит из четырех асинхронных двоичных четырехразрядных счетчиков, соединенных последовательно. Блок 8 компараторов может быть выполнен на четырех компараторах, каждый из которых может сравнивать два четырехразрядных числа. Блок формирования импульсов 10 выполняет функции распределения трех по.следова- тельностей импульсов, следующих с удвоенной частотой сети в шесть последовательностей, следующих с частотой сети, а также обеспечивает требуемые длительность и мощность.

Блок сумматоров 9 может быть выполнен на четырех четырехразрядных сумматорах. Блок входных регистров (фиг.2) состоит из трех 16-ти разрядных регистров. Их реализация может быть осуществлена на 8-разрядных сдвиговых регистрах,Задержка в-выполнении записи информации в этих регистрах не превышает 30 не. Блоки 17,

30

40

45

50

55

18 и 28 вычисления логарифма и 29 - вычисления антилогарифма имеют идентичную реализацию, выполняемую на программируемых постоянных запоминающих устройствах или на программируемых логических матрицах, в которы определенному слову на адресных входах ставится в соответствие определенное, заранее запрограммированное слово на информационных выходах.

При реализации блока 28 логарифмирования косинуса необходимо учитывать, что логарифм может принимать отрицательное значение. Следовательно, на входе зтого блока необходимо формировать число С In(cosQ) и оди разряд выходного слова отвести для передачи знака числа cosQ на вход блока 27 для формирования в последнем правильного знака корректирующего угла. Максимальное время задержки каждого блока составляет не более 80 НС.

В блоке 19 вычисления угла АЛУ 21 работает в зависимости от сигналов на управляющих входах, формируемых блсГком 23.

Для указанных микросхем коды команд на управляющих входах для каждой операции соответствуют табл.1

Блок 30 демультиплексора представляет собой блок, cocтoяш й из трех 16-разрядных регистров, реализованных аналогично блоку 16. Синхронизирующие входы регистров подключены к выходу блока 23 формирования команд, формирующего сигналы разрешения записи в один из регистров.

Блок формирования команд содержит описанные ранее элементы.

Для последовательного вычисления формул на управляющие входы АЛУ 21 блока 19 необходимо последовательно подавать сигналы в соответствии с табл.1. С учетом времени задержки всей схемы вычислительного блока код операции должен сохраняться в течени 0,5 МКС после начала вычислений по одной из формул, что обеспечивает надежное получение результатов. Чере 0,5 МКС результат вычислений должен быть записан в один из регистров блока 30. Операция режима демультиплексирования отражена в табл.2.

Применение устройства позволяет существенно (в 20-100 раз) снизить амплитуду неканонической гармоники

0

5

0

5

выпрямленного напряжения, обусловленной несимметрией напряжений сети в диапазоне углов включения вентилей (uL 20-90°).

Формула изобретения

1. Устройство для управления т- пульсным выпрямителем, содержащее последовательно включенные формирователь т-кратной часфоте сети симметричной последовательности импульсов из однофазного сетевого напряжения, распределитель импульсов по га каналам, а в каждом канале - последовательно включенные блок развертки, первый вход компаратора и источник управляющего, сигнала, отличаю- щ е е с я тем, что, с целью повьщге- ния эффективности компенсации неканонической гармоники, выпрямленного напряжения, обусловленной несимметрией напряжений питающей сети при сохранении высокой симметрии формирования управляющих импульсов, распределитель импульсов выполнен с т/2 выходными каналами, а устройство снабжено тремя двухвходовыми сумматорами, вычислителем корректирующих углов, содержащим первый , второй и ot,; и третий &oi ов выходы, первьш uL , второй и третий М информационные входы, первый и второй управляющие входы, измерителем параметров несимметрии напряжений сети, функциональным арккосинусным преобразователем, блоком формирования управляющих импульсов с двумя группами. входов и элементом ИЛИ, причем вторые входы компараторов подключены к выходам сумматоров, первые входы которых подсоединены к источнику управляющего сигнала через функциональный .g арккосинусный преобразователь, а вторые - соответственно к первому, вто- .-рому и третьему выходам вычислителя корректирующих углов, первый информационный вход которого подсоединен к выходу арккосинусного преобразователя, а второй и третрш входы - к выходам измерителя параметров несимметрии напряжений сети соответственно модуля и аргумента, первый управляющий вход вычислителя корректирующих углов подсоединен к выходу формирователя т-кратной частоте сети симметричной последовательности импульсов из однофазного сетевого напряжения.

0

5

0

0

5

а второй - к выходам компараторов через элемент ИЛИ выходы компараторов каждого канала подключены к обнуляющим входам соответствующих блоков развертки и к входам первой группы блока формирования управляющих импульсов, вторая группа входов которого, а также входь: измерителя параметров несимметрии предназначены для подключения к шинам трехфазной сети, причем зависимость выходных сигналов от входных вычислителя корректирующих углов следующая ;

&6i

АВ

;- с:овЫ.ду ),

uoi

А сТ;;:: ° + д + ),

Доб

sinoi - sin °

2. Устройство по П.1, о т л ю щ е е с я тем, что вычислитель корректирующих углов содержит блок входных регистровJ содержащий первый, второй и третий информационные входы, являющиеся входами вычислителя корректирующих углов, первый, второй и третий информационные выходы и входы управления, три блока логарифмирования, блок вычисления угла, содержащий три информационных входа, один информационный выход и один управляющий вход, блок суммирования, содержащий три информационных входа и один выход, блок вычисления антилогарифма, демультиплексор с одним информационным, одним управляющим входами и тремя информационными выходами, блок входных регистров с тремя информационными и одним управляющим входами, являющимися инфо змаци- онными выходами вычислителя коррек1363405 0

тирующих углов и блокам формирования команд, причем вход управления блока входных регистров подсоединен ко второму управляющему входу вычислителя корректирующих углов, первый и второй выходы блока входных регистров подсоединены к соответствующим блокам логарифмирования, выходы которых подJQ соединены к первым двум входам сумматора, первый и третий выходы блоков входных регистров подсоединены к первым двум входам блока вычисления угла, к третьему входу которого

15 подключен формирователь кода числа |Г/3; управляющий вход блока вычис- .ления, угла подсоединен к выходу блока формирования команд, вход которого подсоединен ко второму управ2Q ляющемувходу вычислителя корректирующих углов, а выход блока вычисления угла через третий блок логарифмирования подсоединен к третьему входу блока суммирования; выход пос- и ч а- 25 леднего через блок вычисления антилогарифма подсоединен к входу де- мультиплексора, управляющий вход которого подключен к выходу блока фор30

35

40

45

мирования команд, а выходы демульти- плексора подсоединены к соответствующим входам блока выходных регистров, управляющий вход которого подсоединен к первому управляющему входу вычислителя корректирующих углов, причем блок вычисления угла содержит двухвходовый сумматор, входы которого являются первьм и вторьм входами . блока, и арифметико-логическое устройство, первый вход которого подсоединен к выходу су -{матора, второй вход подсоединен к третьему входу блока вычисления угла, а управляющий вход является управляющим входом блока вычисления угла, причем арифметико-логическое устройство запрограммировано согласно прилагаемой таблице.

мирования команд, а выходы демульти- плексора подсоединены к соответствующим входам блока выходных регистров, управляющий вход которого подсоединен к первому управляющему входу вычислителя корректирующих углов, причем блок вычисления угла содержит двухвходовый сумматор, входы которого являются первьм и вторьм входами . блока, и арифметико-логическое устройство, первый вход которого подсоединен к выходу су -{матора, второй вход подсоединен к третьему входу блока вычисления угла, а управляющий вход является управляющим входом блока вычисления угла, причем арифметико-логическое устройство запрограммировано согласно прилагаемой таблице.

Таблица 1

0Q 06+ Д

1 Q Q,+A(f + -ir/3 О Q 6i+A()- ir/3

0,1 16

О

О

Таблица 2

О О

Из ген. 5

Из.8

33

Фиг. 2

35

Ha8xC,CTem(/,Sr7

| название | год | авторы | номер документа |

|---|---|---|---|

| Одноканальное устройство для управления @ -пульсным выпрямителем | 1986 |

|

SU1365299A1 |

| Устройство для вычисления функций | 1985 |

|

SU1287150A1 |

| Способ управления вентильным преобразователем | 1986 |

|

SU1374373A1 |

| Способ компенсации неканонических гармоник выпрямленного напряжения | 1986 |

|

SU1415374A1 |

| УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ ОШИБОК | 1991 |

|

RU2037271C1 |

| ИНТЕЛЛЕКТУАЛЬНЫЙ ГАЗОРЕДУЦИРУЮЩИЙ ПУНКТ С ФИКСАЦИЕЙ ПОТЕРЬ ГАЗА | 2024 |

|

RU2825284C1 |

| УСТРОЙСТВО ДЛЯ РЕГУЛИРОВАНИЯ ДАВЛЕНИЯ | 1992 |

|

RU2072548C1 |

| Стенд для испытания тормозов автомобиля | 1987 |

|

SU1422062A1 |

| Цифровой частотный детектор | 1990 |

|

SU1714530A1 |

| Устройство для автоматического измерения амплитудно-частотных характеристик | 1986 |

|

SU1379749A1 |

Изобретение относится к электротехнике и может быть использовано в преобразовательной технике для управления многофазными выпрямителями, к которым предъявляются высокие требования по качеству выпрямленного напряжения. Цель изобретения - появление неканонической гармоники выпрямленного напряжения в преобразователях с многоканальными системами управления, обусловленной несимметрией напряжений питающей сети. Устройство для управления т-пульсным выпрямителем содержит формирователь 1/2 последовательности импульсов из однофазного сетевого напряжения, т/2 канала 2, каждый из которых содержит последовательно включенные блок развертки и компаратор, а также т/2 двухвходовых сумматора 9, вычислитель корректирующих углов 13, функциональный арккосинусный преобразователь 12, блок 10 формирования управляющих импульсов, источник 11 управляющего напряжения и измеритель 14 модуля /БС 00 CD О СП тгптг

Из. 2

32k

36

J7

HGSxR

ГУЛ774/. 7

Редактор И.Сегляник

Составитель В.Бунаков Техред Л.Сердюкова

Корректор С.Шекмар Подписное

Заказ 6375/50Тираж 659

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

. J

Корректор С.Шекмар Подписное

| Устройство для управления тиристорным выпрямителем | 1982 |

|

SU1069120A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для управления многофазными выпрямителями | 1982 |

|

SU1127069A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1987-12-30—Публикация

1986-07-28—Подача