(54) УСТРОЙСТВО ДЛЯ ИЗВЛЕЧЕНИЯ КОРНЯ КВАДРАТНОГО

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для извлечения квадратного корня | 1982 |

|

SU1056186A1 |

| Аналого-цифровой преобразователь интегральных характеристик электрических величин | 1981 |

|

SU1035790A1 |

| Частотно-импульсное делительное устройство | 1980 |

|

SU898429A1 |

| Аналого-цифровой преобразователь действующего значения напряжения | 1987 |

|

SU1585898A1 |

| Цифровое устройство управление весовым дозированием | 1980 |

|

SU866418A1 |

| Число-импульсное устройство для решения задач автоматического дозирования | 1983 |

|

SU1098000A1 |

| Аналого-цифровой преобразователь интегральных характеристик напряжений | 1988 |

|

SU1615888A1 |

| Устройство для вычисления функции @ | 1984 |

|

SU1166102A1 |

| Цифровой измеритель отклонения измеряемой частоты от номинальной | 1979 |

|

SU1200188A1 |

| Адаптивный аналого-цифровой преобразователь | 1984 |

|

SU1226666A1 |

Изобретение относится к вычислительной и измерительной технике и предназначено для извлечения корня квадратного из двоичного кода числа.

Известно устройство для извлечения корня квадратного, содержащее счетчики, сравнения кодов, триггерыГ1Т

Недостатком устройства является низкая точность, вызванная тем, что to оно позволяет получать только целочисленные значения корня, и низкое быстродействие. Наиболее близким по технической сущности к предлагаемому является устройство zj для извлечения корня квадратного содержащеетри интегратора с последовательным переносом и реверсивный счетчик. В известном устрой стве производится преобразование кода входного сигнала N и кода результата извлечения корня квадратного n(t), в

частности fj, и fyq(t), соответственно равные

Js.

(1)

N

N

m

N

5

n(t).

(2)

lilirt

где fg - опорная частота;

%i емкости интеграторов с последовательным переносом,

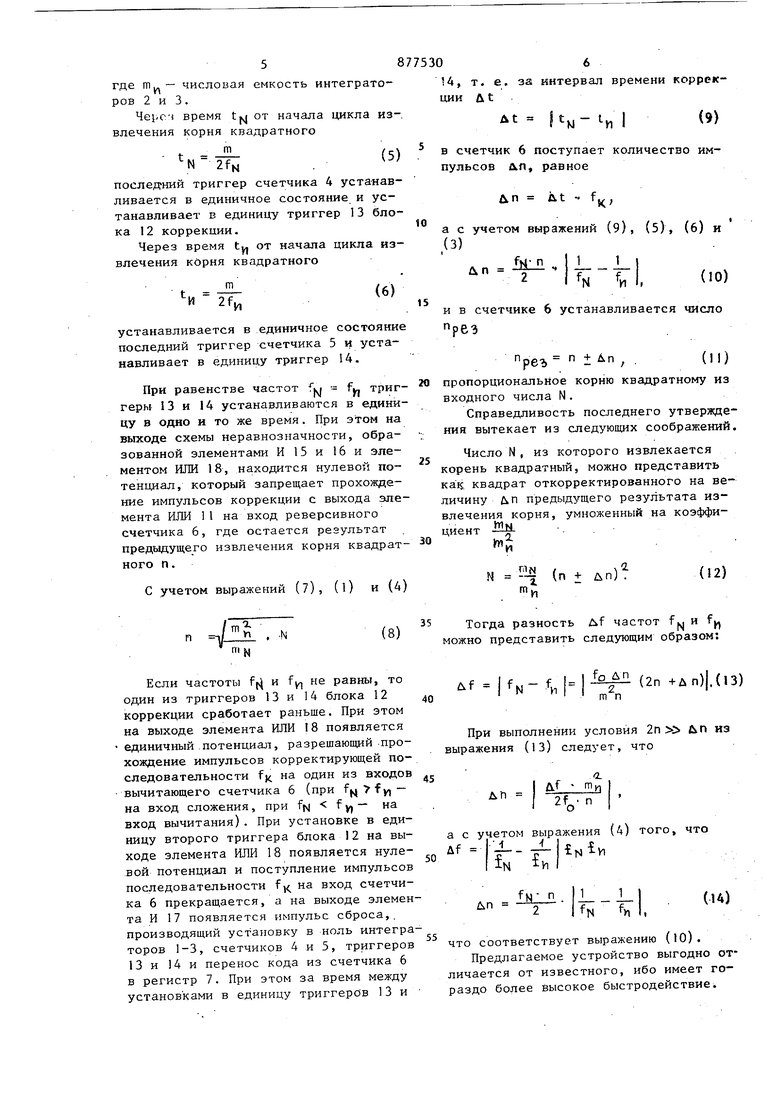

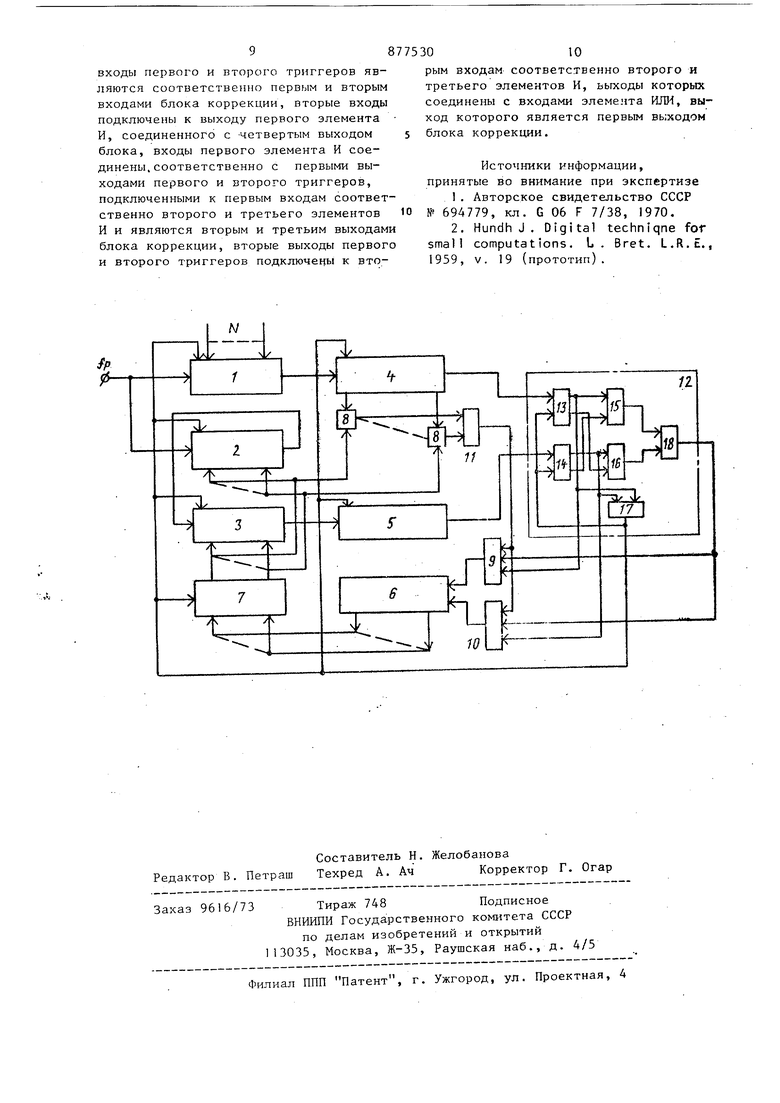

и коррекция числа n(t) импульсами разностной частоты Cf(sj - fj(t)3 до установления равенства f«(t). Недостатком этого устройства является низкое быстродействие, вызванн(эе тем, что коррекция n(t) производится разностной частотой, которая может быть очень малой, особенно при уравнивании образующих ее частот. Цель изобретения - повышение быстродействия устройства. 38 Поставленная цель дости1ается тем, что в устройство для извлечения корня квадратного, содержащее интеграторы и реверсивный счетчик, причем входы первого и второго интеграторов подключены к входу опорной частоты устройства управляющий вход первого интегратора соединен с информационным входом устройства, выход второго интегратора соединен со входом третьего интегратора, введены регистр, два счетчика, группа элементов И, элементы И, ИЛИ и блок коррекции, причем входы первого и второго счетчиков подключены к вьгхо дам первого и третьего интеграторов соответственно, а выходы переполнения - к первому и второму входам блока коррекции, информационные выходы первого счетчика, соединены с первыми входами элементов И группы, вторые входы которых соединены с выходами ре гистра j подключенными к управляющим . входам второго и третьего интеграторов, а выходы элементов И соединены со входами элемента ИЛИ, входы сложения и вычитания реверсивного счетчика соединены соответственно с выходами первого и второго элементов И, первые входы которых подключены к выходу элемента ИЛИ, вторые - к первому а третьи - соответственно ко второму и третьему выходам блока коррекции, четвертый выход которого соединен со входами сброса первого и второго счет чиков, первого, второго и третьего ин теграторов и входам управления записью регистра, входы которого соединен с выходами реверсивного, счетчика. Блок коррекции содержит два триггера, три элемента И, элемент ИЛИ, причем первые входы первого и второго триггеров являются соответственно первым и вторым входами блока коррекции, вторые входы подключены к выходу перв го элемента И, соединенного с четвертым выходом блока, входы первого элемента И соединены соответственно с первыми выходами первого и второго триггеров, подключеннымик первым вхо дам соответственно второго и третьего элементов И и являются вторым и третьим выходами блока коррекции, вторые выходы первого и второго триггеров подключены ко вторым входам соответст венно второго и третьего элементов И, выходы которых соединены со входами элемента ИЛИ, выход которого является Iпервым выходом блока коррекции. 0 На чертеже приведена блок-схема устройства для извлечения корня квадратного. Устройство состоит из интеграторов (с последовательным переносом , счетчиков 4 и 5, реверсивного счетчика 6, регистра 7, группы элементов И 8, элементов И 9, 10 и ИЛИ 1I блока 12 коррекции, включающего в себя триггеры 13 и 14, элементы И 15-17 и ИЛИ 18. 4 и 5 представляют собой двоичные счетчики импульсов, инверсный выход каждого триггера которых соединен со входом триггера следующе-. го разряда. Регистр 7 состоит из D-триггеров, входы синхронизации которых объединены в общую шину управления переносом, а D-ВХОДЫ триггеров являются входами регистра. Устройство работает следующим образом. Перед началом каждого цикла извлечения корня квадратного интеграторы 1-3 с последовательным переносом, счетчики 4 и 5, триггеры 13 и 14 блока 12 коррекции сбрасываются в ноль, а результат предьщущего извлечения корня Квадратного п переносится из реверсивного счетчика 6 в регистр 7. Интегратор с последовательным переносом формирует частотно-импульсную последовательность с частотой следования импульсов fj (выражение 1), пропорциональной величине входного сигнала N, поступающего на вход счетчика 4. Последний используется в качестве делителя частоты f| и, кроме того, совместно с элементами И 8 и элементом ИЛИ 11 образует интегратор с последовательным переносом, на выходе которого формируется частотноимпульсная последовательность коррекции с частотой следования импульсов f. f bL К m где m - числовая емкость счетчиков 4 и 5. Интеграторы 2 и 3 с последовательным переносом, соединенные последовательно, на вход управляющего кода которых подается код результата предыдущего извлечения корня квадратного п, формируют частотно-импульсную последовательность с частотой следовагде числовая емкость интеграторов 2 и 3. Черсч время t от начала цикла извлечения корня квадратного m последгний триггер счетчика 4 устанавливается в единичное состояние и устанавливает в единицу триггер 13 блока 12 коррекции. Через время ty от начала цикла извлечения корня квадратного устанавливается в единичное состояние последний триггер счетчика 5 и устанавливает в единицу триггер 14. При равенстве частот fij геры 13 и 14 устанавливаются в едини цу в одно и то же время. При этом на выходе схемы неравнозначности, образованной элементами И 15 и 16 и элементом ИЛИ 18, находится нулевой потенциал, который запрещает прохождение импульсов коррекции с выхода эле мента ИЛИ 11 на вход реверсивного счетчика 6, где остается результат предыдущего извлечения корня квадрат ного П . с учетом выражений (7), (l)

Ni

У

п

Если частоты fj и fy не равны, то один из триггеров 13 и 14 блока 12 коррекции сработает раньше. При этом на выходе элемента ИЛИ I8 появляется единичный потенциал, разрешающий прохождение импульсов корректирующей последовательности f на один из входов вычитающего счетчика 6 (при - на вход сложения, при N у| на вход вычитания). При установке в единицу второго триггера блока I2 на выходе элемента ИЛИ 18 появляется нулевой потенциал и поступление импульсов последовательности fj на вход счетчика 6 прекращается, а на выходе элемента И 1 7 появляется импульс сброса,, производящий установку в ноль интеграторов 1-3, счетчиков 4 и 5, триггеров 13 и 14 и перенос кода из счетчика 6 в регистр 7. При этом за время между установками в единицу триггеров 13 и 1 триг

Тогда разность Af частот f, и f

35 можно представить следующим образом:

|fN-fц| | T +дп)|.(13)

m п

40

При выполнении условия 2п п из выражения (13) следует, что

.- i. u.f . тк1

Ah

2f.n

а с учетом выражения (4) того, что

1

N Vl

Af

JN и

J fN

(14)

Г

vi I,

что соответствует выражению (lO).

Предлагаемое устройство выгодно от личается от известного, ибо имеет гораздо более высокое быстродействие. т. е. за интервал времени коррекut I в счетчик 6 поступает количество импульсов an, равное Лп а с учетом выражений (9), (5), (б) /3) fM-n 1 1 1 Лп - м т I, (10) 6 устанавливается число и в счетчике реъ ± п , . (II) пропорциональное корню квадратному из входного числа N. Справедливость последнего утверждения вытекает из следующих соображений. Число N, из которого извлекается орень квадратный, можно представить ак квадрат откорректированного на веичину п предыдущего результата излечения корня, умноженный на коэффииентN -т

При неравенстве частот f и fw{fc) (выражения 1 и 2) в известном устройстве для извлечения корня квадратного возникает переходный процесс, определяющийся уравнением fi Ti

- J f(t)dt n{t). (15)

Из (l5) с учетом (Он (2) следует, что длительность переходного процесса То составляетVf4 тЬз), ) относительная погрешность Здесь Пф - фактически полученное значение корня квадратного из числа N. Для предлагаемого устройства врем цикла извлечения корня квадратного tX) составит большее из времени или t.. При tw 7 t fvi учетом выражений (1 (б) и (4) отношение C2/t составляет Т2 nin l + dli±(f) cf 6,( При , и номиналь ном значении Пц0;у 1000, что имеет место в реальном нзвлекателе корня квадратного, ,4. Если условие 2л У и п не выполняется, для точного извлечения корня квадратного в предлагаемом /устройстве требуется несколько циклов извлечения корня. При использовании предлагаемого устройства в реальных элек трических системах, где действующие значения напряжения и силы переменно го тока могут изменяться в пределах О,5-1,5 от их номинальных значений, а следовательно, п изменяется в пределе от 500 до 1500, максимальное вр мя извлечения корня квадратного необ ходимо при изменении п от 500 до 150 или наоборот и составит при погрешно ти менее 0,001, как показывают экспе

риментальные исследования, не более трех циклов, т. е.

Т. ЗТ.

Таким образом, даже в этом случае предлагаемое устройство выигрывает в быстродействии по, сравнению с известным, поскольку

t:,moix Формула изобретения i. Устройство для Извлечения корня квадратного, содержащее интеграторы и реверсивный счетчик, причем входы первого и второго интеграторов подключены к входу опорной частоты устройства, управляющий вход первого интегратора соединен с информационным входом устройства, выход второго интегратора соединен с входом третьего интегратора, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены регистр, цва счетчика, группа элементов И, элементы И, ИЛИ и блок коррекции, причем входы первого и второго счетчиков подключены к выходам первого и третьего интеграторов соответственно, а выходы переполке шя - к первому и второму входам блока коррекции, информационные выходы первого счётчика соединены с первыми входами элементов И группы, вторые входы которых соединены с выходами регистра, подключенными к управляющим входам второго и третьего интеграторов, а выходы элементов И соединены с входами элемента ИЛИ, входы сложения и вычитания реверсного счетчика соединены соответственно с выходами первого и второго элементов И, первые входы которых подключены к выходу элемента ИЛИ, вторые - к первому, а третьи - соответственно к второму и третьему выходам блока коррекции, четвертый выход которого йоединен с входами сброса первого и второго счетчиков, первого, второго и третьего интеграторов и входам управления записью регистра, входы которого соединены с выходами реверсивного счетчика. 2. Устройство по п. I, о т л и чаю. щееся тем, что блок коррекции содержит два триггера, три элемента И, элемент ИЛИ, причем первые

входы первого и второго триггеров являются соответственно первым и вторым входами блока коррекции, вторые входы подключены к выходу первого элемента И, соединенного с -четвертым выходом блока, входы первого элемента И соединены, соответственно с первыми выходами первого и второго триггеров, подключенными к первым входам соответственно второго и третьего элементов И и являются вторым и третьим выходами блока коррекции, вторые выходы первого и второго триггеров подключены к вторым входам соответственно второго и третьего элементов И, ььгходы которых соединены с входами элеме.чта HJDI, выход которого является первым выходом блока коррекции.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1981-10-30—Публикация

1980-01-07—Подача