Изобретение относится к области цифровой вычислительной техники и может быть использовано для проверки устойчивости к сбоям программ управляющих ЦВМ, имеющих средства аппаратного контроля и программную защиту ОТ сбоев, организованную путем разбиения программ на участки, (называемые далее защищенными блоками), допускающие повторные исполнения. ЦВМ имеют вход для подключения внешнего наладочного блока памяти (например, для замены постоянного запоминающего устройства на период отЛс1дки программ) . Известны устройства для определе ния эффективности схем контроля ЦВМ путем введения ошибок 1. Устройство ориентировано на проверку функционирования аппаратных средств и требуютвведения дополнительных элементов в схему ЦВМ. Наиболее близким техническим решением к изобретению является устро ство для проверки программ ЦВМ,соде жащее генератор управляемых сбоев,о му сравнения и внешний наладочный блок памяти 2.Сбой создается путем запрета прохождения информации из внешнего блока памяти в ЦВМ. Недостаток устройства состоит в том, что оно позволяет проверять систему защиты только последовательно (один защищенный сбой за другим) по одному блоку яа каждый прогон теста. Поэтому исследование сбоеустойчивости программ, имеющих значительное число защищенных блоков, требует большего времени. Целью изобретения является сокращение времени проверки системы программ от сбоев, т.е. повышение производительности устройства. Поставленная цель достигается тем, что в устройство для имитации сбоев ЦВМ, содержащее .наладочный блок памяти и генератор управляемых сбоев, причем вход устройства соединен с адресным входом наладочного блока памяти, введены одноразрядный блок памяти и элемент И. Адресный вход одноразрядного блока памяти соединен со входом устройства, выход - со входом генератора управляемых сбоев, выход которого соединен с первым ВХО.ЦОМ элемента И. Выход наладочного блока памяти соединен со вторым входом элемента И, выход которого явля- ется выходом устройства. Генератор управляемых сбоев содержит триггер и

элемент И-НЕ, Вход генератора сбоев соединен со счетным входом триггера первым входом элемента И-НЕ, выход которого является выходом генератора Выход триггера соединен со вторым входом элемента И-НЕ.

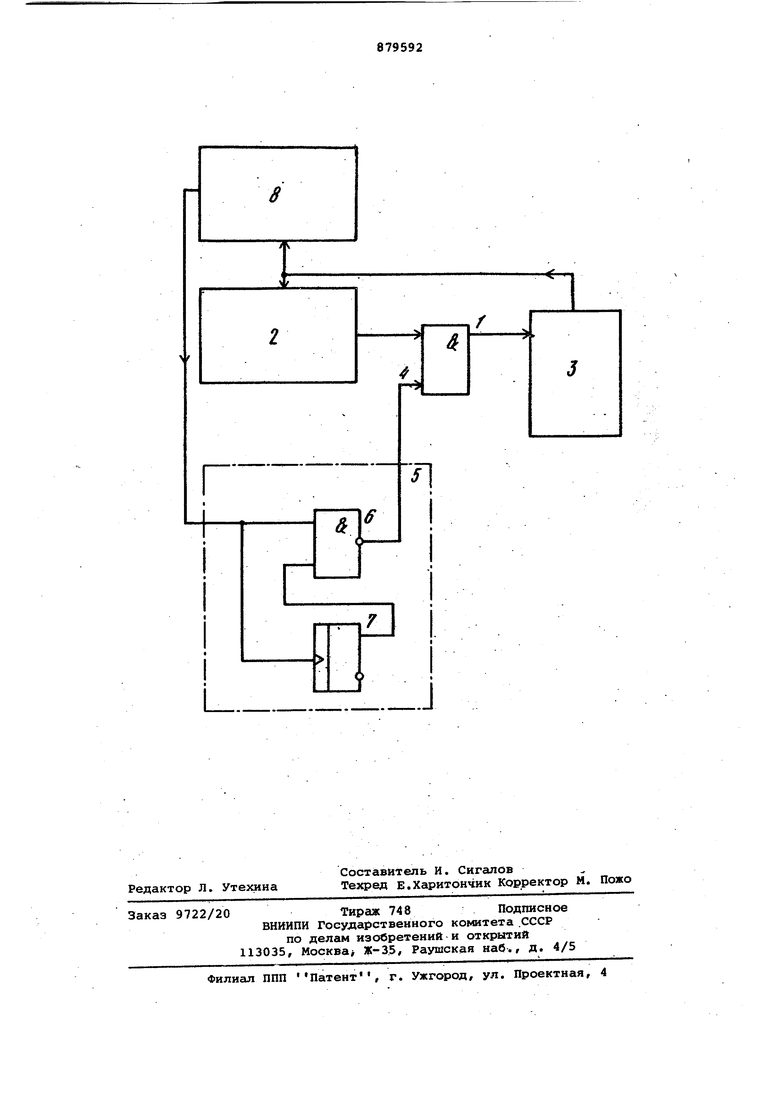

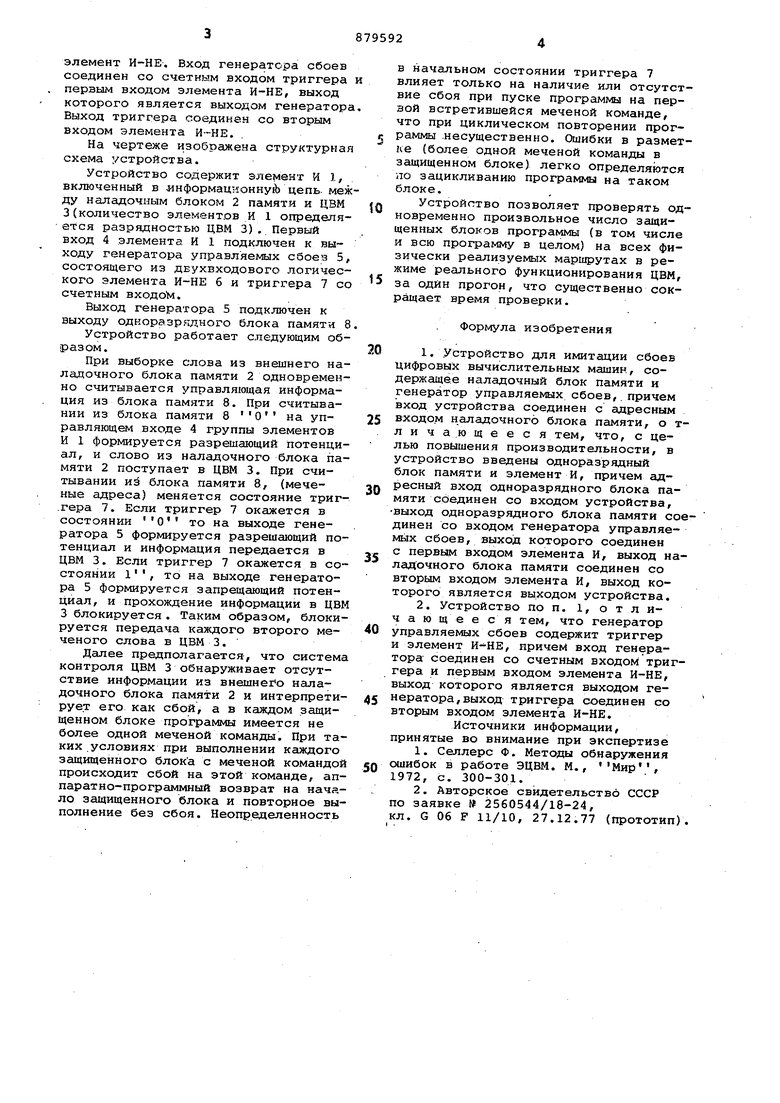

На чертеже изображена структурная схема устройства.

Устройство содержит элемент И 1, включенный в информационну1Ь цепь, между наладочным блоком 2 памяти и ЦВМ 3(количество элементов И 1 определяется разрядностью ЦВМ 3). Первый вход 4 элемента И 1 подключен к выходу генератора управляемых сбоев 5, состоящего из дЕухвходового логического элемента И-НЕ 6 и триггера 7 со счетным входом.

Выход генератора 5 подключен к выходу одноразрядного блока памяти 8

Устройство работает следующим образом.

При выборке слова из внешнего наладочного блока памяти 2 одновременно считывается управляющая информация из блока памяти 8. При считывании из блока памяти 8 на управляющем входе 4 группы элементов И 1 формируется разрешающий потенциал, и слово из наладочного блока памяти 2 поступает в ЦВМ 3. При считывании из блока памяти 8, (меченые адреса) меняется состояние триг.гера 7. Если триггер 7 окажется в

О

состоянии

то на выходе генератора 5 формируется разрешающий потенциал и информация передается в ЦВМ 3. Если триггер 7 окажется в состоянии 1, то на выходе генератора 5 формируется запрещающий потенциал, и прохождение информации в ЦВМ 3 блокируется . Таким образом, блокируется передача каждого второго меченого слова в ЦВМ 3.

Далее предполагается, что система контроля ЦВМ 3 обнаруживает отсутствие информации из внешнего наладочного блока памяти 2 и интерпретирует его как сбой, а в каждом защищенном блоке программы имеется не более одной меченой команды. При таких .условиях при выполнении каждого защищенного блока с меченой командой происходит сбой на этой команде, аппаратно-программный возврат на начало защищенного блока и повторное выполнение без сбоя. Неопределенность

в начальном состоянии триггера 7 влияет только на наличие или отсутствие сбоя при пуске программы на первой встретившейся меченой команде, что при циклическом повторении прогс раммы .несущественно. Ошибки в разметке (более одной меченой команды в защищенном блоке) легко определяются по зацикливанию программы на таком блоке.

Устройство позволяет проверять одновременно произвольное число защищенных блоков программы (в том числе и всю программу в целом) на всех физически реализуемых маршрутах в режиме реального функционирования ЦВМ,

5 за ОДИН прогон, что существенно сокращает время проверки.

Формула изобретения

0 1, Устройство для имитации сбоев цифровых вычислительных машин, содержащее наладочный блок памяти и генератор управляемых сбоев,. причем вход устройства соединен с адресным

5 входом наладочного блока памяти, о т. лича.ющеес я тем, что, с целью повышения производительности, в устройство введены одноразрядный блок памяти и элемент И, причем адQ ресный вход одноразрядного блока памяти соединен со входом устройства, выход одноразрядного блока памяти соединен со входом генератора управляемых сбоев, выход которого соединен

с первым входом элемента И, выход наладочного блока памяти соединен со вторым входом элемента И, выход которого является выходом устройства.

2. Устройство по п. 1, о т л ичающееся тем, что генератор

0 управляемых сбоев содержит триггер и элемент И-НЕ, причем вход генератора соединен со счетным входом триггера и первым входом элемента И-НЕ, выход которого является выходом генератора,выход триггера соединен со вторым входом элемента И-НЕ.

Источники информации, принятые во внимание при экспертизе

1.Селлерс Ф. Методы обнаружения 0 ошибок в работе ЭЦВМ. М., Мир,

1972, с. 300-301.

2.Авторское свидетельство СССР по заявке № 2560544/18-24,

кл. G 06 F 11/10, 27.12.77 (прототип).

/

4

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля правильности выполнения программ при сбоях | 1977 |

|

SU732876A1 |

| Устройство для имитации сбоев цифровых вычислительных машин | 1985 |

|

SU1300648A2 |

| Устройство для проверки полноты тестирования программ | 1983 |

|

SU1136171A1 |

| Устройство для имитации сбоев | 1983 |

|

SU1107126A1 |

| Устройство для контроля устойчивости функционирования программ | 1984 |

|

SU1256033A1 |

| Устройство для отладки программ | 1986 |

|

SU1327112A1 |

| Устройство для отладки программ | 1984 |

|

SU1275452A1 |

| Устройство для проверки полноты тестирования программ | 1987 |

|

SU1425686A1 |

| Устройство для имитации сбоев | 1985 |

|

SU1297056A1 |

| Устройство для контроля устойчивости функционирования программ | 1987 |

|

SU1437869A2 |

Г

L.

Л

..J

Авторы

Даты

1981-11-07—Публикация

1980-01-10—Подача