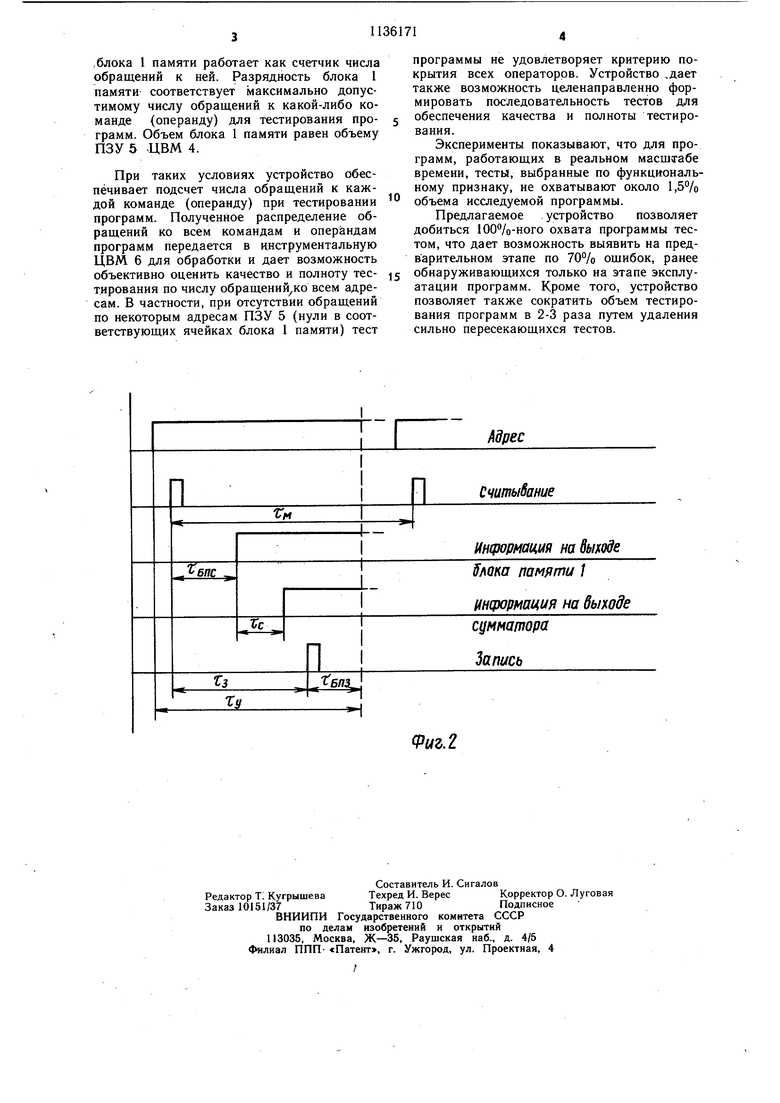

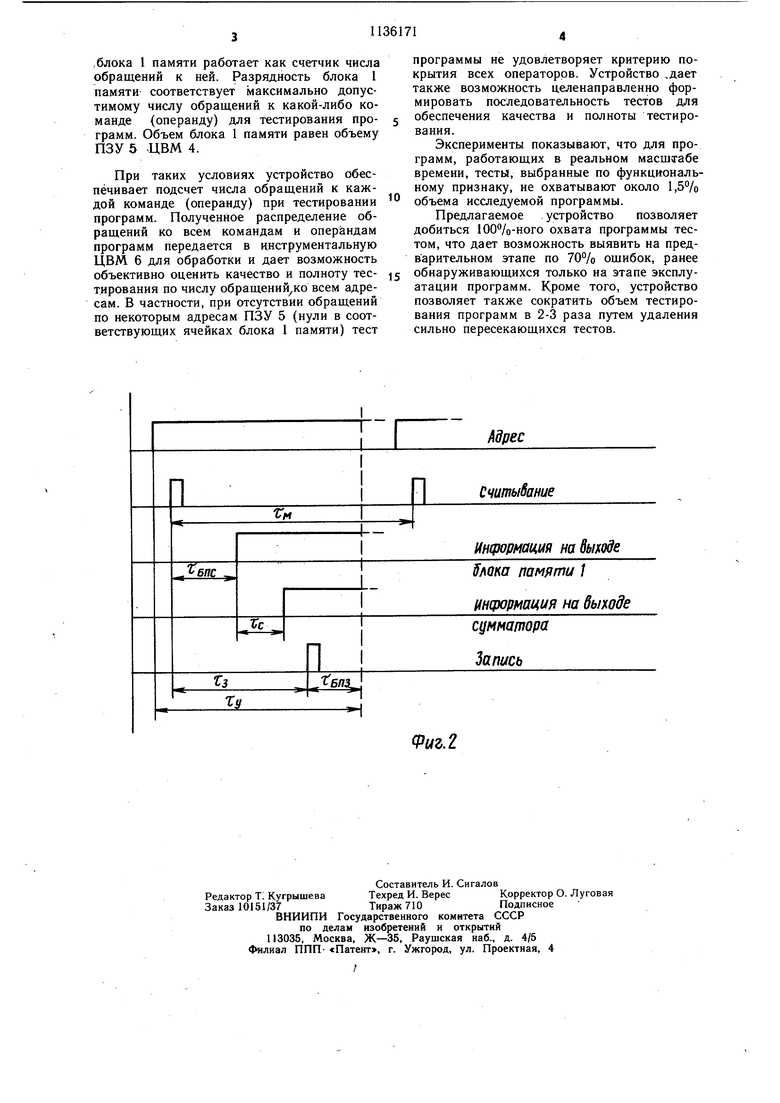

Изобретение относится к цифровой вычислительной технике и может быть использовано для проверки полноты тестирования программ специализированных управляющих цифровых вычислительных машин, которые имеют постоянное запоминающее устройство (ПЗУ) для размещения программ, а также допускают возможность подключения вместо ПЗУ внешнего наладочного блока памяти. Известно устройство для трассировки программ, содержащее блок памяти (стек), который подключается к магистрали ЦВМ, логические узлы и схемы индикации. После запуска исследуемой программы в ЦВМ логические узлы обеспечивают последовательное заполнение стека адресами выполняемых команд переходов, причем после заполнения последнего адреса организуется запись с начального адреса. При остановке программы устройство индикации дает возможность отобразить содержимое стека 1. Однако это устройство ориентировано на отладку программ и может дать ограниченную оценку полноты тестирования, так как оно содержит стек для запоминания конечной последовательности адресов команд только одного типа (перехода) и не дает возможности оценки полноты тестирования по известным критериям оценки качества теста. Наиболее близким по технической сущности к предлагаемому является устройство для проверки полноты тестирования программ, которое состоит из одноразрядного блока памяти и управляющего логического блока. Одноразрядный блок памяти работает параллельно с наладочным блоком памяти специализированной ЦВМ. При запуске исследуемой программы в ЦВМ логический узел обеспечивает появление сбоев в работе ЦВМ при обращении к тем адресам блока памяти, в которые предварительно записываются единицы 2. Однако известное устройство позволяет оценить только качество тестирования системы защиты исследуемой программы от аппаратно обнаруживаемых сбоев и не дает возможности систематически оценить качество тестирования по известным критериям. Целью изобретения является повышение полноты тестирования программ по систематическому критерию, основанному на фиксации в режиме реального функционирования всех обращений исследуемой программы ЦВМ к командам и операндам. Поставленная цель достигается тем, что в устройство для проверки полноты тестирования программ, содержащее блок памяти, адресный и управляющий входы чтения которого являются соответственно информационным в-ходом и входом запуска проверки устройства, информационный выход блока памяти является выходом проверки устройства, введены сумматор и элемент задержки, причем вход запуска проверки устройства через элемент задержки соединен с управляющим входом записи блока памяти, информационный выход блока памяти соединен с входом первого операнда сумматора, вход второго операнда которого соединен с входом единичного потенциала устройства, выход сумматора соединен с информационным входом блока памяти. На фиг. 1 приведена структурная электрическая схема предлагаемого устройства; на фиг. 2 - диаграмма работы устройства; где €м - период обращения ЦВМ () к ПЗУ, Бйс - цикл считывания в блоке памяти, с, - время установления суммы на выходе сумматора, Cj - время задержки сигнала в элементе задержки, бпз - цикл записи в блоке памяти, Sy - цикл работы устройства. Устройство для проверки полноты тестирования программ содержит блок 1 памяти, элемент 2 задержки и сумматор 3. Адресные входы и управляющие входы чтения блока 1 памяти соединены с соответствующими выходами ЦВМ 4 параллельно с ПЗУ 5 (или наладочным блоком памяти), содержащим исследуемую программу. Первый вход сумматора 3 подключен к выходным информационным выходам блока 1 памяти на второй вход сумматора 3 постоянно подается единица, а выход сумматора 3 подключен к входу первого блока 1 памяти. Выход элемента 2 задержки подключен к входу «Запись блока 1 памяти. Второй вход блока I памяти соединен с инструментальной ЦВМ 6, которая используется для подготовки устройства к работе и для обработки полученных устройством результатов. Устройство работает следующим образом. Предварительно в блоке 1 памяти обнуляются все ячейки с помощью инструментальной ЦВМ 6. Далее на ЦВМ 4 опускается тестируемая программа. Поскольку устройство подключено к адресной магистрали и управляющей линии «Чтение ЦВМ 4 параллельно с ПЗУ 5, то одновременно с обращением ЦВМ 4 по некоторому адресу за командой или операндом происходит считывание по тому же адресу информации из блока 1 памяти. Число, считанное из блока 1 памяти, поступает на первый вход сумматора 3, где к нему прибавляется единица, постоянно подаваемая (схемной реализацией) на второй вход сумматора 3. Получившееся число записывается в блок 1 памяти по тому же адресу по сигналу записи, формируемому из сигнала считывания, задержанного на величину элемента 2 задержки. Таким образом, каждая ячейка

,блока 1 памяти работает как счетчик числа обращений к ней. Разрядность блока 1 памяти соответствует максимально допустимому числу обращений к какой-либо команде (операнду) для тестирования программ. Объем блока 1 памяти равен объему ПЗУ 5 -ЦВМ 4.

При таких условиях устройство обеспечивает подсчет числа обращений к каждой команде (операнду) при тестировании программ. Полученное распределение обращений ко всем командам и операндам программ передается в инструментальную ЦВМ 6 для обработки и дает возможность объективно оценить качество и полноту тестирования по числу обращений/ко всем адресам. В частности, при отсутствии обращений по некоторым адресам ПЗУ 5 (нули в соответствующих ячейках блока 1 памяти) тест

программы не удовлетворяет критерию покрытия всех операторов. Устройство ,дает также возможность целенаправленно формировать последовательность тестов для обеспечения качества и полноты тестирования.

Эксперименты показывают, что для программ, работающих в реальном масщтабе времени, тесты, выбранные по функциональному признаку, не охватывают около 1,5% объема исследуемой программы.

Предлагаемое устройство позволяет добиться ЮО /о-ного охвата программы тестом, что дает возможность выявить на предварительном этапе по 70% ошибок, ранее обнаруживающихся только на этапе эксплуатации программ. Кроме того, устройство позволяет также сократить объем тестирования программ в 2-3 раза путем удаления сильно пересекающихся тестов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для проверки полноты тестирования программ | 1987 |

|

SU1425686A1 |

| Устройство для отладки программ | 1986 |

|

SU1327112A1 |

| Устройство для тестового контроля больших интегральных схем | 1984 |

|

SU1218390A1 |

| Вычислительная система | 1989 |

|

SU1777148A1 |

| Устройство для формирования информации о полноте тестирования программ | 1987 |

|

SU1499353A1 |

| Устройство контроля микропроцессорных блоков | 1986 |

|

SU1332320A2 |

| Устройство управления конвейерным вычислительным устройством | 1980 |

|

SU896623A1 |

| Устройство для тестового контроля блоков памяти | 1986 |

|

SU1365134A1 |

| Устройство для контроля микропроцессорных блоков | 1988 |

|

SU1531099A1 |

| Устройство для контроля правильности выполнения программ при сбоях | 1977 |

|

SU732876A1 |

УСТРОЙСТВО ДЛЯ ПРОВЕРКИ ПОЛНОТЫ ТЕСТИРОВАНИЯ ПРОГРАММ содержащее блок памяти, адресный и управляющий входы чтения которого являются соответственно информационным входом и входом запуска проверки устройства, информационный выход блока памяти является выходом проверки устройства, отличающееся тем, что, с целью увеличения полноты контроля, в него введены сумматор и элемент задержки, причем вход запуска проверки устройства через элемент задержки соединен с управляющим входом записи блока памяти, информационный выход блока памяти соединен с входом первого операнда сумматора, вход второго операнда которого соединен с входом единичного потенциала устройства, выход сумматора соединен с информационным входом блока памяти. о:) О)

.ТбПС

,Гс

гз

rjL

Считыбание

Информация на Выходе

ffAQKo памяти / Инозормация на бымде

сумматора Запись

fpuz,2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Сигалов И | |||

| Л | |||

| и др | |||

| Устройство для отладки программ | |||

| - «Управляющие системы и машины, 1980, № 1 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для имитации сбоев цифровых вычислительных машин | 1980 |

|

SU879592A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-01-23—Публикация

1983-04-04—Подача