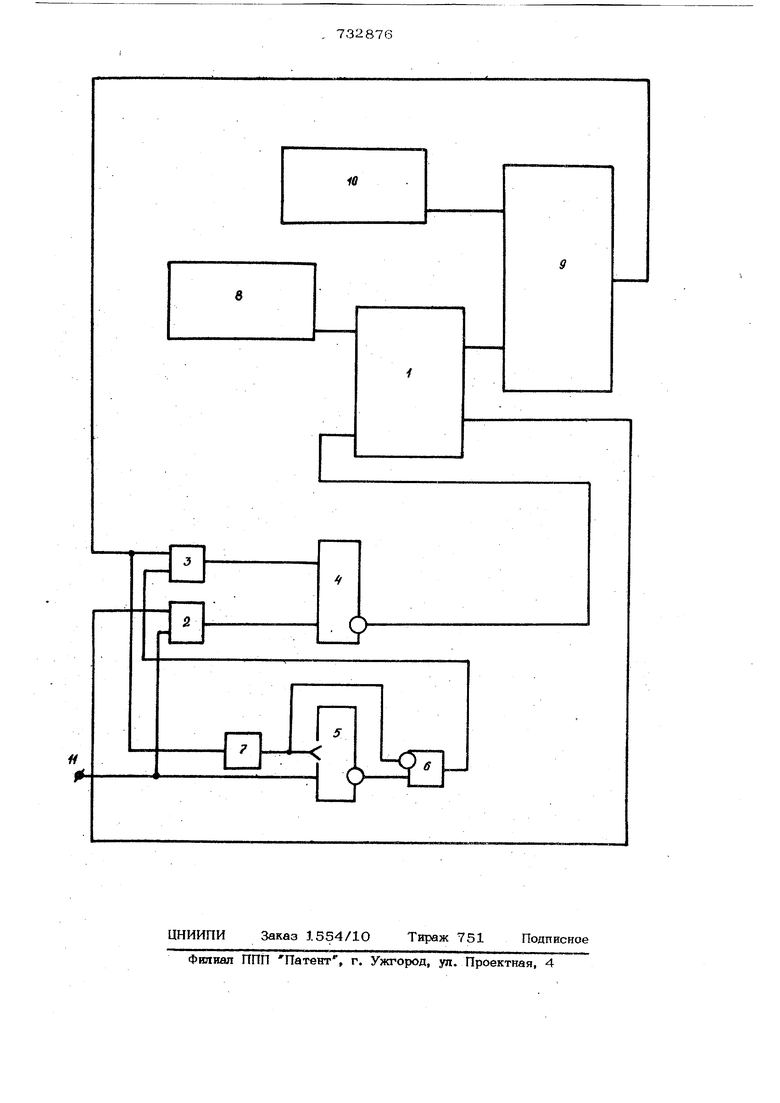

Изобретение относится к цифровой вычислительной технике и может быть испол зовано для проверки устойчивости и сбоям программ специализированных ЦВМ, имек щих средства аппаратного контроля и программную защиту от сбоев, организованную путем разбиения программ на участ ки, допускающие повторное исполнение пос ле сбоя. Эти участки далее называются защищенными блоками. Рассматриваемые специализированные ЦВМ имеют постоянное запоминающее устройство для хранения программ, вход для подключения внеш него наладочного запоминающего устройства и вход, управляющий выборкой из внешнего наладочного запомина1рщего устройства. Известно устройство для определения эффективности схем контроля ЦВМ путем введения ошибок l. Недостаток этого устройстваi состоит в йевозможности проверки правильности выполнения программ при сбоях. Наиболее близким по технической сущности к изобретению является устройство для проверки качества соединения в ци ьровой телефонии, содержащее генератор сбоев, введенный в информационную линию управляемый схемой, определяющей момент времени, когда необходимо создать сбой. С.бой создается инвертированием контрольного бита четкости в передаваемой информации 2. Однако данное устройство в применении для проверки программ ЦВМ имеет ряд недостатков. Включение генератора сбоев в канал связи между п)амятью и процессором приводит к увепиченто цикла выборки из памяти, что может вызвать незапланированные сбои или вообще потерю работоспособности вычислительной мащины. Кроме того,формирование сбоев при каждом достижении определенного ад реса команды приводит к зацикливанию программ. Цель изобретения - повышение достогверности контроля для проверки защищенности от сбоев программы, исполняемой в режиме реального функционирования. Поставленная цель достигается тем, что в устройство для контроля правильности выполнения программ при сбоях, содержащее регистр введен блок сравнения адресов команд, первый и второй триггеры, первый и второй элементы И, элемент ИЛИ, элемент задержки, при чем нулевой выход первого триггера соединен с первым выходом устройства, выход первого элемента И соединен с единичным входом первого триггера, нулевой вход которого соединен с выходом элемента ИЛИ, вь1х;од блока срав нения адресов команд соединен с первым входом первого элемента И и входом элемента задержки, выход которого соединен со счетным входом второго триггера и с инверсным входом второго элемента И, нулевой выход второго триггера соединен со входом второго элемента И выход которого соединен со вторым входом первого элемента И, выход регистра соединен с первым входом блока сравнения адресов команд, второй вход которого является первым входом устройства, первый вход элемента ИЛИ является вторым входом устройства, третий вход которого соедине со вторым входом элемента ИЛИ и с уста новочным входом второго триггера. На чертеже приведена структурная схема устройства. Устройство содержит цифровую вычислительную маилшу 1, элемент И7{И 2, первый элемент И 3, первый триггер 4, второй триггер 5 со счетным входом, вто рой элемент И б, элемент 7 задержки, наладочное запоминающее устройство 8, блок 9 сравнения адресов команд, регистр 10. На вход 11 подается сигнал установка в исходное состояние. Выход наладочного запоминающего устройства 8 подключен к дополнительному входу цифровой вычислительной машины, предназначенного для подключения внешнего наладочного запоминающего устройства. В ЦВМ используется аппаратный контроль по модулю 3 и контрольной код равен наименьшему вычету по модулю 3 плюс 1. Устройство работает следующим образом. , Установка устройства в исходное состояние осуществляется подачей на управляющие входы триггеров 4 и. 5 сигнала установка в исходное состояние . При этом с нулевого выхода первого триггера 4 выдается.на вход цифровой вычислительной машины 1 разрешающий потенциал, при наличии которого в регистр числа (на чертеже не показан) постоянного запоминающего устройства, размещенного в цифровой вычислительной машине, по числовой магистрали принимается из внешнего наладочного запоминающего устройства 8 слово с правильным контрольным кодом по модулю 3; а с нулевого выхода триг-. гера 5 со счетным входом сигнал через второй элемент И 6 (при отсутствии сигнала на его запрещающем входе) поступает на вход первого элемента И 3. Для формирования сбоя в нужном месте проверяемой программы на регистре 10 устанавливается код адреса команды, при котором происходит сбой. Блок 9 сравнения адресов команд сравнивает адрес, выдаваемый регистром адреса команд (на чертеже не указан) цифровой вычислительной машины 1, и адрес, набранный на регистре 10, при совпадении выдает сигнал, который поступает на вход первого элемента И 3. Поскольку на втором егхэ входе присутствует сигнал, то первый элемент И 3 выдает сигнал, поступающий на единичный вход первого триггера 4, Этим сигналом триггер 4 переводится в единичное состояние. Сигнал с выхода блока 9 сравнения адресов команд, задержанный элементом 7 задержки на время, необходимое для переключения триггера 4, поступает на запрешаюший вход второго элемента И 6 и на счетный вход второго триггера 5. При этом запрещается прохождение сигнала с выхода второго элемента И б на вход первого элемента И 3, а триггер 5 переводится в единичное состояние. Поскольку триггер 4 переведен в единичное состояние, на входе цифровой вычислительной машины отсутствует раз решающий потенциал, что запрещает прохождение по числовой магистрали слова из внешнего наладочного запоминающего устройства 8 в регистр числа постоянного запоминающего устройства цифровой вычислительной машины 1. При этом в регистре числа постоянного запоминающего устройства фиксируется наличие слова, состоящего из нулей с неправильным контрольным кодом по модулю 3. В этом случае находящаяся в ЦВМ схема .формирования сигнала признак сбоя (на чертеже не показана) выдает сигнал обратной свя- зщ устанавливающий через элемент ИЛИ 2 триггер 4 в состояние О, при этом с выхода триггера 4 выдается потенциал. 573 разрешающий прохождение по числовой магистрали слова из внешнего наладочного запоминающего устройства 8 в регистр числа цифровой вычислительной машины. Таким образом, в фиксированную точку программы вводится сбой а аппаратнопрограммная система защиты производит возврат в начальную точку той части программы (защищенного блока), в которой содержится адрес команды, набранной на регистре. Если на клавишном регистре 1О сохранить код адреса команды, при котором имеет место сбой, то этот адрес пов торяется вновь при возврате на начало защищенного блока. Однако при следующем совпадении адресов и выдаче сигнала с выхода блбка 9 сравнения адресов команд триггер 4 не переводится в единичное состояние, так как на.втором входе первого элемента И 3 сигнал отсутствует, хотя триггер 5 задержанным сигналом с выХо да блока сравнения адресов команд переводится в нулевое состояние. Это обеспечено тем, что присутствие задержанного сигнала с выхбда блока сравнения адресов команд на запрещающем входе второго элемента И 6 запрещает выдачу сигнала на вход первого элемента И 3 в течение всего времен-и поступления сигнала, определяющего совпадение адресов. Поскольку при повторной выдаче сигнала с выхода блока 9 сравнения адресов команд сбой не формируется, проверяемый участок программы вьшолняется до конца и далее вьшолняется вся проверяемая программа. Если проверяемая программа повторяется с некоторой частотой, то каж дая вторая выдача сигнала с выхода блока 9 сравнения адресов команд не вызывает управляемого сбоя на заданном участ ке программы. Тем самым повышается эффективность -проверки защищенных блоков, так как имеется возможность многократно набгаодать реальное исполнение программы до конца со сбоеТ в заданной точке. Устройство для контроля правильности вьтолнения программ при сбоях позволяет систематически проверять вс.е защищенные блоки программы. Кроме того, оно позво6ляет произвести общую проверку работоспособности программы в условиях сбоев. Для этого следует подать на вход устройства сигналы от внешнего генератора с периодом следования больше половины максимального из времени исполнения за щшденных блоков. Формула изобретения Устройство для контроля правильности выполнения программ при сбоях, содержащее регистр, отличающееся тем, что, с целью повышения достоверности контроля, в устройство введен блок сравнения адресов команд, первый и вто- рой триггеры, первый и второй элементы И, элемент ИЛИ, элемент задержки, причем нулевой выход первого триггера соединен с первым выходом устройства, выход первого элемента И соединен с единичным входом первого триггера, нулевой вход которого соединен с выходом элемента ИЛИ, выход блока сравнения адресов команд соединен с первым входом первого элемента И и входом элемента задержки, выход которого соединен со счетным входом второго триггера и с инверсным входом второго элемента И, нулевой выход второго триггера соединен со входом второго элемента И, выход которого соединен со -вторым входом первого элемен та И, выход регистра соединен с первым входом блока сравнения адресов команд, второй вход которогчз является первым вхо дом устройства, первый вход элемента ИЛИ является вторым входом устройства, третий вход которого соединен со вторым входом элемента ИЛИ и с установочным входом второго триггера. Источники информации, принятые во внимание при экспертизе 1.Селлерс Ф, Методы обнаружения ошибок в работе ЭЦВМ. М., Мир, 1972, с. ЗОО-ЗО1. 2.Патент Франции -№ 2281605, кл. G 06 F 11/10, 09.О4.76 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для имитации сбоев цифровых вычислительных машин | 1980 |

|

SU879592A1 |

| Устройство для отладки программ | 1986 |

|

SU1327112A1 |

| Устройство для проверки полноты тестирования программ | 1983 |

|

SU1136171A1 |

| Устройство для проверки полноты тестирования программ | 1987 |

|

SU1425686A1 |

| Устройство для проверки программ на сбое устойчивость | 1984 |

|

SU1205148A1 |

| Устройство для проверки программы на сбоеустойчивость | 1985 |

|

SU1282138A1 |

| Устройство для проверки программ на сбоеустойчивость | 1986 |

|

SU1411753A2 |

| Устройство для имитации сбоев цифровых вычислительных машин | 1985 |

|

SU1300648A2 |

| Устройство для имитации сбоев и неисправностей цифровой вычислительной машины | 1985 |

|

SU1265779A1 |

| Устройство для тестового контроля цифровых вычислительных машин | 1981 |

|

SU964647A1 |

Авторы

Даты

1980-05-05—Публикация

1977-12-27—Подача