(54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО НА ПОЛНОТОЧНОМНАКОПИТЕЛЕ | 1971 |

|

SU289514A1 |

| Запоминающее устройство | 1978 |

|

SU799001A1 |

| Запоминающее устройство с исправлением ошибок при считывании информации | 1976 |

|

SU607281A1 |

| АССОЦИАТИВНО-АДРЕСНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU336697A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВОСЙ1Ч '^ | 1972 |

|

SU436389A1 |

| ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU344498A1 |

| Устройство для диспетчерской дуплексной связи | 1985 |

|

SU1293853A1 |

| Запоминающее устройство | 1972 |

|

SU517935A1 |

| Запоминающее устройство | 1980 |

|

SU928409A1 |

| Устройство для графического отображения синтезируемой устной речи | 1986 |

|

SU1411802A1 |

Изобретение относится к области запоминающих устройств. Известно выполненное по системе ЗД с матричной селекцией D D Недостатком этого устройства явля ётся большое число селектирующих шин Из известных устройств наиболее близким техническим рещением к изобретению является ЗД содержащее накоп тель, дешифраторы, формирователи импульсов выборки и логические элементы 2. Это устройство требует большого числа селектирующих шин, соединякицих дешифраторы с накопителем, при хорошем избирающем отношении, что снижает надежность устройства. Целью изобретения является сокращение числа селектирующих шин соединения дешифраторов с накопителем при заданном объеме накопителя или увели чении объема накопителя при сохранении числа селектирующих шин, т.е. по вьш1ение надежности ЗУ. Поставленная цель достигается тем, что в ЗУ, содержащее дешифраторы, накопитель, группы формирователей двухполярных импульсов, группу элементов НЕ, причем выхода первого дешифратора подключены к одним из входов формирователей двухполярных импульсов, выходы которых соединены с соответствующими входами накопителя, управляемые входы элементов НЕ соединены с управляющим входом устройства, а входы дешифраторов являются адресными входами устройства, введен функциональный преобразователь, входы которого подключены к выходам второго депшфратора, а выходы соединены с другими входами управляемых элементов НЕ, выходь которьЬс подключены соответственно к другим входам формирователей двухполярных импульсов, входящих в одну группу. При этом целесообразно функциональный преобразователь выполнить в виде .преобразователя двоичного кода в код

Адрмара К-го порядка (где К :j 4 - i|eлое) .

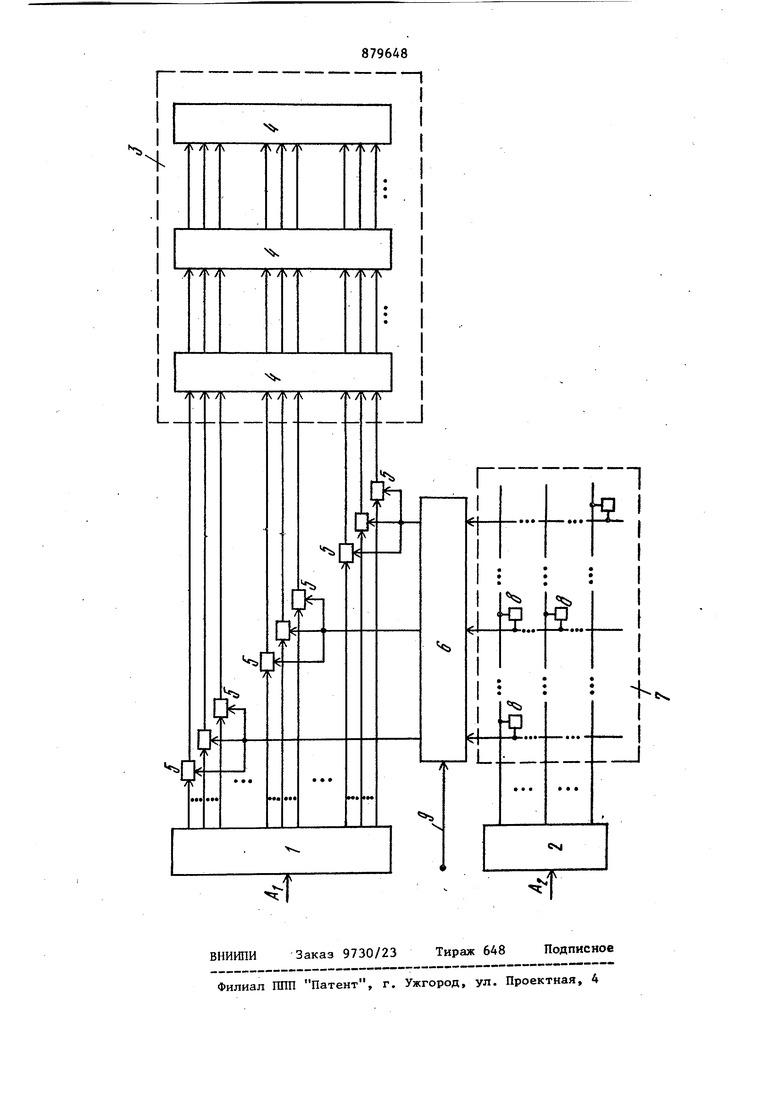

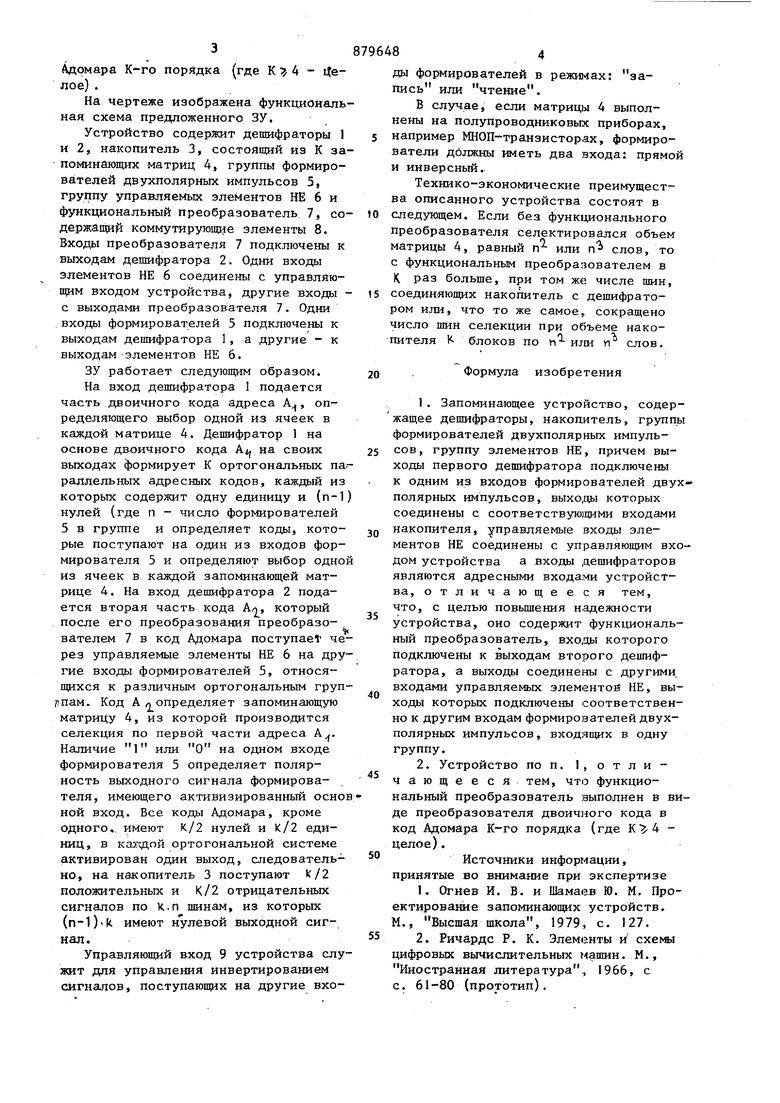

На чертеже изображена функциональная схема предложенного ЗУ.

Устройство содержит дешифраторы 1 и 2, накопитель 3, состоящий из К запоминающих матриц 4, группы формирователей двухполярных импульсов 5, группу управляемых элементов НЕ 6 и функциональный преобразователь. 7, содержащи й коммутирующие элементы В. Входы преобразователя 7 подключены к выходам дешифратора 2. Одни входы элементов НЕ 6 соединены с управляющим входом устройства, другие входы с выходами преобразователя 7. Одни входы формирователей 5 подключены к выходам дешифратора 1, а другие - к выходам элементов НЕ 6.

ЗУ работает следующим образом.

На вход дешифратора 1 подается часть двоичного кода адреса А, определяющего выбор одной из ячеек в каждой матрице 4. Дешифратор 1 на основе двоичного кода на своих выходах формирует К ортогональных параллельных адресных кодов, каждый из которых содержит одну единицу и (п-1) нулей (где п - число формирователей 5 в группе и определяет коды, которые поступают на один из входов формирователя 5 и определяют выбор одной из ячеек в каждой запоминающей матрице 4. На вход дешифратора 2 подается вторая часть кода An, который после его преобразования преобразователем 7 в код Адомара nocTynaet через управляемые элементы НЕ 6 на другие входы формирователей 5, относяШ5нхся к различным ортогональным груп; пам. Код А п определяет запоминающую матрицу 4, из которой производится селекция по первой части адреса А. Наличие 1 или О на одном входе формирователя 5 определяет полярность выходного сигнала формирова- . теля, имеющего активизированный основной вход. Все коды Адомара, кроме одного,, имеют К/2 нулей и К/2 единиц, в ка :сдой ортогональной системе активирован один выход, следовательно, на накопитель 3 поступают /2 положительных и К/2 отрицательных сигналов по К.п шинам, из которых (n-l)k имеют нулевой выходной сигнал.

Управляющий вход 9 устройства служит для управления инвертированием сигналов, поступающих на другие входы формирователей в режиз «ах

за.11 чтение.

пись или

в случае, если матрицы 4 выполнены на полупроводниковых приборах, например МНОП-транзисторах, формирователи должны иметь два входа: прямо и инверсный.

Технико-экономические преимущества описанного устройства состоят в следующем. Если без функ11(ионального преобразователя селектировался объем матрицы 4, равный п или п слов, то с функциональным преобразователем в К раз больше, при том же числе шин, соединяющих накопитель с дешифратором или, что то же самое, сокращено Число шин селекции при объеме накоп или пителя К блоков по

слов.

Формула изобретения

к одним из входов формирователей двухполярных импульсов, выхо,ць1 которых соединены с соответствуюгцими входами накопителя, управляемые входы элементов НЕ соединены с управляюш 1М входом устройства а входы дешифраторов являются адресными входами устройства, отличающее ся тем, что, с целью повьш1ения н.адежности устройства, оно содержит функциональный преобразователь, входа которого подключены к выходам второго дешифратора, а выходы соедине1яя с другими, входами управляемых элементой НЕ, выходы которых подключены соответственно к другим входам формирователей двухполярных импульсов, входящих в одну группу.

Источники информации, принятые во внимание при экспертизе

с. 61-80 (прототип).

Чь

I

/ /N/V/V/r/V/

ч I

/ / / /X/ /V/V/ /

/ Vv/V/v/v/ /WWS

I

I

г

n

Авторы

Даты

1981-11-07—Публикация

1980-01-11—Подача